Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

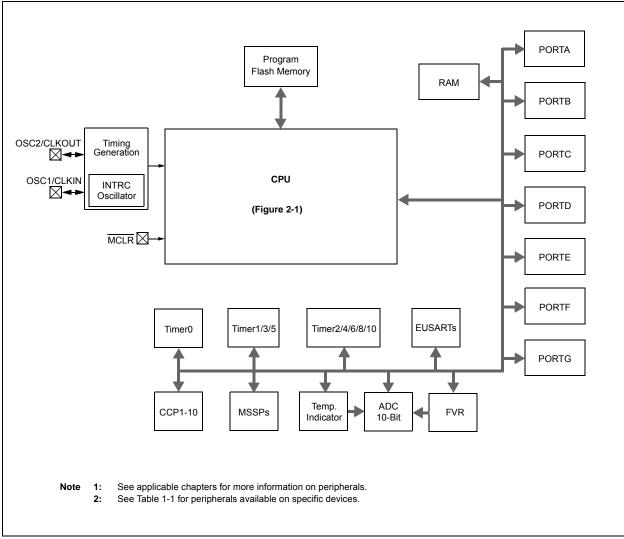

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 54                                                                          |

| Program Memory Size        | 28KB (16K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 1.5K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 30x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 64-TQFP                                                                     |

| Supplier Device Package    | 64-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1527t-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16(L)F151X/152X Family Types

|               |                  |                                 |                      | tes)                         |                      | AI          | C                |                      |        |                             |     |                      |     |

|---------------|------------------|---------------------------------|----------------------|------------------------------|----------------------|-------------|------------------|----------------------|--------|-----------------------------|-----|----------------------|-----|

| Device        | Data Sheet Index | Program Memory<br>Flash (words) | Data SRAM<br>(bytes) | High-Endurance Flash (bytes) | I/O's <sup>(2)</sup> | 10-bit (ch) | Advanced Control | Timers<br>(8/16-bit) | EUSART | MSSP (I <sup>2</sup> C/SPI) | ССР | Debug <sup>(1)</sup> | XLP |

| PIC16(L)F1512 | (1)              | 2048                            | 128                  | 128                          | 25                   | 17          | Y                | 2/1                  | 1      | 1                           | 2   | I                    | Y   |

| PIC16(L)F1513 | (1)              | 4096                            | 256                  | 128                          | 25                   | 17          | Y                | 2/1                  | 1      | 1                           | 2   | I                    | Y   |

| PIC16(L)F1516 | (2)              | 8192                            | 512                  | 128                          | 25                   | 17          | N                | 2/1                  | 1      | 1                           | 2   | I                    | Y   |

| PIC16(L)F1517 | (2)              | 8192                            | 512                  | 128                          | 36                   | 28          | Ν                | 2/1                  | 1      | 1                           | 2   | I                    | Y   |

| PIC16(L)F1518 | (2)              | 16384                           | 1024                 | 128                          | 25                   | 17          | Ν                | 2/1                  | 1      | 1                           | 2   | I                    | Y   |

| PIC16(L)F1519 | (2)              | 16384                           | 1024                 | 128                          | 36                   | 28          | Ν                | 2/1                  | 1      | 1                           | 2   | I                    | Y   |

| PIC16(L)F1526 | (3)              | 8192                            | 768                  | 128                          | 54                   | 30          | N                | 6/3                  | 2      | 2                           | 10  | 1                    | Y   |

| PIC16(L)F1527 | (3)              | 16384                           | 1536                 | 128                          | 54                   | 30          | Ν                | 6/3                  | 2      | 2                           | 10  |                      | Y   |

Note 1: I - Debugging, Integrated on Chip; H - Debugging, available using Debug Header.2: One pin is input-only.

Data Sheet Index: (Unshaded devices are described in this document.)

- 1: DS41624 PIC16(L)F1512/13 Data Sheet, 28-Pin Flash, 8-bit Microcontrollers.

- **2:** DS41452 PIC16(L)F1516/7/8/9 Data Sheet, 28/40/44-Pin Flash, 8-bit MCUs.

- **3:** DS41458 PIC16(L)F1526/7 Data Sheet, 64-Pin Flash, 8-bit MCUs.

**Note:** For other small form-factor package availability and marking information, please visit http://www.microchip.com/packaging or contact your local sales office.

| .,   | _E 3-2: \$ |            |                                                                  |                           |               |              |         |       |           |                      | Value en                        |

|------|------------|------------|------------------------------------------------------------------|---------------------------|---------------|--------------|---------|-------|-----------|----------------------|---------------------------------|

| Addr | Name       | Bit 7      | Bit 6                                                            | Bit 5                     | Bit 4         | Bit 3        | Bit 2   | Bit 1 | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

| Ban  | k 4        |            |                                                                  |                           |               |              |         |       |           |                      |                                 |

| 20Ch | _          | Unimpleme  | nted                                                             |                           |               |              |         |       |           | —                    | —                               |

| 20Dh | WPUB       | WPUB7      | WPUB6                                                            | WPUB5                     | WPUB4         | WPUB3        | WPUB2   | WPUB1 | WPUB0     | 1111 1111            | 1111 1111                       |

| 20Eh | _          | Unimpleme  | Unimplemented                                                    |                           |               |              |         |       |           |                      |                                 |

| 20Fh | WPUD       | WPUD7      | WPUD6                                                            | WPUD5                     | WPUD4         | WPUD3        | WPUD2   | WPUD1 | WPUD0     | 1111 1111            | 1111 1111                       |

| 210h | WPUE       | WPUE7      | WPUE6                                                            | WPUE5                     | WPUE4         | WPUE3        | WPUE2   | WPUE1 | WPUE0     | 1111 1111            | 1111 1111                       |

| 211h | SSP1BUF    | Synchronou | us Serial Por                                                    | t Receive Bu              | uffer/Transmi | it Register  |         |       |           | xxxx xxxx            | uuuu uuuu                       |

| 212h | SSP1ADD    | Synchronou | us Serial Por                                                    | t (I <sup>2</sup> C mode) | Address Re    | egister      |         |       |           | 0000 0000            | 0000 0000                       |

| 213h | SSP1MSK    | Synchronou | us Serial Por                                                    | t (I <sup>2</sup> C mode) | Address Ma    | ask Register |         |       |           | 1111 1111            | 1111 1111                       |

| 214h | SSP1STAT   | SMP        | CKE                                                              | D/A                       | Р             | S            | R/W     | UA    | BF        | 0000 0000            | 0000 0000                       |

| 215h | SSP1CON1   | WCOL       | SSPOV                                                            | SSPEN                     | CKP           |              | SSPM<   | <3:0> |           | 0000 0000            | 0000 0000                       |

| 216h | SSP1CON2   | GCEN       | ACKSTAT                                                          | ACKDT                     | ACKEN         | RCEN         | PEN     | RSEN  | SEN       | 0000 0000            | 0000 0000                       |

| 217h | SSP1CON3   | ACKTIM     | PCIE                                                             | SCIE                      | BOEN          | SDAHT        | SBCDE   | AHEN  | DHEN      | 0000 0000            | 0000 0000                       |

| 218h | _          | Unimpleme  | nted                                                             |                           |               |              |         |       |           | _                    | _                               |

| 219h | SSP2BUF    | Synchronou | us Serial Por                                                    | t Receive Bu              | uffer/Transmi | it Register  |         |       |           | xxxx xxxx            | uuuu uuuu                       |

| 21Ah | SSP2ADD    | Synchronou | Synchronous Serial Port (I <sup>2</sup> C mode) Address Register |                           |               |              |         |       |           | 0000 0000            | 0000 0000                       |

| 21Bh | SSP2MSK    | Synchronou | us Serial Por                                                    | t (I <sup>2</sup> C mode) | Address Ma    | ask Register |         |       |           | 1111 1111            | 1111 1111                       |

| 21Ch | SSP2STAT   | SMP        | CKE                                                              | D/A                       | Р             | S            | R/W     | UA    | BF        | 0000 0000            | 0000 0000                       |

| 21Dh | SSP2CON1   | WCOL       | SSPOV                                                            | SSPEN                     | CKP           |              | SSPM    | <3:0> |           | 0000 0000            | 0000 0000                       |

| 21Eh | SSP2CON2   | GCEN       | ACKSTAT                                                          | ACKDT                     | ACKEN         | RCEN         | PEN     | RSEN  | SEN       | 0000 0000            | 0000 0000                       |

| 21Fh | SSP2CON3   | ACKTIM     | PCIE                                                             | SCIE                      | BOEN          | SDAHT        | SBCDE   | AHEN  | DHEN      | 0000 0000            | 0000 0000                       |

| Ban  | k 5        |            |                                                                  |                           |               |              |         |       |           |                      |                                 |

| 28Ch | PORTF      | RF7        | RF6                                                              | RF5                       | RF4           | RF3          | RF2     | RF1   | RF0       | xxxx xxxx            | uuuu uuuu                       |

| 28Dh | PORTG      | —          | _                                                                | RG5                       | RG4           | RG3          | RG2     | RG1   | RG0       | xx xxxx              | uu uuuu                         |

| 28Eh |            | Unimpleme  | nted                                                             |                           | •             |              |         | •     | •         | _                    | _                               |

| 28Fh |            | Unimpleme  | Unimplemented                                                    |                           |               |              |         |       | _         | _                    |                                 |

| 290h |            | Unimpleme  | Unimplemented                                                    |                           |               |              |         |       | _         | _                    |                                 |

| 291h | CCPR1L     | Capture/Co | Capture/Compare/PWM Register 1 (LSB)                             |                           |               |              |         |       |           | xxxx xxxx            | uuuu uuuu                       |

| 292h | CCPR1H     | Capture/Co | mpare/PWIV                                                       | Register 1                | (MSB)         |              |         |       |           | XXXX XXXX            | uuuu uuuu                       |

| 293h | CCP1CON    | _          | _                                                                | DC1E                      | 3<1:0>        |              | CCP1M   | <3:0> |           | 00 0000              | 00 0000                         |

| 294h |            | Unimpleme  | nted                                                             |                           |               |              |         |       |           | _                    | _                               |

| 295h |            | Unimpleme  | Unimplemented                                                    |                           |               |              |         |       |           | _                    | _                               |

| 296h |            | Unimpleme  | nted                                                             |                           |               |              |         |       |           | _                    | _                               |

| 297h | _          | Unimpleme  | Unimplemented                                                    |                           |               |              |         |       |           | _                    | _                               |

| 298h | CCPR2L     |            | Capture/Compare/PWM Register 2 (LSB)                             |                           |               |              |         |       | xxxx xxxx | uuuu uuuu            |                                 |

| 299h | CCPR2H     | -          | Capture/Compare/PWM Register 2 (ISB)                             |                           |               |              |         |       |           | xxxx xxxx            | uuuu uuuu                       |

| 29Ah | CCP2CON    | _          |                                                                  | DC2E                      | 3<1:0>        |              | CCP2M   | <3:0> |           | 00 0000              | 00 0000                         |

| 29Bh | _          | Unimpleme  | nted                                                             | 1                         |               | 1            |         |       |           | _                    | _                               |

| 29Ch | _          | Unimpleme  |                                                                  |                           |               |              |         |       |           | _                    | _                               |

| 29Dh | CCPTMRS0   | -          | EL<1:0>                                                          | C3TSE                     | EL<1:0>       | C2TSE        | L<1:0>  | C1TSE | EL<1:0>   | 0000 0000            | 0000 0000                       |

| 29Eh | CCPTMRS1   |            | L<1:0>                                                           |                           | L<1:0>        |              | L<1:0>  |       | EL<1:0>   | 0000 0000            | 0000 0000                       |

|      |            | _          |                                                                  | _                         |               |              |         |       |           |                      |                                 |

| 29Fh | CCPTMRS2   | —          | —                                                                | —                         | —             | C10TSI       | EL<1:0> | C9TSE | L<1:0>    | 0000                 |                                 |

#### DEOIO

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'. Legend: Note

1: PIC16F1526/7 only.

Unimplemented, read as '1'. 2:

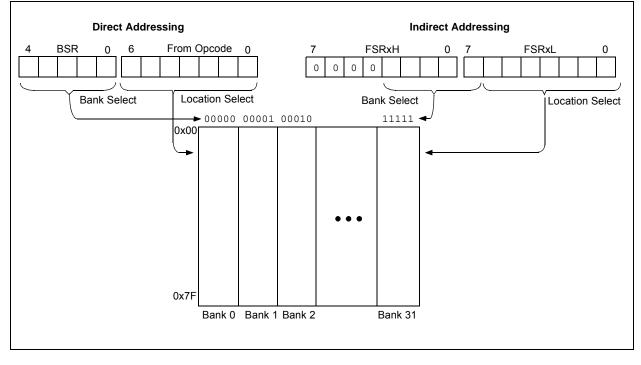

# 3.8.1 TRADITIONAL DATA MEMORY

The traditional data memory is a region from FSR address 0x000 to FSR address 0xFFF. The addresses correspond to the absolute addresses of all SFR, GPR and common registers.

# FIGURE 3-10: TRADITIONAL DATA MEMORY MAP

|                 |                 |                                     | GUNATION                               |                          |                  |                                   |       |

|-----------------|-----------------|-------------------------------------|----------------------------------------|--------------------------|------------------|-----------------------------------|-------|

|                 |                 | R/P-1                               | R/P-1                                  | R/P-1                    | R/P-1            | R/P-1                             | U-1   |

|                 |                 | LVP                                 | DEBUG                                  | LPBOR                    | BORV             | STVREN                            | —     |

|                 |                 | bit 13                              |                                        |                          |                  |                                   | bit 8 |

| U-1             | U-1             | U-1                                 | R/P-1                                  | U-1                      | U-1              | R/P-1                             | R/P-1 |

| 0-1             | 0-1             | 0-1                                 | VCAPEN <sup>(1)</sup>                  | 0-1                      | 0-1              | WRT<                              |       |

| <br>bit 7       | _               |                                     | VCAFEN                                 | _                        | _                |                                   | bit 0 |

|                 |                 |                                     |                                        |                          |                  |                                   | DILU  |

| Legend:         |                 |                                     |                                        |                          |                  |                                   |       |

| R = Readab      | le bit          | P = Programr                        | nable bit                              | U = Unimplen             | nented bit, read | d as '1'                          |       |

| '0' = Bit is cl | eared           | '1' = Bit is set                    |                                        | •                        | en blank or aft  |                                   |       |

| 0 21110 01      |                 |                                     |                                        |                          |                  |                                   |       |

| bit 13          | LVP: Low-Vol    | ltage Programr                      | ning Enable bit                        |                          |                  |                                   |       |

|                 | 1 = Low-volta   | ge programmir                       | ng enabled                             |                          |                  |                                   |       |

|                 |                 | -                                   | nust be used fo                        | or programming           | 9                |                                   |       |

| bit 12          |                 | ircuit Debugge                      |                                        |                          | F ara gaparal p  | urness I/O nins                   |       |

|                 |                 |                                     |                                        |                          |                  | urpose I/O pins<br>to the debugge | r     |

| bit 11          |                 | -Power BOR b                        |                                        |                          |                  |                                   |       |

|                 |                 | er BOR is disal                     |                                        |                          |                  |                                   |       |

|                 | 0 = Low-Powe    | er BOR is enat                      | oled                                   |                          |                  |                                   |       |

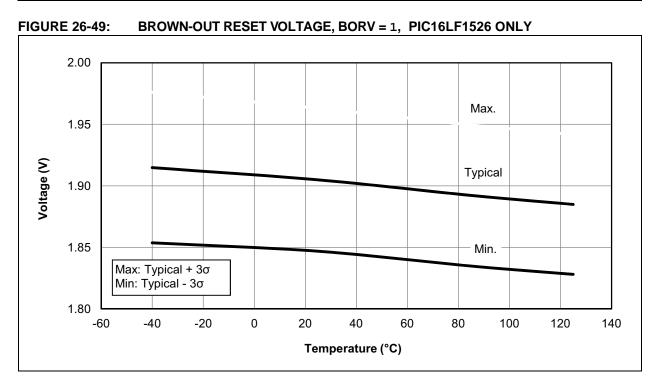

| bit 10          |                 |                                     | tage Selection                         |                          |                  |                                   |       |

|                 |                 |                                     | e (Vbor), low tri<br>e (Vbor), high tr |                          |                  |                                   |       |

| bit 9           |                 | -                                   | nderflow Reset                         |                          | eu.              |                                   |       |

| DIL 9           |                 |                                     | flow will cause                        |                          |                  |                                   |       |

|                 |                 |                                     | flow will not ca                       |                          |                  |                                   |       |

| bit 8-5         | Unimplemen      | ted: Read as '                      | 1'                                     |                          |                  |                                   |       |

| bit 4           | VCAPEN: Vol     | Itage Regulato                      | r Capacitor Ena                        | able bits <sup>(1)</sup> |                  |                                   |       |

|                 |                 | 26/7 (regulator                     |                                        |                          |                  |                                   |       |

|                 |                 | ts are ignored.<br>6/7 (regulator e | All VCAP pin fu                        | nctions are dis          | abled.           |                                   |       |

|                 |                 |                                     | s enabled on R                         | E0                       |                  |                                   |       |

|                 |                 | •                                   | ons are disabled                       |                          |                  |                                   |       |

| bit 3-2         | Unimplemen      | ted: Read as '                      | 1'                                     |                          |                  |                                   |       |

| bit 1-0         | WRT<1:0>: F     | lash Memory S                       | Self-Write Prote                       | ection bits              |                  |                                   |       |

|                 |                 |                                     | ( <u>L)F1526 only)</u> :               |                          |                  |                                   |       |

|                 |                 | ite protection o                    |                                        | NOb to 1EEEb m           | aav ha modifia   | d by PMCON co                     | ntrol |

|                 |                 |                                     |                                        |                          |                  | ed by PMCON co                    |       |

|                 |                 |                                     |                                        |                          |                  | d by PMCON co                     |       |

|                 |                 |                                     | 6(L)F1527 only                         | <u>)</u> :               |                  |                                   |       |

|                 |                 | ite protection o                    |                                        | 0h to 3EEEh m            | nav he modifier  | d by PMCON co                     | ntrol |

|                 |                 |                                     |                                        |                          |                  | fied by PMCON                     |       |

|                 |                 |                                     |                                        |                          |                  | d by PMCON co                     |       |

| Note 1: P       | PIC16F1526/7 on | nly.                                |                                        |                          |                  |                                   |       |

| <b>2:</b> S     | See Vbor parame | eter for specific                   | trip point voltag                      | ges.                     |                  |                                   |       |

|                 |                 |                                     |                                        |                          |                  |                                   |       |

# REGISTER 4-2: CONFIG2: CONFIGURATION WORD 2

| IGURE     | 7-2:         | INTERRUP      | T LATENCY         | 1                |             |                       |                  |                  |

|-----------|--------------|---------------|-------------------|------------------|-------------|-----------------------|------------------|------------------|

|           |              |               |                   |                  |             |                       |                  |                  |

| OSC1      | Q1 Q2 Q3 Q4  |               | ∩<br> Q1 Q2 Q3 Q4 |                  | 01 02 03 04 | /////<br> a1 a2 a3 a4 | ∩<br>Q1 Q2 Q3 Q4 | ∩<br>Q1 Q2 Q3 Q4 |

| CLKR      |              |               | Interru<br>during | pt Sampled<br>Q1 |             |                       |                  |                  |

| Interrupt |              |               |                   |                  |             |                       |                  |                  |

| GIE       |              |               |                   |                  |             |                       |                  |                  |

| PC        | PC-1         | РС            | PC                | +1               | 0004h       | 0005h                 | X                |                  |

| Execute   | 1 Cycle Inst | ruction at PC | Inst(PC)          | NOP              | NOP         | Inst(0004h)           |                  |                  |

| Interrupt |              |               |                   |                  |             |                       |                  |                  |

| GIE       | [            |               | PC+1/FSR          | New PC/          |             |                       | ,<br>,           |                  |

| PC        | PC-1         | PC            | ADDR              | PC+1             | 0004h       | 0005h                 |                  |                  |

| Execute-  | 2 Cycle Inst | ruction at PC | Inst(PC)          | NOP              | NOP         | Inst(0004h)           |                  |                  |

| Interrupt |              |               |                   |                  |             |                       |                  |                  |

| GIE       |              |               |                   |                  |             |                       |                  |                  |

| PC        | PC-1         | PC            | FSR ADDR          | PC+1             | PC+2        | 0004h                 | 0005h            |                  |

| Execute   | 3 Cycle Inst | ruction at PC | INST(PC)          | NOP              | NOP         | NOP                   | Inst(0004h)      | Inst(0005h)      |

| Interrupt |              |               |                   |                  |             |                       |                  |                  |

| GIE       |              |               |                   |                  |             |                       |                  |                  |

| PC        | PC-1         | РС            | FSR ADDR          | PC+1             | P           | C+2                   | 0004h            | 0005h            |

| Execute   | 3 Cycle Inst | ruction at PC | INST(PC)          | NOP              | NOP         | NOP                   | NOP              | Inst(0004h)      |

| U-0          | R/W-0/0                               | U-0                       | U-0             | R/W-0/0        | R/W-0/0          | R/W-0/0           | U-0        |

|--------------|---------------------------------------|---------------------------|-----------------|----------------|------------------|-------------------|------------|

| _            | AD2IF                                 | _                         | _               | BCL1IF         | BCL2IF           | TMR4IF            | _          |

| bit 7        |                                       |                           |                 |                |                  |                   | bit C      |

|              |                                       |                           |                 |                |                  |                   |            |

| Legend:      |                                       |                           |                 |                |                  |                   |            |

| R = Read     | able bit                              | W = Writable              | bit             | U = Unimpler   | nented bit, reac | l as '0'          |            |

| u = Bit is   | unchanged                             | x = Bit is unkr           | nown            | -n/n = Value a | at POR and BO    | R/Value at all ot | her Resets |

| '1' = Bit is | set                                   | '0' = Bit is cle          | ared            |                |                  |                   |            |

|              |                                       |                           |                 |                |                  |                   |            |

| bit 7        | Unimpleme                             | nted: Read as '           | 0'              |                |                  |                   |            |

| bit 6        |                                       | er5 Gate Interrup         | ot Flag bit     |                |                  |                   |            |

|              | 1 = Interrupt                         | is pending is not pending |                 |                |                  |                   |            |

| bit 5-4      |                                       | nted: Read as '           | 0'              |                |                  |                   |            |

| bit 3        | •                                     | SP1 Bus Collisi           |                 | -log bit       |                  |                   |            |

| DIL 3        | 1 = Interrupt                         |                           | on menupi       | lay bit        |                  |                   |            |

|              |                                       | is not pending            |                 |                |                  |                   |            |

| bit 2        | BCL2IF: MS                            | SP2 Bus Collisi           | on Interrupt F  | -lag bit       |                  |                   |            |

|              | 1 = Interrupt                         | is pending                |                 |                |                  |                   |            |

|              | •                                     | is not pending            |                 |                |                  |                   |            |

| bit 1        |                                       | ner4 to PR4 Inte          | errupt Flag bit | t              |                  |                   |            |

|              | 1 = Interrupt                         | is pending is not pending |                 |                |                  |                   |            |

| bit 0        |                                       | nted: Read as '           | 0'              |                |                  |                   |            |

| DILU         | Uninpienie                            | nieu. Reau as             | 0               |                |                  |                   |            |

|              |                                       |                           |                 |                |                  |                   |            |

| Note:        | Interrupt flag bits condition occurs, |                           |                 |                |                  |                   |            |

|              | its corresponding                     |                           |                 |                |                  |                   |            |

|              | Enable bit, GIE,                      | of the INTCON             | register.       |                |                  |                   |            |

|              | User software                         | should ensu               | ure the         |                |                  |                   |            |

# REGISTER 7-7: PIR2: PERIPHERAL INTERRUPT REQUEST REGISTER 2

appropriate interrupt flag bits are clear prior

to enabling an interrupt.

# **10.1** Independent Clock Source

The WDT derives its time base from the 31 kHz LFINTOSC internal oscillator. Time intervals in this chapter are based on a nominal interval of 1 ms. See **Section 25.0 "Electrical Specifications"** for the LFINTOSC tolerances.

# **10.2 WDT Operating Modes**

The Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Words. See Table 10-1.

#### 10.2.1 WDT IS ALWAYS ON

When the WDTE bits of Configuration Words are set to '11', the WDT is always on.

WDT protection is active during Sleep.

#### 10.2.2 WDT IS OFF IN SLEEP

When the WDTE bits of Configuration Words are set to '10', the WDT is on, except in Sleep.

WDT protection is not active during Sleep.

### 10.2.3 WDT CONTROLLED BY SOFTWARE

When the WDTE bits of Configuration Words are set to '01', the WDT is controlled by the SWDTEN bit of the WDTCON register.

WDT protection is unchanged by Sleep. See Table 10-1 for more details.

| WDTE<1:0> | SWDTEN | Device<br>Mode | WDT<br>Mode |  |  |  |

|-----------|--------|----------------|-------------|--|--|--|

| 11        | Х      | Х              | Active      |  |  |  |

| 1.0       |        | Awake          | Active      |  |  |  |

| 10        | X      | Sleep          | Disabled    |  |  |  |

| 0.1       | 1      | х              | Active      |  |  |  |

| 01        | 0      | х              | Disabled    |  |  |  |

| 00        | х      | Х              | Disabled    |  |  |  |

|           |        |                |             |  |  |  |

# TABLE 10-2: WDT CLEARING CONDITIONS

#### 10.3 Time-out Period

The WDTPS bits of the WDTCON register set the time-out period from 1 ms to 256 seconds (nominal). After a Reset, the default time-out period is 2 seconds.

# 10.4 Clearing the WDT

The WDT is cleared when any of the following conditions occur:

- Any Reset

- CLRWDT instruction is executed

- · Device enters Sleep

- · Device wakes up from Sleep

- · Oscillator fail

- WDT is disabled

- Oscillator Start-up Timer (OST) is running

See Table 10-2 for more information.

# 10.5 Operation During Sleep

When the device enters Sleep, the WDT is cleared. If the WDT is enabled during Sleep, the WDT resumes counting.

When the device exits Sleep, the WDT is cleared again. The WDT remains clear until the OST, if enabled, completes. See **Section 5.0** "Oscillator **Module (with Fail-Safe Clock Monitor)**" for more information on the OST.

When a WDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The TO and PD bits in the STATUS register are changed to indicate the event. The RWDT bit in the PCON register can also be used. See **Section 3.0** "**Memory Organization**" and The STATUS register (Register 3-1) for more information.

| WDT                          |  |  |  |  |

|------------------------------|--|--|--|--|

|                              |  |  |  |  |

| Cleared                      |  |  |  |  |

|                              |  |  |  |  |

|                              |  |  |  |  |

| Cleared until the end of OST |  |  |  |  |

| Unaffected                   |  |  |  |  |

|                              |  |  |  |  |

# 12.15 PORTG Registers

# 12.15.1 DATA REGISTER

PORTG is a 6-bit wide, bidirectional port. The corresponding data direction register is TRISG (Register 12-29). Setting a TRISG bit (= 1) will make the corresponding PORTG pin an input (i.e., disable the output driver). Clearing a TRISG bit (= 0) will make the corresponding PORTG pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). The exception is RG5, which is input only and its TRIS bit will always read as '1'. Example 12-1 shows how to initialize an I/O port.

Reading the PORTG register (Register 12-28) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATG).

# 12.15.2 DIRECTION CONTROL

The TRISG register (Register 12-29) controls the PORTG pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISG register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

# 12.15.3 ANALOG CONTROL

The ANSELG register (Register 12-31) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELG bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELG bits has no effect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

| Note: | The ANSELG bits default to the Analog        |

|-------|----------------------------------------------|

|       | mode after Reset. To use any pins as         |

|       | digital general purpose or peripheral        |

|       | inputs, the corresponding ANSEL bits         |

|       | must be initialized to '0' by user software. |

# 12.15.4 PORTG FUNCTIONS AND OUTPUT PRIORITIES

Each PORTG pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 12-16.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority.

Analog input functions, such as ADC, are not shown in the priority lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELx registers. Digital output functions may control the pin when it is in Analog mode with the priority list.

| Pin Name | Function Priority <sup>(1)</sup> |

|----------|----------------------------------|

| RG0      | CCP3<br>RG0                      |

| RG1      | CK2<br>TX2<br>RG1                |

| RG2      | DT2<br>RG2                       |

| RG3      | CCP4<br>RG3                      |

| RG4      | CCP5<br>RG4                      |

| RG5      | Input only pin                   |

### TABLE 12-16: PORTG OUTPUT PRIORITY

Note 1: Priority listed from highest to lowest.

# 13.0 INTERRUPT-ON-CHANGE

The PORTB pins can be configured to operate as Interrupt-On-Change (IOC) pins. An interrupt can be generated by detecting a signal that has either a rising edge or a falling edge. Any individual PORTB pin, or combination of PORTB pins, can be configured to generate an interrupt. The interrupt-on-change module has the following features:

- Interrupt-on-Change enable (Master Switch)

- Individual pin configuration

- · Rising and falling edge detection

- Individual pin interrupt flags

Figure 13-1 is a block diagram of the IOC module.

# 13.1 Enabling the Module

To allow individual PORTB pins to generate an interrupt, the IOCIE bit of the INTCON register must be set. If the IOCIE bit is disabled, the edge detection on the pin will still occur, but an interrupt will not be generated.

# 13.2 Individual Pin Configuration

For each PORTB pin, a rising edge detector and a falling edge detector are present. To enable a pin to detect a rising edge, the associated IOCBPx bit of the IOCBP register is set. To enable a pin to detect a falling edge, the associated IOCBNx bit of the IOCBN register is set.

A pin can be configured to detect rising and falling edges simultaneously by setting both the IOCBPx bit and the IOCBNx bit of the IOCBP and IOCBN registers, respectively.

# 13.3 Interrupt Flags

The IOCBFx bits located in the IOCBF register are status flags that correspond to the Interrupt-on-change pins of PORTB. If an expected edge is detected on an appropriately enabled pin, then the status flag for that pin will be set, and an interrupt will be generated if the IOCIE bit is set. The IOCIF bit of the INTCON register reflects the status of all IOCBFx bits.

# 13.4 Clearing Interrupt Flags

The individual status flags, (IOCBFx bits), can be cleared by resetting them to zero. If another edge is detected during this clearing operation, the associated status flag will be set at the end of the sequence, regardless of the value actually being written.

In order to ensure that no detected edge is lost while clearing flags, only AND operations masking out known changed bits should be performed. The following sequence is an example of what should be performed.

# EXAMPLE 13-1: CLEARING INTERRUPT FLAGS (PORTA EXAMPLE)

MOVLW 0xff XORWF IOCAF, W ANDWF IOCAF, F

# 13.5 Operation in Sleep

The interrupt-on-change interrupt sequence will wake the device from Sleep mode, if the IOCIE bit is set.

If an edge is detected while in Sleep mode, the IOCBF register will be updated prior to the first instruction executed out of Sleep.

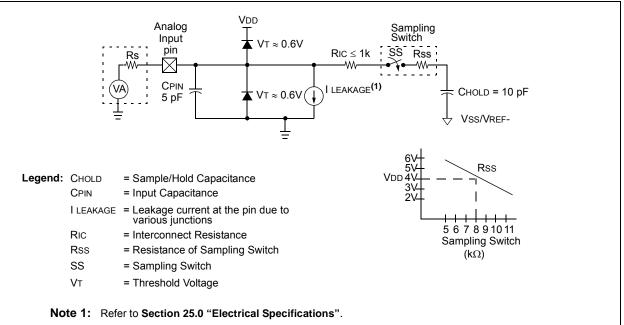

# FIGURE 16-4: ANALOG INPUT MODEL

| TABLE 20-2: | SUMMARY OF REGISTERS ASSOCIATED WITH CAPTURE |

|-------------|----------------------------------------------|

|-------------|----------------------------------------------|

| Name     | Bit 7                                                                                                      | Bit 6                                                   | Bit 5            | Bit 4     | Bit 3                  | Bit 2   | Bit 1    | Bit 0   | Register on<br>Page |

|----------|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|------------------|-----------|------------------------|---------|----------|---------|---------------------|

| APFCON   | _                                                                                                          | _                                                       | _                | _         | _                      | _       | T3CKISEL | CCP2SEL | 112                 |

| CCP1CON  | _                                                                                                          | _                                                       | DC1B             | <1:0>     |                        | 189     |          |         |                     |

| CCP2CON  | _                                                                                                          | _                                                       | DC2B             | <1:0>     |                        | 189     |          |         |                     |

| CCP3CON  | _                                                                                                          | _                                                       | DC3B             | <1:0>     |                        | 189     |          |         |                     |

| CCP4CON  | _                                                                                                          | _                                                       | DC4B             | <1:0>     |                        | 189     |          |         |                     |

| CCP5CON  | _                                                                                                          | _                                                       | DC5B             | <1:0>     |                        | 189     |          |         |                     |

| CCP6CON  | _                                                                                                          | —                                                       | DC6B             | <1:0>     |                        | 189     |          |         |                     |

| CCP7CON  | _                                                                                                          | —                                                       | DC7B             | <1:0>     |                        | 189     |          |         |                     |

| CCP8CON  | _                                                                                                          | —                                                       | DC8B             | <1:0>     |                        | 189     |          |         |                     |

| CCP9CON  | _                                                                                                          | —                                                       | DC9B             | <1:0>     |                        | 189     |          |         |                     |

| CCP10CON | _                                                                                                          | —                                                       | DC10             | 3<1:0>    |                        | 189     |          |         |                     |

| CCPR1L   | DC10B<1:0>         CCP10M<3:0>           Capture/Compare/PWM Register 1 Low Byte (LSB)         CCP10M<3:0> |                                                         |                  |           |                        |         |          | 176*    |                     |

| CCPR2L   | Capture/Compare/PWM Register 2 Low Byte (LSB)                                                              |                                                         |                  |           |                        |         |          | 176*    |                     |

| CCPR3L   | Capture/Compare/PWM Register 3 Low Byte (LSB)                                                              |                                                         |                  |           |                        |         |          | 176*    |                     |

| CCPR4L   | Capture/Com                                                                                                | pare/PWM Reg                                            | gister 4 Low By  | rte (LSB) |                        |         |          |         | 176*                |

| CCPR5L   | Capture/Compare/PWM Register 4 Low Byte (LSB) Capture/Compare/PWM Register 5 Low Byte (LSB)                |                                                         |                  |           |                        |         |          | 176*    |                     |

| CCPR6L   | Capture/Compare/PWM Register 6 Low Byte (LSB)                                                              |                                                         |                  |           |                        |         |          | 176*    |                     |

| CCPR7L   | Capture/Compare/PWM Register 7 Low Byte (LSB)                                                              |                                                         |                  |           |                        |         |          | 176*    |                     |

| CCPR8L   | Capture/Compare/PWM Register 8 Low Byte (LSB)                                                              |                                                         |                  |           |                        |         |          | 176*    |                     |

| CCPR9L   | Capture/Compare/PWM Register 9 Low Byte (LSB)                                                              |                                                         |                  |           |                        |         |          | 176*    |                     |

| CCPR10L  | Capture/Compare/PWM Register 10 Low Byte (LSB)                                                             |                                                         |                  |           |                        |         |          | 176*    |                     |

| CCPR1H   | Capture/Compare/PWM Register 1 High Byte (MSB)                                                             |                                                         |                  |           |                        |         |          | 176*    |                     |

| CCPR2H   | Capture/Compare/PWM Register 2 High Byte (MSB)                                                             |                                                         |                  |           |                        |         |          | 176*    |                     |

| CCPR3H   | Capture/Compare/PWM Register 3 High Byte (MSB)                                                             |                                                         |                  |           |                        |         |          | 176*    |                     |

| CCPR4H   | Capture/Compare/PWM Register 4 High Byte (MSB)                                                             |                                                         |                  |           |                        |         |          | 176*    |                     |

| CCPR5H   | Capture/Compare/PWM Register 5 High Byte (MSB)                                                             |                                                         |                  |           |                        |         |          | 176*    |                     |

| CCPR6H   |                                                                                                            |                                                         |                  |           |                        |         |          |         |                     |

| CCPR7H   | Capture/Compare/PWM Register 6 High Byte (MSB)                                                             |                                                         |                  |           |                        |         | 176*     |         |                     |

|          | Capture/Compare/PWM Register 7 High Byte (MSB)                                                             |                                                         |                  |           |                        |         | 176*     |         |                     |

| CCPR8H   | Capture/Compare/PWM Register 8 High Byte (MSB)                                                             |                                                         |                  |           |                        |         | 176*     |         |                     |

| CCPR9H   | Capture/Compare/PWM Register 9 High Byte (MSB)                                                             |                                                         |                  |           |                        |         | 176*     |         |                     |

| CCPR10H  |                                                                                                            |                                                         | gister 10 High I | ,         |                        |         |          |         | 176*                |

| INTCON   | GIE                                                                                                        |                                                         | TMR0IE           |           | IOCIE                  | TMR0IF  | INTF     | IOCIF   | 76                  |

| PIE1     | TMR1GIE                                                                                                    | ADIE                                                    | RC1IE            | TX1IE     | SSP1IE                 | CCP1IE  | TMR2IE   | TMR1IE  | 77                  |

| PIE2     | OSFIE                                                                                                      | TMR5GIE                                                 | TMR3GIE          | —         | BCL1IE                 | TMR10IE | TMR8IE   | CCP2IE  | 78                  |

| PIE3     | CCP6IE                                                                                                     | CCP5IE                                                  | CCP4IE           | CCP3IE    | TMR6IE                 | TMR5IE  | TMR4IE   | TMR3IE  | 79                  |

| PIE4     | CCP10IE                                                                                                    | CCP9IE                                                  | RC2IE            | TX2IE     | CCP8IE                 | CCP7IE  | BCL2IE   | SSP2IE  | 80                  |

| PIR1     | TMR1GIF                                                                                                    | ADIF                                                    | RC1IF            | TX1IF     | SSP1IF                 | CCP1IF  | TMR2IF   | TMR1IF  | 81                  |

| PIR2     | OSFIF                                                                                                      | TMR5GIF                                                 | TMR3GIF          | —         | BCL1IF                 | TMR10IF | TMR8IF   | CCP2IF  | 82                  |

| PIR3     | CCP6IF                                                                                                     | CCP5IF                                                  | CCP4IF           | CCP3IF    | TMR6IF                 | TMR5IF  | TMR4IF   | TMR3IF  | 83                  |

| PIR4     | CCP10IF                                                                                                    | CCP9IF                                                  | RC2IF            | TX2IF     | CCP8IF                 | CCP7IF  | BCL2IF   | SSP2IF  | 84                  |

| T1CON    | TMR1CS<1:0> T1CKPS<1:0>                                                                                    |                                                         |                  | SOSCEN    | T1SYNC                 | —       | TMR10N   | 168     |                     |

| T3CON    | TMR3CS<1:0> T3CKPS<1:0>                                                                                    |                                                         |                  | SOSCEN    | T3SYNC                 | —       | TMR3ON   | 168     |                     |

| T5CON    | TMR5C                                                                                                      | 1                                                       | T5CKP            |           | SOSCEN T5SYNC — TMR5ON |         |          |         | 168                 |

| T1GCON   |                                                                                                            | TMR1GE T1GPOL T1GTM T1GSPM T1GGO/DONE T1GVAL T1GSS<1:0> |                  |           |                        |         |          | 169     |                     |

| T3GCON   | TMR3GE         T3GPOL         T3GTM         T3GSPM         T3GGO/DONE         T3GVAL         T3GSS<1:0>    |                                                         |                  |           |                        |         | 169      |         |                     |

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by Capture mode. \* Page provides register information.

# 20.3.7 OPERATION IN SLEEP MODE

In Sleep mode, the TMRx register will not increment and the state of the module will not change. If the CCPx pin is driving a value, it will continue to drive that value. When the device wakes up, TMRx will continue from its previous state.

# 20.3.8 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See Section 5.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for additional details.

# 20.3.9 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

# 20.3.10 ALTERNATE PIN LOCATIONS

This module incorporates I/O pins that can be moved to other locations with the use of the alternate pin function register, APFCON. To determine which pins can be moved and what their default locations are upon a reset, see **Section 12.1 "Alternate Pin Function**" for more information.

| Name     | Bit 7                   | Bit 6                           | Bit 5                  | Bit 4  | Bit 3         | Bit 2   | Bit 1    | Bit 0   | Register<br>on Page |

|----------|-------------------------|---------------------------------|------------------------|--------|---------------|---------|----------|---------|---------------------|

| APFCON   | _                       | _                               | _                      | _      | _             | _       | T3CKISEL | CCP2SEL | 112                 |

| CCP1CON  | —                       | — DC1B<1:0>                     |                        |        | CCP1M<3:0>    |         |          |         | 189                 |

| CCP2CON  | —                       | — DC2B<1:0>                     |                        |        | CCP2M<3:0>    |         |          |         | 189                 |

| CCP3CON  | _                       | — DC3B<1:0>                     |                        |        | CCP3M<3:0>    |         |          |         | 189                 |

| CCP4CON  | —                       | _                               | — DC4B<1:0>            |        | CCP4M<3:0>    |         |          |         | 189                 |

| CCP5CON  | —                       | _                               | — DC5B<1:0>            |        | CCP5M<3:0>    |         |          |         | 189                 |

| CCP6CON  | —                       | _                               | DC6B<1:0>              |        |               | 189     |          |         |                     |

| CCP7CON  | —                       | _                               | DC7B                   | <1:0>  | CCP7M<3:0>    |         |          |         | 189                 |

| CCP8CON  | —                       | _                               | DC8B                   | <1:0>  |               | CCP8    | √<3:0>   |         | 189                 |

| CCP9CON  | —                       | _                               | DC9B                   | <1:0>  | D> CCP9M<3:0> |         |          |         | 189                 |

| CCP10CON | —                       | _                               | DC10B<1:0> CCP10M<3:0> |        |               |         | 189      |         |                     |

| INTCON   | GIE                     | PEIE                            | TMR0IE                 | INTE   | IOCIE         | TMR0IF  | INTF     | IOCIF   | 76                  |

| PIE1     | TMR1GIE                 | ADIE                            | RC1IE                  | TX1IE  | SSP1IE        | CCP1IE  | TMR2IE   | TMR1IE  | 77                  |

| PIE2     | OSFIE                   | TMR5GIE                         | TMR3GIE                | _      | BCL1IE        | TMR10IE | TMR8IE   | CCP2IE  | 78                  |

| PIE3     | CCP6IE                  | CCP5IE                          | CCP4IE                 | CCP3IE | TMR6IE        | TMR5IE  | TMR4IE   | TMR3IE  | 79                  |

| PIE4     | CCP10IE                 | CCP9IE                          | RC2IE                  | TX2IE  | CCP8IE        | CCP7IE  | BCL2IE   | SSP2IE  | 80                  |

| PIR1     | TMR1GIF                 | ADIF                            | RC1IF                  | TX1IF  | SSP1IF        | CCP1IF  | TMR2IF   | TMR1IF  | 81                  |

| PIR2     | OSFIF                   | TMR5GIF                         | TMR3GIF                | _      | BCL1IF        | TMR10IF | TMR8IF   | CCP2IF  | 82                  |

| PIR3     | CCP6IF                  | CCP5IF                          | CCP4IF                 | CCP3IF | TMR6IF        | TMR5IF  | TMR4IF   | TMR3IF  | 83                  |

| PIR4     | CCP10IF                 | CCP9IF                          | RC2IF                  | TX2IF  | CCP8IF        | CCP7IF  | BCL2IF   | SSP2IF  | 84                  |

| PR2      | Timer2 Period Register  |                                 |                        |        |               |         | 171*     |         |                     |

| PR4      | Timer4 Period Register  |                                 |                        |        |               |         | 171*     |         |                     |

| PR6      | Timer6 Period Register  |                                 |                        |        |               |         | 171*     |         |                     |

| PR8      | Timer8 Period Register  |                                 |                        |        |               |         | 171*     |         |                     |

| PR10     | Timer10 Period Register |                                 |                        |        |               |         | 171*     |         |                     |

| T2CON    | —                       | T2OUTPS<3:0> TMR2ON T2CKPS<:0>1 |                        |        |               |         | 168      |         |                     |

| T4CON    | —                       | T4OUTPS<3:0> TMR4ON T4CKPS<:0>1 |                        |        |               |         | 168      |         |                     |

| T6CON    | —                       | T6OUTPS<3:0> TMR6ON T6CKPS<:0>1 |                        |        |               | 168     |          |         |                     |

# TABLE 20-9: SUMMARY OF REGISTERS ASSOCIATED WITH STANDARD PWM

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by the PWM.

\* Page provides register information.

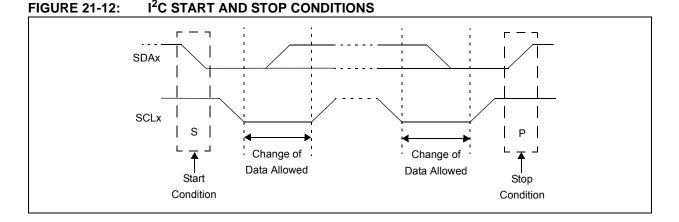

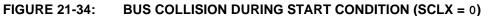

#### 21.4.5 START CONDITION

The  $I^2C$  specification defines a Start condition as a transition of SDAx from a high to a low state while SCLx line is high. A Start condition is always generated by the master and signifies the transition of the bus from an Idle to an Active state. Figure 21-12 shows wave forms for Start and Stop conditions.

A bus collision can occur on a Start condition if the module samples the SDAx line low before asserting it low. This does not conform to the I<sup>2</sup>C Specification that states no bus collision can occur on a Start.

#### 21.4.6 STOP CONDITION

A Stop condition is a transition of the SDAx line from low-to-high state while the SCLx line is high.

**Note:** At least one SCLx low time must appear before a Stop is valid, therefore, if the SDAx line goes low then high again while the SCLx line stays high, only the Start condition is detected.

### 21.4.7 RESTART CONDITION

A Restart is valid any time that a Stop would be valid. A master can issue a Restart if it wishes to hold the bus after terminating the current transfer. A Restart has the same effect on the slave that a Start would, resetting all slave logic and preparing it to clock in an address. The master may want to address the same or another slave. Figure 21-13 shows the wave form for a Restart condition.

In 10-bit Addressing Slave mode a Restart is required for the master to clock data out of the addressed slave. Once a slave has been fully addressed, matching both high and low address bytes, the master can issue a Restart and the high address byte with the  $R/\overline{W}$  bit set. The slave logic will then hold the clock and prepare to clock out data.

After a full match with  $R/\overline{W}$  clear in 10-bit mode, a prior match flag is set and maintained. Until a Stop condition, a high address with  $R/\overline{W}$  clear, or high address match fails.

#### 21.4.8 START/STOP CONDITION INTERRUPT MASKING

The SCIE and PCIE bits of the SSPxCON3 register can enable the generation of an interrupt in Slave modes that do not typically support this function. Slave modes where interrupt on Start and Stop detect are already enabled, these bits will have no effect.

# © 2011-2015 Microchip Technology Inc.

#### 21.5.4 SLAVE MODE 10-BIT ADDRESS RECEPTION

This section describes a standard sequence of events for the MSSPx module configured as an  $I^2C$  slave in 10-bit Addressing mode.

Figure 21-20 is used as a visual reference for this description.

This is a step by step process of what must be done by slave software to accomplish  $I^2C$  communication.

- 1. Bus starts Idle.

- Master sends Start condition; S bit of SSPxSTAT is set; SSPxIF is set if interrupt on Start detect is enabled.

- 3. Master sends matching high address with  $R/\overline{W}$  bit clear; UA bit of the SSPxSTAT register is set.

- 4. Slave sends ACK and SSPxIF is set.

- 5. Software clears the SSPxIF bit.

- 6. Software reads received address from SSPxBUF clearing the BF flag.

- 7. Slave loads low address into SSPxADD, releasing SCLx.

- 8. Master sends matching low address byte to the slave; UA bit is set.

**Note:** Updates to the SSPxADD register are not allowed until after the ACK sequence.

9. Slave sends ACK and SSPxIF is set.

**Note:** If the low address does not match, SSPxIF and UA are still set so that the slave software can set SSPxADD back to the high address. BF is not set because there is no match. CKP is unaffected.

- 10. Slave clears SSPxIF.

- 11. Slave reads the received matching address from SSPxBUF clearing BF.

- 12. Slave loads high address into SSPxADD.

- 13. Master clocks a data <u>byte</u> to the slave and clocks out the slaves ACK on the 9th SCLx pulse; SSPxIF is set.

- 14. If SEN bit of SSPxCON2 is set, CKP is cleared by hardware and the clock is stretched.

- 15. Slave clears SSPxIF.

- 16. Slave reads the received byte from SSPxBUF clearing BF.

- 17. If SEN is set the slave sets CKP to release the SCLx.

- 18. Steps 13-17 repeat for each received byte.

- 19. Master sends Stop to end the transmission.

#### 21.5.5 10-BIT ADDRESSING WITH ADDRESS OR DATA HOLD

Reception using 10-bit addressing with AHEN or DHEN set is the same as with 7-bit modes. The only difference is the need to update the SSPxADD register using the UA bit. All functionality, specifically when the CKP bit is cleared and SCLx line is held low are the same. Figure 21-21 can be used as a reference of a slave in 10-bit addressing with AHEN set.

Figure 21-22 shows a standard waveform for a slave transmitter in 10-bit Addressing mode.

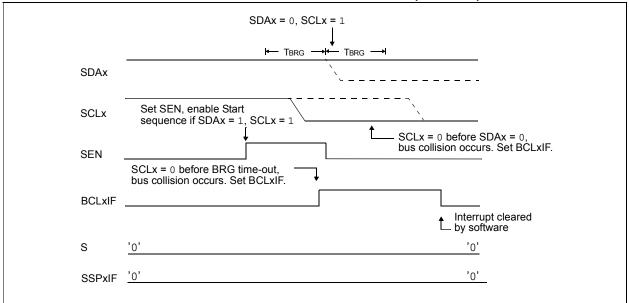

#### FIGURE 21-35: BRG RESET DUE TO SDA ARBITRATION DURING START CONDITION

# 22.4.2 AUTO-BAUD OVERFLOW

During the course of automatic baud detection, the ABDOVF bit of the BAUDxCON register will be set if the baud rate counter overflows before the fifth rising edge is detected on the RX pin. The ABDOVF bit indicates that the counter has exceeded the maximum count that can fit in the 16 bits of the SPxBRGH:SPxBRGL register pair. The overflow condition will set the RCIF flag. The counter continues to count until the fifth rising edge is detected on the RX pin. The RCIDL bit will remain false ('0') until the fifth rising edge at which time the RCIDL bit will be set. If the RCREG is read after the overflow occurs but before the fifth rising edge, then the fifth rising edge will set the RCIF again.

Terminating the auto-baud process early to clear an overflow condition will prevent proper detection of the sync character fifth rising edge. If any falling edges of the sync character have not yet occurred when the ABDEN bit is cleared then those will be falsely detected as Start bits. The following steps are recommended to clear the overflow condition:

- 1. Read RCREG to clear RCIF

- 2. If RCIDL is zero then wait for RCIF and repeat step 1.

- 3. Clear the ABDOVF bit.

# 22.4.3 AUTO-WAKE-UP ON BREAK

During Sleep mode, all clocks to the EUSART are suspended. Because of this, the Baud Rate Generator is inactive and a proper character reception cannot be performed. The Auto-Wake-up feature allows the controller to wake-up due to activity on the RXx/DTx line. This feature is available only in Asynchronous mode.

The Auto-Wake-up feature is enabled by setting the WUE bit of the BAUDxCON register. Once set, the normal receive sequence on RXx/DTx is disabled, and the EUSART remains in an Idle state, monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on the RXx/DTx line. (This coincides with the start of a Sync Break or a wake-up signal character for the LIN protocol.)

The EUSART module generates an RCxIF interrupt coincident with the wake-up event. The interrupt is generated synchronously to the Q clocks in normal CPU operating modes (Figure 22-7), and asynchronously if the device is in Sleep mode (Figure 22-8). The interrupt condition is cleared by reading the RCxREG register.

The WUE bit is automatically cleared by the low-to-high transition on the RXx line at the end of the Break. This signals to the user that the Break event is over. At this point, the EUSART module is in Idle mode waiting to receive the next character.

# 22.4.3.1 Special Considerations

#### Break Character

To avoid character errors or character fragments during a wake-up event, the wake-up character must be all zeros.

When the wake-up is enabled the function works independent of the low time on the data stream. If the WUE bit is set and a valid non-zero character is received, the low time from the Start bit to the first rising edge will be interpreted as the wake-up event. The remaining bits in the character will be received as a fragmented character and subsequent characters can result in framing or overrun errors.

Therefore, the initial character in the transmission must be all '0's. This must be 10 or more bit times, 13-bit times recommended for LIN bus, or any number of bit times for standard RS-232 devices.

#### Oscillator Startup Time

Oscillator start-up time must be considered, especially in applications using oscillators with longer start-up intervals (i.e., LP, XT or HS mode). The Sync Break (or wake-up signal) character must be of sufficient length, and be followed by a sufficient interval, to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

### WUE Bit

The wake-up event causes a receive interrupt by setting the RCxIF bit. The WUE bit is cleared by hardware by a rising edge on RXx/DTx. The interrupt condition is then cleared by software by reading the RCxREG register and discarding its contents.

To ensure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process before setting the WUE bit. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

# 25.7 Timing Parameter Symbology

The timing parameter symbols have been created with one of the following formats:

- 1. TppS2ppS

- 2. TppS

| <u>z. 1pp3</u>                        |                                       |     |                |  |  |

|---------------------------------------|---------------------------------------|-----|----------------|--|--|

| т                                     |                                       |     |                |  |  |

| F                                     | Frequency                             | Т   | Time           |  |  |

| Lowerc                                | case letters (pp) and their meanings: |     |                |  |  |

| рр                                    |                                       |     |                |  |  |

| сс                                    | CCP1                                  | OSC | OSC1           |  |  |

| ck                                    | CLKOUT                                | rd  | RD             |  |  |

| CS                                    | CS                                    | rw  | RD or WR       |  |  |

| di                                    | SDIx                                  | sc  | SCKx           |  |  |

| do                                    | SDO                                   | SS  | SS             |  |  |

| dt                                    | Data in                               | tO  | TOCKI          |  |  |

| io                                    | I/O PORT                              | t1  | T1CKI          |  |  |

| mc                                    | MCLR                                  | wr  | WR             |  |  |

| Uppercase letters and their meanings: |                                       |     |                |  |  |

| S                                     |                                       |     |                |  |  |

| F                                     | Fall                                  | Р   | Period         |  |  |

| Н                                     | High                                  | R   | Rise           |  |  |