Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                                                |

|----------------------------|----------------------------------------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                                                       |

| Core Processor             | ARM® Cortex®-M3                                                                                                |

| Core Size                  | 32-Bit Single-Core                                                                                             |

| Speed                      | 180MHz                                                                                                         |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, Microwire, QEI, SD, SPI, SSI, SSP, UART/USART, USB, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                                              |

| Number of I/O              | 142                                                                                                            |

| Program Memory Size        | -                                                                                                              |

| Program Memory Type        | ROMIess                                                                                                        |

| EEPROM Size                | -                                                                                                              |

| RAM Size                   | 200K x 8                                                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 3.6V                                                                                                    |

| Data Converters            | A/D 8x10b; D/A 1x10b                                                                                           |

| Oscillator Type            | Internal                                                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                              |

| Mounting Type              | Surface Mount                                                                                                  |

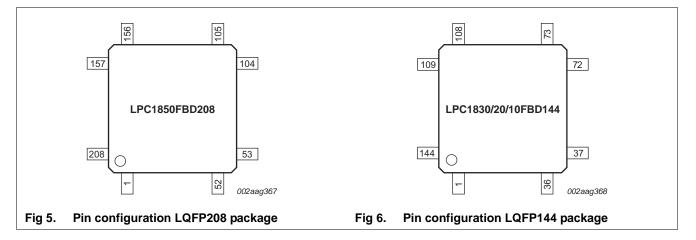

| Package / Case             | 208-LQFP                                                                                                       |

| Supplier Device Package    | 208-LQFP (28x28)                                                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc1850fbd208-551                                      |

|                            |                                                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

32-bit ARM Cortex-M3 microcontroller

### 6.2 Pin description

On the LPC1850/30/20/10, digital pins are grouped into 16 ports, named P0 to P9 and PA to PF, with up to 20 pins used per port. Each digital pin can support up to eight different digital functions, including General-Purpose I/O (GPIO), selectable through the System Configuration Unit (SCU) registers. The pin name is not indicative of the GPIO port assigned to it.

Not all functions listed in <u>Table 3</u> are available on all packages. See <u>Table 2</u> for availability of USB0, USB1, Ethernet, and LCD functions.

#### 32-bit ARM Cortex-M3 microcontroller

Table 3.

Pin description

LCD. Ethernet. USB0. and USB1 functions are not available on all parts. See Table 2.

| Symbol      | LBGA256    | TFBGA180 | TFBGA100 | LQFP208 | LQFP144 |     | Reset state<br>[1] | Type | Description                                                                                                                                                           |

|-------------|------------|----------|----------|---------|---------|-----|--------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Multiplexed | digital pi | ns       |          |         |         |     |                    |      |                                                                                                                                                                       |

| P0_0        | L3         | K3       | G2       | 47      | 32      | [2] | N; PU              | I/O  | <b>GPIO0[0]</b> — General purpose digital input/output pin.                                                                                                           |

|             |            |          |          |         |         |     |                    | I/O  | <b>SSP1_MISO</b> — Master In Slave Out for SSP1.                                                                                                                      |

|             |            |          |          |         |         |     |                    | I    | <b>ENET_RXD1</b> — Ethernet receive data 1 (RMII/MII interface).                                                                                                      |

|             |            |          |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                                |

|             |            |          |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                                |

|             |            |          |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                                |

|             |            |          |          |         |         |     |                    | I/O  | <b>I2S0_TX_WS</b> — Transmit Word Select. It is driven by the master and received by the slave. Corresponds to the signal WS in the $l^2S$ -bus specification.        |

|             |            |          |          |         |         |     |                    | I/O  | <b>I2S1_TX_WS</b> — Transmit Word Select. It is driven by the master and received by the slave. Corresponds to the signal WS in the $l^2S$ -bus specification.        |

| P0_1        | M2         | K2       | G1       | 50      | 34      | [2] | N; PU              | I/O  | GPIO0[1] — General purpose digital input/output pin.                                                                                                                  |

|             |            |          |          |         |         |     |                    | I/O  | SSP1_MOSI — Master Out Slave in for SSP1.                                                                                                                             |

|             |            |          |          |         |         |     |                    | Ι    | ENET_COL — Ethernet Collision detect (MII interface).                                                                                                                 |

|             |            |          |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                                |

|             |            |          |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                                |

|             |            |          |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                                |

|             |            |          |          |         |         |     |                    |      | <b>ENET_TX_EN</b> — Ethernet transmit enable (RMII/MII interface).                                                                                                    |

|             |            |          |          |         |         |     |                    | I/O  | <b>I2S1_TX_SDA</b> — $I^2$ S1 transmit data. It is driven by the transmitter and read by the receiver. Corresponds to the signal SD in the $I^2$ S-bus specification. |

| P1_0        | P2         | L1       | H1       | 54      | 38      | [2] | N; PU              | I/O  | GPIO0[4] — General purpose digital input/output pin.                                                                                                                  |

|             |            |          |          |         |         |     |                    | I    | CTIN_3 — SCT input 3. Capture input 1 of timer 1.                                                                                                                     |

|             |            |          |          |         |         |     |                    | I/O  | EMC_A5 — External memory address line 5.                                                                                                                              |

|             |            |          |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                                |

|             |            |          |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                                |

|             |            |          |          |         |         |     |                    | I/O  | SSP0_SSEL — Slave Select for SSP0.                                                                                                                                    |

|             |            |          |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                                |

|             |            |          |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                                |

#### 32-bit ARM Cortex-M3 microcontroller

| Symbol | LBGA256 | TFBGA180 | TFBGA100 | LQFP208 | LQFP144 |     | Reset state<br>[1] | Type | Description                                                 |

|--------|---------|----------|----------|---------|---------|-----|--------------------|------|-------------------------------------------------------------|

| P1_8   | R7      | M5       | H5       | 71      | 51      | [2] | N; PU              | I/O  | GPIO1[1] — General purpose digital input/output pin.        |

|        |         |          |          |         |         |     |                    | 0    | <b>U1_DTR</b> — Data Terminal Ready output for UART1.       |

|        |         |          |          |         |         |     |                    | 0    | <b>CTOUT_12</b> — SCT output 12. Match output 3 of timer 3. |

|        |         |          |          |         |         |     |                    | I/O  | EMC_D1 — External memory data line 1.                       |

|        |         |          |          |         |         |     |                    | -    | R — Function reserved.                                      |

|        |         |          |          |         |         |     |                    | -    | R — Function reserved.                                      |

|        |         |          |          |         |         |     |                    | -    | R — Function reserved.                                      |

|        |         |          |          |         |         |     |                    | 0    | <b>SD_VOLT0</b> — SD/MMC bus voltage select output 0.       |

| P1_9   | Τ7      | N5       | J5       | 73      | 52      | [2] | N; PU              | I/O  | GPIO1[2] — General purpose digital input/output pin.        |

|        |         |          |          |         |         |     |                    | 0    | U1_RTS — Request to Send output for UART1.                  |

|        |         |          |          |         |         |     |                    | 0    | <b>CTOUT_11</b> — SCT output 11. Match output 3 of timer 2. |

|        |         |          |          |         |         |     |                    | I/O  | EMC_D2 — External memory data line 2.                       |

|        |         |          |          |         |         |     |                    | -    | R — Function reserved.                                      |

|        |         |          |          |         |         |     |                    | -    | R — Function reserved.                                      |

|        |         |          |          |         |         |     |                    | -    | R — Function reserved.                                      |

|        |         |          |          |         |         |     |                    | I/O  | <b>SD_DAT0</b> — SD/MMC data bus line 0.                    |

| P1_10  | R8      | N6       | H6       | 75      | 53      | [2] | N; PU              | I/O  | GPIO1[3] — General purpose digital input/output pin.        |

|        |         |          |          |         |         |     |                    | I    | U1_RI — Ring Indicator input for UART1.                     |

|        |         |          |          |         |         |     |                    | 0    | <b>CTOUT_14</b> — SCT output 14. Match output 2 of timer 3. |

|        |         |          |          |         |         |     |                    | I/O  | EMC_D3 — External memory data line 3.                       |

|        |         |          |          |         |         |     |                    | -    | R — Function reserved.                                      |

|        |         |          |          |         |         |     |                    | -    | R — Function reserved.                                      |

|        |         |          |          |         |         |     |                    | -    | R — Function reserved.                                      |

|        |         |          |          |         |         |     |                    | I/O  | SD_DAT1 — SD/MMC data bus line 1.                           |

| P1_11  | Т9      | P8       | J7       | 77      | 55      | [2] | N; PU              | I/O  | GPIO1[4] — General purpose digital input/output pin.        |

|        |         |          |          |         |         |     |                    | Ι    | <b>U1_CTS</b> — Clear to Send input for UART1.              |

|        |         |          |          |         |         |     |                    | 0    | <b>CTOUT_15</b> — SCT output 15. Match output 3 of time 3.  |

|        |         |          |          |         |         |     |                    | I/O  | EMC_D4 — External memory data line 4.                       |

|        |         |          |          |         |         |     |                    | -    | R — Function reserved.                                      |

|        |         |          |          |         |         |     |                    | -    | R — Function reserved.                                      |

|        |         |          |          |         |         |     |                    | -    | R — Function reserved.                                      |

|        |         |          |          |         |         |     |                    | I/O  | SD_DAT2 — SD/MMC data bus line 2.                           |

#### Table 3. Pin description ... continued

#### 32-bit ARM Cortex-M3 microcontroller

| Symbol | LBGA256 | TFBGA180 | TFBGA100 | LQFP208 | LQFP144 |     | Reset state<br>[1] | Type | Description                                                                                                                                                                           |

|--------|---------|----------|----------|---------|---------|-----|--------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P5_6   | T13     | M11      | -        | 89      | 63      | [2] | N; PU              | I/O  | GPIO2[15] — General purpose digital input/output pin.                                                                                                                                 |

|        |         |          |          |         |         |     |                    | 0    | MCOB1 — Motor control PWM channel 1, output B.                                                                                                                                        |

|        |         |          |          |         |         |     |                    | I/O  | EMC_D10 — External memory data line 10.                                                                                                                                               |

|        |         |          |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                                                |

|        |         |          |          |         |         |     |                    | 0    | U1_TXD — Transmitter output for UART1.                                                                                                                                                |

|        |         |          |          |         |         |     |                    | 0    | T1_MAT2 — Match output 2 of timer 1.                                                                                                                                                  |

|        |         |          |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                                                |

|        |         |          |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                                                |

| P5_7   | R12     | N11      | -        | 91      | 65      | [2] | N; PU              | I/O  | <b>GPIO2[7]</b> — General purpose digital input/output pin.                                                                                                                           |

|        |         |          |          |         |         |     |                    | 0    | MCOA2 — Motor control PWM channel 2, output A.                                                                                                                                        |

|        |         |          |          |         |         |     |                    | I/O  | EMC_D11 — External memory data line 11.                                                                                                                                               |

|        |         |          |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                                                |

|        |         |          |          |         |         |     |                    | I    | U1_RXD — Receiver input for UART1.                                                                                                                                                    |

|        |         |          |          |         |         |     |                    | 0    | T1_MAT3 — Match output 3 of timer 1.                                                                                                                                                  |

|        |         |          |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                                                |

|        |         |          |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                                                |

| P6_0   | M12     | M10      | H7       | 105     | 73      | [2] | N; PU              | -    | R — Function reserved.                                                                                                                                                                |

|        |         |          |          |         |         |     |                    | 0    | I2S0_RX_MCLK — I <sup>2</sup> S receive master clock.                                                                                                                                 |

|        |         |          |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                                                |

|        |         |          |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                                                |

|        |         |          |          |         |         |     |                    | I/O  | <b>I2S0_RX_SCK</b> — Receive Clock. It is driven by the master and received by the slave. Corresponds to the signal SCK in the <i>PS-bus specification</i> .                          |

|        |         |          |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                                                |

|        |         |          |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                                                |

|        |         |          |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                                                |

| °6_1   | R15     | P14      | G5       | 107     | 74      | [2] | N; PU              | I/O  | <b>GPIO3[0]</b> — General purpose digital input/output pin.                                                                                                                           |

|        |         |          |          |         |         |     |                    | 0    | EMC_DYCS1 — SDRAM chip select 1.                                                                                                                                                      |

|        |         |          |          |         |         |     |                    | I/O  | <b>U0_UCLK</b> — Serial clock input/output for USART0 in synchronous mode.                                                                                                            |

|        |         |          |          |         |         |     |                    | I/O  | <b>I2S0_RX_WS</b> — Receive Word Select. It is driven by the master and received by the slave. Corresponds to the signal WS in the <i>I</i> <sup>2</sup> <i>S</i> -bus specification. |

|        |         |          |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                                                |

|        |         |          |          |         |         |     |                    | I    | T2_CAP0 — Capture input 2 of timer 2.                                                                                                                                                 |

|        |         |          |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                                                |

|        |         |          |          |         |         |     |                    | -    | <b>R</b> — Function reserved.                                                                                                                                                         |

|        |         |          |          |         |         |     |                    |      |                                                                                                                                                                                       |

#### Table 3. Pin description ... continued

#### 32-bit ARM Cortex-M3 microcontroller

| Symbol | LBGA256 | TFBGA180 | TFBGA100 | LQFP208 | LQFP144 |     | Reset state<br>[1] | Type | Description                                                                                                                                               |

|--------|---------|----------|----------|---------|---------|-----|--------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| P7_4   | C8      | C6       | -        | 189     | 132     | [5] | N; PU              | I/O  | GPIO3[12] — General purpose digital input/output pin.                                                                                                     |

|        |         |          |          |         |         |     |                    | 0    | <b>CTOUT_13</b> — SCT output 13. Match output 3 of timer 3.                                                                                               |

|        |         |          |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                    |

|        |         |          |          |         |         |     |                    | 0    | LCD_VD16 — LCD data.                                                                                                                                      |

|        |         |          |          |         |         |     |                    | 0    | LCD_VD4 — LCD data.                                                                                                                                       |

|        |         |          |          |         |         |     |                    | 0    | TRACEDATA[0] — Trace data, bit 0.                                                                                                                         |

|        |         |          |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                    |

|        |         |          |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                    |

|        |         |          |          |         |         |     |                    | AI   | <b>ADC0_4</b> — ADC0 and ADC1, input channel 4.<br>Configure the pin as GPIO input and use the ADC function select register in the SCU to select the ADC. |

| P7_5   | A7      | A7       | -        | 191     | 133     | [5] | N; PU              | I/O  | GPIO3[13] — General purpose digital input/output pin.                                                                                                     |

|        |         |          |          |         |         |     |                    | 0    | <b>CTOUT_12</b> — SCT output 12. Match output 3 of timer 3.                                                                                               |

|        |         |          |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                    |

|        |         |          |          |         |         |     |                    | 0    | LCD_VD8 — LCD data.                                                                                                                                       |

|        |         |          |          |         |         |     |                    | 0    | LCD_VD23 — LCD data.                                                                                                                                      |

|        |         |          |          |         |         |     |                    | 0    | TRACEDATA[1] — Trace data, bit 1.                                                                                                                         |

|        |         |          |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                    |

|        |         |          |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                    |

|        |         |          |          |         |         |     |                    | AI   | <b>ADC0_3</b> — ADC0 and ADC1, input channel 3.<br>Configure the pin as GPIO input and use the ADC function select register in the SCU to select the ADC. |

| P7_6   | C7      | F5       | -        | 194     | 134     | [2] | N; PU              | I/O  | GPIO3[14] — General purpose digital input/output pin.                                                                                                     |

|        |         |          |          |         |         |     |                    | 0    | CTOUT_11 — SCT output 1. Match output 3 of timer 2                                                                                                        |

|        |         |          |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                    |

|        |         |          |          |         |         |     |                    | 0    | <b>LCD_LP</b> — Line synchronization pulse (STN).<br>Horizontal synchronization pulse (TFT).                                                              |

|        |         |          |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                    |

|        |         |          |          |         |         |     |                    | 0    | TRACEDATA[2] — Trace data, bit 2.                                                                                                                         |

|        |         |          |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                    |

|        |         |          |          |         |         |     |                    | -    | R — Function reserved.                                                                                                                                    |

#### Table 3. Pin description ... continued

ilahla a Can Table 2 *all na*

#### 32-bit ARM Cortex-M3 microcontroller

| Symbol | LBGA256 | TFBGA180 | TFBGA100 | LQFP208 | LQFP144 |     | Reset state<br>[1] | Type     | Description                                                                                                                                                                           |

|--------|---------|----------|----------|---------|---------|-----|--------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PF_6   | E7      | -        | -        | 192     | -       | [5] | N; PU              | -        | R — Function reserved.                                                                                                                                                                |

|        |         |          |          |         |         |     |                    | I/O      | <b>U3_DIR</b> — RS-485/EIA-485 output enable/direction control for USART3.                                                                                                            |

|        |         |          |          |         |         |     |                    | I/O      | SSP1_MISO — Master In Slave Out for SSP1.                                                                                                                                             |

|        |         |          |          |         |         |     |                    | 0        | TRACEDATA[1] — Trace data, bit 1.                                                                                                                                                     |

|        |         |          |          |         |         |     |                    | I/O      | GPIO7[20] — General purpose digital input/output pin.                                                                                                                                 |

|        |         |          |          |         |         |     |                    | -        | R — Function reserved.                                                                                                                                                                |

|        |         |          |          |         |         |     |                    | -        | R — Function reserved.                                                                                                                                                                |

|        |         |          |          |         |         |     |                    | I/O      | <b>I2S1_TX_SDA</b> — $I^2$ S1 transmit data. It is driven by the transmitter and read by the receiver. Corresponds to the signal SD in the <i>I</i> <sup>2</sup> S-bus specification. |

|        |         |          |          |         |         |     |                    | AI       | <b>ADC1_3</b> — ADC1 and ADC0, input channel 3.<br>Configure the pin as GPIO input and use the ADC function select register in the SCU to select the ADC.                             |

| PF_7   | B7      | -        | -        | 193     | -       | [5] | N; PU              | -        | R — Function reserved.                                                                                                                                                                |

|        |         |          |          |         |         |     |                    | I/O      | U3_BAUD — Baud pin USART3.                                                                                                                                                            |

|        |         |          |          |         |         |     |                    | I/O      | SSP1_MOSI — Master Out Slave in for SSP1.                                                                                                                                             |

|        |         |          |          |         |         |     |                    | 0        | TRACEDATA[2] — Trace data, bit 2.                                                                                                                                                     |

|        |         |          |          |         |         |     |                    | I/O      | GPIO7[21] — General purpose digital input/output pin.                                                                                                                                 |

|        |         |          |          |         |         |     |                    | -        | R — Function reserved.                                                                                                                                                                |

|        |         |          |          |         |         |     |                    | -        | R — Function reserved.                                                                                                                                                                |

|        |         |          |          |         |         |     |                    | I/O      | <b>I2S1_TX_WS</b> — Transmit Word Select. It is driven by the master and received by the slave. Corresponds to the signal WS in the $l^2S$ -bus specification.                        |

|        |         |          |          |         |         |     |                    | Al/<br>O | <b>ADC1_7</b> — ADC1 and ADC0, input channel 7 or band gap output. Configure the pin as GPIO input and use the ADC function select register in the SCU to select the ADC.             |

| PF_8   | E6      | -        | -        | -       | -       | [5] | N; PU              | -        | R — Function reserved.                                                                                                                                                                |

|        |         |          |          |         |         |     |                    | I/O      | <b>U0_UCLK</b> — Serial clock input/output for USART0 in synchronous mode.                                                                                                            |

|        |         |          |          |         |         |     |                    | I        | CTIN_2 — SCT input 2. Capture input 2 of timer 0.                                                                                                                                     |

|        |         |          |          |         |         |     |                    | 0        | TRACEDATA[3] — Trace data, bit 3.                                                                                                                                                     |

|        |         |          |          |         |         |     |                    | I/O      | GPIO7[22] — General purpose digital input/output pin.                                                                                                                                 |

|        |         |          |          |         |         |     |                    | -        | R — Function reserved.                                                                                                                                                                |

|        |         |          |          |         |         |     |                    | -        | R — Function reserved.                                                                                                                                                                |

|        |         |          |          |         |         |     |                    | -        | R — Function reserved.                                                                                                                                                                |

|        |         |          |          |         |         |     |                    | AI       | <b>ADC0_2</b> — ADC0 and ADC1, input channel 2.<br>Configure the pin as GPIO input and use the ADC function select register in the SCU to select the ADC.                             |

#### Table 3. Pin description ...continued

LCD, Ethernet, USB0, and USB1 functions are not available on all parts. See Table 2.

#### 32-bit ARM Cortex-M3 microcontroller

| Symbol        | LBGA256 | TFBGA180 | TFBGA100 | LQFP208 | LQFP144 | Reset state<br>[ <u>1]</u> | Type | Description    |  |

|---------------|---------|----------|----------|---------|---------|----------------------------|------|----------------|--|

| VSSA          | B2      | A3       | C2       | 196     | 135     | -                          | -    | Analog ground. |  |

| Not connected |         |          |          |         |         |                            |      |                |  |

| -             | B9      | B8       | -        | -       | -       | -                          | -    | n.c.           |  |

#### Table 3. Pin description ...continued

LCD, Ethernet, USB0, and USB1 functions are not available on all parts. See Table 2.

[1] N = neutral, input buffer disabled; no extra VDDIO current consumption if the input is driven midway between supplies; set the EZI bit in the SFS register to enable the input buffer; I = input; OL = output driving LOW; OH = output driving HIGH; AI/O = analog input/output; IA = inactive; PU = pull-up enabled (weak pull-up resistor pulls up pin to VDDIO; F = floating. Reset state reflects the pin state at reset without boot code operation.

[2] 5 V tolerant pad with 15 ns glitch filter (5 V tolerant if VDDIO present; if VDDIO not present, do not exceed 3.6 V); provides digital I/O functions with TTL levels and hysteresis; normal drive strength (see Figure 45).

- [3] 5 V tolerant pad with 15 ns glitch filter (5 V tolerant if VDDIO present; if VDDIO not present, do not exceed 3.6 V); provides digital I/O functions with TTL levels, and hysteresis; high drive strength (see Figure 45).

- [4] 5 V tolerant pad with 15 ns glitch filter (5 V tolerant if VDDIO present; if VDDIO not present, do not exceed 3.6 V); provides high-speed digital I/O functions with TTL levels and hysteresis (see Figure 45).

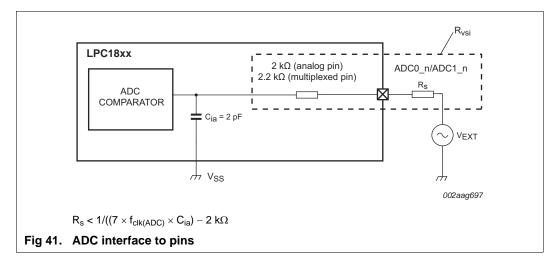

- [5] 5 V tolerant pad providing digital I/O functions (with TTL levels and hysteresis) and analog input or output (5 V tolerant if VDDIO present; if VDDIO not present, do not exceed 3.6 V). When configured as an ADC input or DAC output, the pin is not 5 V tolerant and the digital section of the pad must be disabled by setting the pin to an input function and disabling the pull-up resistor through the pin's SFSP register.

- [6] 5 V tolerant transparent analog pad.

- [7] For maximum load  $C_L = 6.5 \,\mu$ F and maximum pull-down resistance  $R_{pd} = 80 \,k\Omega$ , the VBUS signal takes about 2 s to fall from VBUS = 5 V to VBUS = 0.2 V when it is no longer driven.

- [8] Transparent analog pad. Not 5 V tolerant.

- [9] Pad provides USB functions. It is designed in accordance with the USB specification, revision 2.0 (Full-speed and Low-speed mode only).

- [10] Open-drain 5 V tolerant digital I/O pad, compatible with I<sup>2</sup>C-bus Fast Mode Plus specification. This pad requires an external pull-up to provide output functionality. When power is switched off, this pin connected to the I<sup>2</sup>C-bus is floating and does not disturb the I<sup>2</sup>C lines.

- [11] 5 V tolerant pad with 20 ns glitch filter; provides digital I/O functions with open-drain output with weak pull-up resistor and hysteresis (see Figure 46).

- [12] If not pinned out, VPP is internally connected to VDDIO.

- [13] On the TFBGA100 and LQFP208 packages, VSS is internally connected to VSSIO.

32-bit ARM Cortex-M3 microcontroller

### 7.11 One-Time Programmable (OTP) memory

The OTP provides 32 bit of memory for general-purpose use.

### 7.12 General-Purpose I/O (GPIO)

The LPC1850/30/20/10 provides eight GPIO ports with up to 31 GPIO pins each.

Device pins that are not connected to a specific peripheral function are controlled by the GPIO registers. Pins may be dynamically configured as inputs or outputs. Separate registers allow setting or clearing any number of outputs simultaneously. The value of the output register may be read back as well as the current state of the port pins.

All GPIO pins default to inputs with pull-up resistors enabled and input buffer disabled on reset. The input buffer must be turned on in the system control block SFS register before the GPIO input can be read.

#### 7.12.1 Features

- Accelerated GPIO functions:

- GPIO registers are located on the AHB so that the fastest possible I/O timing can be achieved.

- Mask registers allow treating sets of port bits as a group, leaving other bits unchanged.

- All GPIO registers are byte and half-word addressable.

- Entire port value can be written in one instruction.

- Bit-level set and clear registers allow a single instruction set or clear of any number of bits in one port.

- Direction control of individual bits.

- Up to eight GPIO pins can be selected from all GPIO pins to create an edge- or level-sensitive GPIO interrupt request.

- Two GPIO group interrupts can be triggered by any pin or pins in each port.

### 7.13 AHB peripherals

#### 7.13.1 State Configurable Timer (SCT) subsystem

The SCT allows a wide variety of timing, counting, output modulation, and input capture operations. The inputs and outputs of the SCT are shared with the capture and match inputs/outputs of the 32-bit general-purpose counter/timers.

The SCT can be configured as two 16-bit counters or a unified 32-bit counter. In the two-counter case, in addition to the counter value the following operational elements are independent for each half:

- State variable

- Limit, halt, stop, and start conditions

- Values of Match/Capture registers, plus reload or capture control values

In the two-counter case, the following operational elements are global to the SCT, but the last three can use match conditions from either counter:

#### 32-bit ARM Cortex-M3 microcontroller

• MultiMedia Cards (MMC version 4.4)

#### 7.13.5 External Memory Controller (EMC)

The LPC1850/30/20/10 EMC is a Memory Controller peripheral offering support for asynchronous static memory devices such as RAM, ROM, and NOR flash. In addition, it can be used as an interface with off-chip memory-mapped devices and peripherals.

#### 7.13.5.1 Features

- Dynamic memory interface support including single data rate SDRAM.

- Asynchronous static memory device support including RAM, ROM, and NOR flash, with or without asynchronous page mode.

- Low transaction latency.

- Read and write buffers to reduce latency and to improve performance.

- 8/16/32 data and 24 address lines-wide static memory support. On parts LPC1820/10 only 8/16 data lines are available.

- 16-bit and 32-bit wide chip select SDRAM memory support.

- Static memory features include:

- Asynchronous page mode read

- Programmable Wait States

- Bus turnaround delay

- Output enable and write enable delays

- Extended wait

- Four chip selects for synchronous memory and four chip selects for static memory devices.

- Power-saving modes dynamically control EMC\_CKEOUT and EMC\_CLK signals to SDRAMs.

- Dynamic memory self-refresh mode controlled by software.

- Controller supports 2048 (A0 to A10), 4096 (A0 to A11), and 8192 (A0 to A12) row address synchronous memory parts. Those are typically 512 MB, 256 MB, and 128 MB parts, with 4, 8, 16, or 32 data bits per device.

- · Separate reset domains allow auto-refresh through a chip reset if desired.

Note: Synchronous static memory devices (synchronous burst mode) are not supported.

#### 7.13.6 High-speed USB Host/Device/OTG interface (USB0)

Remark: USB0 is available on parts LPC1850/30/20 (see Table 2).

The USB OTG module allows the part to connect directly to a USB host such as a PC (in device mode) or to a USB device in host mode.

#### 7.13.6.1 Features

- On-chip UTMI+ compliant high-speed transceiver (PHY).

- Complies with Universal Serial Bus specification 2.0.

- Complies with USB On-The-Go supplement.

- Complies with Enhanced Host Controller Interface Specification.

LPC1850 30 20 10

© NXP B.V. 2013. All rights reserved.

#### 32-bit ARM Cortex-M3 microcontroller

- Supports single and dual-panel monochrome Super Twisted Nematic (STN) displays with 4-bit or 8-bit interfaces.

- Supports single and dual-panel color STN displays.

- Supports Thin Film Transistor (TFT) color displays.

- Programmable display resolution including, but not limited to:  $320 \times 200$ ,  $320 \times 240$ ,  $640 \times 200$ ,  $640 \times 240$ ,  $640 \times 480$ ,  $800 \times 600$ , and  $1024 \times 768$ .

- Hardware cursor support for single-panel displays.

- 15 gray-level monochrome, 3375 color STN, and 32 K color palettized TFT support.

- 1, 2, or 4 bits-per-pixel (bpp) palettized displays for monochrome STN.

- 1, 2, 4, or 8 bpp palettized color displays for color STN and TFT.

- 16 bpp true-color non-palettized for color STN and TFT.

- 24 bpp true-color non-palettized for color TFT.

- Programmable timing for different display panels.

- 256 entry, 16-bit palette RAM, arranged as a 128 × 32-bit RAM.

- Frame, line, and pixel clock signals.

- AC bias signal for STN, data enable signal for TFT panels.

- Supports little and big-endian, and Windows CE data formats.

- LCD panel clock can be generated from the peripheral clock, or from a clock input pin.

#### 7.13.9 Ethernet

Remark: Ethernet is available on parts LPC1850/30 (see Table 2).

#### 7.13.9.1 Features

- 10/100 Mbit/s

- DMA support

- Power management remote wake-up frame and magic packet detection

- Supports both full-duplex and half-duplex operation

- Supports CSMA/CD Protocol for half-duplex operation.

- Supports IEEE 802.3x flow control for full-duplex operation.

- Optional forwarding of received pause control frames to the user application in full-duplex operation.

- Back-pressure support for half-duplex operation.

- Automatic transmission of zero-quanta pause frame on deassertion of flow control input in full-duplex operation.

- Support for IEEE 1588 time stamping and IEEE 1588 advanced time stamping (IEEE 1588-2008 v2).

#### 32-bit ARM Cortex-M3 microcontroller

• Smart card mode conforming to ISO7816 specification

#### 7.14.3 SSP serial I/O controller

Remark: The LPC1850/30/20/10 contain two SSP controllers.

The SSP controller can operate on a SPI, 4-wire SSI, or Microwire bus. It can interact with multiple masters and slaves on the bus. Only a single master and a single slave can communicate on the bus during a given data transfer. The SSP supports full-duplex transfers, with frames of 4 bit to 16 bit of data flowing from the master to the slave and from the slave to the master. In practice, often only one of these data flows carries meaningful data.

#### 7.14.3.1 Features

- Maximum SSP speed in full-duplex mode of 25 Mbit/s; for transmit only 50 Mbit/s (master) and 15 Mbit/s (slave).

- Compatible with Motorola SPI, 4-wire Texas Instruments SSI, and National Semiconductor Microwire buses

- Synchronous serial communication

- Master or slave operation

- Eight-frame FIFOs for both transmit and receive

- 4-bit to 16-bit frame

- Connected to the GPDMA

#### 7.14.4 I<sup>2</sup>C-bus interface

**Remark:** The LPC1850/30/20/10 contain two I<sup>2</sup>C-bus interfaces.

The I<sup>2</sup>C-bus is bidirectional for inter-IC control using only two wires: a Serial Clock line (SCL) and a Serial Data line (SDA). Each device is recognized by a unique address and can operate as either a receiver-only device (for example an LCD driver) or a transmitter with the capability to both receive and send information (such as memory). Transmitters and/or receivers can operate in either master or slave mode, depending on whether the chip has to initiate a data transfer or is only addressed. The I<sup>2</sup>C is a multi-master bus and can be controlled by more than one bus master connected to it.

#### 7.14.4.1 Features

- I<sup>2</sup>C0 is a standard I<sup>2</sup>C-compliant bus interface with open-drain pins. I<sup>2</sup>C0 also supports Fast mode plus with bit rates up to 1 Mbit/s.

- I<sup>2</sup>C1 uses standard I/O pins with bit rates of up to 400 kbit/s (Fast I<sup>2</sup>C-bus).

- Easy to configure as master, slave, or master/slave.

- Programmable clocks allow versatile rate control.

- Bidirectional data transfer between masters and slaves.

- Multi-master bus (no central master).

- Arbitration between simultaneously transmitting masters without corruption of serial data on the bus.

- Serial clock synchronization allows devices with different bit rates to communicate via one serial bus.

LPC1850 30 20 10

#### 32-bit ARM Cortex-M3 microcontroller

### 7.18.3 Clock Generation Unit (CGU)

The Clock Generator Unit (CGU) generates several base clocks. The base clocks can be unrelated in frequency and phase and can have different clock sources within the CGU. One CGU base clock is routed to the CLKOUT pins. The base clock that generates the CPU clock is referred to as CCLK.

Multiple branch clocks are derived from each base clock. The branch clocks offer flexible control for power-management purposes. All branch clocks are outputs of one of two Clock Control Units (CCUs) and can be controlled independently. Branch clocks derived from the same base clock are synchronous in frequency and phase.

#### 7.18.4 Internal RC oscillator (IRC)

The IRC is used as the clock source for the WWDT and/or as the clock that drives the PLLs and the CPU. The nominal IRC frequency is 12 MHz. The IRC is trimmed to 1 % accuracy over the entire voltage and temperature range.

Upon power-up or any chip reset, the LPC1850/30/20/10 use the IRC as the clock source. The boot loader then configures the PLL1 to provide a 96 MHz clock for the core and the PLL0USB or PLL0AUDIO as needed if an external boot source is selected.

### 7.18.5 PLL0USB (for USB0)

PLL0 is a dedicated PLL for the USB0 High-speed controller.

PLL0 accepts an input clock frequency from an external oscillator in the range of 14 kHz to 25 MHz. The input frequency is multiplied up to a high frequency with a Current Controlled Oscillator (CCO). The CCO operates in the range of 4.3 MHz to 550 MHz.

### 7.18.6 PLL0AUDIO (for audio)

The audio PLL PLL0AUDIO is a general-purpose PLL with a small step size. This PLL accepts an input clock frequency derived from an external oscillator or internal IRC. The input frequency is multiplied up to a high frequency with a Current Controlled Oscillator (CCO). A sigma-delta converter modulates the PLL divider ratios to obtain the desired output frequency. The output frequency can be set as a multiple of the sampling frequency  $f_s$  to  $32 \times f_s$ ,  $64 \times f_s$ ,  $128 \times f_s$ ,  $256 \times f_s$ ,  $384 \times f_s$ ,  $512 \times f_s$  and the sampling frequency  $f_s$  can range from 16 kHz to 192 kHz (16, 22.05, 32, 44.1, 48, 96,192) kHz. Many other frequencies are possible as well using the integrated fractional divider.

#### 7.18.7 System PLL1

The PLL1 accepts an input clock frequency from an external oscillator in the range of 10 MHz to 25 MHz. The input frequency is multiplied up to a high frequency with a Current Controlled Oscillator (CCO). The multiplier can be an integer value from 1 to 32. The CCO operates in the range of 156 MHz to 320 MHz. This range is possible through an additional divider in the loop to keep the CCO within its frequency range while the PLL is providing the desired output frequency. The output divider can be set to divide by 2, 4, 8, or 16 to produce the output clock. Since the minimum output divider value is 2, it is insured that the PLL output has a 50 % duty cycle. The PLL is turned off and bypassed following a chip reset. After reset, software can enable the PLL. The program must configure and activate the PLL, wait for the PLL to lock, and then connect to the PLL as a clock source. The PLL settling time is 100  $\mu$ s.

#### 32-bit ARM Cortex-M3 microcontroller

| Symbol           | Parameter                                  | Conditions                                                     |             | Min | Typ <u>[1]</u> | Max | Unit |

|------------------|--------------------------------------------|----------------------------------------------------------------|-------------|-----|----------------|-----|------|

| I/O pins - higł  | n drive strength: standard driv            | ve mode                                                        |             |     |                |     |      |

| I <sub>OH</sub>  | HIGH-level output<br>current               | $V_{OH} = V_{DD(IO)} - 0.4 \ V$                                |             | -4  | -              | -   | mA   |

| I <sub>OL</sub>  | LOW-level output<br>current                | $V_{OL} = 0.4 V$                                               |             | 4   | -              | -   | mA   |

| I <sub>OHS</sub> | HIGH-level short-circuit<br>output current | drive HIGH; connected to ground                                | [11]        | -   | -              | 32  | mA   |

| OLS              | LOW-level short-circuit<br>output current  | drive LOW; connected to $V_{DD(IO)}$                           | [11]        | -   | -              | 32  | mA   |

| /O pins - higł   | n drive strength: medium driv              | e mode                                                         |             |     |                |     |      |

| l <sub>он</sub>  | HIGH-level output<br>current               | $V_{OH} = V_{DD(IO)} - 0.4 \text{ V}$                          |             | -8  | -              | -   | mA   |

| lol              | LOW-level output<br>current                | V <sub>OL</sub> = 0.4 V                                        |             | 8   | -              | -   | mA   |

| I <sub>OHS</sub> | HIGH-level short-circuit<br>output current | drive HIGH; connected to ground                                | <u>[11]</u> | -   | -              | 65  | mA   |

| I <sub>OLS</sub> | LOW-level short-circuit<br>output current  | drive LOW; connected to $V_{DD(IO)}$                           | [11]        | -   | -              | 63  | mA   |

| l/O pins - higł  | n drive strength: high drive m             | ode                                                            |             |     |                |     |      |

| lон              | HIGH-level output<br>current               | $V_{OH} = V_{DD(IO)} - 0.4 \text{ V}$                          |             | -14 | -              | -   | mA   |

| I <sub>OL</sub>  | LOW-level output<br>current                | $V_{OL} = 0.4 V$                                               |             | 14  | -              | -   | mA   |

| I <sub>OHS</sub> | HIGH-level short-circuit<br>output current | drive HIGH; connected to ground                                | [11]        | -   | -              | 113 | mA   |

| I <sub>OLS</sub> | LOW-level short-circuit<br>output current  | drive LOW; connected to $V_{DD(IO)}$                           | [11]        | -   | -              | 110 | mA   |

| I/O pins - higł  | n drive strength: ultra-high dr            | ive mode                                                       |             |     |                |     |      |

| l <sub>он</sub>  | HIGH-level output<br>current               | $V_{OH} = V_{DD(IO)} - 0.4 \text{ V}$                          |             | -20 | -              | -   | mA   |

| lol              | LOW-level output<br>current                | $V_{OL} = 0.4 V$                                               |             | 20  | -              | -   | mA   |

| онѕ              | HIGH-level short-circuit<br>output current | drive HIGH; connected to ground                                | <u>[11]</u> | -   | -              | 165 | mA   |

| OLS              | LOW-level short-circuit<br>output current  | drive LOW; connected to $V_{DD(IO)}$                           | [11]        | -   | -              | 156 | mA   |

| /O pins - hig    | h-speed                                    |                                                                |             |     |                |     |      |

| Cı               | input capacitance                          |                                                                |             | -   | -              | 2   | pF   |

| LL               | LOW-level leakage<br>current               | V <sub>I</sub> = 0 V; on-chip pull-up<br>resistor disabled     |             | -   | 3              | -   | nA   |

| LH               | HIGH-level leakage current                 | $V_I = V_{DD(IO)}$ ; on-chip<br>pull-down resistor<br>disabled |             | -   | 3              | -   | nA   |

|                  |                                            | V <sub>I</sub> = 5 V                                           |             |     | 1              |     | nA   |

#### Table 10. Static characteristics ... continued

#### 32-bit ARM Cortex-M3 microcontroller

#### 32-bit ARM Cortex-M3 microcontroller

#### 11.10 External memory interface

#### Table 23. Dynamic characteristics: Static asynchronous external memory interface

$C_L = 22 \text{ pF}$  for EMC\_Dn  $C_L = 20 \text{ pF}$  for all others;  $T_{amb} = -40 \text{ °C}$  to 85 °C; 2.2 V  $\leq V_{DD(REG)(3V3)} \leq 3.6 \text{ V}$ ; 2.7 V  $\leq V_{DD(IO)} \leq 3.6 \text{ V}$ ; values guaranteed by design. Timing parameters are given for single memory access cycles. In a normal read operation, the EMC changes the address while CS is asserted resulting in multiple memory accesses.

| Symbol                | Parameter <sup>[1]</sup>                                      | Conditions |            | Min                                                                                                      | Тур | Max                                                                                                | Unit |

|-----------------------|---------------------------------------------------------------|------------|------------|----------------------------------------------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------|------|

| Read cycl             | e parameters                                                  |            |            |                                                                                                          |     |                                                                                                    |      |

| t <sub>CSLAV</sub>    | CS LOW to address valid time                                  |            |            | -3.1                                                                                                     | -   | 1.6                                                                                                | ns   |

| t <sub>CSLOEL</sub>   | $\overline{\text{CS}}$ LOW to $\overline{\text{OE}}$ LOW time |            | [2]        | $\begin{array}{l} -0.6 + {\rm T_{cy(clk)}} \times \\ {\rm WAITOEN} \end{array}$                          | -   | 1.3 + T <sub>cy(clk)</sub> ×<br>WAITOEN                                                            | ns   |

| t <sub>CSLBLSL</sub>  | CS LOW to BLS LOW time                                        | PB = 1     |            | -0.7                                                                                                     | -   | 1.8                                                                                                | ns   |

| t <sub>oeloeh</sub>   | OE LOW to OE HIGH time                                        |            | [2]        | $\begin{array}{l} -0.6 + \\ (WAITRD - \\ WAITOEN + 1) \times \\ T_{cy(clk)} \end{array}$                 | -   | $\begin{array}{c} -0.4 \ + \\ (WAITRD \ - \\ WAITOEN \ + \ 1) \ \times \\ T_{cy(clk)} \end{array}$ | ns   |

| t <sub>am</sub>       | memory access time                                            |            |            | -                                                                                                        | -   | –16 +<br>(WAITRD –<br>WAITOEN +1) ×<br>T <sub>cy(clk)</sub>                                        | ns   |

| t <sub>h(D)</sub>     | data input hold time                                          |            |            | -16                                                                                                      | -   | -                                                                                                  | ns   |

| t <sub>CSHBLSH</sub>  | CS HIGH to BLS HIGH time                                      | PB = 1     |            | -0.4                                                                                                     | -   | 1.9                                                                                                | ns   |

| t <sub>CSHOEH</sub>   | CS HIGH to OE HIGH time                                       |            |            | -0.4                                                                                                     | -   | 1.4                                                                                                | ns   |

| t <sub>OEHANV</sub>   | OE HIGH to address invalid                                    | PB = 1     |            | -2.0                                                                                                     | -   | 2.6                                                                                                | ns   |

| t <sub>CSHEOR</sub>   | CS HIGH to end of read time                                   |            | [3]        | -2.0                                                                                                     | -   | 0                                                                                                  | ns   |

| t <sub>CSLSOR</sub>   | CS LOW to start of read time                                  |            | [4]        | 0                                                                                                        | -   | 1.8                                                                                                | ns   |

| Write cycl            | le parameters                                                 |            |            |                                                                                                          |     |                                                                                                    |      |

| t <sub>CSLAV</sub>    | CS LOW to address valid time                                  |            |            | -3.1                                                                                                     | -   | 1.6                                                                                                | ns   |

| t <sub>CSLDV</sub>    | CS LOW to data valid time                                     |            |            | -3.1                                                                                                     | -   | 1.5                                                                                                | ns   |

| t <sub>CSLWEL</sub>   | $\overline{\text{CS}}$ LOW to $\overline{\text{WE}}$ LOW time | PB = 1     |            | -1.5                                                                                                     | -   | 0.2                                                                                                | ns   |

| t <sub>CSLBLSL</sub>  | CS LOW to BLS LOW time                                        | PB = 1     |            | -0.7                                                                                                     | -   | 1.8                                                                                                | ns   |

| t <sub>WELWEH</sub>   | WE LOW to WE HIGH time                                        | PB = 1     |            | $\begin{array}{c} -0.6 + \\ (WAITWR - \\ WAITWEN + 1) \times \\ T_{cy(clk)} \end{array}$                 | -   | $\begin{array}{c} -0.4 \ + \\ (WAITWR \ - \\ WAITWEN \ + \ 1) \times \\ T_{cy(clk)} \end{array}$   | ns   |

| t <sub>WEHDNV</sub>   | WE HIGH to data invalid time                                  | PB = 1     | [2]        | $-0.9 + T_{cy(clk)}$                                                                                     | -   | $2.3 + T_{cy(clk)}$                                                                                | ns   |

| t <sub>WEHEOW</sub>   | WE HIGH to end of write time                                  | PB = 1     | [2]<br>[5] | -0.4 + T <sub>cy(clk)</sub>                                                                              | -   | -0.3 + T <sub>cy(clk)</sub>                                                                        | ns   |

| t <sub>CSLBLSL</sub>  | CS LOW to BLS LOW                                             | PB = 0     |            | -0.7                                                                                                     | -   | 1.8                                                                                                | ns   |

| t <sub>BLSLBLSH</sub> | BLS LOW to BLS HIGH time                                      | PB = 0     | [2]        | $\begin{array}{l} -0.9 \mbox{ +} \\ (WAITWR - \\ WAITWEN \mbox{ + 1}) \times \\ T_{cy(clk)} \end{array}$ | -   | $\begin{array}{c} -0.1 \ + \\ (WAITWR \ - \\ WAITWEN \ + \ 1) \times \\ T_{cy(clk)} \end{array}$   | ns   |

#### 32-bit ARM Cortex-M3 microcontroller

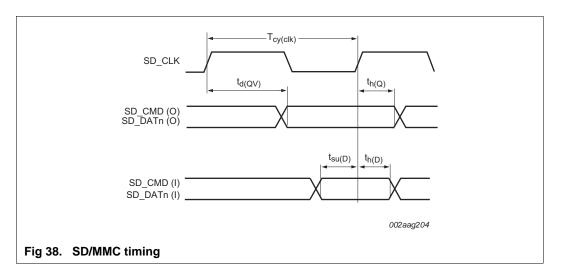

#### 11.13 SD/MMC

#### Table 29. Dynamic characteristics: SD/MMC

$T_{amb} = -40$  °C to 85 °C, 2.2 V  $\leq V_{DD(REG)(3V3)} \leq 3.6$  V; 2.7 V  $\leq V_{DD(IO)} \leq 3.6$  V,  $C_L = 20$  pF. Simulated values.

| Symbol             | Parameter                       | Conditions                            | Min | Мах | Unit |

|--------------------|---------------------------------|---------------------------------------|-----|-----|------|

| f <sub>clk</sub>   | clock frequency                 | on pin SD_CLK; data transfer mode     | 40  | -   | MHz  |

| t <sub>su(D)</sub> | data input set-up time          | on pins SD_CMD, SD_DATn as<br>inputs  | 16  | -   | ns   |

| t <sub>h(D)</sub>  | data input hold time            | on pins SD_CMD, SD_DATn as<br>inputs  | -2  |     | ns   |

| $t_{d(QV)}$        | data output valid delay<br>time | on pins SD_CMD, SD_DATn as<br>outputs |     | 12  | ns   |

| t <sub>h(Q)</sub>  | data output hold time           | on pins SD_CMD, SD_DATn as<br>outputs | 0.3 | -   | ns   |

### 11.14 LCD

#### Table 30. Dynamic characteristics: LCD

$T_{amb} = -40$  °C to 85 °C; 2.2 V  $\leq V_{DD(REG)(3V3)} \leq 3.6$  V; 2.7 V  $\leq V_{DD(IO)} \leq 3.6$  V; C<sub>L</sub> = 20 pF. Simulated values.

| Symbol             | Parameter                    | Conditions      | Min | Тур | Max | Unit |

|--------------------|------------------------------|-----------------|-----|-----|-----|------|

| f <sub>clk</sub>   | clock frequency              | on pin LCD_DCLK | -   | 50  | -   | MHz  |

| t <sub>d(QV)</sub> | data output valid delay time |                 |     | -   | 17  | ns   |

| t <sub>h(Q)</sub>  | data output hold time        |                 | 8.5 | -   |     | ns   |

#### 32-bit ARM Cortex-M3 microcontroller

#### Table 33. DAC characteristics

$V_{DDA(3V3)}$  over specified ranges;  $T_{amb} = -40$  °C to +85 °C; unless otherwise specified

| Symbol              | Parameter                    | Conditions                                                              |            | Min | Тур  | Мах | Unit |

|---------------------|------------------------------|-------------------------------------------------------------------------|------------|-----|------|-----|------|

| E <sub>D</sub>      | differential linearity error | $2.7~V \leq V_{DDA(3V3)} \leq 3.6~V$                                    | <u>[1]</u> | -   | ±0.8 | -   | LSB  |

|                     |                              | $2.2 \text{ V} \le V_{DDA(3V3)} < 2.7 \text{ V}$                        |            | -   | ±1.0 | -   | LSB  |

| E <sub>L(adj)</sub> | integral non-linearity       | code = 0 to 975                                                         | [1]        | -   | ±1.0 | -   | LSB  |

|                     |                              | $2.7~\text{V} \leq \text{V}_{\text{DDA}(3\text{V3})} \leq 3.6~\text{V}$ |            |     |      |     |      |

|                     |                              | $2.2~\text{V} \leq \text{V}_{\text{DDA}(3\text{V3})} < 2.7~\text{V}$    |            | -   | ±1.5 | -   | LSB  |

| E <sub>O</sub>      | offset error                 | $2.7~\text{V} \leq \text{V}_{\text{DDA}(3\text{V3})} \leq 3.6~\text{V}$ | <u>[1]</u> | -   | ±0.8 | -   | LSB  |

|                     |                              | $2.2 \text{ V} \le \text{V}_{\text{DDA}(3\text{V}3)}$ < 2.7 V           |            | -   | ±1.0 | -   | LSB  |

| E <sub>G</sub>      | gain error                   | $2.7~\text{V} \leq \text{V}_{\text{DDA}(3\text{V3})} \leq 3.6~\text{V}$ | <u>[1]</u> | -   | ±0.3 | -   | %    |

|                     |                              | $2.2 \text{ V} \le \text{V}_{\text{DDA}(3\text{V}3)}$ < 2.7 V           |            | -   | ±1.0 | -   | %    |

| CL                  | load capacitance             |                                                                         |            | -   | -    | 200 | pF   |

| RL                  | load resistance              |                                                                         |            | 1   | -    | -   | kΩ   |

| t <sub>s</sub>      | settling time                |                                                                         | [1]        |     | 0.4  |     | μS   |

[1] In the DAC CR register, bit BIAS = 0 (see the *LPC18xx user manual*).

[2] Settling time is calculated within 1/2 LSB of the final value.

32-bit ARM Cortex-M3 microcontroller

| External<br>pin   | TFT 12 bit (4:4:4<br>mode) |                  | TFT 16 bit (5:6:5 mode) |                  | TFT 16 bit (1:5:5:5 mode) |                  | TFT 24 bit          |                  |

|-------------------|----------------------------|------------------|-------------------------|------------------|---------------------------|------------------|---------------------|------------------|