Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                |

|---------------------------|--------------------------------------------------------------------------------|

| Product Status            | Obsolete                                                                       |

| Core Processor            | PIC                                                                            |

| Core Size                 | 16-Bit                                                                         |

| Speed                     | 32MHz                                                                          |

| onnectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| eripherals                | Brown-out Detect/Reset, DMA, LVD, POR, PWM, WDT                                |

| lumber of I/O             | 21                                                                             |

| rogram Memory Size        | 128KB (43K x 24)                                                               |

| rogram Memory Type        | FLASH                                                                          |

| EPROM Size                | -                                                                              |

| AM Size                   | 8K x 8                                                                         |

| oltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| ata Converters            | A/D 10x10b/12b                                                                 |

| scillator Type            | Internal                                                                       |

| perating Temperature      | -40°C ~ 125°C (TA)                                                             |

| ounting Type              | Surface Mount                                                                  |

| ackage / Case             | 28-SOIC (0.295", 7.50mm Width)                                                 |

| upplier Device Package    | 28-SOIC                                                                        |

| urchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128ga202-e-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.3 Arithmetic Logic Unit (ALU)

The PIC24F ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU may affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array, or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

The PIC24F CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit divisor division.

## 3.3.1 MULTIPLIER

The ALU contains a high-speed, 17-bit x 17-bit multiplier. It supports unsigned, signed or mixed sign operation in several multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- · 16-bit unsigned x 16-bit signed

- · 8-bit unsigned x 8-bit unsigned

#### 3.3.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 1. 32-bit signed/16-bit signed divide

- 2. 32-bit unsigned/16-bit unsigned divide

- 3. 16-bit signed/16-bit signed divide

- 4. 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. The 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn), and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

#### 3.3.3 MULTI-BIT SHIFT SUPPORT

The PIC24F ALU supports both single bit and single-cycle, multi-bit arithmetic and logic shifts. Multi-bit shifts are implemented using a shifter block, capable of performing up to a 15-bit arithmetic right shift, or up to a 15-bit left shift, in a single cycle. All multi-bit shift instructions only support Register Direct Addressing for both the operand source and result destination.

A full summary of instructions that use the shift operation is provided in Table 3-2.

| TABLE 3-2: INSTRUCTIONS THAT USE THE SINGLE BIT AND MULTI-BIT SHIFT OPERATION |

|-------------------------------------------------------------------------------|

|-------------------------------------------------------------------------------|

| Instruction | Description                                                 |

|-------------|-------------------------------------------------------------|

| ASR         | Arithmetic Shift Right Source register by one or more bits. |

| SL          | Shift Left Source register by one or more bits.             |

| LSR         | Logical Shift Right Source register by one or more bits.    |

## 4.0 MEMORY ORGANIZATION

As Harvard architecture devices, PIC24F microcontrollers feature separate program and data memory spaces and buses. This architecture also allows direct access of program memory from the Data Space (DS) during code execution.

## 4.1 Program Memory Space

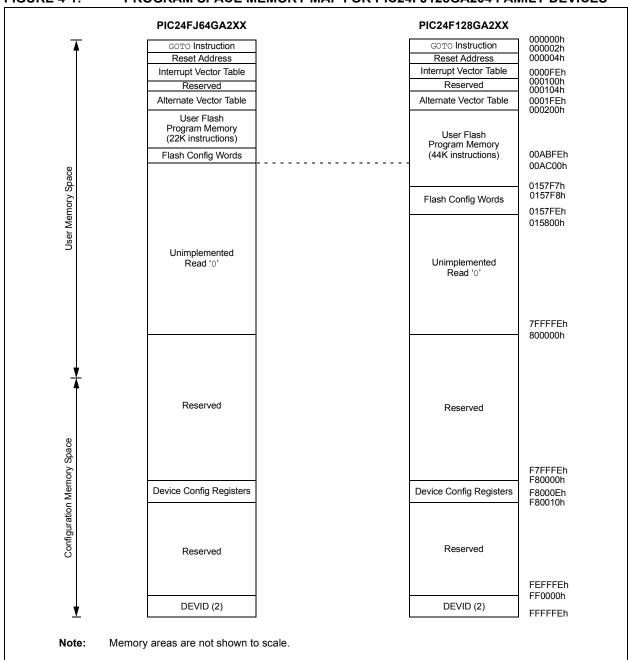

The program address memory space of the PIC24FJ128GA204 family devices is 4M instructions. The space is addressable by a 24-bit value derived

from either the 23-bit Program Counter (PC) during program execution, or from table operation or Data Space remapping, as described in **Section 4.3 "Interfacing Program and Data Memory Spaces"**.

User access to the program memory space is restricted to the lower half of the address range (000000h to 7FFFFFh). The exception is the use of  ${\tt TBLRD/TBLWT}$  operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space.

Memory maps for the PIC24FJ128GA204 family of devices are shown in Figure 4-1.

FIGURE 4-1: PROGRAM SPACE MEMORY MAP FOR PIC24FJ128GA204 FAMILY DEVICES

## TABLE 4-23: REAL-TIME CLOCK AND CALENDAR (RTCC) REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12  | Bit 11  | Bit 10   | Bit 9         | Bit 8       | Bit 7      | Bit 6     | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|------|--------|--------|---------|---------|---------|----------|---------------|-------------|------------|-----------|-------|-------|-------|-------|-------|-------|---------------|

| ALRMVAL      | 011E |        |        |         |         |         | Alarm Va | alue Register | Window Bas  | ed on ALR  | MPTR<1:0  | >     |       |       |       |       |       | xxxx          |

| ALCFGRPT     | 0120 | ALRMEN | CHIME  | AMASK3  | AMASK2  | AMASK1  | AMASK0   | ALRMPTR1      | ALRMPTR0    | ARPT7      | ARPT6     | ARPT5 | ARPT4 | ARPT3 | ARPT2 | ARPT1 | ARPT0 | 0000          |

| RTCVAL       | 0122 |        |        |         |         |         | RTCC \   | /alue Registe | r Window Ba | sed on RT0 | CPTR<1:0> | •     |       |       |       |       |       | xxxx          |

| RCFGCAL      | 0124 | RTCEN  | -      | RTCWREN | RTCSYNC | HALFSEC | RTCOE    | RTCPTR1       | RTCPTR0     | CAL7       | CAL6      | CAL5  | CAL4  | CAL3  | CAL2  | CAL1  | CAL0  | Note 1        |

| RTCPWC       | 0126 | PWCEN  | PWCPOL | PWCPRE  | PWSPRE  | RTCLK1  | RTCLK0   | RTCOUT1       | RTCOUT0     | _          | _         | _     | _     | _     | _     | _     | _     | Note 1        |

**Legend:** — = unimplemented, read as '0'; x = unknown value on Reset. Reset values are shown in hexadecimal.

Note 1: The status of the RCFGCAL and RTCPWC registers on POR is '0000' and on other Resets, it is unchanged.

## TABLE 4-24: DATA SIGNAL MODULATOR (DSM) REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|--------|--------|-------|-------|-------|-------|---------------|

| MDCON        | 02FA | MDEN   | -      | MDSIDL | _      | _      | 1      | -     | -     | _      | MDOE  | MDSLR  | MDOPOL | _     | _     | _     | MDBIT | 0020          |

| MDSRC        | 02FC | _      | _      | _      | -      | _      | _      | _     | _     | SODIS  | _     | _      | _      | MS3   | MS2   | MS1   | MS0   | 0000          |

| MDCAR        | 02FE | CHODIS | CHPOL  | CHSYNC | _      | CH3    | CH2    | CH1   | CH0   | CLODIS | CLPOL | CLSYNC | _      | CL3   | CL2   | CL1   | CL0   | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## **TABLE 4-25: COMPARATOR REGISTER MAP**

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8   | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|------|--------|--------|--------|--------|--------|--------|---------|---------|--------|--------|-------|-------|-------|-------|-------|-------|---------------|

| CMSTAT       | 0242 | CMIDL  | _      | _      | _      | _      | C3EVT  | C2EVT   | C1EVT   | _      | _      | _     | _     | _     | C3OUT | C2OUT | C1OUT | 0000          |

| CVRCON       | 0244 | _      | _      | _      | _      | _      | CVREFP | CVREFM1 | CVREFM0 | CVREN  | CVROE  | CVRSS | CVR4  | CVR3  | CVR2  | CVR1  | CVR0  | 0000          |

| CM1CON       | 0246 | CON    | COE    | CPOL   | _      | _      | _      | CEVT    | COUT    | EVPOL1 | EVPOL0 | _     | CREF  | _     | _     | CCH1  | CCH0  | 0000          |

| CM2CON       | 0248 | CON    | COE    | CPOL   | _      | _      | _      | CEVT    | COUT    | EVPOL1 | EVPOL0 | _     | CREF  | _     | _     | CCH1  | CCH0  | 0000          |

| CM3CON       | 024A | CON    | COE    | CPOL   | _      | _      | _      | CEVT    | COUT    | EVPOL1 | EVPOL0 | _     | CREF  | _     | _     | CCH1  | CCH0  | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# © 2013-2015 Microchip Technology Inc.

## TABLE 4-29: DEEP SLEEP REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8     | Bit 7       | Bit 6    | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1 | Bit 0   | All<br>Resets |

|--------------|------|--------|--------|--------|--------|--------|--------|---------|-----------|-------------|----------|-------|-------|--------|--------|-------|---------|---------------|

| DSCON        | 010E | DSEN   | _      | _      |        | 1      | -      | -       | _         | _           | _        | _     | _     | _      | r      | DSBOR | RELEASE | 0000(1)       |

| DSWAKE       | 0110 | _      | _      | _      | _      | -      | _      | _       | DSINT0    | DSFLT       | _        | _     | DSWDT | DSRTCC | DSMCLR | _     | _       | 0000(1)       |

| DSGPR0       | 0112 |        |        |        |        |        |        | Deep Sl | eep Semap | hore Data ( | Register |       |       |        |        |       |         | 0000(1)       |

| DSGPR1       | 0114 |        |        |        |        |        |        | Deep Sl | eep Semap | hore Data 1 | Register |       |       |        |        |       |         | 0000(1)       |

**Legend:** — = unimplemented, read as '0'; r = reserved. Reset values are shown in hexadecimal.

Note 1: These registers are only reset on a VDD POR event.

## TABLE 4-30: CRYPTOGRAPHIC ENGINE REGISTER MAP

| File<br>Name | Addr | Bit 15                                        | Bit 14                                                 | Bit 13   | Bit 12   | Bit 11   | Bit 10   | Bit 9    | Bit 8         | Bit 7         | Bit 6        | Bit 5   | Bit 4   | Bit 3   | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|--------------|------|-----------------------------------------------|--------------------------------------------------------|----------|----------|----------|----------|----------|---------------|---------------|--------------|---------|---------|---------|----------|----------|----------|---------------|

| CRYCONL      | 01A4 | CRYON                                         | _                                                      | CRYSIDL  | ROLLIE   | DONEIE   | FREEIE   | -        | CRYGO         | OPMOD3        | OPMOD2       | OPMOD1  | OPMOD0  | CPHRSEL | CPHRMOD2 | CPHRMOD1 | CPHRMOD0 | 0000          |

| CRYCONH      | 01A6 | -                                             | CTRSIZE6                                               | CTRSIZE5 | CTRSIZE4 | CTRSIZE3 | CTRSIZE2 | CTRSIZE1 | CTRSIZE0      | SKEYSEL       | KEYMOD1      | KEYMOD0 | -       | KEYSRC3 | KEYSRC2  | KEYSRC1  | KEYSRC0  | 0000          |

| CRYSTAT      | 01A8 | _                                             | _                                                      | -        | -        | -        | -        | _        | _             | CRYBSY        | TXTABSY      | CRYABRT | ROLLOVR | _       | MODFAIL  | KEYFAIL  | PGMFAIL  | 0000          |

| CRYOTP       | 01AC | _                                             | _                                                      | -        | -        | -        | -        | _        | _             | PGMTST        | OTPIE        | CRYREAD | KEYPG3  | KEYPG2  | KEYPG1   | KEYPG0   | CRYWR    | 0020          |

| CRYTXTA      | 01B0 |                                               |                                                        |          |          |          |          | Crypt    | tographic Tex | kt Register A | (128 bits wi | de)     |         |         |          |          |          | xxxx          |

| CRYKEY       | 01C0 |                                               | Cryptographic Key Register (256 bits wide, write-only) |          |          |          |          |          |               |               | xxxx         |         |         |         |          |          |          |               |

| CRYTXTB      | 01E0 |                                               | Cryptographic Text Register B (128 bits wide)          |          |          |          |          |          |               |               | xxxx         |         |         |         |          |          |          |               |

| CRYTXTC      | 01F0 | Cryptographic Text Register C (128 bits wide) |                                                        |          |          |          |          |          |               | xxxx          |              |         |         |         |          |          |          |               |

PIC24FJ128GA204 FAMILY

**Legend:** — = unimplemented, read as '0'; x = unknown value on Reset. Reset values are shown in hexadecimal.

## **TABLE 4-31: NVM REGISTER MAP**

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4    | Bit 3       | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|----------|-------------|--------|--------|--------|---------------|

| NVMCON       | 0760 | WR     | WREN   | WRERR  | _      | -      | _      | _     | -     | -     | ERASE | -     | _        | NVMOP3      | NVMOP2 | NVMOP1 | NVMOP0 | 0000(1)       |

| NVMKEY       | 0766 | _      | _      | _      | _      | _      | _      | _     | _     |       |       | 1     | NVMKEY R | egister<7:0 | >      |        |        | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The Reset value shown is for POR only. The value on other Reset states is dependent on the state of memory write or erase operations at the time of Reset.

If a MCLR Reset event occurs during Deep Sleep, the DSGPRx, DSCON and DSWAKE registers will remain valid, and the RELEASE bit will remain set. The state of the SOSC will also be retained. The I/O pins, however, will be reset to their MCLR Reset state. Since RELEASE is still set, changes to the SOSCEN bit (OSCCON<1>) cannot take effect until the RELEASE bit is cleared.

In all other Deep Sleep wake-up cases, application firmware must clear the RELEASE bit in order to reconfigure the I/O pins.

## 10.4.5 DEEP SLEEP WDT

To enable the DSWDT in Deep Sleep mode, program the Configuration bit, DSWDTEN (CW4<7>). The device WDT need not be enabled for the DSWDT to function. Entry into Deep Sleep modes automatically resets the DSWDT.

The DSWDT clock source is selected by the DSWDTOSC Configuration bit (CW4<5>). The postscaler options are programmed by the DSWDTPS<4:0> Configuration bits (CW4<4:0>). The minimum time-out period that can be achieved is 1 ms and the maximum is 25.7 days. For more information on the CW4 Configuration register and DSWDT configuration options, refer to Section 29.0 "Special Features".

# 10.4.5.1 Switching Clocks in Deep Sleep Mode

Both the RTCC and the DSWDT may run from either SOSC or the LPRC clock source. This allows both the RTCC and DSWDT to run without requiring both the LPRC and SOSC to be enabled together, reducing power consumption.

Running the RTCC from LPRC will result in a loss of accuracy in the RTCC of approximately 5 to 10%. If a more accurate RTCC is required, it must be run from the SOSC clock source. The RTCC clock source is selected with the RTCLK<1:0> bits (RTCPWC<11:10>).

Under certain circumstances, it is possible for the DSWDT clock source to be off when entering Deep Sleep mode. In this case, the clock source is turned on automatically (if DSWDT is enabled), without the need for software intervention. However, this can cause a delay in the start of the DSWDT counters. In order to avoid this delay when using SOSC as a clock source, the application can activate SOSC prior to entering Deep Sleep mode.

## 10.4.6 CHECKING AND CLEARING THE STATUS OF DEEP SLEEP

Upon entry into Deep Sleep mode, the status bit, DPSLP (RCON<10>), becomes set and must be cleared by the software.

On power-up, the software should read this status bit to determine if the Reset was due to an exit from Deep Sleep mode and clear the bit if it is set. Of the four possible combinations of DPSLP and POR bit states, the following three cases can be considered:

- Both the DPSLP and POR bits are cleared. In this case, the Reset was due to some event other than a Deep Sleep mode exit.

- The DPSLP bit is clear, but the POR bit is set; this is a normal Power-on Reset.

- Both the DPSLP and POR bits are set. This

means that Deep Sleep mode was entered, the

device was powered down and Deep Sleep mode

was exited.

## 10.4.7 POWER-ON RESETS (PORs)

VDD voltage is monitored to produce PORs. Since exiting from Deep Sleep mode functionally looks like a POR, the technique described in **Section 10.4.6** "Checking and Clearing the Status of Deep Sleep" should be used to distinguish between Deep Sleep and a true POR event. When a true POR occurs, the entire device, including all Deep Sleep logic (Deep Sleep registers, RTCC, DSWDT, etc.) is reset.

## 10.5 VBAT Mode

This mode represents the lowest power state that the microcontroller can achieve and still resume operation. VBAT mode is automatically triggered when the microcontroller's main power supply on VDD fails. When this happens, the microcontroller's on-chip power switch connects to a backup power source, such as a battery, supplied to the VBAT pin. This maintains a few key systems at an extremely low-power draw until VDD is restored.

The power supplied on VBAT only runs two systems: the RTCC and the Deep Sleep Semaphore registers (DSGPR0 and DSGPR1). To maintain these systems during a sudden loss of VDD, it is essential to connect a power source, other than VDD or AVDD, to the VBAT pin.

When the RTCC is enabled, it continues to operate with the same clock source (SOSC or LPRC) that was selected prior to entering VBAT mode. There is no provision to switch to a lower power clock source after the mode switch.

Since the loss of VDD is usually an unforeseen event, it is recommended that the contents of the Deep Sleep Semaphore registers be loaded with the data to be retained at an early point in code execution.

## 10.5.1 VBAT MODE WITH NO RTCC

By disabling RTCC operation during VBAT mode, power consumption is reduced to the lowest of all power-saving modes. In this mode, only the Deep Sleep Semaphore registers are maintained.

## REGISTER 11-18: RPINR27: PERIPHERAL PIN SELECT INPUT REGISTER 27

| U-0    | U-0 | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   |

|--------|-----|---------|---------|---------|---------|---------|---------|

| _      | _   | U4CTSR5 | U4CTSR4 | U4CTSR3 | U4CTSR2 | U4CTSR1 | U4CTSR0 |

| bit 15 |     |         |         |         |         |         | bit 8   |

| U-0   | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| _     | _   | U4RXR5 | U4RXR4 | U4RXR3 | U4RXR2 | U4RXR1 | U4RXR0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13-8 **U4CTSR<5:0>:** Assign UART4 Clear-to-Send Input (U4CTS) to Corresponding RPn or RPIn Pin bits

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 U4RXR<5:0>: Assign UART4 Receive Input (U4RX) to Corresponding RPn or RPIn Pin bits

## REGISTER 11-19: RPINR28: PERIPHERAL PIN SELECT INPUT REGISTER 28

| U-0    | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| _      | _   | SCK3R5 | SCK3R4 | SCK3R3 | SCK3R2 | SCK3R1 | SCK3R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| _     | _   | SDI3R5 | SDI3R4 | SDI3R3 | SDI3R2 | SDI3R1 | SDI3R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13-8 SCK3R<5:0>: Assign SPI3 Clock Input (SCK3IN) to Corresponding RPn or RPIn Pin bits

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 SDI3R<5:0>: Assign SPI3 Data Input (SDI3) to Corresponding RPn or RPIn Pin bits

T2CK (T4CK) TCY TCKPS<1:0> **TMRCK** 2 SOSC Input Prescaler LPRC Input Gate 1, 8, 64, 256 Sync TECS<1:0> TGATE<sup>(2)</sup> **TGATE** TCS<sup>(2)</sup> D Q Set T3IF (T5IF) Q 0 PR2 PR3 (PR5) (PR4) Equal Comparator A/D Event Trigger(3) MSB LSB TMR3 TMR2 Sync (TMR4) Reset (TMR5) Read TMR2 (TMR4)(1) Write TMR2 (TMR4)(1) 16 16 TMR3HLD (TMR5HLD) Data Bus<15:0> ◀ The 32-Bit Timer Configuration bit, T32, must be set for 32-bit timer/counter operation. All control bits are Note 1: respective to the T2CON and T4CON registers. The timer clock input must be assigned to an available RPn/RPIn pin before use. See Section 11.4 "Peripheral Pin Select (PPS)" for more information. 3: The A/D Event Trigger is available only on Timer2/3 in 32-bit mode and Timer3 in 16-bit mode.

**FIGURE 13-1:** TIMER2/3 AND TIMER4/5 (32-BIT) BLOCK DIAGRAM

#### REGISTER 14-1: ICxCON1: INPUT CAPTURE x CONTROL REGISTER 1

| U-0    | U-0 | R/W-0  | R/W-0   | R/W-0   | R/W-0   | U-0 | U-0   |

|--------|-----|--------|---------|---------|---------|-----|-------|

| _      | _   | ICSIDL | ICTSEL2 | ICTSEL1 | ICTSEL0 | _   | _     |

| bit 15 |     |        |         |         |         |     | bit 8 |

| U-0   | R/W-0 | R/W-0 | R-0, HSC | R-0, HSC | R/W-0               | R/W-0               | R/W-0               |

|-------|-------|-------|----------|----------|---------------------|---------------------|---------------------|

| _     | ICI1  | ICI0  | ICOV     | ICBNE    | ICM2 <sup>(1)</sup> | ICM1 <sup>(1)</sup> | ICM0 <sup>(1)</sup> |

| bit 7 |       |       |          |          |                     |                     | bit 0               |

Legend:HSC = Hardware Settable/Clearable bitR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13 ICSIDL: Input Capture x Module Stop in Idle Control bit

1 = Input capture module halts in CPU Idle mode

0 = Input capture module continues to operate in CPU Idle mode

bit 12-10 ICTSEL<2:0>: Input Capture x Timer Select bits

111 = System clock (Fosc/2)

110 = Reserved

101 = Reserved

100 = Timer1

011 = Timer5

010 = Timer4

001 = Timer2

000 = Timer3

bit 9-7 **Unimplemented:** Read as '0'

bit 6-5 ICI<1:0>: Select Number of Captures per Interrupt bits

11 = Interrupt on every fourth capture event

10 = Interrupt on every third capture event

01 = Interrupt on every second capture event

00 = Interrupt on every capture event

bit 4 **ICOV:** Input Capture x Overflow Status Flag bit (read-only)

1 = Input capture overflow has occurred

0 = No input capture overflow has occurred

bit 3 **ICBNE:** Input Capture x Buffer Empty Status bit (read-only)

1 = Input capture buffer is not empty, at least one more capture value can be read

0 = Input capture buffer is empty

bit 2-0 ICM<2:0>: Input Capture x Mode Select bits<sup>(1)</sup>

111 = Interrupt mode: Input capture functions as an interrupt pin only when the device is in Sleep or Idle mode (rising edge detect only, all other control bits are not applicable)

110 = Unused (module is disabled)

101 = Prescaler Capture mode: Capture on every 16<sup>th</sup> rising edge

100 = Prescaler Capture mode: Capture on every 4<sup>th</sup> rising edge

011 = Simple Capture mode: Capture on every rising edge

010 = Simple Capture mode: Capture on every falling edge

001 = Edge Detect Capture mode: Capture on every edge (rising and falling); ICI<1:0> bits do not control interrupt generation for this mode

000 = Input capture module is turned off

Note 1: The ICx input must also be configured to an available RPn/RPIn pin. For more information, see Section 11.4 "Peripheral Pin Select (PPS)".

#### REGISTER 15-2: OCxCON2: OUTPUT COMPARE x CONTROL REGISTER 2

| R/W-0  | R/W-0  | R/W-0    | R/W-0 | U-0 | R/W-0               | R/W-0               | R/W-0 |

|--------|--------|----------|-------|-----|---------------------|---------------------|-------|

| FLTMD  | FLTOUT | FLTTRIEN | OCINV | _   | DCB1 <sup>(3)</sup> | DCB0 <sup>(3)</sup> | OC32  |

| bit 15 |        |          |       |     |                     |                     | bit 8 |

| R/W-0  | R/W-0, HS | R/W-0  | R/W-0    | R/W-1    | R/W-1    | R/W-0    | R/W-0    |

|--------|-----------|--------|----------|----------|----------|----------|----------|

| OCTRIG | TRIGSTAT  | OCTRIS | SYNCSEL4 | SYNCSEL3 | SYNCSEL2 | SYNCSEL1 | SYNCSEL0 |

| bit 7  |           |        |          |          |          |          | bit 0    |

Legend:HS = Hardware Settable bitR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15 FLTMD: Fault Mode Select bit

1 = Fault mode is maintained until the Fault source is removed and the corresponding OCFLT0 bit is cleared in software

0 = Fault mode is maintained until the Fault source is removed and a new PWM period starts

bit 14 FLTOUT: Fault Out bit

1 = PWM output is driven high on a Fault

0 = PWM output is driven low on a Fault

bit 13 FLTTRIEN: Fault Output State Select bit

1 = Pin is forced to an output on a Fault condition

0 = Pin I/O condition is unaffected by a Fault

bit 12 OCINV: Output Compare x Invert bit

1 = OCx output is inverted

0 = OCx output is not inverted

bit 11 **Unimplemented:** Read as '0'

bit 10-9 **DCB<1:0>:** PWM Duty Cycle Least Significant bits<sup>(3)</sup>

11 = Delays OCx falling edge by 3/4 of the instruction cycle

10 = Delays OCx falling edge by ½ of the instruction cycle

01 = Delays OCx falling edge by 1/4 of the instruction cycle

00 = OCx falling edge occurs at the start of the instruction cycle

bit 8 OC32: Cascade Two Output Compare Modules Enable bit (32-bit operation)

1 = Cascade module operation is enabled

0 = Cascade module operation is disabled

bit 7 OCTRIG: Output Compare x Trigger/Sync Select bit

1 = Triggers OCx from the source designated by the SYNCSELx bits

0 = Synchronizes OCx with the source designated by the SYNCSELx bits

bit 6 TRIGSTAT: Timer Trigger Status bit

1 = Timer source has been triggered and is running

0 = Timer source has not been triggered and is being held clear

bit 5 OCTRIS: Output Compare x Output Pin Direction Select bit

1 = OCx pin is tri-stated

0 = Output Compare Peripheral x is connected to an OCx pin

**Note 1:** Never use an OCx module as its own trigger source, either by selecting this mode or another equivalent SYNCSELx setting.

2: Use these inputs as trigger sources only and never as sync sources.

3: The DCB<1:0> bits are double-buffered in PWM modes only (OCM<2:0> (OCxCON1<2:0>) = 111, 110).

#### REGISTER 17-1: I2CxCONL: I2Cx CONTROL REGISTER LOW

| R/W-0  | U-0 | R/W-0, HC | R/W-1                 | R/W-0  | R/W-0 | R/W-0  | R/W-0 |

|--------|-----|-----------|-----------------------|--------|-------|--------|-------|

| I2CEN  | _   | I2CSIDL   | SCLREL <sup>(1)</sup> | STRICT | A10M  | DISSLW | SMEN  |

| bit 15 |     |           |                       |        |       |        | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0, HC |

|-------|-------|-------|-----------|-----------|-----------|-----------|-----------|

| GCEN  | STREN | ACKDT | ACKEN     | RCEN      | PEN       | RSEN      | SEN       |

| bit 7 |       |       |           |           |           |           | bit 0     |

**Legend:** HC = Hardware Clearable bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **I2CEN:** I2Cx Enable bit (writable from SW only)

1 = Enables the I2Cx module, and configures the SDAx and SCLx pins as serial port pins

$\circ$  = Disables the I2Cx module; all I<sup>2</sup>C<sup>™</sup> pins are controlled by port functions

bit 14 **Unimplemented:** Read as '0'

bit 13 I2CSIDL: I2Cx Stop in Idle Mode bit

1 = Discontinues module operation when device enters Idle mode

0 = Continues module operation in Idle mode

bit 12 SCLREL: SCLx Release Control bit (I<sup>2</sup>C Slave mode only)<sup>(1)</sup>

Module resets and (I2CEN = 0) sets SCLREL = 1.

If STREN = 0:(2)

1 = Releases clock

0 = Forces clock low (clock stretch)

#### If STREN = 1:

1 = Releases clock

0 = Holds clock low (clock stretch); user may program this bit to '0'; clock stretch is at the next SCLx low

bit 11 STRICT: I2Cx Strict Reserved Address Rule Enable bit

1 = Strict reserved addressing is enforced; for reserved addresses, refer to Table 17-1. (In Slave Mode) – The device doesn't respond to reserved address space and addresses falling in that category are NACKed.

(In Master Mode) – The device is allowed to generate addresses with reserved address space.

0 = Reserved addressing would be Acknowledged.

(In Slave Mode) – The device will respond to an address falling in the reserved address space. When there is a match with any of the reserved addresses, the device will generate an ACK. (In Master Mode) – Reserved.

bit 10 **A10M:** 10-Bit Slave Address Flag bit

1 = I2CxADD is a 10-bit slave address

0 = I2CADD is a 7-bit slave address

bit 9 DISSLW: Slew Rate Control Disable bit

1 = Slew rate control is disabled for Standard Speed mode (100 kHz, also disabled for 1 MHz mode)

0 = Slew rate control is enabled for High-Speed mode (400 kHz)

bit 8 SMEN: SMBus Input Levels Enable bit

1 = Enables input logic so thresholds are compliant with the SMBus specification

0 = Disables SMBus-specific inputs

**Note 1:** Automatically cleared to '0' at the beginning of slave transmission; automatically cleared to '0' at the end of slave reception.

**2:** Automatically cleared to '0' at the beginning of slave transmission.

## REGISTER 17-1: I2CxCONL: I2Cx CONTROL REGISTER LOW (CONTINUED)

bit 7 **GCEN:** General Call Enable bit (I<sup>2</sup>C Slave mode only)

1 = Enables interrupt when a general call address is received in I2CxRSR; module is enabled for reception

0 = General call address is disabled

bit 6 STREN: SCLx Clock Stretch Enable bit

In I<sup>2</sup>C Slave mode only; used in conjunction with the SCLREL bit.

1 = Enables clock stretching

0 = Disables clock stretching

bit 5 ACKDT: Acknowledge Data bit

In I<sup>2</sup>C Master mode during Master Receive mode. The value that will be transmitted when the user initiates an Acknowledge sequence at the end of a receive.

In  $I^2C$  Slave mode when AHEN = 1 or DHEN = 1. The value that the slave will transmit when it initiates an Acknowledge sequence at the end of an address or data reception.

1 = A NACK is sent

0 = ACK is sent

bit 4 ACKEN: Acknowledge Sequence Enable bit

In I<sup>2</sup>C Master mode only; applicable during Master Receive mode.

1 = Initiates Acknowledge sequence on SDAx and SCLx pins, and transmits ACKDT data bit

0 = Acknowledge sequence is Idle

bit 3 **RCEN:** Receive Enable bit (I<sup>2</sup>C Master mode only)

1 = Enables Receive mode for I<sup>2</sup>C; automatically cleared by hardware at the end of an 8-bit receive data byte

0 = Receive sequence is not in progress

bit 2 **PEN:** Stop Condition Enable bit (I<sup>2</sup>C Master mode only)

1 = Initiates Stop condition on SDAx and SCLx pins

0 = Stop condition is Idle

bit 1 **RSEN:** Restart Condition Enable bit (I<sup>2</sup>C Master mode only)

1 = Initiates Restart condition on the SDAx and SCLx pins

0 = Restart condition is Idle

bit 0 **SEN:** Start Condition Enable bit (I<sup>2</sup>C Master mode only)

1 = Initiates Start condition on the SDAx and SCLx pins

0 = Start condition is Idle

Note 1: Automatically cleared to '0' at the beginning of slave transmission; automatically cleared to '0' at the end of slave reception.

2: Automatically cleared to '0' at the beginning of slave transmission.

#### REGISTER 17-2: I2CxCONH: I2Cx CONTROL REGISTER HIGH

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| _     | PCIE  | SCIE  | BOEN  | SDAHT | SBCDE | AHEN  | DHEN  |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-7 **Unimplemented:** Read as '0'

bit 6 **PCIE**: Stop Condition Interrupt Enable bit (I<sup>2</sup>C<sup>™</sup> Slave mode only).

1 = Enables interrupt on detection of Stop condition

0 = Stop detection interrupts are disabled

bit 5 **SCIE:** Start Condition Interrupt Enable bit (I<sup>2</sup>C Slave mode only)

1 = Enables interrupt on detection of Start or Restart conditions

0 = Start detection interrupts are disabled

bit 4 **BOEN:** Buffer Overwrite Enable bit (I<sup>2</sup>C Slave mode only)

1 = I2CxRCV is updated and an ACK is generated for a received address/data byte, ignoring the state of the I2COV bit only if the RBF bit = 0

0 = I2CxRCV is only updated when I2COV is clear

bit 3 SDAHT: SDAx Hold Time Selection bit

1 = Minimum of 300 ns hold time on SDAx after the falling edge of SCLx

0 = Minimum of 100 ns hold time on SDAx after the falling edge of SCLx

bit 2 **SBCDE:** Slave Mode Bus Collision Detect Enable bit (I<sup>2</sup>C Slave mode only)

If, on the rising edge of SCLx, SDAx is sampled low when the module is outputting a high state, the BCL bit is set and the bus goes Idle. This Detection mode is only valid during data and ACK transmit sequences.

1 = Enables slave bus collision interrupts

0 = Slave bus collision interrupts are disabled

bit 1 AHEN: Address Hold Enable bit (I<sup>2</sup>C Slave mode only)

1 = Following the 8th falling edge of SCLx for a matching received address byte; SCLREL bit (I2CxCONL<12>) will be cleared and the SCLx will be held low

0 = Address holding is disabled

bit 0 **DHEN:** Data Hold Enable bit (I<sup>2</sup>C Slave mode only)

1 = Following the 8th falling edge of SCLx for a received data byte; slave hardware clears the SCLREL bit (I2CxCONL<12>) and SCLx is held low

0 = Data holding is disabled

#### REGISTER 20-1: PMCON1: EPMP CONTROL REGISTER 1

| R/W-0        | U-0 | R/W-0 | R/W-0   | R/W-0   | U-0 | R/W-0 | R/W-0 |

|--------------|-----|-------|---------|---------|-----|-------|-------|

| PMPEN        | _   | PSIDL | ADRMUX1 | ADRMUX0 | _   | MODE1 | MODE0 |

| bit 15 bit 8 |     |       |         |         |     |       |       |

| R/W-0       | R/W-0 | R/W-0 | R/W-0  | U-0 | R/W-0   | R/W-0 | R/W-0 |

|-------------|-------|-------|--------|-----|---------|-------|-------|

| CSF1        | CSF0  | ALP   | ALMODE | _   | BUSKEEP | IRQM1 | IRQM0 |

| bit 7 bit 0 |       |       |        |     |         |       |       |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **PMPEN:** EPMP Enable bit

1 = EPMP is enabled

0 = EPMP is disabled

bit 14 **Unimplemented:** Read as '0'

bit 13 **PSIDL:** EPMP Stop in Idle Mode bit

1 = Discontinues module operation when device enters Idle mode

0 = Continues module operation in Idle mode

bit 12-11 ADRMUX<1:0>: Address/Data Multiplexing Selection bits

11 = Lower address bits are multiplexed with data bits using 3 address phases

10 = Lower address bits are multiplexed with data bits using 2 address phases

01 = Lower address bits are multiplexed with data bits using 1 address phase

00 = Address and data appear on separate pins

bit 10 **Unimplemented:** Read as '0'

bit 9-8 **MODE<1:0>:** Parallel Port Mode Select bits

11 = Master mode

10 = Enhanced PSP: Pins used are PMRD, PMWR, PMCS, PMD<7:0> and PMA<1:0>

01 = Buffered PSP: Pins used are PMRD, PMWR, PMCS and PMD<7:0>

00 = Legacy Parallel Slave Port: Pins used are PMRD, PMWR, PMCS and PMD<7:0>

bit 7-6 **CSF<1:0>:** Chip Select Function bits

11 = Reserved

10 = PMA<14> is used for Chip Select 1

01 = Reserved

00 = PMCS1 is used for Chip Select 1

bit 5 **ALP:** Address Latch Polarity bit

1 = Active-high (PMALL, PMALH and PMALU)

$0 = Active-low (\overline{PMALL}, \overline{PMALH} \text{ and } \overline{PMALU})$

bit 4 ALMODE: Address Latch Strobe Mode bit

1 = Enables "smart" address strobes (each address phase is only present if the current access would cause a different address in the latch than the previous address)

0 = Disables "smart" address strobes

bit 3 **Unimplemented:** Read as '0'

bit 2 **BUSKEEP:** Bus Keeper bit

1 = Data bus keeps its last value when not actively being driven

0 = Data bus is in a high-impedance state when not actively being driven

bit 1-0 IRQM<1:0>: Interrupt Request Mode bits

11 = Interrupt is generated when Read Buffer 3 is read or Write Buffer 3 is written (Buffered PSP mode), or on a read or write operation when PMA<1:0> = 11 (Addressable PSP mode only)

10 = Reserved

01 = Interrupt is generated at the end of a read/write cycle

00 = No interrupt is generated

# 22.13 Programming CFGPAGE (Page 0) Configuration Bits

- 1. If not already set, set the CRYON bit. Set KEYPG<3:0> to '0000'.

- Read the PGMFAIL status bit. If this bit is '1', an illegal configuration has been selected and the programming operation will not be performed.

- Write the data to be programmed into the Configuration Page into CRYTXTC<31:0>. Any bits that are set ('1') will be permanently programmed, while any bits that are cleared ('0') will not be programmed and may be programmed at a later time.

- Set the CRYWR bit. Poll the bit until it is cleared; alternatively, set the OTPIE bit (CRYOTP<6>) to enable the optional OTP done interrupt.

- Once all programming has completed, set the CRYREAD bit to reload the values from the onchip storage. A read operation must be performed to complete programming.

Note: Do not clear the CRYON bit while the CRYREAD bit is set; this will result in an incomplete read operation and unavailable key data. To recover, set CRYON and CRYREAD, and allow the read operation to fully complete.

- Poll the CRYREAD bit until it is cleared; alternatively, set the OTPIE bit (CRYOTP<6>) to enable the optional OTP done interrupt.

- 7. For production programming, the TSTPGM bit can be set to indicate a successful programming operation. When TSTPGM is set, the PGMTST bit (CRYOTP<7>) will also be set, allowing users to see the OTP array status with performing a read operation on the array.

Note: If the device enters Sleep mode during OTP programming, the contents of the OTP array may become corrupted. This is not a recoverable error. Users must ensure that entry into power-saving modes is disabled before OTP programming is performed.

## 22.14 Programming Keys

- 1. If not already set, set the CRYON bit.

- 2. Configure KEYPG<3:0> to the page you want to program.

- Read the PGMFAIL status bit. If this bit is '1', an illegal configuration has been selected and the programming operation will not be performed.

- 4. Write the data to be programmed into the Configuration Page into CRYTXTC<63:0>. Any bits that are set ('1') will be permanently programmed, while any bits that are cleared ('0') will not be programmed and may be programmed at a later time.

- Set the CRYWR bit. Poll the bit until it is cleared; alternatively, set the OTPIE bit (CRYOTP<6>) to enable the optional OTP done interrupt.

- 6. Repeat Steps 2 through 5 for each OTP array page to be programmed.

- Once all programming has completed, set the CRYREAD bit to reload the values from the onchip storage. A read operation must be performed to complete programming.

Note: Do not clear the CRYON bit while the CRYREAD bit is set; this will result in an incomplete read operation and unavailable key data. To recover, set CRYON and CRYREAD, and allow the read operation to fully complete.

- 8. Poll the CRYREAD bit until it is cleared; alternatively, set the OTPIE bit (CRYOTP<6>) to enable the optional OTP done interrupt.

- For production programming, the TSTPGM bit can be set to indicate a successful programming operation. When TSTPGM is set, the PGMTST bit (CRYOTP<7>) will also be set, allowing users to see the OTP array status with performing a read operation on the array.

Note: If the device enters Sleep mode during OTP programming, the contents of the OTP array may become corrupted. This is not a recoverable error. Users must ensure that entry into power-saving modes is disabled before OTP programming is performed.

## 22.15 Verifying Programmed Keys

To maintain key security, the secure OTP array has no provision to read back its data to any user-accessible memory space in any operating mode. Therefore, there is no way to directly verify programmed data. The only method for verifying that they have been programmed correctly is to perform an encryption operation with a known plaintext/ciphertext pair for each programmed key.

FIGURE 32-7: I<sup>2</sup>C™ BUS DATA TIMING CHARACTERISTICS (SLAVE MODE)

TABLE 32-25: I<sup>2</sup>C™ BUS DATA TIMING REQUIREMENTS (SLAVE MODE)

Standard Operating Conditions: 2.0V to 3.6V (unless otherwise stated)

Operating temperature

-40°C  $\leq$  Ta  $\leq$  +85°C for Industrial -40°C  $\leq$  Ta  $\leq$  +125°C for Extended

Param

**AC CHARACTERISTICS**

No.

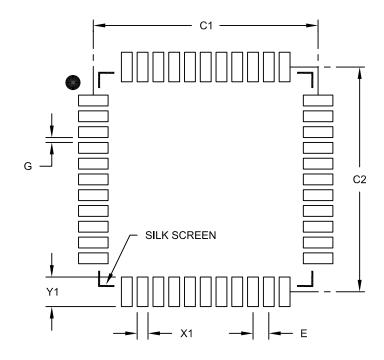

44-Lead Plastic Thin Quad Flatpack (PT) 10X10X1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                          | MILLIMETERS |      |          |      |

|--------------------------|-------------|------|----------|------|

| Dimension                | MIN         | NOM  | MAX      |      |

| Contact Pitch            | Е           |      | 0.80 BSC |      |

| Contact Pad Spacing      | C1          |      | 11.40    |      |

| Contact Pad Spacing      | C2          |      | 11.40    |      |

| Contact Pad Width (X44)  | X1          |      |          | 0.55 |

| Contact Pad Length (X44) | Y1          |      |          | 1.50 |

| Distance Between Pads    | G           | 0.25 |          |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2076B

## Worldwide Sales and Service

#### **AMERICAS**

Corporate Office

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200

Fax: 480-792-7277 Technical Support:

http://www.microchip.com/

support

Web Address:

www.microchip.com

**Atlanta** Duluth, GA

Tel: 678-957-9614

**Austin, TX** Tel: 512-257-3370

**Boston**

Westborough, MA Tel: 774-760-0087

Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

Cleveland

Independence, OH Tel: 216-447-0464

Fax: 216-447-0643 **Dallas**

Addison, TX Tel: 972-818-7423

Fax: 972-818-2924

Detroit Novi. MI

Tel: 248-848-4000

Tel: 248-848-4000

Houston, TX

Tel: 281-894-5983

Indianapolis Noblesville, IN

Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY

Tel: 631-435-6000

San Jose, CA

Tel: 408-735-9110

Canada - Toronto Tel: 905-673-0699

Fax: 905-673-0699

#### ASIA/PACIFIC

**Asia Pacific Office**

Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong Tel: 852-2943-5100

Fax: 852-2401-3431

Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

China - Beijing

Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

China - Chengdu

Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing

Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan

Tel: 86-769-8702-9880

China - Hangzhou

Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

China - Hong Kong SAR

Tel: 852-2943-5100 Fax: 852-2401-3431

China - Nanjing

Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

China - Qingdao

Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

China - Shanghai

Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang

Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

China - Shenzhen

Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

China - Wuhan

Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

China - Xian

Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

China - Xiamen

Tel: 86-592-2388138 Fax: 86-592-2388130

China - Zhuhai

Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore

Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi

Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune

Tel: 91-20-3019-1500

Japan - Osaka

Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

Japan - Tokyo

Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

Korea - Daegu

Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul

Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur

Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang

Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila

Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore

Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu

Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung

Tel: 886-7-213-7828

**Taiwan - Taipei** Tel: 886-2-2508-8600

Fax: 886-2-2508-0102

Thailand - Bangkok

Tel: 66-2-694-1351 Fax: 66-2-694-1350

## EUROPE

Austria - Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen

Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf

Tel: 49-2129-3766400

Germany - Munich

Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Germany - Pforzheim

Tel: 49-7231-424750 Italy - Milan

Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice

Tel: 39-049-7625286

Netherlands - Drunen

Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw

Tel: 48-22-3325737

Spain - Madrid

Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Stockholm

Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

01/27/15