#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, LVD, POR, PWM, WDT                                |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 10x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                 |

| Supplier Device Package    | 28-SSOP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128ga202-e-ss |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS3000000A is version A of document DS30000000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### Customer Notification System

Register on our web site at www.microchip.com to receive the most current information on all of our products.

|              | Pin Num                       | per/Grid        | Locator            |     |                 |                                       |

|--------------|-------------------------------|-----------------|--------------------|-----|-----------------|---------------------------------------|

| Pin Function | 28-Pin<br>SPDIP/SOIC/<br>SSOP | 28-Pin<br>QFN-S | 44-Pin<br>TQFP/QFN | I/O | Input<br>Buffer | Description                           |

| CN0          | 12                            | 9               | 34                 | —   |                 | Interrupt-on-Change Inputs.           |

| CN1          | 11                            | 8               | 33                 | _   | —               |                                       |

| CN2          | 2                             | 27              | 19                 | —   | —               |                                       |

| CN3          | 3                             | 28              | 20                 | _   | —               |                                       |

| CN4          | 4                             | 1               | 21                 | _   |                 |                                       |

| CN5          | 5                             | 2               | 22                 | _   |                 |                                       |

| CN6          | 6                             | 3               | 23                 | _   |                 |                                       |

| CN7          | 7                             | 4               | 24                 |     |                 |                                       |

| CN8          | _                             |                 | 25                 | _   |                 |                                       |

| CN9          | _                             |                 | 26                 |     |                 |                                       |

| CN10         | —                             |                 | 27                 |     |                 |                                       |

| CN11         | 26                            | 23              | 15                 |     |                 |                                       |

| CN12         | 25                            | 22              | 14                 | _   | _               |                                       |

| CN13         | 24                            | 21              | 11                 | _   | _               |                                       |

| CN14         | 23                            | 20              | 10                 |     |                 |                                       |

| CN15         | 22                            | 19              | 9                  |     |                 |                                       |

| CN16         | 21                            | 18              | 8                  | _   | _               |                                       |

| CN17         | —                             |                 | 3                  |     |                 |                                       |

| CN18         | —                             |                 | 2                  | _   | _               |                                       |

| CN19         | —                             |                 | 5                  | _   | _               |                                       |

| CN20         | —                             |                 | 4                  | _   | —               |                                       |

| CN21         | 18                            | 15              | 1                  | _   | _               |                                       |

| CN22         | 17                            | 14              | 44                 | —   | —               |                                       |

| CN23         | 16                            | 13              | 43                 | —   | —               |                                       |

| CN24         | 15                            | 12              | 42                 |     | —               |                                       |

| CN25         | —                             |                 | 37                 |     | _               |                                       |

| CN26         | —                             | —               | 38                 |     | —               |                                       |

| CN27         | 14                            | 11              | 41                 | _   | —               |                                       |

| CN28         |                               |                 | 36                 | _   |                 |                                       |

| CN29         | 10                            | 7               | 31                 | _   |                 |                                       |

| CN30         | 9                             | 6               | 30                 | -   |                 |                                       |

| CN33         | —                             |                 | 13                 | _   |                 |                                       |

| CN34         |                               | _               | 32                 | _   |                 |                                       |

| CN35         | —                             | —               | 35                 | _   | —               |                                       |

| CN36         |                               | _               | 12                 | _   |                 |                                       |

| CTCMP        | 4                             | 1               | 21                 | I   | ANA             | CTMU Comparator 2 Input (Pulse mode). |

#### **TABLE 1-3:** PIC24FJ128GA204 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

ANA = Analog Input  $I^2C$  = ST with  $I^2C^{\text{TM}}$  or SMBus levels

|                      | Pin Num                       | per/Grid        | Locator            |     |                 |                                            |

|----------------------|-------------------------------|-----------------|--------------------|-----|-----------------|--------------------------------------------|

| Pin Function         | 28-Pin<br>SPDIP/SOIC/<br>SSOP | 28-Pin<br>QFN-S | 44-Pin<br>TQFP/QFN | I/O | Input<br>Buffer | Description                                |

| PMA0/PMALL           | _                             | _               | 3                  | 0   | _               | Parallel Master Port Address.              |

| PMA1/PMALH           | _                             |                 | 2                  | 0   | _               |                                            |

| PMA14/PMCS/<br>PMCS1 | _                             | —               | 15                 | 0   | —               |                                            |

| PMA2/PMALU           | _                             |                 | 12                 | 0   | _               |                                            |

| PMA3                 | _                             |                 | 38                 | 0   | _               |                                            |

| PMA4                 | _                             |                 | 37                 | 0   | _               |                                            |

| PMA5                 | _                             |                 | 4                  | 0   | _               |                                            |

| PMA6                 | _                             |                 | 5                  | 0   | _               |                                            |

| PMA7                 | -                             | —               | 13                 | 0   | _               |                                            |

| PMA8                 | -                             | —               | 32                 | 0   | —               |                                            |

| PMA9                 | 1 —                           | _               | 35                 | 0   | —               |                                            |

| PMACK1               | _                             | —               | 27                 | Ι   | ST/TTL          | Parallel Master Port Acknowledge Input 1.  |

| PMBE0                | _                             |                 | 36                 | 0   | _               | Parallel Master Port Byte Enable 0 Strobe. |

| PMBE1                | —                             |                 | 25                 | 0   |                 | Parallel Master Port Byte Enable 1 Strobe. |

| PMCS1                | _                             |                 | 30                 | I/O | ST/TTL          | Parallel Master Port Chip Select 1 Strobe. |

| PMD0                 | _                             |                 | 10                 | I/O | ST/TTL          |                                            |

| PMD1                 | _                             |                 | 9                  | I/O | ST/TTL          | Master mode) or Address/Data (Multiplexed  |

| PMD2                 | _                             |                 | 8                  | I/O | ST/TTL          | Master modes).                             |

| PMD3                 | _                             |                 | 1                  | I/O | ST/TTL          |                                            |

| PMD4                 | —                             |                 | 44                 | I/O | ST/TTL          |                                            |

| PMD5                 | _                             |                 | 43                 | I/O | ST/TTL          |                                            |

| PMD6                 | _                             |                 | 42                 | I/O | ST/TTL          |                                            |

| PMD7                 | _                             |                 | 41                 | I/O | ST/TTL          |                                            |

| PMRD                 | -                             | _               | 11                 | 0   | —               | Parallel Master Port Read Strobe.          |

| PMWR                 | _                             | —               | 14                 | 0   | —               | Parallel Master Port Write Strobe.         |

| RA0                  | 2                             | 27              | 19                 | I/O | ST              | PORTA Digital I/Os.                        |

| RA1                  | 3                             | 28              | 20                 | I/O | ST              |                                            |

| RA2                  | 9                             | 6               | 30                 | I/O | ST              |                                            |

| RA3                  | 10                            | 7               | 31                 | I/O | ST              |                                            |

| RA4                  | 12                            | 9               | 34                 | Ι   | ST              |                                            |

| RA7                  | _                             | —               | 13                 | I/O | ST              |                                            |

| RA8                  | —                             | _               | 32                 | I/O | ST              |                                            |

| RA9                  | _                             | —               | 35                 | I/O | ST              |                                            |

| RA10                 |                               |                 | 12                 | I/O | ST              |                                            |

### TABLE 1-3: PIC24FJ128GA204 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

$I^2C = ST \text{ with } I^2C^{TM} \text{ or SMBus levels}$

### TABLE 4-9: I<sup>2</sup>C<sup>™</sup> REGISTER MAP

| File<br>Name | Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10                       | Bit 9                                                   | Bit 8 | Bit 7 | Bit 6      | Bit 5       | Bit 4       | Bit 3        | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|------|---------|--------|---------|--------|--------|------------------------------|---------------------------------------------------------|-------|-------|------------|-------------|-------------|--------------|-------|-------|-------|---------------|

| I2C1RCV      | 02DA | —       |        | —       | _      | _      |                              | —                                                       | —     |       |            | I           | 2C1 Receiv  | ve Register  |       |       |       | 0000          |

| I2C1TRN      | 02DC | _       | _      | _       | _      | _      | _                            | _                                                       | _     |       |            | l:          | 2C1 Transn  | nit Register |       |       |       | OOFF          |

| I2C1BRG      | 02DE | _       | _      | _       | _      |        | Baud Rate Generator Register |                                                         |       |       |            |             |             | 0000         |       |       |       |               |

| I2C1CONL     | 02E0 | I2CEN   | _      | I2CSIDL | SCLREL | STRICT | A10M                         | 0M DISSLW SMEN GCEN STREN ACKDT ACKEN RCEN PEN RSEN SEN |       |       |            |             |             | 1000         |       |       |       |               |

| I2C1CONH     | 02E2 | _       | _      | _       | _      | _      | _                            | _                                                       | _     | _     | PCIE       | SCIE        | BOEN        | SDAHT        | SBCDE | AHEN  | DHEN  | 0000          |

| I2C1STAT     | 02E4 | ACKSTAT | TRSTAT | ACKTIM  | _      | _      | BCL                          | GCSTAT                                                  | ADD10 | IWCOL | I2COV      | D/A         | Р           | S            | R/W   | RBF   | TBF   | 0000          |

| I2C1ADD      | 02E6 | —       | _      | _       | _      | —      | _                            |                                                         |       |       |            | 2C1 Addres  | ss Register |              |       |       |       | 0000          |

| I2C1MSK      | 02E8 | —       | _      | —       | _      | —      | -                            |                                                         |       |       | I2C        | 1 Address I | Mask Regis  | ter          |       |       |       | 0000          |

| I2C2RCV      | 02EA | —       | _      | —       | _      | —      | -                            | _                                                       | _     |       |            | I           | 2C2 Receiv  | e Register   |       |       |       | 0000          |

| I2C2TRN      | 02EC | _       | _      | _       | _      | _      | _                            | _                                                       | _     |       |            | l:          | 2C2 Transn  | nit Register |       |       |       | OOFF          |

| I2C2BRG      | 02EE | _       | —      | _       | _      |        |                              |                                                         |       | Bau   | d Rate Gen | erator Regi | ster        |              |       |       |       | 0000          |

| I2C2CONL     | 02F0 | I2CEN   | _      | I2CSIDL | SCLREL | STRICT | A10M                         | DISSLW                                                  | SMEN  | GCEN  | STREN      | ACKDT       | ACKEN       | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C2CONH     | 02F2 | _       | _      | _       | _      | _      | _                            | _                                                       | _     | _     | PCIE       | SCIE        | BOEN        | SDAHT        | SBCDE | AHEN  | DHEN  | 0000          |

| I2C2STAT     | 02F4 | ACKSTAT | TRSTAT | ACKTIM  | _      | _      | BCL                          | GCSTAT                                                  | ADD10 | IWCOL | I2COV      | D/A         | Р           | S            | R/W   | RBF   | TBF   | 0000          |

| I2C2ADD      | 02F6 | —       | _      | —       | _      | —      | -                            |                                                         |       |       |            | 2C2 Addres  | ss Register |              |       |       |       | 0000          |

| I2C2MSK      | 02F8 | —       | _      | _       | _      | —      | _                            |                                                         |       |       | I2C        | 2 Address I | Mask Regis  | ter          |       |       |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| DSRPAG<br>(Data Space Read<br>Register) | DSWPAG<br>(Data Space Write<br>Register) | Source/Destination<br>Address While<br>Indirect<br>Addressing | 24-Bit EA<br>Pointing to EDS | Comment                           |

|-----------------------------------------|------------------------------------------|---------------------------------------------------------------|------------------------------|-----------------------------------|

| x <sup>(1)</sup>                        | x <sup>(1)</sup>                         | 0000h to 1FFFh                                                | 000000h to<br>001FFFh        | Near Data Space <sup>(2)</sup>    |

| X. /                                    | Χ',                                      | 2000h to 7FFFh                                                | 002000h to<br>007FFFh        |                                   |

| 001h                                    | 001h                                     |                                                               | 008000h to<br>00FFFEh        |                                   |

| 002h                                    | 002h                                     |                                                               | 010000h to<br>017FFEh        |                                   |

| 003h<br>•                               | 003h<br>•                                |                                                               | 018000h to<br>0187FEh        | EPMP Memory Space                 |

| •                                       | •                                        | 8000h to FFFFh                                                | •                            |                                   |

| •                                       | •                                        |                                                               |                              |                                   |

| •                                       | •                                        |                                                               | •                            |                                   |

| •<br>1FFh                               | •<br>1FFh                                |                                                               | FF8000h to<br>FFFFFEh        |                                   |

| 000h                                    | 000h                                     |                                                               | Invalid Address              | Address Error Trap <sup>(3)</sup> |

### TABLE 4-34: EDS MEMORY ADDRESS WITH DIFFERENT PAGES AND ADDRESSES

Note 1: If the source/destination address is below 8000h, the DSRPAG and DSWPAG registers are not considered.

- 2: This Data Space can also be accessed by Direct Addressing.

- **3:** When the source/destination address is above 8000h and DSRPAG/DSWPAG are '0', an address error trap will occur.

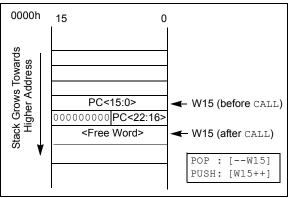

### 4.2.6 SOFTWARE STACK

Apart from its use as a Working register, the W15 register in PIC24F devices is also used as a Software Stack Pointer (SSP). The pointer always points to the first available free word and grows from lower to higher addresses. It predecrements for stack pops and post-increments for stack pushes, as shown in Figure 4-7. Note that for a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, ensuring that the MSB is always clear.

| Note: | A PC push during exception processing    |

|-------|------------------------------------------|

|       | will concatenate the SRL Register to the |

|       | MSB of the PC prior to the push.         |

The Stack Pointer Limit Value (SPLIM) register, associated with the Stack Pointer, sets an upper address boundary for the stack. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0' as all stack operations must be wordaligned. Whenever an EA is generated using W15 as a Source or Destination Pointer, the resulting address is compared with the value in SPLIM. If the contents of the Stack Pointer (W15) and the SPLIM register are equal, and a push operation is performed, a stack error trap will not occur. The stack error trap will occur on a subsequent push operation. Thus, for example, if it is desirable to cause a stack error trap when the stack grows beyond address, 2000h in RAM, initialize the SPLIM with the value, 1FFEh.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0800h. This prevents the stack from interfering with the SFR space.

A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

### FIGURE 4-7: CALL STACK FRAME

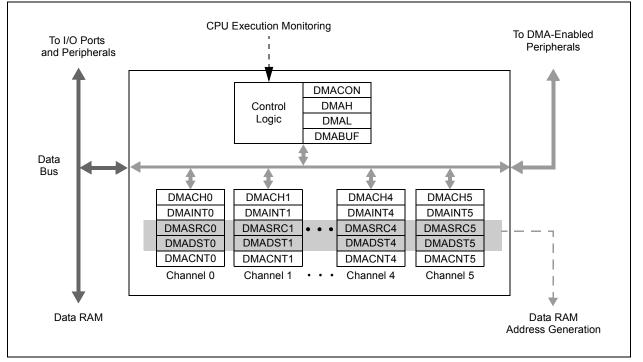

### 5.0 DIRECT MEMORY ACCESS CONTROLLER (DMA)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Direct Memory Access Controller (DMA)" (DS39742). The information in this data sheet supersedes the information in the FRM.

The Direct Memory Access (DMA) Controller is designed to service high data throughput peripherals operating on the SFR bus, allowing them to access data memory directly and alleviating the need for CPU intensive management. By allowing these data-intensive peripherals to share their own data path, the main data bus is also deloaded, resulting in additional power savings.

The DMA Controller functions both as a peripheral and a direct extension of the CPU. It is located on the microcontroller data bus between the CPU and DMA-enabled peripherals, with direct access to SRAM. This partitions the SFR bus into two buses, allowing the DMA Controller access to the DMA capable peripherals located on the new DMA SFR bus. The controller serves as a master device on the DMA SFR bus, controlling data flow from DMA capable peripherals. The controller also monitors CPU instruction processing directly, allowing it to be aware of when the CPU requires access to peripherals on the DMA bus and automatically relinquishing control to the CPU as needed. This increases the effective bandwidth for handling data without DMA operations causing a processor stall. This makes the controller essentially transparent to the user.

The DMA Controller has these features:

- Six multiple independent and independently programmable channels

- Concurrent operation with the CPU (no DMA caused Wait states)

- DMA bus arbitration

- Five Programmable Address modes

- Four Programmable Transfer modes

- Four Flexible Internal Data Transfer modes

- · Byte or word support for data transfer

- 16-Bit Source and Destination Address register for each channel, dynamically updated and reloadable

- 16-Bit Transaction Count register, dynamically updated and reloadable

- Upper and Lower Address Limit registers

- Counter half-full level interrupt

- · Software triggered transfer

- Null Write mode for symmetric buffer operations

A simplified block diagram of the DMA Controller is shown in Figure 5-1.

### FIGURE 5-1: DMA FUNCTIONAL BLOCK DIAGRAM

### REGISTER 8-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0 (CONTINUED)

- bit 2 OC1IF: Output Compare Channel 1 Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 1 IC1IF: Input Capture Channel 1 Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 0 INTOIF: External Interrupt 0 Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

### REGISTER 8-18: IEC5: INTERRUPT ENABLE CONTROL REGISTER 5

| U-0             | U-0                                                                                       | U-0                                  | U-0              | R/W-0             | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |  |

|-----------------|-------------------------------------------------------------------------------------------|--------------------------------------|------------------|-------------------|------------------|-----------------|--------|--|--|--|--|--|

| —               | —                                                                                         | —                                    | —                | SPI3TXIE          | SPI3IE           | U4TXIE          | U4RXIE |  |  |  |  |  |

| bit 15          |                                                                                           |                                      |                  |                   |                  |                 | bit 8  |  |  |  |  |  |

|                 |                                                                                           |                                      |                  |                   |                  |                 |        |  |  |  |  |  |

| R/W-0           | U-0                                                                                       | R/W-0                                | R/W-0            | R/W-0             | R/W-0            | R/W-0           | U-0    |  |  |  |  |  |

| U4ERIE          | _                                                                                         | I2C2BCIE                             | I2C1BCIE         | U3TXIE            | <b>U3RXIE</b>    | U3ERIE          |        |  |  |  |  |  |

| bit 7           |                                                                                           |                                      |                  |                   |                  |                 | bit    |  |  |  |  |  |

| Legend:         |                                                                                           |                                      |                  |                   |                  |                 |        |  |  |  |  |  |

| R = Readable    | bit                                                                                       | W = Writable                         | bit              | U = Unimplem      | nented bit, read | d as '0'        |        |  |  |  |  |  |

| -n = Value at F |                                                                                           | '1' = Bit is set                     |                  | '0' = Bit is clea |                  | x = Bit is unkr | nown   |  |  |  |  |  |

|                 |                                                                                           |                                      |                  |                   |                  |                 |        |  |  |  |  |  |

| bit 15-12       | Unimplemer                                                                                | nted: Read as '                      | ) <b>'</b>       |                   |                  |                 |        |  |  |  |  |  |

| bit 11          | SPI3TXIE: S                                                                               | PI3 Transmit In                      | terrupt Enable   | bit               |                  |                 |        |  |  |  |  |  |

|                 | •                                                                                         | request is enab                      |                  |                   |                  |                 |        |  |  |  |  |  |

|                 |                                                                                           | request is not e                     |                  |                   |                  |                 |        |  |  |  |  |  |

| bit 10          | SPI3IE: SPI3 General Interrupt Enable bit                                                 |                                      |                  |                   |                  |                 |        |  |  |  |  |  |

|                 |                                                                                           | request is enab<br>request is not e  |                  |                   |                  |                 |        |  |  |  |  |  |

| bit 9           | •                                                                                         | •                                    |                  | ole hit           |                  |                 |        |  |  |  |  |  |

| bit 0           | <b>U4TXIE:</b> UART4 Transmitter Interrupt Enable bit<br>1 = Interrupt request is enabled |                                      |                  |                   |                  |                 |        |  |  |  |  |  |

|                 |                                                                                           | 0 = Interrupt request is not enabled |                  |                   |                  |                 |        |  |  |  |  |  |

| bit 8           | U4RXIE: UART4 Receiver Interrupt Enable bit                                               |                                      |                  |                   |                  |                 |        |  |  |  |  |  |

|                 |                                                                                           | request is enab                      |                  |                   |                  |                 |        |  |  |  |  |  |

| bit 7           | -                                                                                         | request is not e<br>RT4 Error Interr |                  |                   |                  |                 |        |  |  |  |  |  |

|                 |                                                                                           | request is enab                      | •                |                   |                  |                 |        |  |  |  |  |  |

|                 |                                                                                           | request is not e                     |                  |                   |                  |                 |        |  |  |  |  |  |

| bit 6           | Unimplemer                                                                                | nted: Read as '                      | o <b>'</b>       |                   |                  |                 |        |  |  |  |  |  |

| bit 5           | 12C2BCIE: 12                                                                              | 2C2 Bus Collisio                     | on Interrupt Ena | able bit          |                  |                 |        |  |  |  |  |  |

|                 | 1 = Interrupt                                                                             | request is enab                      | led              |                   |                  |                 |        |  |  |  |  |  |

|                 | •                                                                                         | request is not e                     |                  |                   |                  |                 |        |  |  |  |  |  |

| bit 4           |                                                                                           | 2C1 Bus Collisio<br>request is enab  |                  | able bit          |                  |                 |        |  |  |  |  |  |

|                 |                                                                                           | request is not e                     |                  |                   |                  |                 |        |  |  |  |  |  |

| bit 3           | -                                                                                         | RT3 Transmitter                      |                  | ole bit           |                  |                 |        |  |  |  |  |  |

|                 | 1 = Interrupt                                                                             | request is enab                      | led              |                   |                  |                 |        |  |  |  |  |  |

|                 | 0 = Interrupt request is not enabled                                                      |                                      |                  |                   |                  |                 |        |  |  |  |  |  |

| bit 2           | U3RXIE: UART3 Receiver Interrupt Enable bit                                               |                                      |                  |                   |                  |                 |        |  |  |  |  |  |

|                 |                                                                                           | request is enab<br>request is not e  |                  |                   |                  |                 |        |  |  |  |  |  |

| bit 1           | -                                                                                         | RT3 Error Interr                     |                  |                   |                  |                 |        |  |  |  |  |  |

|                 |                                                                                           | request is enab                      |                  |                   |                  |                 |        |  |  |  |  |  |

|                 |                                                                                           |                                      |                  |                   |                  |                 |        |  |  |  |  |  |

|                 | •                                                                                         | request is not e                     |                  |                   |                  |                 |        |  |  |  |  |  |

| U-0       | U-0                                   | U-0                                  | U-0                           | U-0                   | U-0                     | U-0                    | U-0                 |

|-----------|---------------------------------------|--------------------------------------|-------------------------------|-----------------------|-------------------------|------------------------|---------------------|

| _         | —                                     | _                                    |                               | —                     | _                       |                        |                     |

| oit 15    |                                       |                                      |                               |                       |                         |                        | bit 8               |

|           |                                       |                                      |                               |                       |                         |                        |                     |

| U-0       | U-0                                   | U-0                                  | r-0                           | R/CO-1                | R/CO-1                  | R/CO-1                 | R/CO-0              |

|           | —                                     | —                                    | _                             | VDDBOR <sup>(1)</sup> | VDDPOR <sup>(1,2)</sup> | VBPOR <sup>(1,3)</sup> | VBAT <sup>(1)</sup> |

| bit 7     |                                       |                                      |                               |                       |                         |                        | bit C               |

|           |                                       |                                      |                               |                       |                         |                        |                     |

| Legend:   |                                       | CO = Clearab                         | -                             | r = Reserved          |                         |                        |                     |

| R = Read  |                                       | W = Writable b                       | bit                           |                       | nented bit, read        |                        |                     |

| -n = Valu | e at POR                              | '1' = Bit is set                     |                               | '0' = Bit is clea     | ared                    | x = Bit is unkno       | own                 |

|           |                                       |                                      |                               |                       |                         |                        |                     |

| bit 15-5  | •                                     | ted: Read as 'C                      | 1-                            |                       |                         |                        |                     |

| bit 4     | Reserved: M                           |                                      | (1)                           |                       |                         |                        |                     |

| bit 3     |                                       | D Brown-out R                        | •                             |                       |                         |                        |                     |

|           |                                       | own-out Reset ł<br>own-out Reset ł   | ·                             |                       | e)                      |                        |                     |

| bit 2     |                                       | D Power-on Re                        |                               |                       |                         |                        |                     |

| 5.12      |                                       | wer-on Reset h                       |                               |                       | e)                      |                        |                     |

|           |                                       | wer-on Reset h                       | •                             | •                     |                         |                        |                     |

| bit 1     | VBPOR: VBA                            | T Power-on Res                       | set Flag bit <sup>(1,3)</sup> |                       |                         |                        |                     |

|           | 1 = A VBAT F                          | OR has occurr                        | ed (no battery                | connected to          | the VBAT pin o          | r VBAT power is        | s below Deep        |

|           |                                       | maphore retent                       |                               | oy hardware)          |                         |                        |                     |

|           |                                       | OR has not occ                       | curred                        |                       |                         |                        |                     |

| bit 0     | <b>VBAT:</b> VBAT F                   | 0                                    |                               |                       |                         |                        |                     |

|           |                                       | xit has occurred<br>xit from Vват ha |                               |                       | e VBAT pin (set         | by hardware)           |                     |

|           | 0 = A POR e                           |                                      | as not occurre                | u                     |                         |                        |                     |

| Note 1:   | This bit is set in h                  | ardware only; it                     | can only be c                 | leared in softwa      | are.                    |                        |                     |

| 2:        | This bit indicates<br>Power-on Reset. | a VDD Power-o                        | n Reset. Settir               | ng the POR bit        | (RCON<0>) inc           | licates a VCORE        | I                   |

| 3:        | This bit is set whe                   | en the device is                     | originally pow                | ered up, even i       | f power is pres         | ent on VBAT.           |                     |

|           |                                       |                                      |                               |                       |                         |                        |                     |

### REGISTER 10-3: RCON2: RESET AND SYSTEM CONTROL REGISTER 2

### **REGISTER 11-3:** ANSC: PORTC ANALOG FUNCTION SELECTION REGISTER<sup>(1)</sup>

| Legend:<br>R = Readable |     | W = Writable |     |     | nented hit read |           |       |

|-------------------------|-----|--------------|-----|-----|-----------------|-----------|-------|

| bit 7                   |     |              |     |     |                 |           | bit C |

| _                       | _   | _            | _   | —   |                 | ANSC<2:0> |       |

| U-0                     | U-0 | U-0          | U-0 | U-0 | R/W-1           | R/W-1     | R/W-1 |

| bit 15                  |     |              |     |     |                 |           | bit 8 |

|                         | _   | —            |     | —   | —               | —         | —     |

| U-0                     | U-0 | U-0          | U-0 | U-0 | U-0             | U-0       | U-0   |

R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15-3 Unimplemented: Read as '0'

bit 2-0 ANSC<2:0>: PORTC Analog Function Selection bits 1 = Pin is configured in Analog mode; I/O port read is disabled 0 = Pin is configured in Digital mode; I/O port read is enabled

Note 1: These pins are not available in 28-pin devices.

| R/W-0              | U-0                                                                    | R/W-0                                                             | U-0                     | U-0                        | U-0             | R/W-0                     | R/W-0                 |  |  |  |  |

|--------------------|------------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------|----------------------------|-----------------|---------------------------|-----------------------|--|--|--|--|

| TON <sup>(2)</sup> | —                                                                      | TSIDL <sup>(2)</sup>                                              | —                       | _                          | _               | TECS1 <sup>(2,3)</sup>    | TECS0 <sup>(2,3</sup> |  |  |  |  |

| bit 15             |                                                                        |                                                                   |                         |                            |                 |                           | bit                   |  |  |  |  |

|                    |                                                                        |                                                                   |                         |                            |                 |                           |                       |  |  |  |  |

| U-0                | R/W-0                                                                  | R/W-0                                                             | R/W-0                   | U-0                        | U-0             | R/W-0                     | U-0                   |  |  |  |  |

| _                  | TGATE <sup>(2)</sup>                                                   | TCKPS1 <sup>(2)</sup>                                             | TCKPS0 <sup>(2)</sup>   | _                          | —               | TCS <sup>(2,3)</sup>      | _                     |  |  |  |  |

| bit 7              |                                                                        |                                                                   |                         |                            |                 |                           | bit                   |  |  |  |  |

| Legend:            |                                                                        |                                                                   |                         |                            |                 |                           |                       |  |  |  |  |

| R = Reada          | ble bit                                                                | W = Writable                                                      | bit                     | U = Unimpler               | nented bit, rea | ad as '0'                 |                       |  |  |  |  |

| -n = Value         | at POR                                                                 | '1' = Bit is set                                                  |                         | '0' = Bit is cle           | ared            | x = Bit is unkn           | iown                  |  |  |  |  |

|                    |                                                                        |                                                                   |                         |                            |                 |                           |                       |  |  |  |  |

| bit 15             | TON: Timery                                                            |                                                                   |                         |                            |                 |                           |                       |  |  |  |  |

|                    | 1 = Starts 16-<br>0 = Stops 16-                                        |                                                                   |                         |                            |                 |                           |                       |  |  |  |  |

| bit 14             | •                                                                      | ted: Read as '                                                    | )'                      |                            |                 |                           |                       |  |  |  |  |

| bit 13             | TSIDL: Timer                                                           | ry Stop in Idle M                                                 | lode bit <sup>(2)</sup> |                            |                 |                           |                       |  |  |  |  |

|                    |                                                                        | ues module ope                                                    |                         |                            | lle mode        |                           |                       |  |  |  |  |

|                    |                                                                        | s module opera                                                    |                         | de                         |                 |                           |                       |  |  |  |  |

| bit 12-10          | -                                                                      | ted: Read as '                                                    |                         |                            |                 | (2.2)                     |                       |  |  |  |  |

| bit 9-8            |                                                                        | Timery Extende                                                    |                         | -                          | selected when   | TCS = 1) <sup>(2,3)</sup> |                       |  |  |  |  |

|                    |                                                                        | 11 = Generic Timer (TMRCK) External Input<br>10 = LPRC Oscillator |                         |                            |                 |                           |                       |  |  |  |  |

|                    |                                                                        | xternal Clock In                                                  | put                     |                            |                 |                           |                       |  |  |  |  |

|                    | 00 <b>= SOSC</b>                                                       |                                                                   | •                       |                            |                 |                           |                       |  |  |  |  |

| bit 7              | Unimplemen                                                             | ted: Read as '                                                    | )'                      |                            |                 |                           |                       |  |  |  |  |

| bit 6              | <b>TGATE:</b> Timery Gated Time Accumulation Enable bit <sup>(2)</sup> |                                                                   |                         |                            |                 |                           |                       |  |  |  |  |

|                    | When TCS =                                                             |                                                                   |                         |                            |                 |                           |                       |  |  |  |  |

|                    | This bit is ign<br>When TCS =                                          |                                                                   |                         |                            |                 |                           |                       |  |  |  |  |

|                    |                                                                        | <u></u><br>ne accumulatio                                         | n is enabled            |                            |                 |                           |                       |  |  |  |  |

|                    | 0 = Gated tin                                                          | ne accumulatio                                                    | n is disabled           |                            |                 |                           |                       |  |  |  |  |

| bit 5-4            | TCKPS<1:0>                                                             | : Timery Input                                                    | Clock Prescale          | Select bits <sup>(2)</sup> |                 |                           |                       |  |  |  |  |

|                    | 11 <b>= 1:256</b>                                                      |                                                                   |                         |                            |                 |                           |                       |  |  |  |  |

|                    | 10 = 1:64<br>01 = 1:8                                                  |                                                                   |                         |                            |                 |                           |                       |  |  |  |  |

|                    | 01 = 1.8<br>00 = 1:1                                                   |                                                                   |                         |                            |                 |                           |                       |  |  |  |  |

| bit 3-2            |                                                                        | ted: Read as '                                                    | )'                      |                            |                 |                           |                       |  |  |  |  |

| bit 1              | -                                                                      | Clock Source S                                                    |                         |                            |                 |                           |                       |  |  |  |  |

|                    | -                                                                      | clock from pin,                                                   |                         | sing edge)                 |                 |                           |                       |  |  |  |  |

|                    | 0 = Internal c                                                         | lock (Fosc/2)                                                     |                         |                            |                 |                           |                       |  |  |  |  |

| bit 0              | Unimplemen                                                             | ted: Read as '                                                    | )'                      |                            |                 |                           |                       |  |  |  |  |

|                    | Changing the value reset and is not re                                 | -                                                                 | nile the timer is       | running (TON               | = 1) causes th  | e timer prescale          | counter to            |  |  |  |  |

|                    | When 32-bit oper operation; all time                                   |                                                                   |                         |                            |                 | ts have no effect         | on Timery             |  |  |  |  |

|                    | If TCS = 1 and TI<br>available RPn/RF                                  |                                                                   |                         |                            | • • • •         | •                         |                       |  |  |  |  |

| REGISTER 17-3: I20 | xSTAT: I2Cx STATUS REGISTER |

|--------------------|-----------------------------|

|--------------------|-----------------------------|

| REGISTER     | 17-3: 120                      | XSTAT: 120                       | Cx STATUS                                            | REGISTER                                                       |                                                  |                                  |                 |

|--------------|--------------------------------|----------------------------------|------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------|----------------------------------|-----------------|

| R-0, HSC     | R-0, HSC                       | R-0, HSC                         | U-0                                                  | U-0                                                            | R/C-0, HSC                                       | R-0, HSC                         | R-0, HSC        |

| ACKSTAT      | TRSTAT                         | ACKTIM                           | —                                                    | —                                                              | BCL                                              | GCSTAT                           | ADD10           |

| bit 15       |                                |                                  |                                                      |                                                                |                                                  |                                  | bita            |

| R/C-0, HS    | R/C-0, HS                      | R-0, HSC                         | R/C-0, HSC                                           | R/C-0, HSC                                                     | R-0, HSC                                         | R-0, HSC                         | R-0, HSC        |

| IWCOL        | 12COV                          | D/A                              | P                                                    | S                                                              | R/W                                              | RBF                              | TBF             |

| bit 7        | 12000                          | DIA                              | I                                                    | 5                                                              | 10.00                                            | I TOI                            | bit             |

|              |                                |                                  |                                                      |                                                                |                                                  |                                  | Dit             |

| Legend:      |                                | C = Clearab                      | ole bit                                              | HS = Hardware                                                  | Settable/Cleara                                  | ble bit                          |                 |

| R = Readab   | le bit                         | W = Writabl                      | e bit                                                | U = Unimpleme                                                  | ented bit, read as                               | s 'O'                            |                 |

| -n = Value a | t POR                          | '1' = Bit is s                   | et                                                   | '0' = Bit is clear                                             | ed                                               | HS = Hardware                    | e Settable bit  |

| bit 15       | 1 = Acknow                     | ledge was no                     | e Status bit (up<br>ot received fro<br>ceived from s | m slave                                                        | ter and Slave m                                  | odes)                            |                 |

| bit 14       | 1 = Master t                   | ransmit is in                    | s bit (when op<br>progress (8 b<br>t in progress     | •                                                              | master; applical                                 | ble to master trai               | nsmit operatior |

| bit 13       | 1 = Indicates                  | s I <sup>2</sup> C bus is i      | n an Acknowl                                         |                                                                |                                                  | g edge of SCLx o<br>c clock      | lock            |

| bit 12-11    | Unimpleme                      | nted: Read a                     | <b>as</b> '0'                                        |                                                                |                                                  |                                  |                 |

| bit 10       | 1 = A bus co                   | ollision has b                   |                                                      | during a master                                                | ared when I <sup>2</sup> C m<br>or slave transmi | nodule is disable<br>t operation | d, I2CEN = 0)   |

| bit 9        | 1 = General                    | call address                     | tatus bit (clea<br>was received<br>was not rece      |                                                                | etection)                                        |                                  |                 |

| bit 8        |                                |                                  |                                                      | ared after Stop d                                              | etection)                                        |                                  |                 |

| bit o        | 1 = 10-bit ac                  | ddress was n<br>ddress was n     | natched                                              |                                                                | eteetiony                                        |                                  |                 |

| bit 7        |                                | mpt to write to<br>are           | sion Detect bi<br>o the I2CxTRI                      |                                                                | because the I <sup>2</sup> C                     | module is busy;                  | must be cleare  |

| bit 6        | 1 = A byte                     | was receive<br>are" in Trans     |                                                      |                                                                |                                                  | the previous by                  | yte; I2COV is   |

| bit 5        | 1 = Indicates<br>0 = Indicates | s that the las<br>s that the las | t byte receive                                       | g as I <sup>2</sup> C slave)<br>d was data<br>d or transmitted | was an address                                   |                                  |                 |

| bit 4        | 1 = Indicates                  | en Start, Res                    | bit has been                                         |                                                                | d when the I <sup>2</sup> C m                    | nodule is disable                | d, I2CEN = 0.   |

| Data Port Size           | PMA<9:8>      | PMA<7:0>    | PMD<7:4>      | PMD<3:0>  | Accessible memory |

|--------------------------|---------------|-------------|---------------|-----------|-------------------|

|                          | Demultiplexed | Address (AI | DRMUX<1:0>    | = 00)     |                   |

| 8-Bit (PTSZ<1:0> = 00)   | Addr<9:8>     | Addr<7:0>   | Da            | ata       | 1K                |

| 4-Bit (PTSZ<1:0> = 01)   | Addr<9:8>     | Addr<7:0>   | _             | Data      | 1K                |

|                          | 1 Address     | Phase (ADRM | /IUX<1:0> = 0 | 1)        |                   |

| 8-Bit (PTSZ<1:0> = 00)   | _             | PMALL       | Addr<7:       | 0> Data   | 1K                |

| 4-Bit (PTSZ<1:0> = 01)   | Addr<9:8>     | PMALL       | Addr<7:4>     | Addr<3:0> | 1K                |

| 4-Dil (P132<1.02 - 01)   | Auui < 9.62   | FIVIALL     | —             | Data (1)  | IK                |

|                          | 2 Address I   | Phases (ADR | MUX<1:0> = 1  | .0)       |                   |

|                          |               | PMALL       | Addr          | <7:0>     |                   |

| 8-Bit (PTSZ<1:0> = 00)   | —             | PMALH       | Addr<         | :15:8>    | 64K               |

|                          |               | —           | Da            | ata       |                   |

|                          |               | PMALL       | Addr          | <3:0>     |                   |

| 4-Bit (PTSZ<1:0> = 01)   | Addr<9:8>     | PMALH       | Addr<7:4>     |           | 1K                |

|                          |               | —           | Da            | ata       |                   |

|                          | 3 Address I   | Phases (ADR | MUX<1:0> = 1  | 1)        |                   |

|                          |               | PMALL       | Addr          | <7:0>     |                   |

| 8-Bit (PTSZ<1:0> = 00)   |               | PMALH       | Addr<         | :15:8>    | 2 Mbytes          |

| 6-Bit (F132 > 1.0 - 0.0) | _             | PMALU       | Addr<         | 22:16>    | 2 Mbytes          |

|                          |               | —           | Da            | ata       |                   |

|                          |               | PMALL       | Addr          | <3:0>     |                   |

| 4-Bit (PTSZ<1:0> = 01)   | Addr<13:12>   | PMALH       | Addr          | <7:4>     | 16K               |

|                          |               | PMALU       |               | <11:8>    |                   |

|                          |               | —           | Da            | ata       |                   |

### TABLE 20-1: MEMORY ADDRESSABLE IN DIFFERENT MODES

### REGISTER 22-1: CRYCONL: CRYPTOGRAPHIC CONTROL LOW REGISTER (CONTINUED)

| bit 7-4 | <b>OPMOD&lt;3:0&gt;:</b> Operating Mode Selection bits <sup>(1,2)</sup>                                               |

|---------|-----------------------------------------------------------------------------------------------------------------------|

|         | 1111 = Loads session key (decrypt session key in CRYTXTA/CRYTXTB using the Key Encryption Key and write to CRYKEY)    |

|         | 1110 = Encrypts session key (encrypt session key in CRYKEY using the Key Encryption Key and write to CRYTXTA/CRYTXTB) |

|         | 1011 = Reserved                                                                                                       |

|         | 1010 = Generate a random number                                                                                       |

|         | 1001                                                                                                                  |

|         | •                                                                                                                     |

|         | • = Reserved                                                                                                          |

|         | •                                                                                                                     |

|         |                                                                                                                       |

|         | 0010 = AES decryption key expansion                                                                                   |

|         | 0001 = Decryption<br>0000 = Encryption                                                                                |

| bit 3   | CPHRSEL: Cipher Engine Select bit <sup>(1,2)</sup>                                                                    |

| DIL 3   |                                                                                                                       |

|         | 1 = AES engine<br>0 = DES engine                                                                                      |

|         | •                                                                                                                     |

| bit 2-0 | CPHRMOD<2:0>: Cipher Mode bits <sup>(1,2)</sup>                                                                       |

|         | 11x = Reserved                                                                                                        |

|         | 101 = Reserved                                                                                                        |

|         | 100 = Counter (CTR) mode                                                                                              |

|         | 011 = Output Feedback (OFB) mode                                                                                      |

|         | 010 = Cipher Feedback (CFB) mode                                                                                      |

|         | 001 = Cipher Block Chaining (CBC) mode                                                                                |

|         | 000 = Electronic Codebook (ECB) mode                                                                                  |

| Note 1  | These bits are react on system Peacets or whenever the CRVMD bit is act                                               |

- **Note 1:** These bits are reset on system Resets or whenever the CRYMD bit is set.

- **2:** Writes to these bit fields are locked out whenever an operation is in progress (CRYGO bit is set).

- **3:** If the device enters Idle mode when CRYSIDL = 1, the module will stop its current operation. Entering into Idle mode while an OTP write operation is in process can result in irreversible corruption of the OTP.

### REGISTER 22-2: CRYCONH: CRYPTOGRAPHIC CONTROL HIGH REGISTER

| U-0    | R/W-0 <sup>(1)</sup>      |

|--------|---------------------------|---------------------------|---------------------------|---------------------------|---------------------------|---------------------------|---------------------------|

|        | CTRSIZE6 <sup>(2,3)</sup> | CTRSIZE5 <sup>(2,3)</sup> | CTRSIZE4 <sup>(2,3)</sup> | CTRSIZE3 <sup>(2,3)</sup> | CTRSIZE2 <sup>(2,3)</sup> | CTRSIZE1 <sup>(2,3)</sup> | CTRSIZE0 <sup>(2,3)</sup> |

| bit 15 |                           |                           |                           |                           |                           |                           | bit 8                     |

| R/W-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup>   | R/W-0 <sup>(1)</sup>   | U-0 | R/W-0 <sup>(1)</sup>   | R/W-0 <sup>(1)</sup>   | R/W-0 <sup>(1)</sup>   | R/W-0 <sup>(1)</sup>   |

|----------------------|------------------------|------------------------|-----|------------------------|------------------------|------------------------|------------------------|

| SKEYSEL              | KEYMOD1 <sup>(2)</sup> | KEYMOD0 <sup>(2)</sup> | —   | KEYSRC3 <sup>(2)</sup> | KEYSRC2 <sup>(2)</sup> | KEYSRC1 <sup>(2)</sup> | KEYSRC0 <sup>(2)</sup> |

| bit 7                |                        |                        |     |                        |                        |                        | bit 0                  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

### bit 15 Unimplemented: Read as '0'

|          | Unimplemented. Read as 0                                                                                                       |

|----------|--------------------------------------------------------------------------------------------------------------------------------|

| bit 14-8 | CTRSIZE<6:0>: Counter Size Select bits <sup>(1,2,3)</sup>                                                                      |