#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betano                     |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART                     |

| Peripherals                | AES, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, HLVD, POR, PWM, WDT        |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                |                                                                                |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 10x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

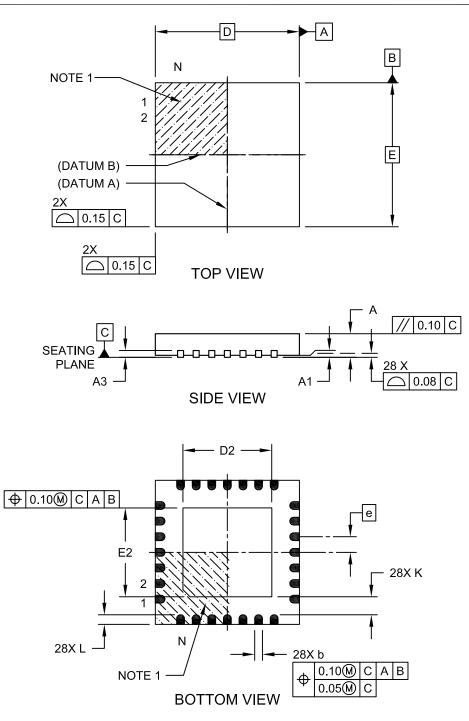

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                 |

| Supplier Device Package    | 28-SSOP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128ga202-i-ss |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|              | Pin Num                       | per/Grid        | Locator            |     |                 |                                       |

|--------------|-------------------------------|-----------------|--------------------|-----|-----------------|---------------------------------------|

| Pin Function | 28-Pin<br>SPDIP/SOIC/<br>SSOP | 28-Pin<br>QFN-S | 44-Pin<br>TQFP/QFN | I/O | Input<br>Buffer | Description                           |

| CN0          | 12                            | 9               | 34                 | —   |                 | Interrupt-on-Change Inputs.           |

| CN1          | 11                            | 8               | 33                 | _   | —               |                                       |

| CN2          | 2                             | 27              | 19                 | —   | —               |                                       |

| CN3          | 3                             | 28              | 20                 | _   | —               |                                       |

| CN4          | 4                             | 1               | 21                 | _   |                 |                                       |

| CN5          | 5                             | 2               | 22                 | _   |                 |                                       |

| CN6          | 6                             | 3               | 23                 | _   |                 |                                       |

| CN7          | 7                             | 4               | 24                 |     |                 |                                       |

| CN8          | _                             |                 | 25                 | _   |                 |                                       |

| CN9          | _                             |                 | 26                 |     |                 |                                       |

| CN10         | —                             |                 | 27                 |     |                 |                                       |

| CN11         | 26                            | 23              | 15                 |     |                 |                                       |

| CN12         | 25                            | 22              | 14                 | _   | _               |                                       |

| CN13         | 24                            | 21              | 11                 | _   | _               |                                       |

| CN14         | 23                            | 20              | 10                 |     |                 |                                       |

| CN15         | 22                            | 19              | 9                  |     |                 |                                       |

| CN16         | 21                            | 18              | 8                  | _   | _               |                                       |

| CN17         | —                             |                 | 3                  |     |                 |                                       |

| CN18         | —                             |                 | 2                  | _   | _               |                                       |

| CN19         | —                             |                 | 5                  | _   | _               |                                       |

| CN20         | —                             |                 | 4                  | _   | —               |                                       |

| CN21         | 18                            | 15              | 1                  | _   | _               |                                       |

| CN22         | 17                            | 14              | 44                 | —   | —               |                                       |

| CN23         | 16                            | 13              | 43                 | —   | —               |                                       |

| CN24         | 15                            | 12              | 42                 |     | —               |                                       |

| CN25         | —                             |                 | 37                 |     | _               |                                       |

| CN26         | —                             | —               | 38                 |     | —               |                                       |

| CN27         | 14                            | 11              | 41                 | _   | —               |                                       |

| CN28         |                               |                 | 36                 | _   |                 |                                       |

| CN29         | 10                            | 7               | 31                 | _   |                 |                                       |

| CN30         | 9                             | 6               | 30                 |     |                 |                                       |

| CN33         | —                             |                 | 13                 | _   |                 |                                       |

| CN34         |                               | _               | 32                 | _   |                 |                                       |

| CN35         | —                             | —               | 35                 | _   | —               |                                       |

| CN36         |                               | _               | 12                 | _   |                 |                                       |

| CTCMP        | 4                             | 1               | 21                 | I   | ANA             | CTMU Comparator 2 Input (Pulse mode). |

#### **TABLE 1-3**: PIC24FJ128GA204 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

ANA = Analog Input  $I^2C$  = ST with  $I^2C^{\text{TM}}$  or SMBus levels

#### TABLE 4-29: DEEP SLEEP REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14                                  | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8     | Bit 7       | Bit 6    | Bit 5 | Bit 4 | Bit 3  | Bit 2   | Bit 1 | Bit 0   | All<br>Resets   |

|--------------|------|--------|-----------------------------------------|--------|--------|--------|--------|---------|-----------|-------------|----------|-------|-------|--------|---------|-------|---------|-----------------|

| DSCON        | 010E | DSEN   | _                                       |        | _      | _      | —      | _       |           | -           | _        | _     | _     |        | r       | DSBOR | RELEASE | 0000(1)         |

| DSWAKE       | 0110 | —      | —                                       | _      | _      | _      | _      | _       | DSINT0    | DSFLT       | _        | _     | DSWDT | DSRTCC | DSMCLR  | _     | _       | 0000(1)         |

| DSGPR0       | 0112 |        |                                         |        |        |        |        | Deep SI | eep Semap | hore Data 0 | Register |       |       |        |         |       |         | 0000 <b>(1)</b> |

| DSGPR1       | 0114 |        | Deep Sleep Semaphore Data 1 Register 00 |        |        |        |        |         |           |             |          |       |       |        | 0000(1) |       |         |                 |

**Legend:** — = unimplemented, read as '0'; r = reserved. Reset values are shown in hexadecimal.

Note 1: These registers are only reset on a VDD POR event.

#### TABLE 4-30: CRYPTOGRAPHIC ENGINE REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14                                        | Bit 13                      | Bit 12   | Bit 11   | Bit 10   | Bit 9     | Bit 8         | Bit 7         | Bit 6          | Bit 5    | Bit 4  | Bit 3   | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|--------------|------|--------|-----------------------------------------------|-----------------------------|----------|----------|----------|-----------|---------------|---------------|----------------|----------|--------|---------|----------|----------|----------|---------------|

| CRYCONL      | 01A4 | CRYON  | —                                             | CRYSIDL                     | ROLLIE   | DONEIE   | FREEIE   | —         | CRYGO         | OPMOD3        | OPMOD2         | OPMOD1   | OPMOD0 | CPHRSEL | CPHRMOD2 | CPHRMOD1 | CPHRMOD0 | 0000          |

| CRYCONH      | 01A6 |        | CTRSIZE6                                      | CTRSIZE5                    | CTRSIZE4 | CTRSIZE3 | CTRSIZE2 | CTRSIZE1  | CTRSIZE0      | SKEYSEL       | KEYMOD1        | KEYMOD0  |        | KEYSRC3 | KEYSRC2  | KEYSRC1  | KEYSRC0  | 0000          |

| CRYSTAT      | 01A8 | I      | _                                             | MODFAIL KEYFAIL PGMFAIL 000 |          |          |          |           |               |               |                |          |        |         | 0000     |          |          |               |

| CRYOTP       | 01AC | I      | _                                             | _                           | _        | _        | _        | _         | —             | PGMTST        | OTPIE          | CRYREAD  | KEYPG3 | KEYPG2  | KEYPG1   | KEYPG0   | CRYWR    | 0020          |

| CRYTXTA      | 01B0 |        |                                               |                             |          |          |          | Crypt     | tographic Tex | kt Register A | (128 bits wi   | de)      |        |         |          |          |          | XXXX          |

| CRYKEY       | 01C0 |        |                                               |                             |          |          |          | Cryptogra | aphic Key Re  | gister (256 l | oits wide, wri | te-only) |        |         |          |          |          | XXXX          |

| CRYTXTB      | 01E0 |        |                                               |                             |          |          |          | Crypt     | tographic Te  | d Register E  | (128 bits wi   | de)      |        |         |          |          |          | XXXX          |

| CRYTXTC      | 01F0 |        | Cryptographic Text Register C (128 bits wide) |                             |          |          |          |           |               |               |                |          |        |         | XXXX     |          |          |               |

Legend: — = unimplemented, read as '0'; x = unknown value on Reset. Reset values are shown in hexadecimal.

#### TABLE 4-31: NVM REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4   | Bit 3       | Bit 2  | Bit 1  | Bit 0  | All<br>Resets   |

|--------------|------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|---------|-------------|--------|--------|--------|-----------------|

| NVMCON       | 0760 | WR     | WREN   | WRERR  | _      | _      |        | _     |       | _     | ERASE | _     | _       | NVMOP3      | NVMOP2 | NVMOP1 | NVMOP0 | 0000 <b>(1)</b> |

| NVMKEY       | 0766 | _      | _      | _      | _      | _      | _      | _     | _     |       |       | 1     | VMKEY R | egister<7:0 | >      |        |        | 0000            |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The Reset value shown is for POR only. The value on other Reset states is dependent on the state of memory write or erase operations at the time of Reset.

#### 5.1.6 CHANNEL PRIORITY

Each DMA channel functions independently of the others, but also competes with the others for access to the data and DMA buses. When access collisions occur, the DMA Controller arbitrates between the channels using a user-selectable priority scheme. Two schemes are available:

- Round Robin: When two or more channels collide, the lower numbered channel receives priority on the first collision. On subsequent collisions, the higher numbered channels each receive priority based on their channel number.

- Fixed Priority: When two or more channels collide, the lowest numbered channel always receives priority, regardless of past history.

#### 5.2 Typical Setup

To set up a DMA channel for a basic data transfer:

- Enable the DMA Controller (DMAEN = 1) and select an appropriate channel priority scheme by setting or clearing PRSSEL.

- 2. Program DMAH and DMAL with appropriate upper and lower address boundaries for data RAM operations.

- 3. Select the DMA channel to be used and disable its operation (CHEN = 0).

- Program the appropriate source and destination addresses for the transaction into the channel's DMASRCn and DMADSTn registers. For PIA Addressing mode, use the base address value.

- 5. Program the DMACNTn register for the number of triggers per transfer (One-Shot or Continuous modes) or the number of words (bytes) to be transferred (Repeated modes).

- 6. Set or clear the SIZE bit to select the data size.

- 7. Program the TRMODE<1:0> bits to select the Data Transfer mode.

- 8. Program the SAMODE<1:0> and DAMODE<1:0> bits to select the addressing mode.

- 9. Enable the DMA channel by setting CHEN.

- 10. Enable the trigger source interrupt.

#### 5.3 Peripheral Module Disable

Unlike other peripheral modules, the channels of the DMA Controller cannot be individually powered down using the Peripheral Module Disable x (PMDx) registers. Instead, the channels are controlled as two groups. The DMA0MD bit (PMD7<4>) selectively controls DMACH0 through DMACH3. The DMA1MD bit (PMD7<5>) controls DMACH4 and DMACH5. Setting both bits effectively disables the DMA Controller.

#### 5.4 Registers

The DMA Controller uses a number of registers to control its operation. The number of registers depends on the number of channels implemented for a particular device.

There are always four module-level registers (one control and three buffer/address):

- DMACON: DMA Control Register (Register 5-1)

- DMAH and DMAL: DMA High and Low Address Limit Registers

- DMABUF: DMA Transfer Data Buffer

Each of the DMA channels implements five registers (two control and three buffer/address):

- DMACHn: DMA Channel n Control Register (Register 5-2)

- DMAINTn: DMA Channel n Interrupt Control Register (Register 5-3)

- DMASRCn: DMA Data Source Address Pointer for Channel n Register

- DMADSTn: DMA Data Destination Source for Channel n Register

- DMACNTn: DMA Transaction Counter for Channel n Register

For PIC24FJ128GA204 family devices, there are a total of 34 registers.

#### 6.6.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

The user can program one row of Flash program memory at a time. To do this, it is necessary to erase the 8-row erase block containing the desired row. The general process is:

- 1. Read eight rows of program memory (512 instructions) and store in data RAM.

- 2. Update the program data in RAM with the desired new data.

- 3. Erase the block (see Example 6-1):

- a) Set the NVMOPx bits (NVMCON<3:0>) to '0010' to configure for block erase. Set the ERASE (NVMCON<6>) and WREN (NVMCON<14>) bits.

- b) Write the starting address of the block to be erased into the TBLPAG and W registers.

- c) Write 55h to NVMKEY.

- d) Write AAh to NVMKEY.

- e) Set the WR bit (NVMCON<15>). The erase cycle begins and the CPU stalls for the duration of the erase cycle. When the erase is done, the WR bit is cleared automatically.

- 4. Write the first 64 instructions from data RAM into the program memory buffers (see Example 6-3).

- 5. Write the program block to Flash memory:

- a) Set the NVMOPx bits to '0001' to configure for row programming. Clear the ERASE bit and set the WREN bit.

- b) Write 55h to NVMKEY.

- c) Write AAh to NVMKEY.

- d) Set the WR bit. The programming cycle begins and the CPU stalls for the duration of the write cycle. When the write to Flash memory is done, the WR bit is cleared automatically.

- 6. Repeat Steps 4 and 5, using the next available 64 instructions from the block in data RAM by incrementing the value in TBLPAG, until all 512 instructions are written back to Flash memory.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS, as shown in Example 6-4.

#### EXAMPLE 6-1: ERASING A PROGRAM MEMORY BLOCK (ASSEMBLY LANGUAGE CODE)

; Set up NVMCON for block erase operation MOV #0×4042, W0 MOV W0, NVMCON ; Initialize NVMCON ; Init pointer to row to be ERASED MOV #tblpage(PROG\_ADDR), W0 ; MOV W0, TBLPAG ; Initialize Program Memory (PM) Page Boundary SFR MOV #tbloffset(PROG ADDR), W0 ; Initialize in-page EA<15:0> pointer TBLWTL WO, [WO] ; Set base address of erase block ; Block all interrupts with priority <7 DISI #5 ; for next 5 instructions MOV.B #0x55, W0 MOV WO. NVMKEY ; Write the 0x55 key MOV.B #0xAA, W1 : MOV W1, NVMKEY ; Write the OxAA key BSET NVMCON, #WR ; Start the erase sequence NOP ; Insert two NOPs after the erase NOP ; command is asserted

#### TABLE 8-2: IMPLEMENTED INTERRUPT VECTORS (CONTINUED)

|                   | Vector | IRQ | IVT     | ΑΙΥΤ    | Inte     | errupt Bit Loca | tions        |

|-------------------|--------|-----|---------|---------|----------|-----------------|--------------|

| Interrupt Source  | #      | #   | Address | Address | Flag     | Enable          | Priority     |

| SPI1 General      | 17     | 9   | 000026h | 000126h | IFS0<9>  | IEC0<9>         | IPC2<6:4>    |

| SPI1 Transmit     | 18     | 10  | 000028h | 000128h | IFS0<10> | IEC0<10>        | IPC2<10:8>   |

| SPI1 Receive      | 66     | 58  | 000088h | 000188h | IFS3<10> | IEC3<10>        | IPC14<10:8>  |

| SPI2 General      | 40     | 32  | 000054h | 000154h | IFS2<0>  | IEC2<0>         | IPC8<2:0>    |

| SPI2 Transmit     | 41     | 33  | 000056h | 000156h | IFS2<1>  | IEC2<1>         | IPC8<6:4>    |

| SPI2 Receive      | 67     | 59  | 00008Ah | 00018Ah | IFS3<11> | IEC3<11>        | IPC14<14:12> |

| SPI3 General      | 98     | 90  | 0000C8h | 0001C8h | IFS5<10> | IEC5<10>        | IPC22<10:8>  |

| SPI3 Transmit     | 99     | 91  | 0000CAh | 0001CAh | IFS5<11> | IEC5<11>        | IPC22<14:12> |

| SPI3 Receive      | 68     | 60  | 000054h | 000154h | IFS3<12> | IEC3<12>        | IPC15<2:0>   |

| Timer1            | 11     | 3   | 00001Ah | 00011Ah | IFS0<3>  | IEC0<3>         | IPC0<14:12>  |

| Timer2            | 15     | 7   | 000022h | 000122h | IFS0<7>  | IEC0<7>         | IPC1<14:12>  |

| Timer3            | 16     | 8   | 000024h | 000124h | IFS0<8>  | IEC0<8>         | IPC2<2:0>    |

| Timer4            | 35     | 27  | 00004Ah | 00014Ah | IFS1<11> | IEC1<11>        | IPC6<14:12>  |

| Timer5            | 36     | 28  | 00004Ch | 00014Ch | IFS1<12> | IEC1<12>        | IPC7<2:0>    |

| UART1 Error       | 73     | 65  | 000096h | 000196h | IFS4<1>  | IEC4<1>         | IPC16<6:4>   |

| UART1 Receiver    | 19     | 11  | 00002Ah | 00012Ah | IFS0<11> | IEC0<11>        | IPC2<14:12>  |

| UART1 Transmitter | 20     | 12  | 00002Ch | 00012Ch | IFS0<12> | IEC0<12>        | IPC3<2:0>    |

| UART2 Error       | 74     | 66  | 000098h | 000198h | IFS4<2>  | IEC4<2>         | IPC16<10:8>  |

| UART2 Receiver    | 38     | 30  | 000050h | 000150h | IFS1<14> | IEC1<14>        | IPC7<10:8>   |

| UART2 Transmitter | 39     | 31  | 000052h | 000152h | IFS1<15> | IEC1<15>        | IPC7<14:12>  |

| UART3 Error       | 89     | 81  | 0000B6h | 0001B6h | IFS5<1>  | IEC5<1>         | IPC20<6:4>   |

| UART3 Receiver    | 90     | 82  | 0000B8h | 0001B8h | IFS5<2>  | IEC5<2>         | IPC20<10:8>  |

| UART3 Transmitter | 91     | 83  | 0000BAh | 0001BAh | IFS5<3>  | IEC5<3>         | IPC20<14:12> |

| UART4 Error       | 95     | 87  | 0000C2h | 0001C2h | IFS5<7>  | IEC5<7>         | IPC21<14:12> |

| UART4 Receiver    | 96     | 88  | 0000C4h | 0001C4h | IFS5<8>  | IEC5<8>         | IPC22<2:0>   |

| UART4 Transmitter | 97     | 89  | 0000C6h | 0001C6h | IFS5<9>  | IEC5<9>         | IPC22<6:4>   |

# PIC24FJ128GA204 FAMILY

| U-0           | R/W-0         | R/W-0                                                  | R/W-0           | R/W-0             | R/W-0            | U-0             | R/W-0    |

|---------------|---------------|--------------------------------------------------------|-----------------|-------------------|------------------|-----------------|----------|

| _             | RTCIF         | DMA5IF                                                 | <b>SPI3RXIF</b> | SPI2RXIF          | SPI1RXIF         | —               | KEYSTRIF |

| pit 15        |               |                                                        |                 |                   |                  |                 | bit 8    |

| R/W-0         | R/W-0         | R/W-0                                                  | U-0             | U-0               | R/W-0            | R/W-0           | U-0      |

| CRYDNIF       | INT4IF        | INT3IF                                                 | —               |                   | MI2C2IF          | SI2C2IF         | —        |

| oit 7         | ·             | ·                                                      |                 |                   |                  |                 | bit 0    |

| Legend:       |               |                                                        |                 |                   |                  |                 |          |

| R = Readabl   | e bit         | W = Writable b                                         | bit             | U = Unimplem      | nented bit, read | l as '0'        |          |

| -n = Value at | POR           | '1' = Bit is set                                       |                 | '0' = Bit is clea | ared             | x = Bit is unkr | nown     |

| bit 15        | Unimplemer    | nted: Read as '                                        | )'              |                   |                  |                 |          |

| oit 14        | -             | -Time Clock/Cale                                       |                 | Flag Status bit   |                  |                 |          |

|               |               | request has occ<br>request has not                     |                 |                   |                  |                 |          |

| oit 13        | •             | IA Channel 5 Int                                       |                 | tus bit           |                  |                 |          |

|               | 1 = Interrupt | request has occ<br>request has not                     | urred           |                   |                  |                 |          |

| oit 12        | •             | PI3 Receive Inte                                       |                 | us bit            |                  |                 |          |

|               |               | request has occ<br>request has not                     |                 |                   |                  |                 |          |

| pit 11        |               | PI2 Receive Inte                                       |                 | us bit            |                  |                 |          |

|               |               | request has occ                                        |                 |                   |                  |                 |          |

|               | 0 = Interrupt | request has not                                        | occurred        |                   |                  |                 |          |

| bit 10        |               | PI1 Receive Inte                                       |                 | us bit            |                  |                 |          |

|               |               | request has occ<br>request has not                     |                 |                   |                  |                 |          |

| oit 9         | -             | nted: Read as '                                        |                 |                   |                  |                 |          |

| bit 8         | 1 = Interrupt | Cryptographic Ko<br>request has occ<br>request has not | urred           | am Done Interro   | upt Flag Status  | bit             |          |

| oit 7         | CRYDNIF: C    | ryptographic Op                                        | eration Done I  | nterrupt Flag St  | atus bit         |                 |          |

|               | •             | request has occ<br>request has not                     |                 |                   |                  |                 |          |

| oit 6         | -             | rnal Interrupt 4                                       |                 |                   |                  |                 |          |

|               |               | request has occ<br>request has not                     |                 |                   |                  |                 |          |

| bit 5         | INT3IF: Exte  | rnal Interrupt 3                                       | -lag Status bit |                   |                  |                 |          |

|               |               | request has occ<br>request has not                     |                 |                   |                  |                 |          |

| bit 4-3       | Unimpleme     | nted: Read as '                                        | )'              |                   |                  |                 |          |

| bit 2         | MI2C2IF: Ma   | ster I2C2 Event                                        | Interrupt Flag  | Status bit        |                  |                 |          |

|               |               | request has occ<br>request has not                     |                 |                   |                  |                 |          |

| bit 1         | SI2C2IF: Sla  | ve I2C2 Event Ir                                       | terrupt Flag St | atus bit          |                  |                 |          |

|               |               | request has occ<br>request has not                     |                 |                   |                  |                 |          |

|               |               | •                                                      |                 |                   |                  |                 |          |

#### REGISTER 8-8: IFS3: INTERRUPT FLAG STATUS REGISTER 3

| U-0          | R/W-0                 | R/W-0                               | R/W-0            | R/W-0            | R/W-0            | U-0             | R/W-0         |

|--------------|-----------------------|-------------------------------------|------------------|------------------|------------------|-----------------|---------------|

| —            | RTCIE                 | DMA5IE                              | <b>SPI3RXIE</b>  | SPI2RXIE         | SPI1RXIE         | —               | KEYSTRIE      |

| bit 15       |                       |                                     |                  |                  |                  |                 | bit 8         |

| R/W-0        | R/W-0                 | R/W-0                               | U-0              | U-0              | R/W-0            | R/W-0           | U-0           |

| CRYDNIE      | INT4IE <sup>(1)</sup> | INT3IE <sup>(1)</sup>               |                  | _                | MI2C2IE          | SI2C2IE         |               |

| bit 7        |                       |                                     |                  |                  |                  |                 | bit 0         |

| Legend:      |                       |                                     |                  |                  |                  |                 |               |

| R = Readab   | ole bit               | W = Writable                        | bit              | U = Unimplen     | nented bit, read | as '0'          |               |

| -n = Value a |                       | '1' = Bit is set                    |                  | '0' = Bit is cle |                  | x = Bit is unki | nown          |

|              |                       | 1 Bit lo cot                        |                  | Bit lo bio       |                  |                 |               |

| bit 15       | Unimplemen            | ted: Read as '                      | 0'               |                  |                  |                 |               |

| bit 14       | RTCIE: Real-          | Time Clock/Ca                       | lendar Interrup  | t Enable bit     |                  |                 |               |

|              |                       | request is enab                     |                  |                  |                  |                 |               |

| bit 13       | •                     | request is not e                    |                  | hit              |                  |                 |               |

| DIC 13       |                       | A Channel 5 In<br>request is enab   | -                | DIL              |                  |                 |               |

|              |                       | request is enaction of e            |                  |                  |                  |                 |               |

| bit 12       | •                     | PI3 Receive Int                     |                  | bit              |                  |                 |               |

|              |                       | request is enab                     | •                |                  |                  |                 |               |

|              | 0 = Interrupt i       | request is not e                    | nabled           |                  |                  |                 |               |

| bit 11       |                       | PI2 Receive Int                     | •                | bit              |                  |                 |               |

|              |                       | request is enab                     |                  |                  |                  |                 |               |

| bit 10       | -                     | request is not e                    |                  | h:+              |                  |                 |               |

|              |                       | PI1 Receive Int<br>request is enab  | •                | DIL              |                  |                 |               |

|              |                       | request is not e                    |                  |                  |                  |                 |               |

| bit 9        | Unimplemen            | ted: Read as '                      | 0'               |                  |                  |                 |               |

| bit 8        | KEYSTRIE: (           | Cryptographic k                     | ey Store Progr   | ram Done Inter   | rupt Enable bit  |                 |               |

|              |                       | request is enab                     |                  |                  |                  |                 |               |

|              | •                     | request is not e                    |                  |                  |                  |                 |               |

| bit 7        |                       |                                     |                  | Interrupt Enable | e bit            |                 |               |

|              |                       | request is enab<br>request is not e |                  |                  |                  |                 |               |

| bit 6        | •                     | nal Interrupt 4                     |                  |                  |                  |                 |               |

|              |                       | request is enab                     |                  |                  |                  |                 |               |

|              | •                     | request is not e                    |                  |                  |                  |                 |               |

| bit 5        |                       | mal Interrupt 3                     |                  |                  |                  |                 |               |

|              |                       | request is enab                     |                  |                  |                  |                 |               |

| bit 4-3      | •                     | request is not e                    |                  |                  |                  |                 |               |

| bit 2        | -                     | ted: Read as '<br>ster I2C2 Even    |                  | hla hit          |                  |                 |               |

|              |                       | request is enab                     | -                |                  |                  |                 |               |

|              |                       | request is not e                    |                  |                  |                  |                 |               |

| Note 1: If   | f an external inte    | rrupt is enabled                    | d. the interrupt | input must also  | be configured    | to an available | e RPn or RPIn |

#### REGISTER 8-16: IEC3: INTERRUPT ENABLE CONTROL REGISTER 3

| U-0          | U-0           | R/W-0                                  | U-0            | U-0               | U-0             | U-0             | R/W-0  |  |  |  |  |  |  |

|--------------|---------------|----------------------------------------|----------------|-------------------|-----------------|-----------------|--------|--|--|--|--|--|--|

| _            | _             | CTMUIE                                 | _              | —                 | —               | _               | HLVDIE |  |  |  |  |  |  |

| oit 15       |               |                                        |                |                   |                 |                 | bit 8  |  |  |  |  |  |  |

|              |               |                                        |                |                   |                 |                 |        |  |  |  |  |  |  |

| U-0          | U-0           | U-0                                    | U-0            | R/W-0             | R/W-0           | R/W-0           | U-0    |  |  |  |  |  |  |

| —            |               | —                                      | —              | CRCIE             | U2ERIE          | U1ERIE          | —      |  |  |  |  |  |  |

| bit 7        |               |                                        |                |                   |                 |                 | bit C  |  |  |  |  |  |  |

|              |               |                                        |                |                   |                 |                 |        |  |  |  |  |  |  |

| Legend:      |               |                                        |                |                   |                 |                 |        |  |  |  |  |  |  |

| R = Readat   |               | W = Writable b                         | oit            | •                 | nented bit, rea |                 |        |  |  |  |  |  |  |

| -n = Value a | at POR        | '1' = Bit is set                       |                | '0' = Bit is clea | ared            | x = Bit is unkn | iown   |  |  |  |  |  |  |

|              |               |                                        |                |                   |                 |                 |        |  |  |  |  |  |  |

| oit 15-14    | •             | nted: Read as '0                       |                |                   |                 |                 |        |  |  |  |  |  |  |

| oit 13       |               | CTMUIE: CTMU Interrupt Enable bit      |                |                   |                 |                 |        |  |  |  |  |  |  |

|              |               | request is enable<br>request is not en |                |                   |                 |                 |        |  |  |  |  |  |  |

| bit 12-9     | •             | nted: Read as '0                       |                |                   |                 |                 |        |  |  |  |  |  |  |

| bit 8        | •             | h/Low-Voltage D                        |                | ot Enable bit     |                 |                 |        |  |  |  |  |  |  |

|              | •             | request is enable                      |                |                   |                 |                 |        |  |  |  |  |  |  |

|              |               | request is not en                      |                |                   |                 |                 |        |  |  |  |  |  |  |

| bit 7-4      | Unimpleme     | nted: Read as '0                       | 3              |                   |                 |                 |        |  |  |  |  |  |  |

| bit 3        | CRCIE: CRC    | Generator Inter                        | rupt Enable b  | bit               |                 |                 |        |  |  |  |  |  |  |

|              |               | request is enable                      |                |                   |                 |                 |        |  |  |  |  |  |  |

|              | 0 = Interrupt | request is not en                      | abled          |                   |                 |                 |        |  |  |  |  |  |  |

| bit 2        | U2ERIE: UA    | RT2 Error Interru                      | ipt Enable bit |                   |                 |                 |        |  |  |  |  |  |  |

|              |               | request is enable                      |                |                   |                 |                 |        |  |  |  |  |  |  |

|              | •             | request is not en                      |                |                   |                 |                 |        |  |  |  |  |  |  |

| bit 1        |               | RT1 Error Interru                      |                |                   |                 |                 |        |  |  |  |  |  |  |

|              | •             | request is enable<br>request is not en |                |                   |                 |                 |        |  |  |  |  |  |  |

| bit 0        | •             | nted: Read as '0                       |                |                   |                 |                 |        |  |  |  |  |  |  |

|              | Simplemen     |                                        |                |                   |                 |                 |        |  |  |  |  |  |  |

#### REGISTER 8-17: IEC4: INTERRUPT ENABLE CONTROL REGISTER 4

#### REGISTER 13-1: TxCON: TIMER2 AND TIMER4 CONTROL REGISTER<sup>(1)</sup> (CONTINUED)

- bit 3 **T32:** 32-Bit Timer Mode Select bit<sup>(3)</sup>

- 1 = Timerx and Timery form a single 32-bit timer

- 0 = Timerx and Timery act as two 16-bit timers

- In 32-bit mode, T3CON control bits do not affect 32-bit timer operation.

- bit 2 Unimplemented: Read as '0'

- bit 1 **TCS**: Timerx Clock Source Select bit<sup>(2)</sup>

- 1 = Timer source is selected by TECS<1:0>0 = Internal clock (Fosc/2)

- bit 0 Unimplemented: Read as '0'

- **Note 1:** Changing the value of TxCON while the timer is running (TON = 1) causes the timer prescale counter to reset and is not recommended.

- 2: If TCS = 1 and TECS<1:0> = x1, the selected external timer input (TMRCK or TxCK) must be configured to an available RPn/RPIn pin. For more information, see Section 11.4 "Peripheral Pin Select (PPS)".

- **3:** In T4CON, the T45 bit is implemented instead of T32 to select 32-bit mode. In 32-bit mode, the T3CON or T5CON control bits do not affect 32-bit timer operation.

#### REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2 (CONTINUED)

- bit 4-0 SYNCSEL<4:0>: Synchronization/Trigger Source Selection bits

- 1111x = Reserved

- 11101 = Reserved

- 11100 = CTMU<sup>(1)</sup>

- 11011 = A/D<sup>(1)</sup>

- $11010 = \text{Comparator 3}^{(1)}$

- 11001 = Comparator 2<sup>(1)</sup>

- 11000 = Comparator 1<sup>(1)</sup>

- 10111 = Reserved

- 10110 = Reserved

- 10101 = Input Capture  $6^{(2)}$

- 10100 = Input Capture 5<sup>(2)</sup> 10011 = Input Capture 4<sup>(2)</sup>

- $10011 = \text{Input Capture 4}^{(1)}$  $10010 = \text{Input Capture 3}^{(2)}$

- 10010 = Input Capture 3(\*)10001 = Input Capture 2(2)

- $10001 = \text{Input Capture 2}^{(7)}$  $10000 = \text{Input Capture 1}^{(2)}$

- 01111 = Timer5

- 01110 = Timer3

- 01101 = Timer3

- 01100 = Timer3

- 01011 = Timer1

- 01010 = **Reserved**

- 01001 = Reserved

- 01000 = Reserved

- 00111 = **Reserved**

- 00110 = Output Compare 6

- 00101 = Output Compare 5

- 00100 = Output Compare 4

- 00011 = Output Compare 3

- 00010 = Output Compare 2

- 00001 = Output Compare 1

- 00000 = Not synchronized to any other module

- Note 1: Use these inputs as trigger sources only and never as sync sources.

- 2: Never use an ICx module as its own trigger source by selecting this mode.

#### 15.0 OUTPUT COMPARE WITH DEDICATED TIMERS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Output Compare with Dedicated Timer" (DS70005159). The information in this data sheet supersedes the information in the FRM.

Devices in the PIC24FJ128GA204 family all feature six independent output compare modules. Each of these modules offers a wide range of configuration and operating options for generating pulse trains on internal device events, and can produce Pulse-Width Modulated (PWM) waveforms for driving power applications.

Key features of the output compare module include:

- Hardware-configurable for 32-bit operation in all modes by cascading two adjacent modules

- Synchronous and Trigger modes of output compare operation, with up to 31 user-selectable trigger/sync sources available

- Two separate Period registers (a main register, OCxR, and a secondary register, OCxRS) for greater flexibility in generating pulses of varying widths

- Configurable for single pulse or continuous pulse generation on an output event, or continuous PWM waveform generation

- Up to 6 clock sources available for each module, driving a separate internal 16-bit counter

#### 15.1 General Operating Modes

#### 15.1.1 SYNCHRONOUS AND TRIGGER MODES

When the output compare module operates in a Free-Running mode, the internal 16-bit counter, OCxTMR, runs counts up continuously, wrapping around from 0xFFFF to 0x0000 on each overflow. Its period is synchronized to the selected external clock source. Compare or PWM events are generated each time a match between the internal counter and one of the Period registers occurs. In Synchronous mode, the module begins performing its compare or PWM operation as soon as its selected clock source is enabled. Whenever an event occurs on the selected sync source, the module's internal counter is reset. In Trigger mode, the module waits for a sync event from another internal module to occur before allowing the counter to run.

Free-Running mode is selected by default or any time that the SYNCSEL<4:0> bits (OCxCON2<4:0>) are set to '00000'. Synchronous or Trigger modes are selected any time the SYNCSELx bits are set to any value except '00000'. The OCTRIG bit (OCxCON2<7>) selects either Synchronous or Trigger mode; setting the bit selects Trigger mode operation. In both modes, the SYNCSELx bits determine the sync/trigger source.

#### 15.1.2 CASCADED (32-BIT) MODE

By default, each module operates independently with its own set of 16-bit Timer and Duty Cycle registers. To increase resolution, adjacent even and odd modules can be configured to function as a single 32-bit module. (For example, Modules 1 and 2 are paired, as are Modules 3 and 4, and so on.) The odd numbered module, Output Compare x (OCx), provides the Least Significant 16 bits of the 32-bit register pairs and the even numbered module, Output Compare y (OCy), provides the Most Significant 16 bits. Wrap arounds of the OCx registers cause an increment of their corresponding OCy registers.

Cascaded operation is configured in hardware by setting the OC32 bit (OCxCON2<8>) for both modules. For more information on cascading, refer to the *"dsPIC33/PIC24 Family Reference Manual"*, **"Output Compare with Dedicated Timer"** (DS70005159).

# PIC24FJ128GA204 FAMILY

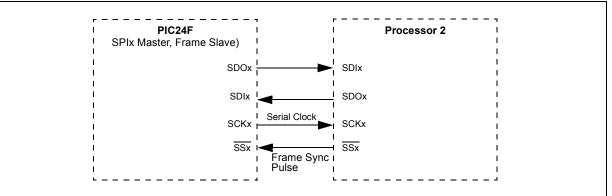

FIGURE 16-6: SPIx MASTER, FRAME SLAVE CONNECTION DIAGRAM

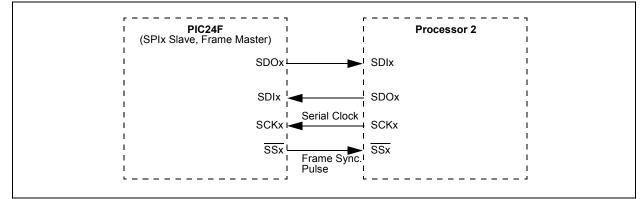

#### FIGURE 16-7: SPIx SLAVE, FRAME MASTER CONNECTION DIAGRAM

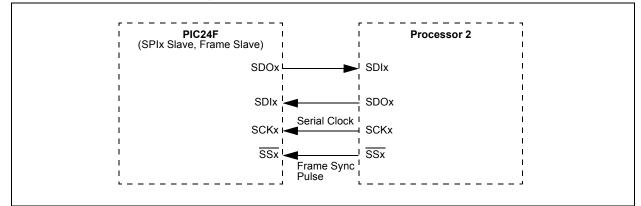

#### FIGURE 16-8: SPIx SLAVE, FRAME SLAVE CONNECTION DIAGRAM

#### EQUATION 16-1: RELATIONSHIP BETWEEN DEVICE AND SPIX CLOCK SPEED

$$Baud Rate = \frac{FPB}{(2 * (SPIxBRG + 1))}$$

Where:

FPB is the Peripheral Bus Clock Frequency.

#### 18.1 UARTx Baud Rate Generator (BRG)

The UARTx module includes a dedicated, 16-bit Baud Rate Generator. The UxBRG register controls the period of a free-running, 16-bit timer. Equation 18-1 shows the formula for computation of the baud rate when BRGH = 0.

## EQUATION 18-1: UARTx BAUD RATE WITH BRGH = $0^{(1,2)}$

$$Baud Rate = \frac{FCY}{16 \cdot (UxBRG + 1)}$$

$$UxBRG = \frac{FCY}{16 \cdot Baud Rate} - 1$$

Note 1: FCY denotes the instruction cycle clock frequency (FOSC/2).

2: Based on FCY = FOSC/2; Doze mode and PLL are disabled.

Example 18-1 shows the calculation of the baud rate error for the following conditions:

- Fcy = 4 MHz

- Desired Baud Rate = 9600

The maximum baud rate (BRGH = 0) possible is FCY/16 (for UxBRG = 0) and the minimum baud rate possible is FCY/(16 \* 65536).

Equation 18-2 shows the formula for computation of the baud rate when BRGH = 1.

## EQUATION 18-2: UARTX BAUD RATE WITH BRGH = $1^{(1,2)}$

$$Baud Rate = \frac{FCY}{4 \cdot (UxBRG + 1)}$$

$$UxBRG = \frac{FCY}{4 \cdot Baud Rate} - 1$$

- **Note 1:** FCY denotes the instruction cycle clock frequency.

- **2:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

The maximum baud rate (BRGH = 1) possible is FcY/4 (for UxBRG = 0) and the minimum baud rate possible is FcY/(4 \* 65536).

Writing a new value to the UxBRG register causes the BRG timer to be reset (cleared). This ensures the BRG does not wait for a timer overflow before generating the new baud rate.

#### EXAMPLE 18-1: BAUD RATE ERROR CALCULATION (BRGH = 0)<sup>(1)</sup>

Desired Baud Rate = FCY/(16 (UxBRG + 1))Solving for UxBRG Value: **UxBRG** = ((FCY/Desired Baud Rate)/16) - 1**UxBRG** = ((400000/9600)/16) - 1UxBRG = 25 Calculated Baud Rate = 4000000/(16(25+1))= 9615 Error = (Calculated Baud Rate – Desired Baud Rate) Desired Baud Rate = (9615 - 9600)/9600 = 0.16% Note 1: Based on FCY = FOSC/2; Doze mode and PLL are disabled.

#### 21.3.2 RTCVAL REGISTER MAPPINGS

#### **REGISTER 21-4:** YEAR: YEAR VALUE REGISTER<sup>(1)</sup>

| U-0    |

|--------|--------|--------|--------|--------|--------|--------|--------|

| —      | —      | —      | —      | —      | —      | —      | —      |

| bit 15 |        |        |        |        |        |        | bit 8  |

|        |        |        |        |        |        |        |        |

| R/W-x  |

| YRTEN3 | YRTEN2 | YRTEN2 | YRTEN1 | YRONE3 | YRONE2 | YRONE1 | YRONE0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15-8 Unimplemented: Read as '0'

bit 7-4 **YRTEN<3:0>:** Binary Coded Decimal Value of Year's Tens Digit bits Contains a value from 0 to 9.

bit 3-0 **YRONE<3:0>:** Binary Coded Decimal Value of Year's Ones Digit bits Contains a value from 0 to 9.

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

#### REGISTER 21-5: MTHDY: MONTH AND DAY VALUE REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   |

|--------|-----|-----|---------|---------|---------|---------|---------|

| —      | —   | —   | MTHTEN0 | MTHONE3 | MTHONE2 | MTHONE1 | MTHONE0 |

| bit 15 |     |     |         |         |         |         | bit 8   |

| U-0   | U-0 | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   |

|-------|-----|---------|---------|---------|---------|---------|---------|

|       | —   | DAYTEN1 | DAYTEN0 | DAYONE3 | DAYONE2 | DAYONE1 | DAYONE0 |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'                                                                                    |

|-----------|---------------------------------------------------------------------------------------------------------------|

| bit 12    | <b>MTHTEN0:</b> Binary Coded Decimal Value of Month's Tens Digit bit Contains a value of '0' or '1'.          |

| bit 11-8  | <b>MTHONE&lt;3:0&gt;:</b> Binary Coded Decimal Value of Month's Ones Digit bits Contains a value from 0 to 9. |

| bit 7-6   | Unimplemented: Read as '0'                                                                                    |

| bit 5-4   | <b>DAYTEN&lt;1:0&gt;:</b> Binary Coded Decimal Value of Day's Tens Digit bits Contains a value from 0 to 3.   |

| bit 3-0   | <b>DAYONE&lt;3:0&gt;:</b> Binary Coded Decimal Value of Day's Ones Digit bits Contains a value from 0 to 9.   |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

# PIC24FJ128GA204 FAMILY

| R/W-0                        | R-0                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W-0                                                       | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |  |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-------|-------------------|------------------|-----------------|-------|--|

| ADRC                         | EXTSAM                                                                                                                                                                                                                                                                                                                                                                                                              | PUMPEN                                                      | SAMC4 | SAMC3             | SAMC2            | SAMC1           | SAMC0 |  |

| bit 15                       |                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                             |       |                   |                  | •               | bit 8 |  |

| R/W-0                        | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0                                                       | R/W-0 | R/W-0             | R/W-0            | R/W-0           | R/W-0 |  |

| ADCS7                        | ADCS6                                                                                                                                                                                                                                                                                                                                                                                                               | ADCS5                                                       | ADCS4 | ADCS3             | ADCS2            | ADCS1           | ADCS0 |  |

| bit 7                        | I                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                             |       |                   |                  |                 | bit ( |  |

| Legend:                      |                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                             |       |                   |                  |                 |       |  |

| R = Readab                   | le bit                                                                                                                                                                                                                                                                                                                                                                                                              | W = Writable                                                | oit   | U = Unimplen      | nented bit, read | d as '0'        |       |  |

| -n = Value a                 | t POR                                                                                                                                                                                                                                                                                                                                                                                                               | '1' = Bit is set                                            |       | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |  |

| bit 14<br>bit 13<br>bit 12-8 | <ul> <li>1 = RC clock</li> <li>0 = Clock derived from system clock</li> <li>EXTSAM: Extended Sampling Time bit</li> <li>1 = A/D is still sampling after SAMP = 0</li> <li>0 = A/D is finished sampling</li> <li>PUMPEN: Charge Pump Enable bit</li> <li>1 = Charge pump for switches is enabled</li> <li>0 = Charge pump for switches is disabled</li> <li>SAMC&lt;4:0&gt;: Auto-Sample Time Select bits</li> </ul> |                                                             |       |                   |                  |                 |       |  |

| bit 7-0                      |                                                                                                                                                                                                                                                                                                                                                                                                                     | ND<br>ND<br>A/D Conversio<br>256 • Tcy = Tat<br>2•Tcy = Tad |       | bits              |                  |                 |       |  |

#### REGISTER 24-3: AD1CON3: A/D CONTROL REGISTER 3

#### REGISTER 24-9: AD1CSSH: A/D INPUT SCAN SELECT REGISTER (HIGH WORD)

| R/W-0                              | R/W-0 | R/W-0            | R/W-0 | R/W-0                              | U-0 | U-0             | U-0                |  |

|------------------------------------|-------|------------------|-------|------------------------------------|-----|-----------------|--------------------|--|

|                                    |       | CSS<31:27>       |       |                                    |     | _               | _                  |  |

| bit 15                             |       |                  |       |                                    |     |                 | bit 8              |  |

|                                    |       |                  |       |                                    |     |                 |                    |  |

| U-0                                | U-0   | U-0              | U-0   | U-0                                | U-0 | U-0             | U-0                |  |

| —                                  | _     | —                | —     | —                                  | —   | —               | —                  |  |

| bit 7                              |       |                  |       |                                    |     |                 | bit 0              |  |

|                                    |       |                  |       |                                    |     |                 |                    |  |

| Legend:                            |       |                  |       |                                    |     |                 |                    |  |

| R = Readable                       | e bit | W = Writable b   | bit   | U = Unimplemented bit, read as '0' |     |                 |                    |  |

| -n = Value at POR '1' = Bit is set |       | '1' = Bit is set |       | '0' = Bit is cleared x             |     | x = Bit is unkr | κ = Bit is unknown |  |

1 = Includes corresponding channel for input scan

0 = Skips channel for input scan

bit 10-0 Unimplemented: Read as '0'

#### REGISTER 24-10: AD1CSSL: A/D INPUT SCAN SELECT REGISTER (LOW WORD)

| U-0    | R/W-0                    | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|--------------------------|-------|-------|-------|-------|-------|-------|

|        | CSS<14:8> <sup>(1)</sup> |       |       |       |       |       |       |

| bit 15 |                          |       |       |       |       |       | bit 8 |

| R/W-0 | R/W-0    | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |

|-------|----------|-------|-------|-------|-------|-------|-------|--|--|--|--|

|       | CSS<7:0> |       |       |       |       |       |       |  |  |  |  |

| bit 7 |          |       |       |       |       |       |       |  |  |  |  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15 Unimplemented: Read as '0'

bit 14-0 CSS<14:0>: A/D Input Scan Selection bits<sup>(1)</sup>

1 = Includes corresponding channel for input scan

0 = Skips channel for input scan

Note 1: The CSS<12:10> bits are unimplemented in 28-pin devices, read as '0'.

#### REGISTER 26-1: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER

| U-0                  | U-0                                                                                                                                      | U-0                                                                                                                                                        | U-0                                                                                                                                        | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W-0            | R/W-0           | R/W-0         |  |  |  |  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------|---------------|--|--|--|--|

| _                    | —                                                                                                                                        | —                                                                                                                                                          | _                                                                                                                                          | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CVREFP           | CVREFM1         | CVREFM0       |  |  |  |  |

| bit 15               |                                                                                                                                          |                                                                                                                                                            |                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                  |                 | bit 8         |  |  |  |  |

|                      | 5444                                                                                                                                     |                                                                                                                                                            |                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                  | 5444.0          |               |  |  |  |  |