#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART                      |

| Peripherals                | AES, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, HLVD, POR, PWM, WDT         |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

| Data Converters            | A/D 10x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 28-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128ga202t-i-so |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

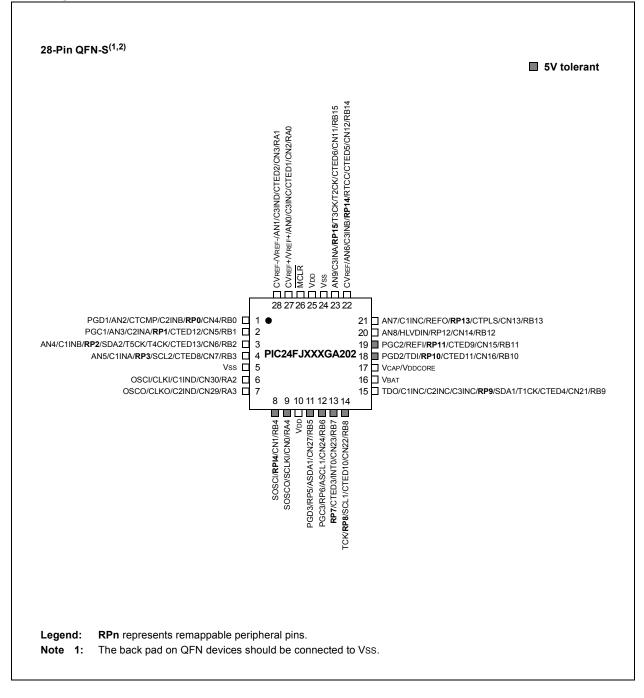

#### Pin Diagrams (Continued)

### 1.0 DEVICE OVERVIEW

This document contains device-specific information for the following devices:

- PIC24FJ64GA202 PIC24FJ128GA202

- PIC24FJ64GA204 PIC24FJ128GA204

The PIC24FJ128GA204 family expands the capabilities of the PIC24F family by adding a complete selection of Cryptographic Engines, ISO 7816 support and I<sup>2</sup>S support to its existing features. This combination, along with its ultra low-power features and Direct Memory Access (DMA) for peripherals, make this family the new standard for mixed-signal PIC<sup>®</sup> microcontrollers in one economical and power-saving package.

#### 1.1 Core Features

#### 1.1.1 16-BIT ARCHITECTURE

Central to all PIC24F devices is the 16-bit modified Harvard architecture, first introduced with Microchip's dsPIC<sup>®</sup> Digital Signal Controllers (DSCs). The PIC24F CPU core offers a wide range of enhancements, such as:

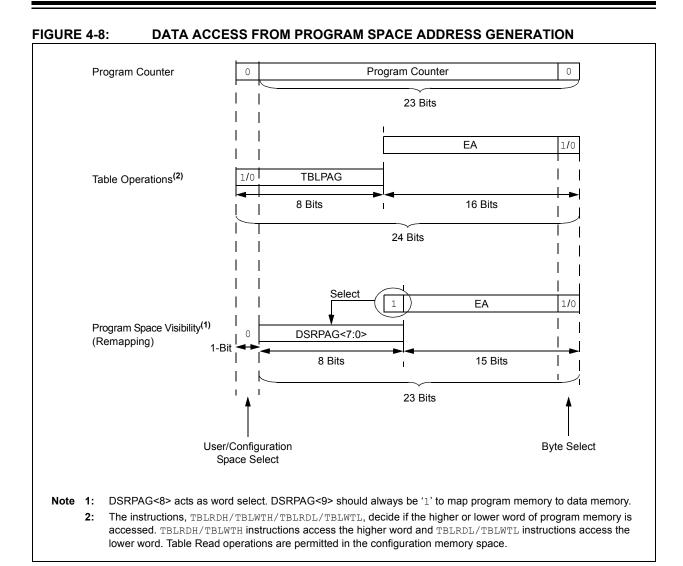

- 16-bit data and 24-bit address paths with the ability to move information between data and memory spaces

- Linear addressing of up to 12 Mbytes (program space) and 32 Kbytes (data)

- A 16-element Working register array with built-in software stack support

- A 17 x 17 hardware multiplier with support for integer math

- Hardware support for 32 by 16-bit division

- An instruction set that supports multiple addressing modes and is optimized for high-level languages, such as 'C'

- Operational performance up to 16 MIPS

#### 1.1.2 XLP POWER-SAVING TECHNOLOGY

The PIC24FJ128GA204 family of devices introduces a greatly expanded range of power-saving operating modes for the ultimate in power conservation. The new modes include:

- Retention Sleep, with essential circuits being powered from a separate low-voltage regulator

- Deep Sleep without RTCC, for the lowest possible power consumption under software control

- VBAT mode (with or without RTCC), to continue limited operation from a backup battery when VDD is removed

Many of these new low-power modes also support the continuous operation of the low-power, on-chip Real-Time Clock/Calendar (RTCC), making it possible for an application to keep time while the device is otherwise asleep.

Aside from these new features, PIC24FJ128GA204 family devices also include all of the legacy power-saving features of previous PIC24F microcontrollers, such as:

- On-the-Fly Clock Switching, allowing the selection of a lower power clock during run time

- Doze Mode Operation, for maintaining peripheral clock speed while slowing the CPU clock

- Instruction-Based Power-Saving Modes, for quick invocation of Idle and the many Sleep modes

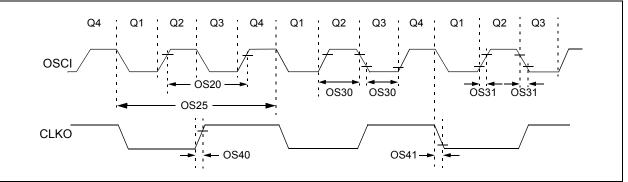

### 1.1.3 OSCILLATOR OPTIONS AND FEATURES

All of the devices in the PIC24FJ128GA204 family offer five different oscillator options, allowing users a range of choices in developing application hardware. These include:

- Two Crystal modes

- Two External Clock modes

- A Phase-Locked Loop (PLL) frequency multiplier, which allows clock speeds of up to 32 MHz

- A Fast Internal Oscillator (FRC) nominal 8 MHz output with multiple frequency divider options and automatic frequency self-calibration during run time

- A separate, Low-Power Internal RC Oscillator (LPRC) – 31 kHz nominal, for low-power, timing-insensitive applications.

The internal oscillator block also provides a stable reference source for the Fail-Safe Clock Monitor (FSCM). This option constantly monitors the main clock source against a reference signal provided by the internal oscillator and enables the controller to switch to the internal oscillator, allowing for continued low-speed operation or a safe application shutdown.

#### 1.1.4 EASY MIGRATION

Regardless of the memory size, all devices share the same rich set of peripherals, allowing for a smooth migration path as applications grow and evolve. This extends the ability of applications to grow from the relatively simple, to the powerful and complex, yet still selecting a Microchip device.

#### TABLE 4-11: SPI1 REGISTER MAP

| File<br>Name | Addr | Bit 15           | Bit 14    | Bit 13  | Bit 12   | Bit 11  | Bit 10 | Bit 9   | Bit 8    | Bit 7     | Bit 6       | Bit 5   | Bit 4  | Bit 3   | Bit 2   | Bit 1    | Bit 0    | All<br>Resets |

|--------------|------|------------------|-----------|---------|----------|---------|--------|---------|----------|-----------|-------------|---------|--------|---------|---------|----------|----------|---------------|

| SPI1CON1L    | 0300 | SPIEN            | —         | SPISIDL | DISSDO   | MODE32  | MODE16 | SMP     | CKE      | SSEN      | CKP         | MSTEN   | DISSDI | DISSCK  | MCLKEN  | SPIFE    | ENHBUF   | 0000          |

| SPI1CON1H    | 0302 | AUDEN            | SPISGNEXT | IGNROV  | IGNTUR   | AUDMONO | URDTEN | AUDMOD1 | AUDMOD0  | FRMEN     | FRMSYNC     | FRMPOL  | MSSEN  | FRMSYPW | FRMCNT2 | FRMCNT1  | FRMCNT0  | 0000          |

| SPI1CON2L    | 0304 |                  |           |         |          |         |        |         |          |           |             | 0000    |        |         |         |          |          |               |

| SPI1STATL    | 0308 | _                | _         | -       | FRMERR   | SPIBUSY | _      | _       | SPITUR   | SRMT      | SPIROV      | SPIRBE  | _      | SPITBE  | _       | SPITBF   | SPIRBF   | 0028          |

| SPI1STATH    | 030A | _                | _         | RXELM5  | RXELM4   | RXELM3  | RXELM2 | RXELM1  | RXELM0   | _         | _           | TXELM5  | TXELM4 | TXELM3  | TXELM2  | TXELM1   | TXELM0   | 0000          |

| SPI1BUFL     | 030C |                  |           |         |          |         |        |         | SPI1BU   | FL<15:0>  |             |         |        |         |         |          |          | 0000          |

| SPI1BUFH     | 030E |                  |           |         |          |         |        |         | SPI1BUI  | =H<31:16> |             |         |        |         |         |          |          | 0000          |

| SPI1BRGL     | 0310 | _                | _         | _       |          |         |        |         |          | SP        | 11BRG<12:0> |         |        |         |         |          |          | 0000          |

| SPI1IMSKL    | 0314 | _                | _         | _       | FRMERREN | BUSYEN  | _      | _       | SPITUREN | SRMTEN    | SPIROVEN    | SPIRBEN | _      | SPITBEN | _       | SPITBFEN | SPIRBFEN | 0000          |

| SPI1IMSKH    | 0316 | RXWIEN           | _         | RXMSK5  | RXMSK4   | RXMSK3  | RXMSK2 | RXMSK1  | RXMSK0   | TXWIEN    | _           | TXMSK5  | TXMSK4 | TXMSK3  | TXMSK2  | TXMSK1   | TXMSK0   | 0000          |

| SPI1URDTL    | 0318 |                  |           |         |          |         |        |         | SPI1URI  | DTL<15:0> |             |         |        |         |         |          |          | 0000          |

| SPI1URDTH    | 031A | SPI1URDTH<31:16> |           |         |          |         |        |         |          |           |             | 0000    |        |         |         |          |          |               |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-12: SPI2 REGISTER MAP

| File      | Addr | Bit 15       | Bit 14    | Bit 13  | Bit 12   | Bit 11  | Bit 10 | Bit 9   | Bit 8    | Bit 7      | Bit 6       | Bit 5   | Bit 4  | Bit 3   | Bit 2   | Bit 1    | Bit 0    | All    |

|-----------|------|--------------|-----------|---------|----------|---------|--------|---------|----------|------------|-------------|---------|--------|---------|---------|----------|----------|--------|

| Name      | Auui | Dit 10       | Dit 14    | Dit 10  | DICIZ    | DICH    | Dit IV | Dity    | Ditto    | Diti       | Diro        | Dito    | Dit 4  | Ditto   | Dit 2   | Dit i    | Ditt     | Resets |

| SPI2CON1L | 031C | SPIEN        | _         | SPISIDL | DISSDO   | MODE32  | MODE16 | SMP     | CKE      | SSEN       | CKP         | MSTEN   | DISSDI | DISSCK  | MCLKEN  | SPIFE    | ENHBUF   | 0000   |

| SPI2CON1H | 031E | AUDEN        | SPISGNEXT | IGNROV  | IGNTUR   | AUDMONO | URDTEN | AUDMOD1 | AUDMOD0  | FRMEN      | FRMSYNC     | FRMPOL  | MSSEN  | FRMSYPW | FRMCNT2 | FRMCNT1  | FRMCNT0  | 0000   |

| SPI2CON2L | 0320 | WLENGTH<4:0> |           |         |          |         |        |         |          |            | 0000        |         |        |         |         |          |          |        |

| SPI2STATL | 0324 | _            | _         | _       | FRMERR   | SPIBUSY | _      | _       | SPITUR   | SRMT       | SPIROV      | SPIRBE  | _      | SPITBE  | _       | SPITBF   | SPIRBF   | 0028   |

| SPI2STATH | 0326 | _            | _         | RXELM5  | RXELM4   | RXELM3  | RXELM2 | RXELM1  | RXELM0   | _          | _           | TXELM5  | TXELM4 | TXELM3  | TXELM2  | TXELM1   | TXELM0   | 0000   |

| SPI2BUFL  | 0328 |              |           |         |          |         |        |         | SPI2B    | JFL<15:0>  |             |         |        |         |         |          |          | 0000   |

| SPI2BUFH  | 032A |              |           |         |          |         |        |         | SPI2BL   | IFH<31:16> |             |         |        |         |         |          |          | 0000   |

| SPI2BRGL  | 032C | _            | _         | _       |          |         |        |         |          | S          | PI2BRG<12:0 | >       |        |         |         |          |          | 0000   |

| SPI2IMSKL | 0330 |              | _         | _       | FRMERREN | BUSYEN  | _      | _       | SPITUREN | SRMTEN     | SPIROVEN    | SPIRBEN | _      | SPITBEN | _       | SPITBFEN | SPIRBFEN | 0000   |

| SPI2IMSKH | 0332 | RXWIEN       | _         | RXMSK5  | RXMSK4   | RXMSK3  | RXMSK2 | RXMSK1  | RXMSK0   | TXWIEN     | _           | TXMSK5  | TXMSK4 | TXMSK3  | TXMSK2  | TXMSK1   | TXMSK0   | 0000   |

| SPI2URDTL | 0334 |              |           |         |          |         |        |         | SPI2UF   | RDTL<15:0> |             |         |        |         |         |          |          | 0000   |

| SPI2URDTH | 0336 |              |           |         |          |         |        |         | SPI2UR   | DTH<31:16> |             |         |        |         |         |          |          | 0000   |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### REGISTER 7-1: RCON: RESET CONTROL REGISTER (CONTINUED)

| bit 5   | <b>SWDTEN:</b> Software Enable/Disable of WDT bit <sup>(4)</sup><br>1 = WDT is enabled<br>0 = WDT is disabled                            |

|---------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4   | WDTO: Watchdog Timer Time-out Flag bit <sup>(1)</sup><br>1 = WDT time-out has occurred<br>0 = WDT time-out has not occurred              |

| bit 3   | SLEEP: Wake from Sleep Flag bit <sup>(1)</sup>                                                                                           |

|         | <ul><li>1 = Device has been in Sleep mode</li><li>0 = Device has not been in Sleep mode</li></ul>                                        |

| bit 2   | IDLE: Wake from Idle Flag bit <sup>(1)</sup>                                                                                             |

|         | <ul><li>1 = Device has been in Idle mode</li><li>0 = Device has not been in Idle mode</li></ul>                                          |

| bit 1   | BOR: Brown-out Reset Flag bit <sup>(1)</sup>                                                                                             |

|         | <ul> <li>1 = A Brown-out Reset has occurred (also set after a Power-on Reset)</li> <li>0 = A Brown-out Reset has not occurred</li> </ul> |

| bit 0   | <b>POR:</b> Power-on Reset Flag bit <sup>(1)</sup>                                                                                       |

|         | <ul><li>1 = A Power-on Reset has occurred</li><li>0 = A Power-on Reset has not occurred</li></ul>                                        |

| Noto 1: | All of the Reset status hits may be set or cleared in software. Setting one of                                                           |

- **Note 1:** All of the Reset status bits may be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the LPCFG Configuration bit is '1' (unprogrammed), the retention regulator is disabled and the RETEN bit has no effect.

- **3:** Re-enabling the regulator after it enters Standby mode will add a delay, TVREG, when waking up from Sleep. Applications that do not use the voltage regulator should set this bit to prevent this delay from occurring.

- 4: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

#### 8.3 Interrupt Control and Status Registers

The PIC24FJ128GA204 family of devices implements a total of 43 registers for the interrupt controller:

- INTCON1

- INTCON2

- IFS0 through IFS7

- IEC0 through IEC7

- IPC0 through IPC16, IPC18 through IPC22, IPC26 and IPC29

- INTTREG

Global interrupt control functions are controlled from INTCON1 and INTCON2. INTCON1 contains the Interrupt Nesting Disable (NSTDIS) bit, as well as the control and status flags for the processor trap sources. The INTCON2 register controls the external interrupt request signal behavior and the use of the Alternate Interrupt Vector Table (AIVT).

The IFSx registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or an external signal and is cleared via software.

The IECx registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

The IPCx registers are used to set the Interrupt Priority Level (IPL) for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels.

The INTTREG register contains the associated interrupt vector number and the new CPU Interrupt Priority Level, which are latched into the Vector Number (VECNUM<7:0>) and the Interrupt Priority Level (ILR<3:0>) bit fields in the INTTREG register. The new Interrupt Priority Level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx and IPCx registers in the order of their vector numbers, as shown in Table 8-2. For example, the INT0 (External Interrupt 0) is shown as having a vector number and a natural order priority of 0. Thus, the INT0IF status bit is found in IFS0<0>, the INT0IE enable bit in IEC0<0> and the INT0IP<2:0> priority bits in the first position of IPC0 (IPC0<2:0>).

Although they are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality. The ALU STATUS Register (SR) contains the IPL<2:0> bits (SR<7:5>). These indicate the current CPU Interrupt Priority Level. The user can change the current CPU priority level by writing to the IPLx bits.

The CORCON register contains the IPL3 bit, which together with the IPL<2:0> bits, indicates the current CPU priority level. IPL3 is a read-only bit so that trap events cannot be masked by the user software.

The interrupt controller has the Interrupt Controller Test register, INTTREG, which displays the status of the interrupt controller. When an interrupt request occurs, its associated vector number and the new Interrupt Priority Level are latched into INTTREG. This information can be used to determine a specific interrupt source if a generic ISR is used for multiple vectors (such as when ISR remapping is used in bootloader applications) or to check if another interrupt is pending while in an ISR.

All Interrupt registers are described in Register 8-1 through Register 8-45 in the succeeding pages.

| REGISTER     | 8-10: IFS5:                                                                                                      | INTERRUPT                                                                                        | FLAGSIAI        | US REGISTE        | :K 5             |                 |         |  |  |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------|-------------------|------------------|-----------------|---------|--|--|--|--|--|

| U-0          | U-0                                                                                                              | U-0                                                                                              | U-0             | R/W-0             | R/W-0            | R/W-0           | R/W-0   |  |  |  |  |  |

|              | —                                                                                                                | _                                                                                                |                 | SPI3TXIF          | SPI3IF           | U4TXIF          | U4RXIF  |  |  |  |  |  |

| bit 15       |                                                                                                                  |                                                                                                  |                 |                   |                  |                 | bit 8   |  |  |  |  |  |

|              |                                                                                                                  | 5444                                                                                             | 5444            | 5444.0            |                  | 5444.6          |         |  |  |  |  |  |

| R/W-0        | U-0                                                                                                              | R/W-0                                                                                            | R/W-0           | R/W-0             | R/W-0            | R/W-0           | U-0     |  |  |  |  |  |

| U4ERIF       | —                                                                                                                | I2C2BCIF                                                                                         | I2C1BCIF        | U3TXIF            | U3RXIF           | U3ERIF          | — hit 0 |  |  |  |  |  |

| bit 7        |                                                                                                                  |                                                                                                  |                 |                   |                  |                 | bit 0   |  |  |  |  |  |

| Legend:      |                                                                                                                  |                                                                                                  |                 |                   |                  |                 |         |  |  |  |  |  |

| R = Readab   | le bit                                                                                                           | W = Writable                                                                                     | bit             | U = Unimplem      | nented bit, read | d as '0'        |         |  |  |  |  |  |

| -n = Value a | t POR                                                                                                            | '1' = Bit is set                                                                                 |                 | '0' = Bit is clea | ared             | x = Bit is unkr | nown    |  |  |  |  |  |

|              |                                                                                                                  |                                                                                                  |                 |                   |                  |                 |         |  |  |  |  |  |

| bit 15-12    | -                                                                                                                | ted: Read as '                                                                                   |                 |                   |                  |                 |         |  |  |  |  |  |

| bit 11       |                                                                                                                  | PI3 Transmit In                                                                                  |                 | atus bit          |                  |                 |         |  |  |  |  |  |

|              |                                                                                                                  | request has oco<br>request has no                                                                |                 |                   |                  |                 |         |  |  |  |  |  |

| bit 10       | -                                                                                                                | General Interro                                                                                  |                 | bit               |                  |                 |         |  |  |  |  |  |

|              |                                                                                                                  | request has oc                                                                                   |                 |                   |                  |                 |         |  |  |  |  |  |

|              |                                                                                                                  | request has no                                                                                   |                 |                   |                  |                 |         |  |  |  |  |  |

| bit 9        |                                                                                                                  | <b>U4TXIF:</b> UART4 Transmitter Interrupt Flag Status bit<br>1 = Interrupt request has occurred |                 |                   |                  |                 |         |  |  |  |  |  |

|              |                                                                                                                  |                                                                                                  |                 |                   |                  |                 |         |  |  |  |  |  |

| bit 8        | <ul> <li>Interrupt request has not occurred</li> <li>U4RXIF: UART4 Receiver Interrupt Flag Status bit</li> </ul> |                                                                                                  |                 |                   |                  |                 |         |  |  |  |  |  |

|              |                                                                                                                  | request has oc                                                                                   |                 |                   |                  |                 |         |  |  |  |  |  |

|              |                                                                                                                  | request has no                                                                                   |                 |                   |                  |                 |         |  |  |  |  |  |

| bit 7        |                                                                                                                  | RT4 Error Interr                                                                                 |                 | s bit             |                  |                 |         |  |  |  |  |  |

|              | <ul> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> </ul>           |                                                                                                  |                 |                   |                  |                 |         |  |  |  |  |  |

| bit 6        | •                                                                                                                | ited: Read as '                                                                                  |                 |                   |                  |                 |         |  |  |  |  |  |

| bit 5        | -                                                                                                                | C2 Bus Collisio                                                                                  |                 | a Status bit      |                  |                 |         |  |  |  |  |  |

|              |                                                                                                                  | request has oc                                                                                   |                 | 9                 |                  |                 |         |  |  |  |  |  |

|              | 0 = Interrupt                                                                                                    | request has no                                                                                   | toccurred       |                   |                  |                 |         |  |  |  |  |  |

| bit 4        |                                                                                                                  | C1 Bus Collisio                                                                                  |                 | g Status bit      |                  |                 |         |  |  |  |  |  |

|              | •                                                                                                                | request has oco<br>request has not                                                               |                 |                   |                  |                 |         |  |  |  |  |  |

| bit 3        | •                                                                                                                | RT3 Transmitter                                                                                  |                 | Status hit        |                  |                 |         |  |  |  |  |  |

| bit o        |                                                                                                                  | request has oc                                                                                   |                 | Oldius bit        |                  |                 |         |  |  |  |  |  |

|              |                                                                                                                  | request has no                                                                                   |                 |                   |                  |                 |         |  |  |  |  |  |

| bit 2        | U3RXIF: UAF                                                                                                      | RT3 Receiver Ir                                                                                  | nterrupt Flag S | tatus bit         |                  |                 |         |  |  |  |  |  |

|              |                                                                                                                  | request has oc                                                                                   |                 |                   |                  |                 |         |  |  |  |  |  |

| bit 1        | -                                                                                                                | request has no <sup>:</sup><br>RT3 Error Interr                                                  |                 | - hit             |                  |                 |         |  |  |  |  |  |

|              |                                                                                                                  | request has oc                                                                                   |                 |                   |                  |                 |         |  |  |  |  |  |

|              |                                                                                                                  | request has not                                                                                  |                 |                   |                  |                 |         |  |  |  |  |  |

| bit 0        | Unimplemen                                                                                                       | ted: Read as '                                                                                   | 0'              |                   |                  |                 |         |  |  |  |  |  |

|              |                                                                                                                  |                                                                                                  |                 |                   |                  |                 |         |  |  |  |  |  |

#### REGISTER 8-10: IFS5: INTERRUPT FLAG STATUS REGISTER 5

| REGISTER                     | ( 0-24. IF 03.                                                                                                 |                                                                                                                                                                   |                                                                        | CONTROL RE       |                  |                 |                  |  |  |

|------------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|------------------|------------------|-----------------|------------------|--|--|

| U-0                          | U-0                                                                                                            | U-0                                                                                                                                                               | U-0                                                                    | U-0              | R/W-1            | R/W-0           | R/W-0            |  |  |

| _                            |                                                                                                                |                                                                                                                                                                   |                                                                        |                  | DMA1IP2          | DMA1IP1         | DMA1IP0          |  |  |

| bit 15                       |                                                                                                                |                                                                                                                                                                   |                                                                        |                  |                  |                 | bit              |  |  |

| U-0                          | R/W-1                                                                                                          | R/W-0                                                                                                                                                             | R/W-0                                                                  | U-0              | R/W-1            | R/W-0           | R/W-0            |  |  |

|                              | AD1IP2                                                                                                         | AD1IP1                                                                                                                                                            | AD1IP0                                                                 | _                | U1TXIP2          | U1TXIP1         | U1TXIP0          |  |  |

| bit 7                        |                                                                                                                |                                                                                                                                                                   | 1                                                                      |                  |                  | 1               | bit              |  |  |

| Legend:                      |                                                                                                                |                                                                                                                                                                   |                                                                        |                  |                  |                 |                  |  |  |

| R = Readab                   | ole bit                                                                                                        | W = Writable                                                                                                                                                      | bit                                                                    | U = Unimplen     | nented bit, read | d as '0'        |                  |  |  |

| -n = Value a                 | at POR                                                                                                         | '1' = Bit is set                                                                                                                                                  |                                                                        | '0' = Bit is cle | ared             | x = Bit is unkr | = Bit is unknown |  |  |

| bit 10-8<br>bit 7<br>bit 6-4 | 111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>AD1IP<2:0>:<br>111 = Interru<br>001 = Interru | >: DMA Chann<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ited:</b> Read as '<br>A/D Interrupt F<br>pt is Priority 7 (<br>pt is Priority 1 | (highest priority<br>abled<br>o'<br>Priority bits<br>(highest priority | / interrupt)     |                  |                 |                  |  |  |

| bit 3<br>bit 2-0             | Unimplemen<br>U1TXIP<2:0><br>111 = Interru<br>•<br>•<br>001 = Interru                                          | <pre>ipt source is dis<br/>ited: Read as 'i<br/>&gt;: UART1 Trans<br/>ipt is Priority 7 (<br/>ipt is Priority 1<br/>ipt source is dis</pre>                       | <sub>0</sub> '<br>smitter Interrup<br>(highest priority                | •                |                  |                 |                  |  |  |

#### REGISTER 8-24: IPC3: INTERRUPT PRIORITY CONTROL REGISTER 3

| U-0          | R/W-1                                                                                                                             | R/W-0                                        | R/W-0            | U-0               | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|------------------|-------------------|------------------|-----------------|---------|--|--|--|--|--|

| _            | U3TXIP2                                                                                                                           | U3TXIP1                                      | U3TXIP0          | _                 | U3RXIP2          | U3RXIP1         | U3RXIP0 |  |  |  |  |  |

| bit 15       |                                                                                                                                   |                                              |                  |                   |                  |                 | bit 8   |  |  |  |  |  |

| U-0          | R/W-1                                                                                                                             | R/W-0                                        | R/W-0            | U-0               | U-0              | U-0             | U-0     |  |  |  |  |  |

|              | U3ERIP2                                                                                                                           | U3ERIP1                                      | U3ERIP0          | 0-0               | <u> </u>         | <u> </u>        | 0-0     |  |  |  |  |  |

| bit 7        | USERI 2                                                                                                                           | UJEINI                                       | USEI(III U       |                   |                  |                 | bit (   |  |  |  |  |  |

|              |                                                                                                                                   |                                              |                  |                   |                  |                 |         |  |  |  |  |  |

| Legend:      |                                                                                                                                   |                                              |                  |                   |                  |                 |         |  |  |  |  |  |

| R = Readab   | ole bit                                                                                                                           | W = Writable                                 | bit              | U = Unimplen      | nented bit, read | d as '0'        |         |  |  |  |  |  |

| -n = Value a | at POR                                                                                                                            | '1' = Bit is set                             |                  | '0' = Bit is clea | ared             | x = Bit is unkr | nown    |  |  |  |  |  |

|              |                                                                                                                                   |                                              |                  |                   |                  |                 |         |  |  |  |  |  |

| bit 15       | -                                                                                                                                 | ted: Read as '                               |                  |                   |                  |                 |         |  |  |  |  |  |

| bit 14-12    | <b>U3TXIP&lt;2:0&gt;:</b> UART3 Transmitter Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt) |                                              |                  |                   |                  |                 |         |  |  |  |  |  |

|              | 111 = Interru                                                                                                                     | pt is Priority 7 (                           | highest priority | (interrupt)       |                  |                 |         |  |  |  |  |  |

|              | •                                                                                                                                 |                                              |                  |                   |                  |                 |         |  |  |  |  |  |

|              | •                                                                                                                                 |                                              |                  |                   |                  |                 |         |  |  |  |  |  |

|              |                                                                                                                                   | pt is Priority 1<br>pt source is dis         | abled            |                   |                  |                 |         |  |  |  |  |  |

| bit 11       | Unimplemen                                                                                                                        | ted: Read as '                               | o'               |                   |                  |                 |         |  |  |  |  |  |

| bit 10-8     | U3RXIP<2:0>: UART3 Receiver Interrupt Priority bits                                                                               |                                              |                  |                   |                  |                 |         |  |  |  |  |  |

|              | 111 = Interrupt is Priority 7 (highest priority interrupt)                                                                        |                                              |                  |                   |                  |                 |         |  |  |  |  |  |

|              | •                                                                                                                                 |                                              |                  |                   |                  |                 |         |  |  |  |  |  |

|              | •                                                                                                                                 |                                              |                  |                   |                  |                 |         |  |  |  |  |  |

|              | 001 = Interrupt is Priority 1                                                                                                     |                                              |                  |                   |                  |                 |         |  |  |  |  |  |

|              |                                                                                                                                   | pt source is dis                             |                  |                   |                  |                 |         |  |  |  |  |  |

| bit 7        | •                                                                                                                                 | ted: Read as '                               |                  |                   |                  |                 |         |  |  |  |  |  |

| bit 6-4      |                                                                                                                                   | : UART3 Error                                | •                |                   |                  |                 |         |  |  |  |  |  |

|              | 111 = Interrupt is Priority 7 (highest priority interrupt)                                                                        |                                              |                  |                   |                  |                 |         |  |  |  |  |  |

|              | •                                                                                                                                 |                                              |                  |                   |                  |                 |         |  |  |  |  |  |

|              | •                                                                                                                                 |                                              |                  |                   |                  |                 |         |  |  |  |  |  |

|              | 001 = Interrupt is Priority 1                                                                                                     |                                              |                  |                   |                  |                 |         |  |  |  |  |  |

|              | 0.0.0 1.1.                                                                                                                        | - +                                          |                  |                   |                  |                 |         |  |  |  |  |  |

| bit 3-0      |                                                                                                                                   | pt source is dis<br>i <b>ted:</b> Read as 'o |                  |                   |                  |                 |         |  |  |  |  |  |

### 11.3 Input Change Notification (ICN)

The Input Change Notification function of the I/O ports allows the PIC24FJ128GA204 family of devices to generate interrupt requests to the processor in response to a Change-of-State (COS) on selected input pins. This feature is capable of detecting input Change-of-States, even in Sleep mode, when the clocks are disabled. Depending on the device pin count, there are up to 82 external inputs that may be selected (enabled) for generating an interrupt request on a Change-of-State.

Registers, CNEN1 through CNEN3, contain the interrupt enable control bits for each of the CN input pins. Setting any of these bits enables a CN interrupt for the corresponding pins. Each CN pin has both a weak pull-up and a weak pull-down connected to it. The pull-ups act as a current source that is connected to the pin, while the pull-downs act as a current sink that is connected to the pin. These eliminate the need for external resistors when push button or keypad devices are connected. The pull-ups and pull-downs are separately enabled using the CNPU1 through CNPU3 registers (for pull-ups), and the CNPD1 through CNPD3 registers (for pull-downs). Each CN pin has individual control bits for its pull-up and pull-down. Setting a control bit enables the weak pull-up or pull-down for the corresponding pin.

When the internal pull-up is selected, the pin pulls up to VDD - 1.1V (typical). When the internal pull-down is selected, the pin pulls down to Vss.

Note: Pull-ups on Input Change Notification pins should always be disabled whenever the port pin is configured as a digital output.

#### EXAMPLE 11-1: PORT READ/WRITE IN ASSEMBLY

| MOV 0xFF00,   | W0 ; | Configure PORTB<15:8> as inputs |

|---------------|------|---------------------------------|

| MOV W0, TRIS  | в;   | and PORTB<7:0> as outputs       |

| NOP           | ;    | Delay 1 cycle                   |

| BTSS PORTB, # | 13 ; | Next Instruction                |

#### EXAMPLE 11-2: PORT READ/WRITE IN 'C'

| TRISB = 0xFF00;                     | <pre>// Configure PORTB&lt;15:8&gt; as inputs and PORTB&lt;7:0&gt; as outputs</pre> |

|-------------------------------------|-------------------------------------------------------------------------------------|

| Nop();                              | // Delay 1 cycle                                                                    |

| <pre>If (PORTBbits.RB13) { };</pre> | // Next Instruction                                                                 |

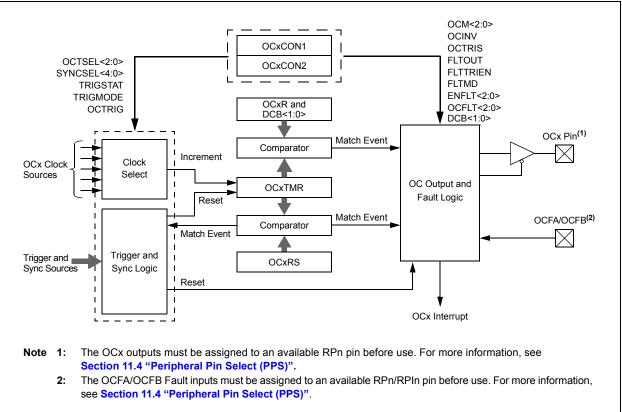

#### FIGURE 15-1: OUTPUT COMPARE x BLOCK DIAGRAM (16-BIT MODE)

#### 15.2 Compare Operations

In Compare mode (Figure 15-1), the output compare module can be configured for single-shot or continuous pulse generation. It can also repeatedly toggle an output pin on each timer event.

To set up the module for compare operations:

- 1. Configure the OCx output for one of the available Peripheral Pin Select pins.

- Calculate the required values for the OCxR and (for Double Compare modes) OCxRS Duty Cycle registers:

- a) Determine the instruction clock cycle time. Take into account the frequency of the external clock to the timer source (if one is used) and the timer prescaler settings.

- b) Calculate the time to the rising edge of the output pulse relative to the timer start value (0000h).

- c) Calculate the time to the falling edge of the pulse based on the desired pulse width and the time to the rising edge of the pulse.

- 3. Write the rising edge value to OCxR and the falling edge value to OCxRS.

- 4. Set the Timer Period register, PRy, to a value equal to or greater than the value in OCxRS.

- 5. Set the OCM<2:0> bits for the appropriate compare operation ('0xx').

- For Trigger mode operations, set OCTRIG to enable Trigger mode. Set or clear TRIGMODE to configure trigger operation and TRIGSTAT to select a hardware or software trigger. For Synchronous mode, clear OCTRIG.

- Set the SYNCSEL<4:0> bits to configure the trigger or synchronization source. If free-running timer operation is required, set the SYNCSELx bits to '00000' (no sync/trigger source).

- Select the time base source with the OCTSEL<2:0> bits. If necessary, set the TON bit for the selected timer, which enables the compare time base to count. Synchronous mode operation starts as soon as the time base is enabled; Trigger mode operation starts after a trigger source event occurs.

#### **REGISTER 16-4:** SPIxSTATL: SPIx STATUS REGISTER LOW

| U-0    | U-0 | U-0 | R/C-0, HS | R-0, HSC | U-0 | U-0 | R-0, HSC              |

|--------|-----|-----|-----------|----------|-----|-----|-----------------------|

| —      | —   | -   | FRMERR    | SPIBUSY  | —   | _   | SPITUR <sup>(1)</sup> |

| bit 15 |     |     |           |          |     |     | bit 8                 |

| R-0, HSC | R/C-0, HS | R-1, HSC | U-0 | R-1, HSC | U-0 | R-0, HSC | R-0, HSC |

|----------|-----------|----------|-----|----------|-----|----------|----------|

| SRMT     | SPIROV    | SPIRBE   | —   | SPITBE   | —   | SPITBF   | SPIRBF   |

| bit 7    |           |          |     |          |     |          | bit 0    |

| Legend:           | C = Clearable bit | HSC = Hardware Settable/Clearable bit |                            |  |

|-------------------|-------------------|---------------------------------------|----------------------------|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0'    |                            |  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared                  | HS = Hardware Settable bit |  |

| bit 15-13 | Unimplemented: Read as '0'                                                                                                                                                                     |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 12    | FRMERR: SPIx Frame Error Status bit                                                                                                                                                            |

|           | 1 = Frame error is detected                                                                                                                                                                    |

|           | 0 = No frame error is detected                                                                                                                                                                 |

| bit 11    | SPIBUSY: SPIx Activity Status bit                                                                                                                                                              |

|           | <ul><li>1 = Module is currently busy with some transactions</li><li>0 = No ongoing transactions (at time of read)</li></ul>                                                                    |

| bit 10-9  | Unimplemented: Read as '0'                                                                                                                                                                     |

| bit 8     | SPITUR: SPIx Transmit Underrun Status bit <sup>(1)</sup>                                                                                                                                       |

|           | <ul> <li>1 = Transmit buffer has encountered a Transmit Underrun (TUR) condition</li> <li>0 = Transmit buffer does not have a Transmit Underrun condition</li> </ul>                           |

| bit 7     | SRMT: SPIx Shift Register Empty Status bit                                                                                                                                                     |

|           | <ul><li>1 = No current or pending transactions (i.e., neither SPIxTXB or SPIxTXSR contains data to transmit)</li><li>0 = Current or pending transactions</li></ul>                             |

| bit 6     | SPIROV: SPIx Receive Overflow Status bit                                                                                                                                                       |

|           | <ul><li>1 = A new byte/half-word/word has been completely received when the SPIxRXB was full</li><li>0 = No overflow</li></ul>                                                                 |

| bit 5     | SPIRBE: SPIx RX Buffer Empty Status bit                                                                                                                                                        |

|           | 1 = RX buffer is empty                                                                                                                                                                         |

|           | 0 = RX buffer is not empty                                                                                                                                                                     |

|           | <u>Standard Buffer Mode:</u><br>Automatically set in hardware when SPIxBUF is read from, reading SPIxRXB. Automatically cleared in hardware when SPIx transfers data from SPIxRXSR to SPIxRXB. |

|           | Enhanced Buffer Mode:<br>Indicates RXELM<5:0> = 6' b000000.                                                                                                                                    |

| bit 4     | Unimplemented: Read as '0'                                                                                                                                                                     |

| bit 3     | SPITBE: SPIx Transmit Buffer Empty Status bit                                                                                                                                                  |

|           | 1 = SPIxTXB is empty                                                                                                                                                                           |

|           | 0 = SPIxTXB is not empty                                                                                                                                                                       |

|           | Standard Buffer Mode:                                                                                                                                                                          |

|           | Automatically set in hardware when SPIx transfers data from SPIxTXB to SPIxTXSR. Automatically cleared in hardware when SPIxBUF is written, loading SPIxTXB.                                   |

|           | Enhanced Buffer Mode:                                                                                                                                                                          |

|           | Indicates TXELM<5:0> = 6' b000000.                                                                                                                                                             |

|           |                                                                                                                                                                                                |

**Note 1:** SPITUR is cleared when SPIEN = 0. When IGNTUR = 1, SPITUR provides dynamic status of the Transmit Underrun condition, but does not stop RX/TX operation and does not need to be cleared by software.

#### U-0 U-0 U-0 R/W-0 R/W-0 U-0 U-0 R/W-0 FRMERREN BUSYEN SPITUREN bit 15 bit 8 R/W-0 R/W-0 R/W-0 U-0 R/W-0 U-0 R/W-0 R/W-0 SPIROVEN SPIRBEN SPITBEN SPITBFEN SPIRBFEN SRMTEN bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' '0' = Bit is cleared x = Bit is unknown -n = Value at POR '1' = Bit is set bit 15-13 Unimplemented: Read as '0' bit 12 FRMERREN: Enable Interrupt Events via FRMERR bit 1 = Frame error generates an interrupt event 0 = Frame error does not generate an interrupt event bit 11 BUSYEN: Enable Interrupt Events via SPIBUSY bit 1 = SPIBUSY generates an interrupt event 0 = SPIBUSY does not generate an interrupt event bit 10-9 Unimplemented: Read as '0' bit 8 SPITUREN: Enable Interrupt Events via SPITUR bit 1 = Transmit Underrun (TUR) generates an interrupt event 0 = Transmit Underrun does not generate an interrupt event bit 7 SRMTEN: Enable Interrupt Events via SRMT bit 1 = Shift Register Empty (SRMT) generates an interrupt events 0 = Shift Register Empty does not generate an interrupt events bit 6 SPIROVEN: Enable Interrupt Events via SPIROV bit 1 = SPIx Receive Overflow generates an interrupt event 0 = SPIx Receive Overflow does not generate an interrupt event bit 5 SPIRBEN: Enable Interrupt Events via SPIRBE bit 1 = SPIx RX buffer empty generates an interrupt event 0 = SPIx RX buffer empty does not generate an interrupt event bit 4 Unimplemented: Read as '0' bit 3 SPITBEN: Enable Interrupt Events via SPITBE bit 1 = SPIx transmit buffer empty generates an interrupt event 0 = SPIx transmit buffer empty does not generate an interrupt event bit 2 Unimplemented: Read as '0' bit 1 SPITBFEN: Enable Interrupt Events via SPITBF bit 1 = SPIx transmit buffer full generates an interrupt event 0 = SPIx transmit buffer full does not generate an interrupt event SPIRBFEN: Enable Interrupt Events via SPIRBF bit bit 0 1 = SPIx receive buffer full generates an interrupt event 0 = SPIx receive buffer full does not generate an interrupt event

| U-0           | U-0                                                                                                            | R/W-0                               | R/W-0                  | U-0                  | U-0              | R/W-0              | R/W-0           |

|---------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------|------------------------|----------------------|------------------|--------------------|-----------------|

| —             | —                                                                                                              | RXRPTIF <sup>(2)</sup>              | TXRPTIF <sup>(2)</sup> | _                    | _                | WTCIF              | GTCIF           |

| bit 15        |                                                                                                                |                                     |                        |                      |                  |                    | bit 8           |

| U-0           | R/W-0                                                                                                          | R/W-0                               | R/W-0                  | U-0                  | U-0              | R/W-0              | R/W-0           |

| 0-0           | PARIE <sup>(2)</sup>                                                                                           | RXRPTIE <sup>(2)</sup>              | TXRPTIE <sup>(2)</sup> | 0-0                  | 0-0              | WTCIE              | GTCIE           |

| <br>bit 7     |                                                                                                                |                                     | TARFTIE                |                      |                  | WICIE              | bit 0           |

|               |                                                                                                                |                                     |                        |                      |                  |                    |                 |

| Legend:       |                                                                                                                |                                     |                        |                      |                  | -l (0)             |                 |

| R = Readable  |                                                                                                                | W = Writable                        | DIt                    | •                    | nented bit, rea  |                    |                 |

| -n = Value at | POR                                                                                                            | '1' = Bit is set                    |                        | '0' = Bit is clea    | ared             | x = Bit is unkn    | iown            |

| bit 15-14     | Unimplemer                                                                                                     | nted: Read as 'd                    | )'                     |                      |                  |                    |                 |

| bit 13        | RXRPTIF: R                                                                                                     | eceive Repeat I                     | nterrupt Flag b        | it <sup>(2)</sup>    |                  |                    |                 |

|               |                                                                                                                | or has persisted                    |                        |                      | s been receive   | ed five times (fou | ur retransmits) |

| bit 12        | -                                                                                                              | ansmit Repeat I                     | nterrupt Flag b        | it <sup>(2)</sup>    |                  |                    |                 |

|               | 1 = Line erro<br>0 = Flag is cl                                                                                | r has been dete<br>eared            | cted after the la      | ast retransmit µ     | per TXRPT<1:     | 0> (see Registe    | r 18-5)         |

| bit 11-10     | Unimplemer                                                                                                     | nted: Read as '                     | )'                     |                      |                  |                    |                 |

| bit 9         | WTCIF: Wait                                                                                                    | ing Time Count                      | er Interrupt Flag      | g bit                |                  |                    |                 |

|               | <ul> <li>1 = Waiting Time Counter has reached 0</li> <li>0 = Waiting Time Counter has not reached 0</li> </ul> |                                     |                        |                      |                  |                    |                 |

| bit 8         | GTCIF: Guar                                                                                                    | rd Time Counter                     | Interrupt Flag         | bit                  |                  |                    |                 |

|               |                                                                                                                | me Counter has<br>me Counter has    |                        |                      |                  |                    |                 |

| bit 7         | Unimplemer                                                                                                     | nted: Read as '                     | )'                     |                      |                  |                    |                 |

| bit 6         | PARIE: Parit                                                                                                   | y Interrupt Enab                    | ole bit <sup>(2)</sup> |                      |                  |                    |                 |

|               |                                                                                                                | rupt is invoked<br><3>) in Register |                        |                      | ed with a pa     | rity error; see    | the PERR bit    |

| bit 5         | •                                                                                                              | eceive Repeat I                     | nterrupt Enable        | e bit <sup>(2)</sup> |                  |                    |                 |

|               |                                                                                                                | rupt is invoked                     |                        |                      | rsisted after th | ne same charad     | cter has been   |

|               |                                                                                                                | l five times (four                  |                        |                      |                  |                    |                 |

| bit 4         | TXRPTIE: Tr                                                                                                    | ansmit Repeat                       | Interrupt Enable       | e bit <sup>(2)</sup> |                  |                    |                 |

|               |                                                                                                                | rupt is invoked v<br>been completed |                        |                      | fter the last re | transmit per the   | TXRPT<1:0>      |

| bit 3-2       | -                                                                                                              | nted: Read as '                     | ٦,                     |                      |                  |                    |                 |

| bit 0 2       | -                                                                                                              | ting Time Count                     |                        | able bit             |                  |                    |                 |

|               | 1 = Waiting T                                                                                                  | Time Counter int                    | errupt is enable       | ed                   |                  |                    |                 |

| bit 0         | -                                                                                                              | rd Time Counter                     | -                      |                      |                  |                    |                 |

|               |                                                                                                                | me Counter inte                     | -                      |                      |                  |                    |                 |

|               |                                                                                                                | me Counter inte                     |                        |                      |                  |                    |                 |

|               |                                                                                                                |                                     |                        |                      |                  |                    |                 |

### REGISTER 18-6: UxSCINT: UARTx SMART CARD INTERRUPT REGISTER<sup>(1)</sup>

DS30010038C-page 256

#### **REGISTER 22-1: CRYCONL: CRYPTOGRAPHIC CONTROL LOW REGISTER**

| R/W-0  | U-0 | R/W-0                  | R/W-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup> | U-0 | R/W-0, HC <sup>(1)</sup> |

|--------|-----|------------------------|----------------------|----------------------|----------------------|-----|--------------------------|

| CRYON  |     | CRYSIDL <sup>(3)</sup> | ROLLIE               | DONEIE               | FREEIE               | —   | CRYGO                    |

| bit 15 |     | ·                      |                      |                      |                      |     | bit 8                    |

| R/W-0 <sup>(1)</sup>   | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>    | R/W-0 <sup>(1)</sup>    |

|-----------------------|-----------------------|-----------------------|-----------------------|------------------------|-------------------------|-------------------------|-------------------------|

| OPMOD3 <sup>(2)</sup> | OPMOD2 <sup>(2)</sup> | OPMOD1 <sup>(2)</sup> | OPMOD0 <sup>(2)</sup> | CPHRSEL <sup>(2)</sup> | CPHRMOD2 <sup>(2)</sup> | CPHRMOD1 <sup>(2)</sup> | CPHRMOD0 <sup>(2)</sup> |

| bit 7                 |                       |                       |                       |                        |                         |                         | bit 0                   |

| Legend:           | HC = Hardware Clearable bit |                             |                    |  |  |  |

|-------------------|-----------------------------|-----------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, read | as '0'             |  |  |  |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared        | x = Bit is unknown |  |  |  |

| bit 15 | CRYON: Cryptographic Enable bit                                                                                                                                                                                           |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | 1 = Module is enabled                                                                                                                                                                                                     |

|        | 0 = Module is disabled                                                                                                                                                                                                    |

| bit 14 | Unimplemented: Read as '0'                                                                                                                                                                                                |

| bit 13 | CRYSIDL: Cryptographic Stop in Idle Control bit <sup>(3)</sup>                                                                                                                                                            |

|        | 1 = Stops module operation in Idle mode                                                                                                                                                                                   |

|        | 0 = Continues module operation in Idle mode                                                                                                                                                                               |

| bit 12 | ROLLIE: CRYTXTB Rollover Interrupt Enable bit <sup>(1)</sup>                                                                                                                                                              |

|        | 1 = Generates an interrupt event when the counter portion of CRYTXTB rolls over to '0'                                                                                                                                    |

|        | 0 = Does not generate an interrupt event when the counter portion of CRYTXTB rolls over to '0'                                                                                                                            |

| bit 11 | DONEIE: Operation Done Interrupt Enable bit <sup>(1)</sup>                                                                                                                                                                |

|        | 1 = Generates an interrupt event when the current cryptographic operation completes                                                                                                                                       |

|        | <ul> <li>Does not generate an interrupt event when the current cryptographic operation completes; software<br/>must poll the CRYGO or CRYBSY bit to determine when current cryptographic operation is complete</li> </ul> |

| bit 10 | FREEIE: Input Text Interrupt Enable bit <sup>(1)</sup>                                                                                                                                                                    |