#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART                      |

| Peripherals                | AES, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, HLVD, POR, PWM, WDT         |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

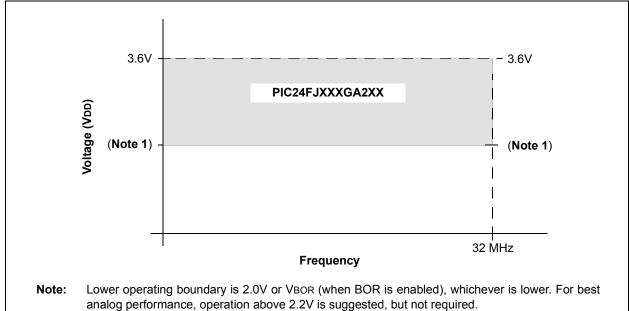

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

| Data Converters            | A/D 10x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                  |

| Supplier Device Package    | 28-SSOP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128ga202t-i-ss |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 DEVICE OVERVIEW

This document contains device-specific information for the following devices:

- PIC24FJ64GA202 PIC24FJ128GA202

- PIC24FJ64GA204 PIC24FJ128GA204

The PIC24FJ128GA204 family expands the capabilities of the PIC24F family by adding a complete selection of Cryptographic Engines, ISO 7816 support and I<sup>2</sup>S support to its existing features. This combination, along with its ultra low-power features and Direct Memory Access (DMA) for peripherals, make this family the new standard for mixed-signal PIC<sup>®</sup> microcontrollers in one economical and power-saving package.

## 1.1 Core Features

### 1.1.1 16-BIT ARCHITECTURE

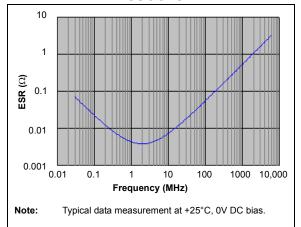

Central to all PIC24F devices is the 16-bit modified Harvard architecture, first introduced with Microchip's dsPIC<sup>®</sup> Digital Signal Controllers (DSCs). The PIC24F CPU core offers a wide range of enhancements, such as:

- 16-bit data and 24-bit address paths with the ability to move information between data and memory spaces

- Linear addressing of up to 12 Mbytes (program space) and 32 Kbytes (data)

- A 16-element Working register array with built-in software stack support

- A 17 x 17 hardware multiplier with support for integer math

- Hardware support for 32 by 16-bit division

- An instruction set that supports multiple addressing modes and is optimized for high-level languages, such as 'C'

- Operational performance up to 16 MIPS

#### 1.1.2 XLP POWER-SAVING TECHNOLOGY

The PIC24FJ128GA204 family of devices introduces a greatly expanded range of power-saving operating modes for the ultimate in power conservation. The new modes include:

- Retention Sleep, with essential circuits being powered from a separate low-voltage regulator

- Deep Sleep without RTCC, for the lowest possible power consumption under software control

- VBAT mode (with or without RTCC), to continue limited operation from a backup battery when VDD is removed

Many of these new low-power modes also support the continuous operation of the low-power, on-chip Real-Time Clock/Calendar (RTCC), making it possible for an application to keep time while the device is otherwise asleep.

Aside from these new features, PIC24FJ128GA204 family devices also include all of the legacy power-saving features of previous PIC24F microcontrollers, such as:

- On-the-Fly Clock Switching, allowing the selection of a lower power clock during run time

- Doze Mode Operation, for maintaining peripheral clock speed while slowing the CPU clock

- Instruction-Based Power-Saving Modes, for quick invocation of Idle and the many Sleep modes

## 1.1.3 OSCILLATOR OPTIONS AND FEATURES

All of the devices in the PIC24FJ128GA204 family offer five different oscillator options, allowing users a range of choices in developing application hardware. These include:

- Two Crystal modes

- Two External Clock modes

- A Phase-Locked Loop (PLL) frequency multiplier, which allows clock speeds of up to 32 MHz

- A Fast Internal Oscillator (FRC) nominal 8 MHz output with multiple frequency divider options and automatic frequency self-calibration during run time

- A separate, Low-Power Internal RC Oscillator (LPRC) – 31 kHz nominal, for low-power, timing-insensitive applications.

The internal oscillator block also provides a stable reference source for the Fail-Safe Clock Monitor (FSCM). This option constantly monitors the main clock source against a reference signal provided by the internal oscillator and enables the controller to switch to the internal oscillator, allowing for continued low-speed operation or a safe application shutdown.

## 1.1.4 EASY MIGRATION

Regardless of the memory size, all devices share the same rich set of peripherals, allowing for a smooth migration path as applications grow and evolve. This extends the ability of applications to grow from the relatively simple, to the powerful and complex, yet still selecting a Microchip device.

### 2.4 Voltage Regulator Pins (ENVREG/ DISVREG and VCAP/VDDCORE)

Note: This section applies only to PIC24FJ devices with an on-chip voltage regulator.

The on-chip voltage regulator enable/disable pin (ENVREG or DISVREG, depending on the device family) must always be connected directly to either a supply voltage or to ground. The particular connection is determined by whether or not the regulator is to be used:

- For ENVREG, tie to VDD to enable the regulator, or to ground to disable the regulator

- For DISVREG, tie to ground to enable the regulator or to VDD to disable the regulator

Refer to **Section 29.2 "On-Chip Voltage Regulator"** for details on connecting and using the on-chip regulator.

When the regulator is enabled, a low-ESR (< 5 $\Omega$ ) capacitor is required on the VCAP/VDDCORE pin to stabilize the voltage regulator output voltage. The VCAP/VDDCORE pin must not be connected to VDD and must use a capacitor of 10  $\mu$ F connected to ground. The type can be ceramic or tantalum. Suitable examples of capacitors are shown in Table 2-1. Capacitors with equivalent specifications can be used.

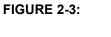

Designers may use Figure 2-3 to evaluate ESR equivalence of candidate devices.

The placement of this capacitor should be close to VCAP/VDDCORE. It is recommended that the trace length not exceed 0.25 inch (6 mm). Refer to **Section 32.0** "Electrical Characteristics" for additional information.

When the regulator is disabled, the VCAP/VDDCORE pin must be tied to a voltage supply at the VDDCORE level. Refer to Section 32.0 "Electrical Characteristics" for information on VDD and VDDCORE.

#### FREQUENCY vs. ESR PERFORMANCE FOR SUGGESTED VCAP

| Make      | Part #             | Nominal<br>Capacitance | Base Tolerance | Rated Voltage | Temp. Range   |

|-----------|--------------------|------------------------|----------------|---------------|---------------|

| TDK       | C3216X7R1C106K     | 10 µF                  | ±10%           | 16V           | -55 to +125°C |

| TDK       | C3216X5R1C106K     | 10 µF                  | ±10%           | 16V           | -55 to +85°C  |

| Panasonic | ECJ-3YX1C106K      | 10 µF                  | ±10%           | 16V           | -55 to +125°C |

| Panasonic | ECJ-4YB1C106K      | 10 µF                  | ±10%           | 16V           | -55 to +85°C  |

| Murata    | GRM32DR71C106KA01L | 10 µF                  | ±10%           | 16V           | -55 to +125°C |

| Murata    | GRM31CR61C106KC31L | 10 µF                  | ±10%           | 16V           | -55 to +85°C  |

## TABLE 2-1: SUITABLE CAPACITOR EQUIVALENTS

## PIC24FJ128GA204 FAMILY

| Register(s) Name | Description                        | Description |  |  |  |  |

|------------------|------------------------------------|-------------|--|--|--|--|

| W0 through W15   | Working Register Array             |             |  |  |  |  |

| PC               | 23-Bit Program Counter             |             |  |  |  |  |

| SR               | ALU STATUS Register                |             |  |  |  |  |

| SPLIM            | Stack Pointer Limit Value Register |             |  |  |  |  |

| TBLPAG           | Table Memory Page Address Register |             |  |  |  |  |

| RCOUNT           | REPEAT Loop Counter Register       |             |  |  |  |  |

| CORCON           | CPU Control Register               |             |  |  |  |  |

| DISICNT          | Disable Interrupt Count Register   |             |  |  |  |  |

| DSRPAG           | Data Space Read Page Register      |             |  |  |  |  |

| DSWPAG           | Data Space Write Page Register     |             |  |  |  |  |

## TABLE 4-5: INTERRUPT CONTROLLER REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14     | Bit 13     | Bit 12          | Bit 11          | Bit 10     | Bit 9      | Bit 8      | Bit 7   | Bit 6     | Bit 5     | Bit 4     | Bit 3         | Bit 2         | Bit 1         | Bit 0     | All<br>Resets |

|--------------|------|--------|------------|------------|-----------------|-----------------|------------|------------|------------|---------|-----------|-----------|-----------|---------------|---------------|---------------|-----------|---------------|

| INTCON1      | 0080 | NSTDIS | _          | —          | _               | —               | _          | _          | -          | —       | —         | —         | MATHERR   | ADDRERR       | STKERR        | OSCFAIL       | -         | 0000          |

| INTCON2      | 0082 | ALTIVT | DISI       | -          | —               |                 | -          | _          | —          | -       | -         | -         | INT4EP    | INT3EP        | INT2EP        | INT1EP        | INT0EP    | 0000          |

| IFS0         | 0084 | _      | DMA1IF     | AD1IF      | U1TXIF          | U1RXIF          | SPI1TXIF   | SPI1IF     | T3IF       | T2IF    | OC2IF     | IC2IF     | DMA0IF    | T1IF          | OC1IF         | IC1IF         | INTOIF    | 0000          |

| IFS1         | 0086 | U2TXIF | U2RXIF     | INT2IF     | T5IF            | T4IF            | OC4IF      | OC3IF      | DMA2IF     | _       | _         | _         | INT1IF    | CNIF          | CMIF          | MI2C1IF       | SI2C1IF   | 0000          |

| IFS2         | 0088 | _      | DMA4IF     | PMPIF      | _               | _               | OC6IF      | OC5IF      | IC6IF      | IC5IF   | IC4IF     | IC3IF     | DMA3IF    | CRYROLLIF     | CRYFREEIF     | SPI2TXIF      | SPI2IF    | 0000          |

| IFS3         | 008A | _      | RTCIF      | DMA5IF     | <b>SPI3RXIF</b> | SPI2RXIF        | SPI1RXIF   | _          | KEYSTRIF   | CRYDNIF | INT4IF    | INT3IF    | _         | _             | MI2C2IF       | SI2C2IF       | _         | 0000          |

| IFS4         | 008C | _      |            | CTMUIF     | _               | _               | _          | _          | HLVDIF     | _       | _         | _         | _         | CRCIF         | U2ERIF        | U1ERIF        | _         | 000           |

| IFS5         | 008E | —      | _          | _          | _               | <b>SPI3TXIF</b> | SPI3IF     | U4TXIF     | U4RXIF     | U4ERIF  | _         | I2C2BCIF  | I2C1BCIF  | U3TXIF        | <b>U3RXIF</b> | <b>U3ERIF</b> | _         | 0000          |

| IFS6         | 0090 | —      | _          | _          | _               | _               | FSTIF      | _          | —          | _       | _         | _         | _         | —             | _             | _             | _         | 000           |

| IFS7         | 0092 | —      | _          | _          | _               | _               | _          | _          | —          | _       | _         | JTAGIF    | _         | _             | _             | _             | _         | 000           |

| IEC0         | 0094 | —      | DMA1IE     | AD1IE      | U1TXIE          | U1RXIE          | SPI1TXIE   | SPI1IE     | T3IE       | T2IE    | OC2IE     | IC2IE     | DMA0IE    | T1IE          | OC1IE         | IC1IE         | INTOIE    | 0000          |

| IEC1         | 0096 | U2TXIE | U2RXIE     | INT2IE     | T5IE            | T4IE            | OC4IE      | OC3IE      | DMA2IE     | _       | _         | _         | INT1IE    | CNIE          | CMIE          | MI2C1IE       | SI2C1IE   | 000           |

| IEC2         | 0098 | —      | DMA4IE     | PMPIE      | _               | _               | OC6IE      | OC5IE      | IC6IE      | IC5IE   | IC4IE     | IC3IE     | DMA3IE    | CRYROLLIE     | CRYFREEIE     | SPI2TXIE      | SPI2IE    | 000           |

| IEC3         | 009A | —      | RTCIE      | DMA5IE     | <b>SPI3RXIE</b> | SPI2RXIE        | SPI1RXIE   | _          | KEYSTRIE   | CRYDNIE | INT4IE    | INT3IE    | _         | —             | MI2C2IE       | SI2C2IE       | _         | 000           |

| IEC4         | 009C | —      | _          | CTMUIE     | _               | _               | _          | _          | HLVDIE     | _       | _         | _         | _         | CRCIE         | U2ERIE        | U1ERIE        | _         | 000           |

| IEC5         | 009E |        | _          | _          | _               | SPI3TXIE        | SPI3IE     | U4TXIE     | U4RXIE     | U4ERIE  | -         | I2C2BCIE  | I2C1BCIE  | <b>U3TXIE</b> | <b>U3RXIE</b> | <b>U3ERIE</b> | _         | 000           |

| IEC6         | 00A0 | —      | _          | _          | _               | _               | FSTIE      | _          | —          | _       | _         | _         | _         | —             | _             | _             | _         | 000           |

| IEC7         | 00A2 | —      | _          | _          | _               | _               | _          | _          | _          | _       | _         | JTAGIE    | _         | _             | _             | _             | _         | 000           |

| IPC0         | 00A4 | —      | T1IP2      | T1IP1      | T1IP0           | _               | OC1IP2     | OC1IP1     | OC1IP0     | _       | IC1IP2    | IC1IP1    | IC1IP0    | —             | INT0IP2       | INT0IP1       | INT0IP0   | 444           |

| IPC1         | 00A6 | —      | T2IP2      | T2IP1      | T2IP0           | _               | OC2IP2     | OC2IP1     | OC2IP0     | _       | IC2IP2    | IC2IP1    | IC2IP0    | —             | DMA0IP2       | DMA0IP1       | DMA0IP0   | 444           |

| IPC2         | 00A8 | —      | U1RXIP2    | U1RXIP1    | U1RXIP0         | _               | SPI1TXIP2  | SPI1TXIP1  | SPI1TXIP0  | _       | SPI1IP2   | SPI1IP1   | SPI1IP0   | —             | T3IP2         | T3IP1         | T3IP0     | 444           |

| IPC3         | 00AA |        | _          | _          | _               | _               | DMA1IP2    | DMA1IP1    | DMA1IP0    | _       | AD1IP2    | AD1IP1    | AD1IP0    | _             | U1TXIP2       | U1TXIP1       | U1TXIP0   | 044           |

| IPC4         | 00AC | —      | CNIP2      | CNIP1      | CNIP0           | _               | CMIP2      | CMIP1      | CMIP0      | _       | MI2C1IP2  | MI2C1IP1  | MI2C1IP0  | —             | SI2C1IP2      | SI2C1IP1      | SI2C1IP0  | 444           |

| IPC5         | 00AE | —      | _          | _          | _               | _               | _          | _          | —          | _       | _         | _         | _         | —             |               | INT1IP<2:0>   |           | 000           |

| IPC6         | 00B0 | —      | T4IP2      | T4IP1      | T4IP0           | _               | OC4IP2     | OC4IP1     | OC4IP0     | _       | OC3IP2    | OC3IP1    | OC3IP0    | —             | DMA2IP2       | DMA2IP1       | DMA2IP0   | 444           |

| IPC7         | 00B2 | —      | U2TXIP2    | U2TXIP1    | U2TXIP0         | _               | U2RXIP2    | U2RXIP1    | U2RXIP0    | _       | INT2IP2   | INT2IP1   | INT2IP0   | —             | T5IP2         | T5IP1         | T5IP0     | 444           |

| IPC8         | 00B4 | —      | CRYROLLIP2 | CRYROLLIP1 | CRYROLLIP0      | _               | CRYFREEIP2 | CRYFREEIP1 | CRYFREEIP0 | _       | SPI2TXIP2 | SPI2TXIP1 | SPI2TXIP0 | —             | SPI2IP2       | SPI2IP1       | SPI2IP0   | 444           |

| IPC9         | 00B6 | —      | IC5IP2     | IC5IP1     | IC5IP0          | _               | IC4IP2     | IC4IP1     | IC4IP0     | _       | IC3IP2    | IC3IP1    | IC3IP0    | _             | DMA3IP2       | DMA3IP1       | DMA3IP0   | 444           |

| IPC10        | 00B8 | _      | _          | —          | —               | _               | OC6IP2     | OC6IP1     | OC6IP0     | -       | OC5IP2    | OC5IP1    | OC5IP0    | _             | IC6IP2        | IC6IP1        | IC6IP0    | 044           |

| IPC11        | 00BA | —      | _          | —          | —               | _               | DMA4IP2    | DMA4IP1    | DMA4IP0    | —       | PMPIP2    | PMPIP1    | PMPIP0    | —             | —             | —             | —         | 044           |

| IPC12        | 00BC | —      | _          | —          | —               | _               | MI2C2IP2   | MI2C2IP1   | MI2C2IP0   | —       | SI2C2IP2  | SI2C2IP1  | SI2C2IP0  | —             | —             | _             | —         | 044           |

| IPC13        | 00BE | _      | CRYDNIP2   | CRYDNIP1   | CRYDNIP0        | _               | INT4IP2    | INT4IP1    | INT4IP0    | _       | INT3IP2   | INT3IP1   | INT3IP0   | _             | _             | _             | _         | 444           |

| IPC14        | 00CO | _      | SPI2RXIP2  | SPI2RXIP1  | SPI2RXIP0       | _               | SPI1RXIP2  | SPI1RXIP1  | SPI1RXIP0  | _       | _         | —         | —         | —             | KEYSTRIP2     | KEYSTRIP1     | KEYSTRIP0 | 440           |

| IPC15        | 00C2 | _      | _          | _          | _               | _               | RTCIP2     | RTCIP1     | RTCIP0     | _       | DMA5IP2   | DMA5IP1   | DMA5IP0   | _             | SPI3RXIP2     | SPI3RXIP1     | SPI3RXIP0 | 044           |

DS30010038C-page 39

### 4.3 Interfacing Program and Data Memory Spaces

The PIC24F architecture uses a 24-bit wide program space and 16-bit wide Data Space. The architecture is also a modified Harvard scheme, meaning that data can also be present in the program space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the PIC24F architecture provides two methods by which program space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the program space

- Remapping a portion of the program space into the Data Space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This makes the method ideal for accessing data tables that need to be updated from time to time. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look-ups from a large table of static data. It can only access the least significant word of the program word.

## 4.3.1 ADDRESSING PROGRAM SPACE

Since the address ranges for the data and program spaces are 16 and 24 bits, respectively, a method is needed to create a 23-bit or 24-bit program address from 16-bit Data registers. The solution depends on the interface method to be used.

For table operations, the 8-bit Table Memory Page Address register (TBLPAG) is used to define a 32K word region within the program space. This is concatenated with a 16-bit EA to arrive at a full 24-bit program space address. In this format, the MSbs of TBLPAG are used to determine if the operation occurs in the user memory (TBLPAG<7> = 0) or the configuration memory (TBLPAG<7> = 1).

For remapping operations, the 10-bit Extended Data Space Read register (DSRPAG) is used to define a 16K word page in the program space. When the Most Significant bit (MSb) of the EA is '1' and the MSb (bit 9) of DSRPAG is '1', the lower 8 bits of DSRPAG are concatenated with the lower 15 bits of the EA to form a 23-bit program space address. The DSRPAG<8> bit decides whether the lower word (when the bit is '0') or the higher word (when the bit is '1') of program memory is mapped. Unlike table operations, this strictly limits remapping operations to the user memory area.

Table 4-35 and Figure 4-8 show how the program EA is created for table operations and remapping accesses from the data EA. Here, the P<23:0> bits refer to a program space word, whereas the D<15:0> bits refer to a Data Space word.

|                          | Access        | Program Space Address        |           |                                                 |                    |                    |  |  |

|--------------------------|---------------|------------------------------|-----------|-------------------------------------------------|--------------------|--------------------|--|--|

| Access Type              | Space         | <23>                         | <22:16>   | <15>                                            | <14:1>             | <0>                |  |  |

| Instruction Access       | User          | 0 PC<22:1>                   |           |                                                 |                    | 0                  |  |  |

| (Code Execution)         |               | 0xx xxxx xxxx xxxx xxxx xxx0 |           |                                                 |                    |                    |  |  |

| TBLRD/TBLWT              | User          | TB                           | LPAG<7:0> | Data EA<15:0>                                   |                    |                    |  |  |

| (Byte/Word Read/Write)   |               | 0:                           | XXX XXXX  | XXXX XXXX XXXX XXXX                             |                    |                    |  |  |

|                          | Configuration | TB                           | LPAG<7:0> | Data EA<15:0>                                   |                    |                    |  |  |

|                          |               | 1xxx xxxx xxx                |           |                                                 | XX XXXX XXXX XXXX  |                    |  |  |

| Program Space Visibility | User          | 0 DSRPAG<7:                  |           | :0> <sup>(2)</sup> Data EA<14:0> <sup>(1)</sup> |                    | :0> <sup>(1)</sup> |  |  |

| (Block Remap/Read)       |               | 0                            | XXXX XXXX |                                                 | XXX XXXX XXXX XXXX |                    |  |  |

#### TABLE 4-35: PROGRAM SPACE ADDRESS CONSTRUCTION

**Note 1:** Data EA<15> is always '1' in this case, but is not used in calculating the program space address. Bit 15 of the address is DSRPAG<0>.

2: DSRPAG<9> is always '1' in this case. DSRPAG<8> decides whether the lower word or higher word of program memory is read. When DSRPAG<8> is '0', the lower word is read and when it is '1', the higher word is read.

## 5.1 Summary of DMA Operations

The DMA Controller is capable of moving data between addresses according to a number of different parameters. Each of these parameters can be independently configured for any transaction. In addition, any or all of the DMA channels can independently perform a different transaction at the same time. Transactions are classified by these parameters:

- Source and destination (SFRs and data RAM)

- · Data size (byte or word)

- Trigger source

- Transfer mode (One-Shot, Repeated or Continuous)

- Addressing modes (Fixed Address or Address Blocks with or without Address Increment/Decrement)

In addition, the DMA Controller provides channel priority arbitration for all channels.

#### 5.1.1 SOURCE AND DESTINATION

Using the DMA Controller, data may be moved between any two addresses in the Data Space. The SFR space (0000h to 07FFh), or the data RAM space (0800h to FFFFh) can serve as either the source or the destination. Data can be moved between these areas in either direction or between addresses in either area. The four different combinations are shown in Figure 5-2.

If it is necessary to protect areas of data RAM, the DMA Controller allows the user to set upper and lower address boundaries for operations in the Data Space above the SFR space. The boundaries are set by the DMAH and DMAL High/Low Address Limit registers. If a DMA channel attempts an operation outside of the address boundaries, the transaction is terminated and an interrupt is generated.

#### 5.1.2 DATA SIZE

The DMA Controller can handle both 8-bit and 16-bit transactions. Size is user-selectable using the SIZE bit (DMACHn<1>). By default, each channel is configured for word-size transactions. When byte-size transactions are chosen, the LSb of the source and/or destination address determines if the data represents the upper or lower byte of the data RAM location.

#### 5.1.3 TRIGGER SOURCE

The DMA Controller can use 63 of the device's interrupt sources to initiate a transaction. The DMA trigger sources occur in reverse order than their natural interrupt priority and are shown in Table 5-1.

Since the source and destination addresses for any transaction can be programmed independently of the trigger source, the DMA Controller can use any trigger to perform an operation on any peripheral. This also allows DMA channels to be cascaded to perform more complex transfer operations.

#### 5.1.4 TRANSFER MODE

The DMA Controller supports four types of data transfers, based on the volume of data to be moved for each trigger:

- One-Shot: A single transaction occurs for each trigger.

- Continuous: A series of back-to-back transactions occur for each trigger; the number of transactions is determined by the DMACNTn transaction counter.

- Repeated One-Shot: A single transaction is performed repeatedly, once per trigger, until the DMA channel is disabled.

- Repeated Continuous: A series of transactions are performed repeatedly, one cycle per trigger, until the DMA channel is disabled.

All Transfer modes allow the option to have the source and destination addresses, and counter value, automatically reloaded after the completion of a transaction; Repeated mode transfers do this automatically.

## 5.1.5 ADDRESSING MODES

The DMA Controller also supports transfers between single addresses or address ranges. The four basic options are:

- · Fixed-to-Fixed: Between two constant addresses

- Fixed-to-Block: From a constant source address to a range of destination addresses

- Block-to-Fixed: From a range of source addresses to a single, constant destination address

- Block-to-Block: From a range of source addresses to a range of destination addresses

The option to select auto-increment or auto-decrement of source and/or destination addresses is available for Block Addressing modes.

In addition to the four basic modes, the DMA Controller also supports Peripheral Indirect Addressing (PIA) mode, where the source or destination address is generated jointly by the DMA Controller and a PIA capable peripheral. When enabled, the DMA channel provides a base source and/or destination address, while the peripheral provides a fixed range offset address.

For PIC24FJ128GA204 family devices, the 12-bit A/D Converter module is the only PIA capable peripheral. Details for its use in PIA mode are provided in Section 24.0 "12-Bit A/D Converter with Threshold Detect".

# PIC24FJ128GA204 FAMILY

#### REGISTER 8-26: IPC5: INTERRUPT PRIORITY CONTROL REGISTER 5

| U-0        | U-0    | U-0            | U-0 | U-0         | U-0             | U-0         | U-0   |

|------------|--------|----------------|-----|-------------|-----------------|-------------|-------|

| —          | —      | —              | —   | _           | —               | —           | —     |

| bit 15     |        |                |     |             |                 |             | bit 8 |

|            |        |                |     |             |                 |             |       |

| U-0        | U-0    | U-0            | U-0 | U-0         | R/W-1           | R/W-0       | R/W-0 |

| —          | —      | —              | —   | —           |                 | INT1IP<2:0> |       |

| bit 7      |        |                |     |             |                 |             | bit C |

|            |        |                |     |             |                 |             |       |

| Legend:    |        |                |     |             |                 |             |       |

| R = Readab | le bit | W = Writable I | oit | U = Unimple | mented bit, rea | d as '0'    |       |

| R = Readable bit  | VV = VVritable bit | U = Unimplemented bit, real | ad as '0'          |

|-------------------|--------------------|-----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set   | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 15-3 Unimplemented: Read as '0'

bit 2-0 INT1IP<2:0>: External Interrupt 1 Priority bits

- 111 = Interrupt is Priority 7 (highest priority interrupt)

001 = Interrupt is Priority 1

000 = Interrupt source is disabled

## PIC24FJ128GA204 FAMILY

#### REGISTER 8-43: IPC26: INTERRUPT PRIORITY CONTROL REGISTER 26

| U-0          | U-0           | U-0                | U-0               | U-0                                   | R/W-1           | R/W-0      | R/W-0 |

|--------------|---------------|--------------------|-------------------|---------------------------------------|-----------------|------------|-------|

|              |               |                    | _                 |                                       |                 | FSTIP<2:0> |       |

| bit 15       |               |                    |                   |                                       |                 |            | bit 8 |

|              |               |                    |                   |                                       |                 |            |       |

| U-0          | U-0           | U-0                | U-0               | U-0                                   | U-0             | U-0        | U-0   |

| —            | —             | _                  | —                 | _                                     | —               | —          | —     |

| bit 7        |               | -                  | -                 | -<br>-                                |                 |            | bit 0 |

|              |               |                    |                   |                                       |                 |            |       |

| Legend:      |               |                    |                   |                                       |                 |            |       |

| R = Readab   | ole bit       | W = Writable       | bit               | U = Unimplen                          | nented bit, rea | d as '0'   |       |

| -n = Value a | at POR        | '1' = Bit is set   |                   | '0' = Bit is cleared x = Bit is unkno |                 |            | own   |

|              |               |                    |                   |                                       |                 |            |       |

| bit 15-11    | Unimplemen    | ted: Read as '     | 0'                |                                       |                 |            |       |

| bit 10-8     | FSTIP<2:0>:   | FRC Self-Tune      | e Interrupt Prior | ity bits                              |                 |            |       |

|              | 111 = Interru | pt is Priority 7 ( | (highest priority | interrupt)                            |                 |            |       |

|              | •             |                    |                   |                                       |                 |            |       |

|              | •             |                    |                   |                                       |                 |            |       |

|              | •             |                    |                   |                                       |                 |            |       |

|              |               | pt is Priority 1   |                   |                                       |                 |            |       |

|              |               | pt source is dis   |                   |                                       |                 |            |       |

| bit 7-0      | Unimplemen    | ted: Read as '     | 0'                |                                       |                 |            |       |

|              |               |                    |                   |                                       |                 |            |       |

#### REGISTER 8-44: IPC29: INTERRUPT PRIORITY CONTROL REGISTER 29

| U-0        | U-0          | U-0                 | U-0              | U-0                                     | U-0 | U-0 | U-0   |  |  |  |

|------------|--------------|---------------------|------------------|-----------------------------------------|-----|-----|-------|--|--|--|

| _          | —            | —                   | —                | —                                       | —   | —   | _     |  |  |  |

| bit 15     |              |                     |                  |                                         |     |     | bit 8 |  |  |  |

|            |              |                     |                  |                                         |     |     |       |  |  |  |

| U-0        | R/W-1        | R/W-0               | R/W-0            | U-0                                     | U-0 | U-0 | U-0   |  |  |  |

| _          |              | JTAGIP<2:0>         |                  | —                                       | —   | —   | —     |  |  |  |

| bit 7      | ·            |                     |                  |                                         |     |     | bit 0 |  |  |  |

|            |              |                     |                  |                                         |     |     |       |  |  |  |

| Legend:    |              |                     |                  |                                         |     |     |       |  |  |  |

| R = Reada  | ble bit      | W = Writable        | bit              | U = Unimplemented bit, read as '0'      |     |     |       |  |  |  |

| -n = Value | at POR       | '1' = Bit is set    |                  | '0' = Bit is cleared x = Bit is unknown |     |     | own   |  |  |  |

|            |              |                     |                  |                                         |     |     |       |  |  |  |

| bit 15-7   | Unimpleme    | nted: Read as '     | )'               |                                         |     |     |       |  |  |  |

| bit 6-4    | JTAGIP<2:0   | >: JTAG Interru     | ot Priority bits |                                         |     |     |       |  |  |  |

|            | 111 = Interr | upt is Priority 7 ( | highest priority | interrupt)                              |     |     |       |  |  |  |

|            | •            |                     |                  |                                         |     |     |       |  |  |  |

|            | •            |                     |                  |                                         |     |     |       |  |  |  |

|            | •            |                     |                  |                                         |     |     |       |  |  |  |

|            | 001 = Interr | upt is Priority 1   |                  |                                         |     |     |       |  |  |  |

000 = Interrupt source is disabled

bit 3-0 Unimplemented: Read as '0'

## REGISTER 13-1: TxCON: TIMER2 AND TIMER4 CONTROL REGISTER<sup>(1)</sup> (CONTINUED)

- bit 3 **T32:** 32-Bit Timer Mode Select bit<sup>(3)</sup>

- 1 = Timerx and Timery form a single 32-bit timer

- 0 = Timerx and Timery act as two 16-bit timers

- In 32-bit mode, T3CON control bits do not affect 32-bit timer operation.

- bit 2 Unimplemented: Read as '0'

- bit 1 **TCS**: Timerx Clock Source Select bit<sup>(2)</sup>

- 1 = Timer source is selected by TECS<1:0>0 = Internal clock (Fosc/2)

- bit 0 Unimplemented: Read as '0'

- **Note 1:** Changing the value of TxCON while the timer is running (TON = 1) causes the timer prescale counter to reset and is not recommended.

- 2: If TCS = 1 and TECS<1:0> = x1, the selected external timer input (TMRCK or TxCK) must be configured to an available RPn/RPIn pin. For more information, see Section 11.4 "Peripheral Pin Select (PPS)".

- **3:** In T4CON, the T45 bit is implemented instead of T32 to select 32-bit mode. In 32-bit mode, the T3CON or T5CON control bits do not affect 32-bit timer operation.

# 14.0 INPUT CAPTURE WITH DEDICATED TIMERS

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"dsPIC33/PIC24 Family Reference Manual"*, *"Input Capture with Dedicated Timer"* (DS39722). The information in this data sheet supersedes the information in the FRM.

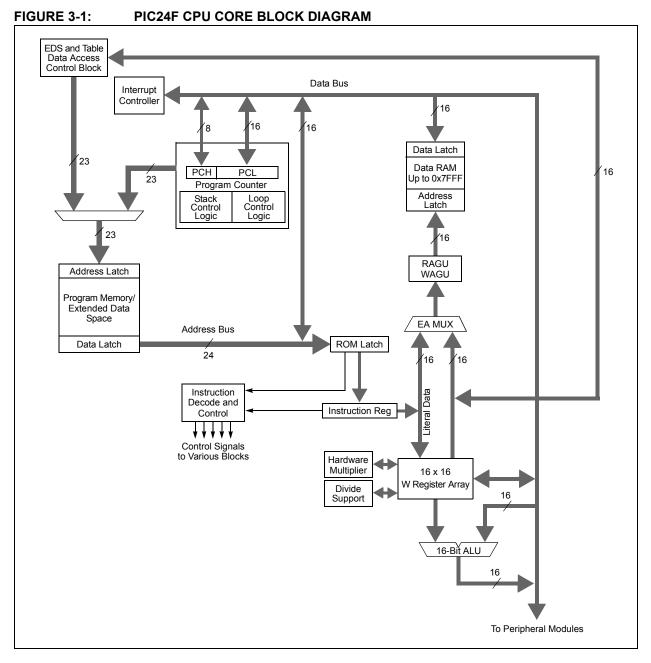

Devices in the PIC24FJ128GA204 family contain six independent input capture modules. Each of the modules offers a wide range of configuration and operating options for capturing external pulse events and generating interrupts.

Key features of the input capture module include:

- Hardware-configurable for 32-bit operation in all modes by cascading two adjacent modules

- Synchronous and Trigger modes of output compare operation with up to 30 user-selectable sync/trigger sources available

- A 4-level FIFO buffer for capturing and holding timer values for several events

- Configurable interrupt generation

- Up to 6 clock sources available for each module, driving a separate, internal 16-bit counter

The module is controlled through two registers: ICxCON1 (Register 14-1) and ICxCON2 (Register 14-2). A general block diagram of the module is shown in Figure 14-1.

## 14.1 General Operating Modes

#### 14.1.1 SYNCHRONOUS AND TRIGGER MODES

When the input capture module operates in a Free-Running mode, the internal 16-bit counter, ICxTMR, counts up continuously, wrapping around from FFFFh to 0000h on each overflow. Its period is synchronized to the selected external clock source. When a capture event occurs, the current 16-bit value of the internal counter is written to the FIFO buffer.

In Synchronous mode, the module begins capturing events on the ICx pin as soon as its selected clock source is enabled. Whenever an event occurs on the selected sync source, the internal counter is reset. In Trigger mode, the module waits for a sync event from another internal module to occur before allowing the internal counter to run.

Standard, free-running operation is selected by setting the SYNCSEL<4:0> bits (ICxCON2<4:0>) to '00000' and clearing the ICTRIG bit (ICxCON2<7>). Synchronous and Trigger modes are selected any time the SYNCSELx bits are set to any value except '00000'. The ICTRIG bit selects either Synchronous or Trigger mode; setting the bit selects Trigger mode operation. In both modes, the SYNCSELx bits determine the sync/trigger source.

When the SYNCSELx bits are set to '00000' and ICTRIG is set, the module operates in Software Trigger mode. In this case, capture operations are started by manually setting the TRIGSTAT bit (ICxCON2<6>).

## 18.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582). The information in this data sheet supersedes the information in the FRM.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the PIC24F device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins. The UART module includes the ISO 7816 compliant Smart Card support and the IrDA<sup>®</sup> encoder/decoder unit.

The PIC24FJ128GA204 family devices are equipped with four UART modules, referred to as UART1, UART2, UART3 and UART4.

The primary features of the UARTx modules are:

- Full-Duplex, 8 or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- One or Two Stop bits

- Hardware Flow Control Option with the UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Range from 61 bps to 4 Mbps at 16 MIPS in 4x mode

- Baud Rates Range from 15 bps to 1 Mbps at 16 MIPS in 16x mode

- 4-Deep, First-In-First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-Bit mode with Address Detect (9<sup>th</sup> bit = 1)

- · Separate Transmit and Receive Interrupts

- · Loopback mode for Diagnostic Support

- · Polarity Control for Transmit and Receive Lines

- · Support for Sync and Break Characters

- Supports Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- Includes DMA Support

- 16x Baud Clock Output for IrDA Support

- Smart Card ISO 7816 Support (UART1 and UART2 only):

- T = 0 protocol with automatic error handling

- T = 1 protocol

- Dedicated Guard Time Counter (GTC)

- Dedicated Waiting Time Counter (WTC)

A simplified block diagram of the UARTx module is shown in Figure 18-1. The UARTx module consists of these key important hardware elements:

- Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

- **Note:** Throughout this section, references to register and bit names that may be associated with a specific UART module are referred to generically by the use of 'x' in place of the specific module number. Thus, "UxSTA" might refer to the Status register for either UART1, UART2, UART3 or UART4.

| R/W-0                        | U-0           | R/W-0                           | R/W-0                                 | R/W-0             | U-0                          | R/W-0             | R/W-0       |

|------------------------------|---------------|---------------------------------|---------------------------------------|-------------------|------------------------------|-------------------|-------------|

| PMPEN                        |               | PSIDL                           | ADRMUX1                               | ADRMUX0           | —                            | MODE1             | MODE0       |

| bit 15                       |               |                                 |                                       |                   |                              |                   | bit 8       |

| R/W-0                        | R/W-0         | R/W-0                           | R/W-0                                 | U-0               | R/W-0                        | R/W-0             | R/W-0       |

| CSF1                         | CSF0          | ALP                             | ALMODE                                |                   | BUSKEEP                      | IRQM1             | IRQM0       |

| bit 7                        | 0010          |                                 | ALWODE                                |                   | DUGINELI                     | IIII              | bit         |

|                              |               |                                 |                                       |                   |                              |                   |             |

| Legend:                      |               |                                 | <b>L</b> .1                           |                   | a a material la bita una a s |                   |             |

| R = Readabl<br>-n = Value at |               | W = Writable<br>'1' = Bit is se |                                       | '0' = Bit is clea | nented bit, read             | x = Bit is unkr   |             |

|                              | FOR           |                                 |                                       |                   | areu                         |                   | IOWIT       |

| bit 15                       | PMPEN: EPM    | IP Enable bit                   |                                       |                   |                              |                   |             |

|                              | 1 = EPMP is   |                                 |                                       |                   |                              |                   |             |

|                              | 0 = EPMP is   |                                 |                                       |                   |                              |                   |             |

| bit 14                       | -             | ted: Read as                    |                                       |                   |                              |                   |             |

| bit 13                       |               | P Stop in Idle N                |                                       |                   |                              |                   |             |

|                              |               |                                 | eration when d                        |                   | le mode                      |                   |             |

| bit 12-11                    |               | -                               | ation in Idle moo<br>ata Multiplexing |                   |                              |                   |             |

| DIL 12-11                    |               |                                 | e multiplexed wi                      | •                 |                              | hasos             |             |

|                              |               |                                 | multiplexed wi                        |                   |                              |                   |             |

|                              |               |                                 | multiplexed wi                        |                   |                              |                   |             |

|                              | 00 = Address  | and data app                    | ear on separate                       | pins              |                              |                   |             |

| bit 10                       | Unimplemen    | ted: Read as                    | 0'                                    |                   |                              |                   |             |

| bit 9-8                      | MODE<1:0>:    | Parallel Port I                 | Node Select bits                      | 5                 |                              |                   |             |

|                              | 11 = Master I | mode                            |                                       |                   |                              |                   |             |

|                              |               |                                 | ised are PMRD                         |                   |                              |                   |             |

|                              |               |                                 | ed are PMRD, I                        |                   |                              |                   |             |

| bit 7-6                      |               |                                 | Port: Pins used                       | are PivikD, Pr    | VIVR, PIVICS a               |                   |             |

| DIL 7-0                      | 11 = Reserve  | hip Select Fun                  | CLION DILS                            |                   |                              |                   |             |

|                              |               | u<br>4> is used for (           | Chin Select 1                         |                   |                              |                   |             |

|                              | 01 = Reserve  |                                 |                                       |                   |                              |                   |             |

|                              | 00 = PMCS1    | is used for Ch                  | ip Select 1                           |                   |                              |                   |             |

| bit 5                        | ALP: Addres   | s Latch Polarit                 | y bit                                 |                   |                              |                   |             |

|                              |               |                                 | ALH and PMA                           |                   |                              |                   |             |

| bit 4                        |               | -                               | trobe Mode bit                        | ,                 |                              |                   |             |

|                              |               |                                 | s strobes (each                       | n address phas    | e is only prese              | nt if the current | access woul |

|                              |               |                                 | ss in the latch th                    | •                 | • •                          |                   |             |

|                              |               | "smart" addre                   |                                       |                   |                              |                   |             |

| bit 3                        | Unimplemen    | ted: Read as                    | 0'                                    |                   |                              |                   |             |

| bit 2                        | BUSKEEP: E    | Bus Keeper bit                  |                                       |                   |                              |                   |             |

|                              | 1 = Data bus  | keeps its last                  | alue when not                         | actively being    | driven                       |                   |             |

|                              |               | -                               | pedance state v                       | when not active   | ly being driven              |                   |             |

| bit 1-0                      |               | Interrupt Requ                  |                                       |                   |                              |                   |             |

|                              |               |                                 | vhen Read Buff                        |                   |                              |                   |             |

|                              |               |                                 | peration when H                       | PMA<1:0> = 11     | (Addressable                 | PSP mode on       | у)          |

|                              | 10 = Reserve  | ed                              | peration when F<br>at the end of a i  |                   |                              | PSP mode on       | y)          |

## REGISTER 20-1: PMCON1: EPMP CONTROL REGISTER 1

## REGISTER 20-6: PMCSxBS: EPMP CHIP SELECT x BASE ADDRESS REGISTER<sup>(2)</sup>

| R/W <sup>(1)</sup>                 | R/W <sup>(1)</sup> | R/W <sup>(1)</sup> | R/W <sup>(1)</sup>                                                                                           | R/W <sup>(1)</sup>                                                                                                                      | R/W <sup>(1)</sup>                                                                                                                                                         | R/W <sup>(1)</sup>                                                                                                                                                                                          |  |

|------------------------------------|--------------------|--------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                    |                    | BASE               | <23:16>                                                                                                      |                                                                                                                                         |                                                                                                                                                                            |                                                                                                                                                                                                             |  |

|                                    |                    |                    |                                                                                                              |                                                                                                                                         |                                                                                                                                                                            | bit 8                                                                                                                                                                                                       |  |

|                                    |                    |                    |                                                                                                              |                                                                                                                                         |                                                                                                                                                                            |                                                                                                                                                                                                             |  |

| U-0                                | <u>U-0</u>         | U-0                | R/W(")                                                                                                       | U-0                                                                                                                                     | <u>U-0</u>                                                                                                                                                                 | U-0                                                                                                                                                                                                         |  |

|                                    | —                  | —                  | BASE11                                                                                                       |                                                                                                                                         | —                                                                                                                                                                          |                                                                                                                                                                                                             |  |

|                                    |                    |                    |                                                                                                              |                                                                                                                                         |                                                                                                                                                                            | bit 0                                                                                                                                                                                                       |  |

|                                    |                    |                    |                                                                                                              |                                                                                                                                         |                                                                                                                                                                            |                                                                                                                                                                                                             |  |

|                                    |                    |                    |                                                                                                              |                                                                                                                                         |                                                                                                                                                                            |                                                                                                                                                                                                             |  |

| R = Readable bit W = Writable bit  |                    |                    | U = Unimplemented bit, read as '0'                                                                           |                                                                                                                                         |                                                                                                                                                                            |                                                                                                                                                                                                             |  |

| -n = Value at POR '1' = Bit is set |                    |                    | '0' = Bit is cleared x = Bit is unknow                                                                       |                                                                                                                                         |                                                                                                                                                                            | own                                                                                                                                                                                                         |  |

|                                    | U-0<br>—           | U-0 U-0<br>— — —   | U-0         U-0         U-0           —         —         —           bit         W = Writable bit         W | BASE<23:16>         U-0       U-0       R/W <sup>(1)</sup> —       —       BASE11         Dit       W = Writable bit       U = Unimplem | BASE<23:16>         U-0       U-0       R/W <sup>(1)</sup> U-0         —       —       BASE11       —         bit       W = Writable bit       U = Unimplemented bit, read | BASE<23:16>         U-0       U-0       R/W <sup>(1)</sup> U-0       U-0         —       —       —       BASE11       —       —         bit       W = Writable bit       U = Unimplemented bit, read as '0' |  |

bit 15-7 BASE<23:15>: Chip Select x Base Address bits<sup>(1)</sup>

bit 6-4 Unimplemented: Read as '0'

bit 3 **BASE11:** Chip Select x Base Address bit<sup>(1)</sup>

bit 2-0 Unimplemented: Read as '0'

Note 1: The value at POR is 0080h for PMCS1BS and 0880h for PMCS2BS.

2: If the whole PMCS2BS register is written together as 0x0000, then the last EDS address for Chip Select 1 will be FFFFFFh. In this case, Chip Select 2 should not be used. PMCS1BS has no such feature.

## 27.0 CHARGE TIME MEASUREMENT UNIT (CTMU)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Charge Time Measurement Unit, refer to the "dsPIC33/PIC24 Family Reference Manual", "Charge Time Measurement Unit (CTMU) with Threshold Detect" (DS39743).

The Charge Time Measurement Unit (CTMU) is a flexible analog module that provides charge measurement, accurate differential time measurement between pulse sources and asynchronous pulse generation. Its key features include:

- Thirteen external edge input trigger sources

- · Polarity control for each edge source

- · Control of edge sequence

- Control of response to edge levels or edge transitions

- Time measurement resolution of one nanosecond

- Accurate current source suitable for capacitive measurement

Together with other on-chip analog modules, the CTMU can be used to precisely measure time, measure capacitance, measure relative changes in capacitance or generate output pulses that are independent of the system clock. The CTMU module is ideal for interfacing with capacitive-based touch sensors.

The CTMU is controlled through three registers: CTMUCON1, CTMUCON2 and CTMUICON. CTMUCON1 enables the module and controls the mode of operation of the CTMU, as well as controlling edge sequencing. CTMUCON2 controls edge source selection and edge source polarity selection. The CTMUICON register selects the current range of current source and trims the current.

## 27.1 Measuring Capacitance

The CTMU module measures capacitance by generating an output pulse, with a width equal to the time between edge events, on two separate input channels. The pulse edge events to both input channels can be selected from four sources: two internal peripheral modules (OC1 and Timer1) and up to 13 external pins (CTED1 through CTED13). This pulse is used with the module's precision current source to calculate capacitance according to the relationship:

#### EQUATION 27-1:

$$I = C \bullet \frac{dV}{dT}$$

For capacitance measurements, the A/D Converter samples an external Capacitor (CAPP) on one of its input channels after the CTMU output's pulse. A Precision Resistor (RPR) provides current source calibration on a second A/D channel. After the pulse ends, the converter determines the voltage on the capacitor. The actual calculation of capacitance is performed in software by the application.

Figure 27-1 illustrates the external connections used for capacitance measurements and how the CTMU and A/D modules are related in this application. This example also shows the edge events coming from Timer1, but other configurations using external edge sources are possible. A detailed discussion on measuring capacitance and time with the CTMU module is provided in the *"dsPIC33/PIC24 Family Reference Manual"*, **"Charge Time Measurement Unit (CTMU) with Threshold Detect"** (DS39743).

# PIC24FJ128GA204 FAMILY

| R/W-0         | R/W-0                                                                                                   | R/W-0                            | R/W-0           | R/W-0             | R/W-0            | R/W-0           | R/W-0    |  |  |  |  |

|---------------|---------------------------------------------------------------------------------------------------------|----------------------------------|-----------------|-------------------|------------------|-----------------|----------|--|--|--|--|

| EDG1MOD       | EDG1POL                                                                                                 | EDG1SEL3                         | EDG1SEL2        | EDG1SEL1          | EDG1SEL0         | EDG2STAT        | EDG1STAT |  |  |  |  |

| bit 15        |                                                                                                         |                                  |                 |                   |                  |                 | bit 8    |  |  |  |  |

|               |                                                                                                         |                                  |                 |                   |                  |                 |          |  |  |  |  |

| R/W-0         | R/W-0                                                                                                   | R/W-0 R/W-0                      |                 | R/W-0             | R/W-0            | U-0             | U-0      |  |  |  |  |

| EDG2MOD       | EDG2POL                                                                                                 | EDG2SEL3                         | EDG2SEL2        | EDG2SEL1          | EDG2SEL0         | —               | —        |  |  |  |  |

| bit 7         |                                                                                                         |                                  |                 |                   |                  |                 | bit 0    |  |  |  |  |

|               |                                                                                                         |                                  |                 |                   |                  |                 |          |  |  |  |  |

| Legend:       |                                                                                                         |                                  |                 |                   |                  |                 |          |  |  |  |  |

| R = Readable  | bit                                                                                                     | W = Writable I                   | oit             | U = Unimplen      | nented bit, read | l as '0'        |          |  |  |  |  |

| -n = Value at | POR                                                                                                     | '1' = Bit is set                 |                 | '0' = Bit is clea | ared             | x = Bit is unkr | nown     |  |  |  |  |

|               |                                                                                                         |                                  |                 |                   |                  |                 |          |  |  |  |  |

| bit 15        |                                                                                                         | Edge 1 Edge-Se                   | ensitive Select | bit               |                  |                 |          |  |  |  |  |

|               | 1 = Input is ed                                                                                         |                                  |                 |                   |                  |                 |          |  |  |  |  |

|               | 0 = Input is le                                                                                         |                                  |                 |                   |                  |                 |          |  |  |  |  |

| bit 14        |                                                                                                         | dge 1 Polarity                   |                 |                   |                  |                 |          |  |  |  |  |

|               | 1 = Edge 1 is programmed for a positive edge response                                                   |                                  |                 |                   |                  |                 |          |  |  |  |  |

| bit 13-10     | 0 = Edge 1 is programmed for a negative edge response                                                   |                                  |                 |                   |                  |                 |          |  |  |  |  |

| 51115-10      | EDG1SEL<3:0>: Edge 1 Source Select bits                                                                 |                                  |                 |                   |                  |                 |          |  |  |  |  |

|               | 1111 = Edge 1 source is Comparator 3 output<br>1110 = Edge 1 source is Comparator 2 output              |                                  |                 |                   |                  |                 |          |  |  |  |  |

|               | 1101 = Edge 1 source is Comparator 1 output                                                             |                                  |                 |                   |                  |                 |          |  |  |  |  |

|               | 1100 = Edge 1 source is IC3                                                                             |                                  |                 |                   |                  |                 |          |  |  |  |  |

|               | 1011 = Edge 1 source is IC2                                                                             |                                  |                 |                   |                  |                 |          |  |  |  |  |

|               | 1010 = Edge 1 source is IC1<br>1001 = Edge 1 source is CTED8                                            |                                  |                 |                   |                  |                 |          |  |  |  |  |

|               |                                                                                                         | 1 source is CT                   |                 |                   |                  |                 |          |  |  |  |  |

|               |                                                                                                         | 1 source is CT                   |                 |                   |                  |                 |          |  |  |  |  |

|               |                                                                                                         | 1 source is CT                   |                 |                   |                  |                 |          |  |  |  |  |

|               | •                                                                                                       | 1 source is CT                   |                 |                   |                  |                 |          |  |  |  |  |

|               | •                                                                                                       | 1 source is CT<br>1 source is CT |                 |                   |                  |                 |          |  |  |  |  |

|               |                                                                                                         | 1 source is CT                   |                 |                   |                  |                 |          |  |  |  |  |

|               | 0001 = Edge 1 source is OC1                                                                             |                                  |                 |                   |                  |                 |          |  |  |  |  |

|               | 0000 <b>= Edge</b>                                                                                      | 1 source is Tim                  | ner1            |                   |                  |                 |          |  |  |  |  |

| bit 9         |                                                                                                         | Edge 2 Status b                  |                 |                   |                  |                 |          |  |  |  |  |

|               | Indicates the status of Edge 2 and can be written to control current source.                            |                                  |                 |                   |                  |                 |          |  |  |  |  |

|               | 1 = Edge 2 has occurred<br>0 = Edge 2 has not occurred                                                  |                                  |                 |                   |                  |                 |          |  |  |  |  |

| hit Q         | -                                                                                                       |                                  | i+              |                   |                  |                 |          |  |  |  |  |

| bit 8         | EDG1STAT: Edge 1 Status bit                                                                             |                                  |                 |                   |                  |                 |          |  |  |  |  |

|               | Indicates the status of Edge 1 and can be written to control current source.<br>1 = Edge 1 has occurred |                                  |                 |                   |                  |                 |          |  |  |  |  |

|               | 0 = Edge 1 has occurred                                                                                 |                                  |                 |                   |                  |                 |          |  |  |  |  |

| bit 7         | -                                                                                                       | Edge 2 Edge-Se                   | ensitive Select | bit               |                  |                 |          |  |  |  |  |