#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, LVD, POR, PWM, WDT                                |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

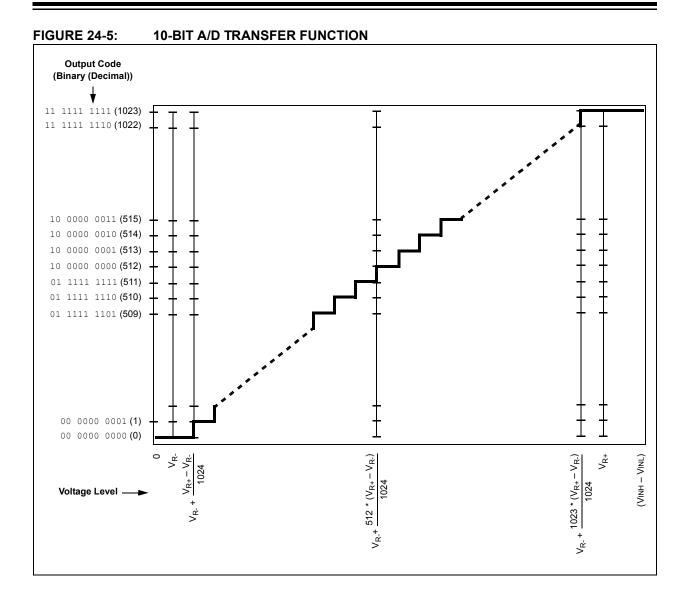

| Data Converters            | A/D 13x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

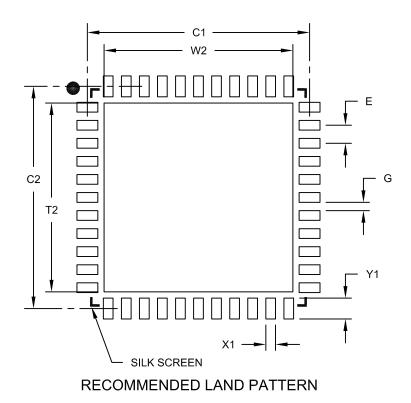

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-TQFP                                                                        |

| Supplier Device Package    | 44-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128ga204-e-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

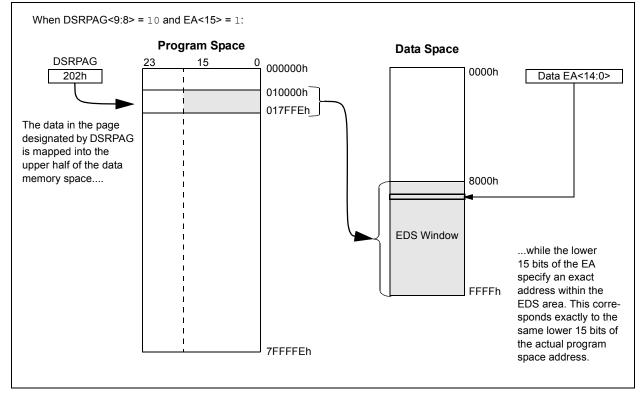

## FIGURE 4-10: PROGRAM SPACE VISIBILITY OPERATION TO ACCESS LOWER WORD

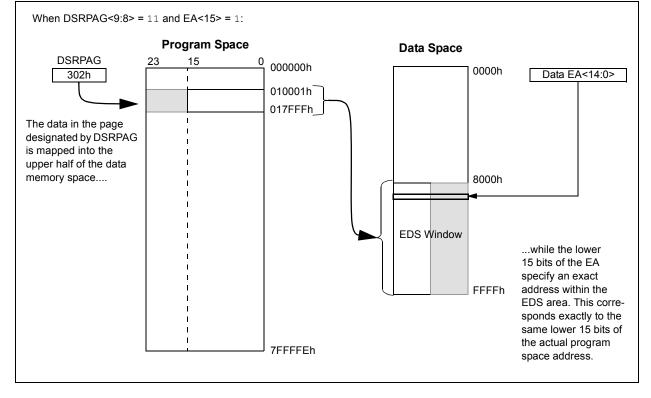

#### FIGURE 4-11: PROGRAM SPACE VISIBILITY OPERATION TO ACCESS UPPER WORD

| U-0           | R/W-1                                                                                                                          | R/W-0                                                      | R/W-0            | U-0              | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|------------------|------------------|------------------|-----------------|---------|--|--|--|--|

| _             | SPI3TXIP2                                                                                                                      | SPI3TXIP1                                                  | SPI3TXIP0        |                  | SPI3IP2          | SPI3IP1         | SPI3IP0 |  |  |  |  |

| bit 15        |                                                                                                                                |                                                            |                  |                  |                  |                 | bit     |  |  |  |  |

| U-0           | R/W-1                                                                                                                          | R/W-0                                                      | R/W-0            | U-0              | R/W-1            | R/W-0           | R/W-0   |  |  |  |  |

|               | U4TXIP2                                                                                                                        | U4TXIP1                                                    | U4TXIP0          |                  | U4RXIP2          | U4RXIP1         | U4RXIP0 |  |  |  |  |

| bit 7         | 0117412                                                                                                                        | <b>O</b> TIXE T                                            | 0 TIXII 0        |                  | 0 notin 2        | <b>O</b> HOULT  | bit     |  |  |  |  |

|               |                                                                                                                                |                                                            |                  |                  |                  |                 |         |  |  |  |  |

| Legend:       |                                                                                                                                |                                                            |                  |                  |                  |                 |         |  |  |  |  |

| R = Readabl   |                                                                                                                                | W = Writable                                               |                  |                  | mented bit, reac |                 |         |  |  |  |  |

| -n = Value at | t POR                                                                                                                          | '1' = Bit is set                                           |                  | '0' = Bit is cle | ared             | x = Bit is unkr | IOWN    |  |  |  |  |

| bit 15        | Unimplement                                                                                                                    | ted: Read as '                                             | )'               |                  |                  |                 |         |  |  |  |  |

| bit 14-12     | -                                                                                                                              | >: SPI3 Trans                                              |                  | riority bits     |                  |                 |         |  |  |  |  |

|               | 111 = Interrup                                                                                                                 | ot is Priority 7 (                                         | highest priority | / interrupt)     |                  |                 |         |  |  |  |  |

|               | •                                                                                                                              | •                                                          |                  |                  |                  |                 |         |  |  |  |  |

|               | •                                                                                                                              |                                                            |                  |                  |                  |                 |         |  |  |  |  |

|               | 001 = Interrupt is Priority 1                                                                                                  |                                                            |                  |                  |                  |                 |         |  |  |  |  |

|               | -                                                                                                                              | ot source is dis                                           |                  |                  |                  |                 |         |  |  |  |  |

| bit 11        | -                                                                                                                              | ted: Read as '                                             |                  |                  |                  |                 |         |  |  |  |  |

| bit 10-8      | SPI3IP<2:0>: SPI3 General Interrupt Priority bits                                                                              |                                                            |                  |                  |                  |                 |         |  |  |  |  |

|               | <ul> <li>111 = Interrupt is Priority 7 (highest priority interrupt)</li> </ul>                                                 |                                                            |                  |                  |                  |                 |         |  |  |  |  |

|               | •                                                                                                                              |                                                            |                  |                  |                  |                 |         |  |  |  |  |

|               | •                                                                                                                              | at in Driamity 1                                           |                  |                  |                  |                 |         |  |  |  |  |

|               | 001 = Interrup                                                                                                                 | ot is Phonity 1                                            | abled            |                  |                  |                 |         |  |  |  |  |

| bit 7         | -                                                                                                                              | ted: Read as '                                             |                  |                  |                  |                 |         |  |  |  |  |

| bit 6-4       | -                                                                                                                              | : UART4 Trans                                              |                  | t Priority bits  |                  |                 |         |  |  |  |  |

|               | 111 = Interrup                                                                                                                 | 111 = Interrupt is Priority 7 (highest priority interrupt) |                  |                  |                  |                 |         |  |  |  |  |

|               | •                                                                                                                              |                                                            |                  |                  |                  |                 |         |  |  |  |  |

|               | •                                                                                                                              |                                                            |                  |                  |                  |                 |         |  |  |  |  |

|               | 001 = Interrup                                                                                                                 |                                                            |                  |                  |                  |                 |         |  |  |  |  |

|               | -                                                                                                                              | ot source is dis                                           |                  |                  |                  |                 |         |  |  |  |  |

| bit 3         | Unimplemented: Read as '0'                                                                                                     |                                                            |                  |                  |                  |                 |         |  |  |  |  |

| bit 2-0       | <b>U4RXIP&lt;2:0&gt;:</b> UART4 Receiver Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt) |                                                            |                  |                  |                  |                 |         |  |  |  |  |

|               | •                                                                                                                              |                                                            | nighest phonty   | interrupt)       |                  |                 |         |  |  |  |  |

|               | •                                                                                                                              |                                                            |                  |                  |                  |                 |         |  |  |  |  |

|               |                                                                                                                                |                                                            |                  |                  |                  |                 |         |  |  |  |  |

|               | •<br>001 = Interrup                                                                                                            | t is Driority 1                                            |                  |                  |                  |                 |         |  |  |  |  |

### REGISTER 8-42: IPC22: INTERRUPT PRIORITY CONTROL REGISTER 22

| R/W-0        | U-0                                | R/W-0                                                                                                                                                                            | R/W-0                | R-0                       | R/W-0             | R-0            | R/W-0   |  |

|--------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------------------|-------------------|----------------|---------|--|

| STEN         | —                                  | STSIDL                                                                                                                                                                           | STSRC <sup>(1)</sup> | STLOCK                    | STLPOL            | STOR           | STORPOL |  |

| bit 15       |                                    |                                                                                                                                                                                  |                      |                           |                   |                | bit     |  |

| U-0          | U-0                                | R/W-0                                                                                                                                                                            | R/W-0                | R/W-0                     | R/W-0             | R/W-0          | R/W-0   |  |

| _            | -                                  | TUN5                                                                                                                                                                             | TUN4                 | TUN3                      | TUN2              | TUN1           | TUN0    |  |

| bit 7        |                                    |                                                                                                                                                                                  |                      |                           |                   |                | bit     |  |

| Legend:      |                                    |                                                                                                                                                                                  |                      |                           |                   |                |         |  |

| R = Readab   | ole bit                            | W = Writable                                                                                                                                                                     | bit                  | U = Unimplem              | nented bit, read  | l as '0'       |         |  |

| -n = Value a | It POR                             | '1' = Bit is set                                                                                                                                                                 |                      | '0' = Bit is clea         | ared              | x = Bit is unk | nown    |  |

| bit 15       | 1 = FRC sel                        | Self-Tune Enat<br>f-tuning is enabl<br>f-tuning is disab                                                                                                                         | ed; TUNx bits a      |                           |                   | bits           |         |  |

| bit 14       | Unimpleme                          | nted: Read as '                                                                                                                                                                  | 0'                   |                           |                   |                |         |  |

| bit 13       | STSIDL: FR                         | C Self-Tune Sto                                                                                                                                                                  | p in Idle bit        |                           |                   |                |         |  |

|              |                                    | ng stops during<br>ng continues du                                                                                                                                               |                      |                           |                   |                |         |  |

| bit 12       | STSRC: FR                          | C Self-Tune Ret                                                                                                                                                                  | ference Clock S      | Source bit <sup>(1)</sup> |                   |                |         |  |

|              |                                    | 1 = Reserved<br>0 = FRC is tuned to approximately match the 32.768 kHz SOSC tolerance                                                                                            |                      |                           |                   |                |         |  |

| bit 11       | STLOCK: F                          | RC Self-Tune Lo                                                                                                                                                                  | ock Status bit       |                           |                   |                |         |  |

|              |                                    | <ul> <li>1 = FRC accuracy is currently within ±0.2% of the STSRC reference accuracy</li> <li>0 = FRC accuracy may not be within ±0.2% of the STSRC reference accuracy</li> </ul> |                      |                           |                   |                |         |  |

| bit 10       | STLPOL: FI                         | RC Self-Tune Lo                                                                                                                                                                  | ock Interrupt Po     | larity bit                |                   |                |         |  |

|              |                                    | ne lock interrup                                                                                                                                                                 |                      |                           |                   |                |         |  |

| bit 9        | STOR: FRC                          | Self-Tune Out                                                                                                                                                                    | of Range Status      | s bit                     |                   |                |         |  |

|              |                                    | reference clock<br>reference clock                                                                                                                                               |                      |                           |                   |                | med     |  |

| bit 8        | STORPOL:                           | FRC Self-Tune                                                                                                                                                                    | Out of Range li      | nterrupt Polarity         | y bit             |                |         |  |

|              |                                    | ne out of range ne out of range                                                                                                                                                  |                      |                           |                   |                |         |  |

| bit 7-6      | Unimpleme                          | nted: Read as '                                                                                                                                                                  | 0'                   |                           |                   |                |         |  |

| bit 5-0      | TUN<5:0>:                          | FRC Oscillator                                                                                                                                                                   | Funing bits          |                           |                   |                |         |  |

|              |                                    | laximum freque                                                                                                                                                                   | ncy deviation        |                           |                   |                |         |  |

|              | 011110 =                           |                                                                                                                                                                                  |                      |                           |                   |                |         |  |

|              | •                                  |                                                                                                                                                                                  |                      |                           |                   |                |         |  |

|              | •                                  |                                                                                                                                                                                  |                      |                           |                   |                |         |  |

|              | 000001 =<br>000000 = C<br>111111 = | enter frequency                                                                                                                                                                  | , oscillator is ru   | nning at factory          | v calibrated free | quency         |         |  |

|              | •                                  |                                                                                                                                                                                  |                      |                           |                   |                |         |  |

|              | •                                  |                                                                                                                                                                                  |                      |                           |                   |                |         |  |

|              | 100001 =                           |                                                                                                                                                                                  |                      |                           |                   |                |         |  |

|              | 100000 = M                         | linimum frequen                                                                                                                                                                  | cv deviation         |                           |                   |                |         |  |

## Note 1: Use of either clock recovery source has specific application requirements. For more information, see Section 9.5 "FRC Self-Tuning".

A recommended code sequence for a clock switch includes the following:

- 1. Disable interrupts during the OSCCON register unlock and write sequence.

- Execute the unlock sequence for the OSCCON high byte by writing 78h and 9Ah to OSCCON<15:8> in two back-to-back instructions.

- 3. Write the new oscillator source to the NOSCx bits in the instruction immediately following the unlock sequence.

- Execute the unlock sequence for the OSCCON low byte by writing 46h and 57h to OSCCON<7:0> in two back-to-back instructions.

- 5. Set the OSWEN bit in the instruction immediately following the unlock sequence.

- 6. Continue to execute code that is not clock- sensitive (optional).

- 7. Invoke an appropriate amount of software delay (cycle counting) to allow the selected oscillator and/or PLL to start and stabilize.

- Check to see if OSWEN is '0'. If it is, the switch was successful. If OSWEN is still set, then check the LOCK bit to determine the cause of the failure.

The core sequence for unlocking the OSCCON register and initiating a clock switch is shown in Example 9-1.

#### EXAMPLE 9-1: BASIC CODE SEQUENCE FOR CLOCK SWITCHING

| ;Place the new oscillator selection in WO |

|-------------------------------------------|

| ;OSCCONH (high byte) Unlock Sequence      |

| MOV #OSCCONH, w1                          |

| MOV #0x78, w2                             |

| MOV #0x9A, w3                             |

| MOV.b w2, [w1]                            |

| MOV.b w3, [w1]                            |

| ;Set new oscillator selection             |

| MOV.b WREG, OSCCONH                       |

| ;OSCCONL (low byte) unlock sequence       |

| MOV #OSCCONL, w1                          |

| MOV #0x46, w2                             |

| MOV #0x57, w3                             |

| MOV.b w2, [w1]                            |

| MOV.b w3, [w1]                            |

| ;Start oscillator switch operation        |

| BSET OSCCON,#0                            |

|                                           |

## 9.5 FRC Self-Tuning

PIC24FJ128GA204 family devices include an automatic mechanism to calibrate the FRC during run time. This system uses clock recovery from a source of known accuracy to maintain the FRC within a very narrow margin of its nominal 8 MHz frequency. This allows for a frequency accuracy that exceeds 0.25%, which is well within the requirements.

The self-tune system is controlled by the bits in the upper half of the OSCTUN register. Setting the STEN bit (OSCTUN<15>) enables the system, causing it to recover a calibration clock from a source selected by the STSRC bit (OSCTUN<12>). When STSRC = 0, the system uses the crystal controlled SOSC for its calibration source. Regardless of the source, the system uses the TUN<5:0> bits (OSCTUN<5:0>) to change the FRC's frequency. Frequency monitoring and adjustment is dynamic, occurring continuously during run time. While the system is active, the TUNx bits cannot be written to by software.

| Note: | If the SOSC is to be used as the clock |  |  |  |  |  |

|-------|----------------------------------------|--|--|--|--|--|

|       | recovery source (STSRC = 0), the SOSC  |  |  |  |  |  |

|       | must always be enabled.                |  |  |  |  |  |

The self-tune system can generate a hardware interrupt, FSTIF. The interrupt can result from a drift of the FRC from the reference by greater than 0.2% in either direction or whenever the frequency deviation is beyond the ability of the TUNx bits to correct (i.e., greater than 1.5%). The STLOCK and STOR status bits (OSCTUN<11,9>) are used to indicate these conditions.

The STLPOL and STORPOL bits (OSCTUN<10,8>) configure the FSTIF interrupt to occur in the presence or the absence of the conditions. It is the user's responsibility to monitor both the STLOCK and STOR bits to determine the exact cause of the interrupt.

Note: The STLPOL and STORPOL bits should be ignored when the self-tune system is disabled (STEN = 0).

## 10.4 Deep Sleep Mode

Deep Sleep mode provides the lowest levels of power consumption available from the instruction-based modes.

Deep Sleep mode has these features:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption will be reduced to a minimum.

- The I/O pin directions and states are frozen.

- The Fail-Safe Clock Monitor does not operate during Sleep mode since the system clock source is disabled.

- The LPRC clock will continue to run in Deep Sleep mode if the WDT or RTCC, with LPRC as the clock source, is enabled.

- The dedicated Deep Sleep WDT and BOR systems, if enabled, are used.

- The RTCC and its clock source continue to run, if enabled. All other peripherals are disabled.

Entry into Deep Sleep mode is completely under software control. Exiting from the Deep Sleep mode can be triggered from any of the following events:

- POR event

- MCLR event

- RTCC alarm (If the RTCC is present)

- External Interrupt 0

- Deep Sleep Watchdog Timer (DSWDT) time-out

### 10.4.1 ENTERING DEEP SLEEP MODE

Deep Sleep mode is entered by setting the DSEN bit in the DSCON register and then executing a Sleep command (PWRSAV #SLEEP\_MODE), within one instruction cycle, to minimize the chance that Deep Sleep will be spuriously entered.

If the PWRSAV command is not given within one instruction cycle, the DSEN bit will be cleared by the hardware and must be set again by the software before entering Deep Sleep mode. The DSEN bit is also automatically cleared when exiting Deep Sleep mode.

**Note:** To re-enter Deep Sleep after a Deep Sleep wake-up, allow a delay of at least 3 TcY after clearing the RELEASE bit.

The sequence to enter Deep Sleep mode is:

- If the application requires the Deep Sleep WDT, enable it and configure its clock source. For more information on Deep Sleep WDT, see Section 10.4.5 "Deep Sleep WDT".

- If the application requires Deep Sleep BOR, enable it by programming the DSBOREN Configuration bit (CW4<6>).

- 3. If the application requires wake-up from Deep Sleep on RTCC alarm, enable and configure the RTCC module. For more information on RTCC, see Section 21.0 "Real-Time Clock and Calendar (RTCC)".

- If needed, save any critical application context data by writing it to the DSGPR0 and DSGPR1 registers (optional).

- 5. Enable Deep Sleep mode by setting the DSEN bit (DSCON<15>).

- Note: A repeat sequence is required to set the DSEN bit. The repeat sequence (repeating the instruction twice) is required to write into any of the Deep Sleep registers (DSCON, DSWAKE, DSGPR0, DSGPR1). This is required to prevent the user from entering Deep Sleep by mistake. Any write to these registers has to be done twice to actually complete the write (see Example 10-2).

- 6. Enter Deep Sleep mode by issuing 3 NOP commands and then a PWRSAV #0 instruction.

Any time the DSEN bit is set, all bits in the DSWAKE register will be automatically cleared.

### EXAMPLE 10-2: THE REPEAT SEQUENCE

| ; enable DS                       |

|-----------------------------------|

|                                   |

| ; second write required to        |

| actually write to DSCON           |

|                                   |

|                                   |

|                                   |

|                                   |

|                                   |

|                                   |

| ; enable DS (two writes required) |

|                                   |

## 11.4 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. In an application that needs to use more than one peripheral multiplexed on a single pin, inconvenient work arounds in application code, or a complete redesign, may be the only option.

The Peripheral Pin Select (PPS) feature provides an alternative to these choices by enabling the user's peripheral set selection and its placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the microcontroller to their entire application, rather than trimming the application to fit the device.

The Peripheral Pin Select feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of any one of many digital peripherals to any one of these I/O pins. PPS is performed in software and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

#### 11.4.1 AVAILABLE PINS

The PPS feature is used with a range of up to 44 pins, depending on the particular device and its pin count. Pins that support the Peripheral Pin Select feature include the designation, "RPn" or "RPIn", in their full pin designation, where "n" is the remappable pin number. "RP" is used to designate pins that support both remappable input and output functions, while "RPI" indicates pins that support remappable input functions only.

PIC24FJ128GA204 family devices support a larger number of remappable input only pins than remappable input/output pins. In this device family, there are up to 25 remappable input/output pins, depending on the pin count of the particular device selected. These pins are numbered, RP0 through RP25.

See Table 1-3 for a summary of pinout options in each package offering.

#### 11.4.2 AVAILABLE PERIPHERALS

The peripherals managed by the PPS are all digital only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer related peripherals (input capture and output compare) and external interrupt inputs. Also included are the outputs of the comparator module, since these are discrete digital signals. PPS is not available for these peripherals:

- $I^2C^{TM}$  (input and output)

- Change Notification Inputs

- RTCC Alarm Output(s)

- EPMP Signals (input and output)

- Analog (inputs and outputs)

- INT0

A key difference between pin select and non-pin select peripherals is that pin select peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-pin select peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

#### 11.4.2.1 Peripheral Pin Select Function Priority

Pin-selectable peripheral outputs (e.g., output compare, UART transmit) will take priority over general purpose digital functions on a pin, such as EPMP and port I/O. Specialized digital outputs will take priority over PPS outputs on the same pin. The pin diagrams list peripheral outputs in the order of priority. Refer to them for priority concerns on a particular pin.

Unlike PIC24F devices with fixed peripherals, pinselectable peripheral inputs will never take ownership of a pin. The pin's output buffer will be controlled by the TRISx setting or by a fixed peripheral on the pin. If the pin is configured in Digital mode, then the PPS input will operate correctly. If an analog function is enabled on the pin, the PPS input will be disabled.

#### 11.4.3 CONTROLLING PERIPHERAL PIN SELECT

PPS features are controlled through two sets of Special Function Registers (SFRs): one to map peripheral inputs and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral-selectable pin is handled in two different ways, depending on if an input or an output is being mapped.

## REGISTER 11-10: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

| U-0     | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|---------|-----|--------|--------|--------|--------|--------|--------|

| —       | —   | OCFBR5 | OCFBR4 | OCFBR3 | OCFBR2 | OCFBR1 | OCFBR0 |

| bit 15  | •   |        |        |        |        |        | bit 8  |

|         |     |        |        |        |        |        |        |

| U-0     | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

| —       | —   | OCFAR5 | OCFAR4 | OCFAR3 | OCFAR2 | OCFAR1 | OCFAR0 |

| bit 7   |     |        |        |        |        |        | bit 0  |

|         |     |        |        |        |        |        |        |

| Legend: |     |        |        |        |        |        |        |

| Legena.           |                  |                       |                    |  |

|-------------------|------------------|-----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |  |

| bit 15-14 | Unimplemented: Read as '0'                                                             |

|-----------|----------------------------------------------------------------------------------------|

| bit 13-8  | OCFBR<5:0>: Assign Output Compare Fault B (OCFB) to Corresponding RPn or RPIn Pin bits |

| bit 7-6   | Unimplemented: Read as '0'                                                             |

| bit 5-0   | OCFAR<5:0>: Assign Output Compare Fault A (OCFA) to Corresponding RPn or RPIn Pin bits |

## REGISTER 11-11: RPINR17: PERIPHERAL PIN SELECT INPUT REGISTER 17

| U-0    | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1  | R/W-1 | R/W-1 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| —      | —   |       |       | U3RXI | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

| U-0         | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 |

|-------------|-----|-----|-----|-----|-----|-----|-----|

| —           | —   | —   | —   | —   | —   | —   | —   |

| bit 7 bit 0 |     |     |     |     |     |     |     |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 U3RXR<5:0>: Assign UART3 Receive (U3RX) to Corresponding RPn or RPIn Pin bits

bit 7-0 Unimplemented: Read as '0'

#### REGISTER 11-12: RPINR18: PERIPHERAL PIN SELECT INPUT REGISTER 18

| U-0    | U-0 | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   |

|--------|-----|---------|---------|---------|---------|---------|---------|

| —      | —   | U1CTSR5 | U1CTSR4 | U1CTSR3 | U1CTSR2 | U1CTSR1 | U1CTSR0 |

| bit 15 |     |         |         |         |         |         | bit 8   |

| U-0   | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | U1RXR5 | U1RXR4 | U1RXR3 | U1RXR2 | U1RXR1 | U1RXR0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                            |

|-----------|---------------------------------------------------------------------------------------|

| bit 13-8  | U1CTSR<5:0>: Assign UART1 Clear-to-Send (U1CTS) to Corresponding RPn or RPIn Pin bits |

| bit 7-6   | Unimplemented: Read as '0'                                                            |

| bit 5-0   | U1RXR<5:0>: Assign UART1 Receive (U1RX) to Corresponding RPn or RPIn Pin bits         |

### REGISTER 11-13: RPINR19: PERIPHERAL PIN SELECT INPUT REGISTER 19

| U-0    | U-0 | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   |

|--------|-----|---------|---------|---------|---------|---------|---------|

| —      | —   | U2CTSR5 | U2CTSR4 | U2CTSR3 | U2CTSR2 | U2CTSR1 | U2CTSR0 |

| bit 15 |     |         |         |         |         |         | bit 8   |

| U-0   | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | U2RXR5 | U2RXR4 | U2RXR3 | U2RXR2 | U2RXR1 | U2RXR0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 U2CTSR<5:0>: Assign UART2 Clear-to-Send (U2CTS) to Corresponding RPn or RPIn Pin bits

bit 7-6 Unimplemented: Read as '0'

bit 5-0 U2RXR<5:0>: Assign UART2 Receive (U2RX) to Corresponding RPn or RPIn Pin bits

| R/W-0              | U-0                                    | R/W-0                     | U-0                     | U-0                        | U-0             | R/W-0                     | R/W-0                 |

|--------------------|----------------------------------------|---------------------------|-------------------------|----------------------------|-----------------|---------------------------|-----------------------|

| TON <sup>(2)</sup> | —                                      | TSIDL <sup>(2)</sup>      | —                       | _                          | _               | TECS1 <sup>(2,3)</sup>    | TECS0 <sup>(2,3</sup> |

| bit 15             |                                        |                           |                         |                            |                 |                           | bit                   |

|                    |                                        |                           |                         |                            |                 |                           |                       |

| U-0                | R/W-0                                  | R/W-0                     | R/W-0                   | U-0                        | U-0             | R/W-0                     | U-0                   |

| _                  | TGATE <sup>(2)</sup>                   | TCKPS1 <sup>(2)</sup>     | TCKPS0 <sup>(2)</sup>   | _                          | —               | TCS <sup>(2,3)</sup>      | _                     |

| bit 7              |                                        |                           |                         |                            |                 |                           | bit                   |

| Legend:            |                                        |                           |                         |                            |                 |                           |                       |

| R = Reada          | ble bit                                | W = Writable              | bit                     | U = Unimpler               | nented bit, rea | ad as '0'                 |                       |

| -n = Value         | at POR                                 | '1' = Bit is set          |                         | '0' = Bit is cle           | ared            | x = Bit is unkn           | iown                  |

|                    |                                        |                           |                         |                            |                 |                           |                       |

| bit 15             | TON: Timery                            |                           |                         |                            |                 |                           |                       |

|                    | 1 = Starts 16-<br>0 = Stops 16-        |                           |                         |                            |                 |                           |                       |

| bit 14             | •                                      | ted: Read as '            | )'                      |                            |                 |                           |                       |

| bit 13             | TSIDL: Timer                           | ry Stop in Idle M         | lode bit <sup>(2)</sup> |                            |                 |                           |                       |

|                    |                                        | ues module ope            |                         |                            | lle mode        |                           |                       |

|                    |                                        | s module opera            |                         | de                         |                 |                           |                       |

| bit 12-10          | -                                      | ted: Read as '            |                         |                            |                 | (2.2)                     |                       |

| bit 9-8            |                                        | Timery Extende            |                         | -                          | selected when   | TCS = 1) <sup>(2,3)</sup> |                       |

|                    | 11 = Generic<br>10 = LPRC C            | Timer (TMRCK              | () External Inpu        | ut                         |                 |                           |                       |

|                    |                                        | xternal Clock In          | put                     |                            |                 |                           |                       |

|                    | 00 <b>= SOSC</b>                       |                           | •                       |                            |                 |                           |                       |

| bit 7              | Unimplemen                             | ted: Read as '            | )'                      |                            |                 |                           |                       |

| bit 6              | TGATE: Time                            | ery Gated Time            | Accumulation            | Enable bit <sup>(2)</sup>  |                 |                           |                       |

|                    | When TCS =                             |                           |                         |                            |                 |                           |                       |

|                    | This bit is ign<br>When TCS =          |                           |                         |                            |                 |                           |                       |

|                    |                                        | <u></u><br>ne accumulatio | n is enabled            |                            |                 |                           |                       |

|                    | 0 = Gated tin                          | ne accumulatio            | n is disabled           |                            |                 |                           |                       |

| bit 5-4            | TCKPS<1:0>                             | : Timery Input            | Clock Prescale          | Select bits <sup>(2)</sup> |                 |                           |                       |

|                    | 11 <b>= 1:256</b>                      |                           |                         |                            |                 |                           |                       |

|                    | 10 = 1:64<br>01 = 1:8                  |                           |                         |                            |                 |                           |                       |

|                    | 01 = 1.8<br>00 = 1:1                   |                           |                         |                            |                 |                           |                       |

| bit 3-2            |                                        | ted: Read as '            | )'                      |                            |                 |                           |                       |

| bit 1              | -                                      | Clock Source S            |                         |                            |                 |                           |                       |

|                    | -                                      | clock from pin,           |                         | sing edge)                 |                 |                           |                       |

|                    | 0 = Internal c                         | lock (Fosc/2)             |                         |                            |                 |                           |                       |

| bit 0              | Unimplemen                             | ted: Read as '            | )'                      |                            |                 |                           |                       |

|                    | Changing the value reset and is not re | -                         | nile the timer is       | running (TON               | = 1) causes th  | e timer prescale          | counter to            |

|                    | When 32-bit oper operation; all time   |                           |                         |                            |                 | ts have no effect         | on Timery             |

|                    | If TCS = 1 and TI<br>available RPn/RF  |                           |                         |                            | • • • •         | •                         |                       |

NOTES:

## 16.0 SERIAL PERIPHERAL INTERFACE (SPI)

Note: This data sheet summarizes the features of the PIC24FJ128GA204 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "Serial Peripheral Interface (SPI) with Audio Codec Support" (DS70005136) which is available from the Microchip web site (www.microchip.com).

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D Converters, etc. The SPI module is compatible with the Motorola<sup>®</sup> SPI and SIOP interfaces. All devices in the PIC24FJ128GA204 family include three SPI modules.

The module supports operation in two buffer modes. In Standard Buffer mode, data is shifted through a single serial buffer. In Enhanced Buffer mode, data is shifted through a FIFO buffer. The FIFO level depends on the configured mode.

Variable length data can be transmitted and received, from 2 to 32-bits.

| Note: | Do not perform Read-Modify-Write opera-      |

|-------|----------------------------------------------|

|       | tions (such as bit-oriented instructions) on |

|       | the SPIxBUF register in either Standard or   |

|       | Enhanced Buffer mode.                        |

The module also supports a basic framed SPI protocol while operating in either Master or Slave mode. A total of four framed SPI configurations are supported.

The module also supports Audio modes. Four different Audio modes are available.

- I<sup>2</sup>S mode

- · Left Justified

- Right Justified

- PCM/DSP

In each of these modes, the serial clock is free-running and audio data is always transferred.

If an audio protocol data transfer takes place between two devices, then usually one device is the master and the other is the slave. However, audio data can be transferred between two slaves. Because the audio protocols require free-running clocks, the master can be a third party controller. In either case, the master generates two free-running clocks: SCKx and LRC (Left, Right Channel Clock/SSx/FSYNC). The SPI serial interface consists of four pins:

- SDIx: Serial Data Input

- SDOx: Serial Data Output

- SCKx: Shift Clock Input or Output

- SSx: Active-Low Slave Select or Frame Synchronization I/O Pulse

The SPI module can be configured to operate using 2, 3 or 4 pins. In the 3-pin mode,  $\overline{SSx}$  is not used. In the 2-pin mode, both SDOx and  $\overline{SSx}$  are not used.

The SPI module has the ability to generate three interrupts, reflecting the events that occur during the data communication. The following types of interrupts can be generated:

- 1. Receive interrupts are signalled by SPIxRXIF. This event occurs when:

- RX watermark interrupt

- SPIROV = 1

- SPIRBF = 1

- **SPIRBE =** 1

provided the respective mask bits are enabled in SPIxIMSKL/H.

- 2. Transmit interrupts are signalled by SPIxTXIF. This event occurs when:

- TX watermark interrupt

- SPITUR = 1

- SPITBF = 1

- SPITBE = 1

provided the respective mask bits are enabled in SPIxIMSKL/H.

- 3. General interrupts are signalled by SPIxIF. This event occurs when

- FRMERR = 1

- SPIBUSY = 1

- SRMT = 1

provided the respective mask bits are enabled in SPIxIMSKL/H.

Block diagrams of the module in Standard and Enhanced modes are shown in Figure 16-1 and Figure 16-2.

Note: In this section, the SPI modules are referred to together as SPIx, or separately as SPI1, SPI2 or SPI3. Special Function Registers will follow a similar notation. For example, SPIxCON1L and SPIxCON1H refer to the control registers for any of the three SPI modules.

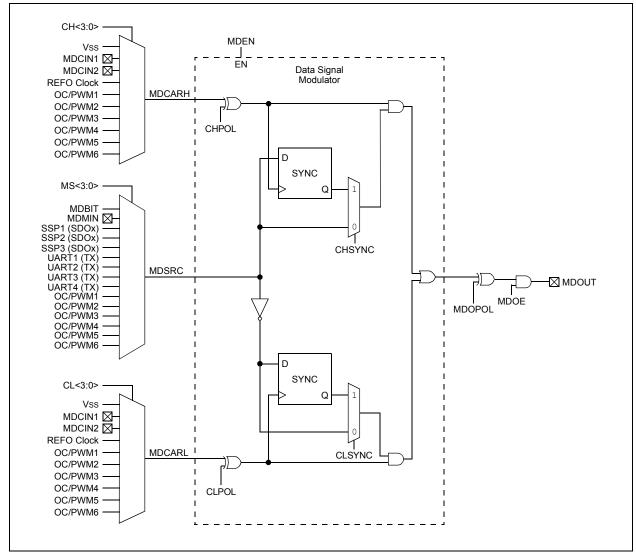

## 19.0 DATA SIGNAL MODULATOR (DSM)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Data Signal Modulator (DSM)" (DS39744). The information in this data sheet supersedes the information in the FRM.

The Data Signal Modulator (DSM) allows the user to mix a digital data stream (the "modulator signal") with a carrier signal to produce a modulated output. Both the carrier and the modulator signals are supplied to the DSM module, either internally from the output of a peripheral, or externally through an input pin. The modulated output signal is generated by performing a logical AND operation of both the carrier and modulator signals, and then it is provided to the MDOUT pin. Using this method, the DSM can generate the following types of key modulation schemes:

- Frequency Shift Keying (FSK)

- Phase-Shift Keying (PSK)

- On-Off Keying (OOK)

Figure 19-1 shows a simplified block diagram of the Data Signal Modulator peripheral.

### REGISTER 25-1: CMxCON: COMPARATOR x CONTROL REGISTERS (COMPARATORS 1 THROUGH 3)

| R/W-0                 | R/W-0                                       | R/W-0                                   | U-0               | U-0                          | U-0               | R/W-0, HS       | R-0, HSC      |  |  |  |

|-----------------------|---------------------------------------------|-----------------------------------------|-------------------|------------------------------|-------------------|-----------------|---------------|--|--|--|

| CON                   | COE                                         | CPOL                                    | —                 | —                            | —                 | CEVT            | COUT          |  |  |  |

| bit 15                |                                             |                                         |                   |                              |                   |                 | bit 8         |  |  |  |

|                       |                                             |                                         |                   |                              |                   |                 |               |  |  |  |

| R/W-0                 | R/W-0                                       | U-0                                     | R/W-0             | U-0                          | U-0               | R/W-0           | R/W-0         |  |  |  |

| EVPOL1 <sup>(1)</sup> | EVPOL0 <sup>(1)</sup>                       | <u> </u>                                | CREF              |                              | —                 | CCH1            | CCH0          |  |  |  |

| bit 7                 |                                             |                                         |                   |                              |                   |                 | bit (         |  |  |  |

|                       |                                             |                                         |                   |                              |                   |                 |               |  |  |  |

| Legend:               |                                             | HS = Hardware                           |                   |                              | vare Settable/0   |                 |               |  |  |  |

| R = Readable          |                                             | W = Writable b                          | it                | •                            | mented bit, rea   |                 |               |  |  |  |

| -n = Value at         | POR                                         | '1' = Bit is set                        |                   | '0' = Bit is cle             | ared              | x = Bit is unkr | nown          |  |  |  |

|                       |                                             |                                         |                   |                              |                   |                 |               |  |  |  |

| bit 15                | -                                           | rator Enable bit                        |                   |                              |                   |                 |               |  |  |  |

|                       | 1 = Comparat                                | tor is disabled                         |                   |                              |                   |                 |               |  |  |  |

| bit 14                | •                                           | rator Output En                         | able bit          |                              |                   |                 |               |  |  |  |

|                       |                                             | tor output is pres                      |                   | OUT pin                      |                   |                 |               |  |  |  |

|                       |                                             | tor output is inte                      |                   |                              |                   |                 |               |  |  |  |

| bit 13                | CPOL: Comparator Output Polarity Select bit |                                         |                   |                              |                   |                 |               |  |  |  |

|                       | 1 = Comparator output is inverted           |                                         |                   |                              |                   |                 |               |  |  |  |

|                       | 0 = Comparat                                | tor output is not                       | inverted          |                              |                   |                 |               |  |  |  |

| bit 12-10             | Unimplemen                                  | ted: Read as '0                         | 3                 |                              |                   |                 |               |  |  |  |

| bit 9                 | CEVT: Compa                                 | arator Event bit                        |                   |                              |                   |                 |               |  |  |  |

|                       | •                                           | tor event that is<br>bled until the bit | •                 | OL<1:0> has c                | occurred; subs    | equent triggers | and interrupt |  |  |  |

|                       | 0 = Compara                                 | ator event has no                       | ot occurred       |                              |                   |                 |               |  |  |  |

| bit 8                 | COUT: Comp                                  | arator Output bi                        | t                 |                              |                   |                 |               |  |  |  |

|                       | When CPOL                                   |                                         |                   |                              |                   |                 |               |  |  |  |

|                       | 1 = VIN+ > VII<br>0 = VIN+ < VII            |                                         |                   |                              |                   |                 |               |  |  |  |

|                       | When CPOL                                   |                                         |                   |                              |                   |                 |               |  |  |  |

|                       | 1 = VIN + < VII                             |                                         |                   |                              |                   |                 |               |  |  |  |

|                       | 0 = VIN+ > VII                              | N-                                      |                   |                              |                   |                 |               |  |  |  |

| bit 7-6               | EVPOL<1:0>                                  | : Trigger/Event/                        | Interrupt Polarit | y Select bits <sup>(1)</sup> |                   |                 |               |  |  |  |

|                       |                                             | event/interrupt is                      |                   |                              |                   |                 |               |  |  |  |

|                       |                                             | event/interrupt is                      |                   |                              |                   |                 |               |  |  |  |

|                       |                                             | event/interrupt is<br>event/interrupt g | •                 | •                            | i transition of t | ne comparator   | ουιρυι        |  |  |  |

| bit 5                 |                                             | ted: Read as '0                         |                   |                              |                   |                 |               |  |  |  |

| bit 4                 | -                                           | arator Referenc                         |                   | n-invertina inn              | ut)               |                 |               |  |  |  |

| ~                     |                                             | rting input conne                       | -                 |                              | -                 |                 |               |  |  |  |

|                       |                                             | rting input conne                       |                   |                              | <u> </u>          |                 |               |  |  |  |

| bit 3-2               | Unimplemen                                  | ted: Read as '0                         | 3                 |                              |                   |                 |               |  |  |  |

| Note de 161           | -                                           | )> hits are set to                      |                   | hen (00) the "               |                   |                 |               |  |  |  |

| MUTO 1' IT I          | UB EVPUI <11                                |                                         | a value otner t   | nan nn thá ti                |                   |                 |               |  |  |  |

**Note 1:** If the EVPOL<1:0> bits are set to a value other than '00', the first interrupt generated will occur on any transition of COUT. Subsequent interrupts will occur based on the EVPOLx bits setting.

## REGISTER 29-1: CW1: FLASH CONFIGURATION WORD 1

| U-1    | U-1 | U-1 | U-1 | U-1 | U-1 | U-1 | U-1    |

|--------|-----|-----|-----|-----|-----|-----|--------|

| —      | —   | —   | —   | —   | —   | —   | —      |

| bit 23 |     |     |     |     |     |     | bit 16 |

| r-x    | R/PO-1 |

|--------|--------|--------|--------|--------|--------|--------|--------|

| —      | JTAGEN | GCP    | GWRP   | DEBUG  | LPCFG  | ICS1   | ICS0   |

| bit 15 |        |        |        |        |        |        | bit 8  |

| R/PO-1      | R/PO-1  | R/PO-1 | R/PO-1 | R/PO-1 | R/PO-1 | R/PO-1 | R/PO-1 |

|-------------|---------|--------|--------|--------|--------|--------|--------|

| FWDTEN1     | FWDTEN0 | WINDIS | FWPSA  | WDTPS3 | WDTPS2 | WDTPS1 | WDTPS0 |

| bit 7 bit 0 |         |        |        |        |        |        |        |

| Legend:           | r = Reserved bit | PO = Program Once bit       |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 23-16 | Unimplemented: Read as '1'                                                                                                                                                                                                                                                                                         |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15    | Reserved: The value is unknown; program as '0'                                                                                                                                                                                                                                                                     |

| bit 14    | JTAGEN: JTAG Port Enable bit                                                                                                                                                                                                                                                                                       |

|           | <ul><li>1 = JTAG port is enabled</li><li>0 = JTAG port is disabled</li></ul>                                                                                                                                                                                                                                       |

| bit 13    | GCP: General Segment Program Memory Code Protection bit                                                                                                                                                                                                                                                            |

|           | <ul> <li>1 = Code protection is disabled</li> <li>0 = Code protection is enabled for the entire program memory space</li> </ul>                                                                                                                                                                                    |

| bit 12    | GWRP: General Segment Code Flash Write Protection bit                                                                                                                                                                                                                                                              |

|           | <ul><li>1 = Writes to program memory are allowed</li><li>0 = Writes to program memory are not allowed</li></ul>                                                                                                                                                                                                    |

| bit 11    | DEBUG: Background Debugger Enable bit                                                                                                                                                                                                                                                                              |

|           | <ul> <li>1 = Device resets into Operational mode</li> <li>0 = Device resets into Debug mode</li> </ul>                                                                                                                                                                                                             |

| bit 10    | LPCFG: Low-Voltage/Retention Regulator Configuration bit                                                                                                                                                                                                                                                           |

|           | <ul> <li>1 = Low-voltage/retention regulator is always disabled</li> <li>0 = Low-power, low-voltage/retention regulator is enabled and controlled in firmware by the RETEN bit</li> </ul>                                                                                                                          |

| bit 9-8   | ICS<1:0>: Emulator Pin Placement Select bits                                                                                                                                                                                                                                                                       |

|           | <ul> <li>11 = Emulator functions are shared with PGEC1/PGED1</li> <li>10 = Emulator functions are shared with PGEC2/PGED2</li> <li>01 = Emulator functions are shared with PGEC3/PGED3</li> <li>00 = Reserved; do not use</li> </ul>                                                                               |

| bit 7-6   | FWDTEN<1:0>: Watchdog Timer Configuration bits                                                                                                                                                                                                                                                                     |

|           | <ul> <li>11 = WDT is always enabled; the SWDTEN bit has no effect</li> <li>10 = WDT is enabled and controlled in firmware by the SWDTEN bit</li> <li>01 = WDT is enabled only in Run mode and disabled in Sleep modes; SWDTEN bit is disabled</li> <li>00 = WDT is disabled; the SWDTEN bit is disabled</li> </ul> |

| bit 5     | WINDIS: Windowed Watchdog Timer Disable bit                                                                                                                                                                                                                                                                        |

|           | <ul> <li>1 = Standard Watchdog Timer is enabled</li> <li>0 = Windowed Watchdog Timer is enabled (FWDTEN&lt;1:0&gt; must not be '00')</li> </ul>                                                                                                                                                                    |

| bit 4     | FWPSA: WDT Prescaler Ratio Select bit                                                                                                                                                                                                                                                                              |

|           | <ul> <li>1 = Prescaler ratio of 1:128</li> <li>0 = Prescaler ratio of 1:32</li> </ul>                                                                                                                                                                                                                              |

|           |                                                                                                                                                                                                                                                                                                                    |

| Assembly<br>Mnemonic | Assembly Syntax<br>GOTO Expr |                  | Description                                  | # of<br>Words | # of<br>Cycles<br>2 | Status Flags<br>Affected |

|----------------------|------------------------------|------------------|----------------------------------------------|---------------|---------------------|--------------------------|

| GOTO                 |                              |                  | Go to Address                                | 2             |                     | None                     |

|                      | GOTO                         | Wn               | Go to Indirect                               | 1             | 2                   | None                     |

| INC                  | INC                          | f                | f = f + 1                                    | 1             | 1                   | C, DC, N, OV, Z          |

|                      | INC                          | f,WREG           | WREG = f + 1                                 | 1             | 1                   | C, DC, N, OV, Z          |

|                      | INC                          | Ws,Wd            | Wd = Ws + 1                                  | 1             | 1                   | C, DC, N, OV, Z          |

| INC2                 | INC2                         | f                | f = f + 2                                    | 1             | 1                   | C, DC, N, OV, Z          |