Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

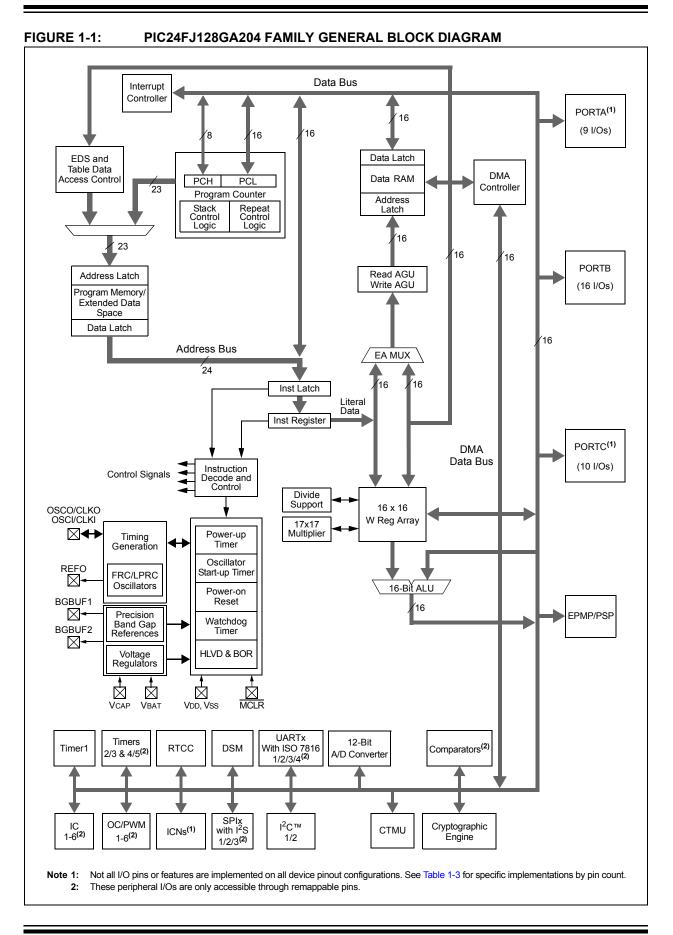

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP/PSP, SmartCard, SPI, UART/USART            |

| Peripherals                | AES, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, HLVD, POR, PWM, WDT        |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 13x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

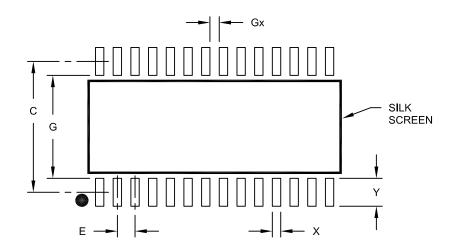

| Package / Case             | 44-TQFP                                                                        |

| Supplier Device Package    | 44-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128ga204-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# REGISTER 8-23: IPC2: INTERRUPT PRIORITY CONTROL REGISTER 2

| U-0           | R/W-1                                                                                                                        | R/W-0                                                                                                                          | R/W-0            | U-0              | R/W-1            | R/W-0           | R/W-0     |  |  |  |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|------------------|-----------------|-----------|--|--|--|--|--|

| _             | U1RXIP2                                                                                                                      | U1RXIP1                                                                                                                        | U1RXIP0          | _                | SPI1TXIP2        | SPI1TXIP1       | SPI1TXIP0 |  |  |  |  |  |

| bit 15        | •                                                                                                                            | •                                                                                                                              |                  |                  |                  | •               | bit       |  |  |  |  |  |

|               |                                                                                                                              |                                                                                                                                |                  |                  |                  |                 |           |  |  |  |  |  |

| U-0           | R/W-1                                                                                                                        | R/W-0                                                                                                                          | R/W-0            | U-0              | R/W-1            | R/W-0           | R/W-0     |  |  |  |  |  |

|               | SPI1IP2                                                                                                                      | SPI1IP1                                                                                                                        | SPI1IP0          | _                | T3IP2            | T3IP1           | T3IP0     |  |  |  |  |  |

| bit 7         |                                                                                                                              |                                                                                                                                |                  |                  |                  |                 | bit       |  |  |  |  |  |

| Legend:       |                                                                                                                              |                                                                                                                                |                  |                  |                  |                 |           |  |  |  |  |  |

| R = Readabl   | le hit                                                                                                                       | W = Writable                                                                                                                   | hit              | II = Unimplen    | nented bit, read | l as '0'        |           |  |  |  |  |  |

| -n = Value at |                                                                                                                              | '1' = Bit is set                                                                                                               | 5 N              | '0' = Bit is cle |                  | x = Bit is unkr | nown      |  |  |  |  |  |

|               |                                                                                                                              |                                                                                                                                |                  |                  |                  |                 |           |  |  |  |  |  |

| bit 15        | Unimplemen                                                                                                                   | ted: Read as '                                                                                                                 | )'               |                  |                  |                 |           |  |  |  |  |  |

| bit 14-12     | U1RXIP<2:0>                                                                                                                  | : UART1 Rece                                                                                                                   | iver Interrupt F | Priority bits    |                  |                 |           |  |  |  |  |  |

|               | 111 = Interru                                                                                                                | <b>U1RXIP&lt;2:0&gt;:</b> UART1 Receiver Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt) |                  |                  |                  |                 |           |  |  |  |  |  |

|               | •                                                                                                                            | •                                                                                                                              |                  |                  |                  |                 |           |  |  |  |  |  |

|               | •                                                                                                                            |                                                                                                                                |                  |                  |                  |                 |           |  |  |  |  |  |

|               | 001 = Interrupt is Priority 1                                                                                                |                                                                                                                                |                  |                  |                  |                 |           |  |  |  |  |  |

|               |                                                                                                                              | 000 = Interrupt source is disabled                                                                                             |                  |                  |                  |                 |           |  |  |  |  |  |

| bit 11        |                                                                                                                              | ted: Read as '                                                                                                                 |                  |                  |                  |                 |           |  |  |  |  |  |

| bit 10-8      | SPI1TXIP<2:0>: SPI1 Transmit Interrupt Priority bits                                                                         |                                                                                                                                |                  |                  |                  |                 |           |  |  |  |  |  |

|               | <ul> <li>111 = Interrupt is Priority 7 (highest priority interrupt)</li> </ul>                                               |                                                                                                                                |                  |                  |                  |                 |           |  |  |  |  |  |

|               | •                                                                                                                            |                                                                                                                                |                  |                  |                  |                 |           |  |  |  |  |  |

|               | •                                                                                                                            |                                                                                                                                |                  |                  |                  |                 |           |  |  |  |  |  |

|               | 001 = Interrupt is Priority 1<br>000 = Interrupt source is disabled                                                          |                                                                                                                                |                  |                  |                  |                 |           |  |  |  |  |  |

| bit 7         |                                                                                                                              | ted: Read as '                                                                                                                 |                  |                  |                  |                 |           |  |  |  |  |  |

| bit 6-4       | -                                                                                                                            |                                                                                                                                |                  | tv bits          |                  |                 |           |  |  |  |  |  |

|               | <b>SPI1IP&lt;2:0&gt;:</b> SPI1 General Interrupt Priority bits<br>111 = Interrupt is Priority 7 (highest priority interrupt) |                                                                                                                                |                  |                  |                  |                 |           |  |  |  |  |  |

|               | •                                                                                                                            |                                                                                                                                |                  |                  |                  |                 |           |  |  |  |  |  |

|               | •                                                                                                                            |                                                                                                                                |                  |                  |                  |                 |           |  |  |  |  |  |

|               | •<br>001 = Interrupt is Priority 1                                                                                           |                                                                                                                                |                  |                  |                  |                 |           |  |  |  |  |  |

|               |                                                                                                                              | pt source is dis                                                                                                               | abled            |                  |                  |                 |           |  |  |  |  |  |

| bit 3         | Unimplemen                                                                                                                   | ted: Read as '                                                                                                                 | )'               |                  |                  |                 |           |  |  |  |  |  |

| bit 2-0       | T3IP<2:0>: ⊤                                                                                                                 | imer3 Interrupt                                                                                                                | Priority bits    |                  |                  |                 |           |  |  |  |  |  |

|               | 111 = Interru                                                                                                                | 111 = Interrupt is Priority 7 (highest priority interrupt)                                                                     |                  |                  |                  |                 |           |  |  |  |  |  |

|               | •                                                                                                                            |                                                                                                                                |                  |                  |                  |                 |           |  |  |  |  |  |

|               | •                                                                                                                            |                                                                                                                                |                  |                  |                  |                 |           |  |  |  |  |  |

|               | 001 = Interru                                                                                                                |                                                                                                                                |                  |                  |                  |                 |           |  |  |  |  |  |

|               |                                                                                                                              | pt source is dis                                                                                                               | ablad            |                  |                  |                 |           |  |  |  |  |  |

| REGISTER                     | ( 0-24. IF 03.                                                                                                 |                                                                                                                                                                   |                                                                        | CONTROL RE       |                  |                 |         |

|------------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|------------------|------------------|-----------------|---------|

| U-0                          | U-0                                                                                                            | U-0                                                                                                                                                               | U-0                                                                    | U-0              | R/W-1            | R/W-0           | R/W-0   |

| _                            |                                                                                                                |                                                                                                                                                                   |                                                                        |                  | DMA1IP2          | DMA1IP1         | DMA1IP0 |

| bit 15                       |                                                                                                                |                                                                                                                                                                   |                                                                        |                  |                  |                 | bit     |

| U-0                          | R/W-1                                                                                                          | R/W-0                                                                                                                                                             | R/W-0                                                                  | U-0              | R/W-1            | R/W-0           | R/W-0   |

|                              | AD1IP2                                                                                                         | AD1IP1                                                                                                                                                            | AD1IP0                                                                 | _                | U1TXIP2          | U1TXIP1         | U1TXIP0 |

| bit 7                        |                                                                                                                |                                                                                                                                                                   | 1                                                                      |                  |                  |                 | bit     |

| Legend:                      |                                                                                                                |                                                                                                                                                                   |                                                                        |                  |                  |                 |         |

| R = Readab                   | ole bit                                                                                                        | W = Writable                                                                                                                                                      | bit                                                                    | U = Unimplen     | nented bit, read | d as '0'        |         |

| -n = Value a                 | at POR                                                                                                         | '1' = Bit is set                                                                                                                                                  |                                                                        | '0' = Bit is cle | ared             | x = Bit is unkr | iown    |

| bit 10-8<br>bit 7<br>bit 6-4 | 111 = Interru<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>AD1IP<2:0>:<br>111 = Interru<br>001 = Interru | >: DMA Chann<br>pt is Priority 7 (<br>pt is Priority 1<br>pt source is dis<br><b>ited:</b> Read as '<br>A/D Interrupt F<br>pt is Priority 7 (<br>pt is Priority 1 | (highest priority<br>abled<br>o'<br>Priority bits<br>(highest priority | / interrupt)     |                  |                 |         |

| bit 3<br>bit 2-0             | Unimplemen<br>U1TXIP<2:0><br>111 = Interru<br>•<br>•<br>001 = Interru                                          | <pre>ipt source is dis<br/>ited: Read as 'i<br/>&gt;: UART1 Trans<br/>ipt is Priority 7 (<br/>ipt is Priority 1<br/>ipt source is dis</pre>                       | <sub>0</sub> '<br>smitter Interrup<br>(highest priority                | •                |                  |                 |         |

# REGISTER 8-24: IPC3: INTERRUPT PRIORITY CONTROL REGISTER 3

# 8.4 Interrupt Setup Procedures

### 8.4.1 INITIALIZATION

To configure an interrupt source:

- 1. Set the NSTDIS (INTCON1<15>) control bit if nested interrupts are not desired.

- Select the user-assigned priority level for the interrupt source by writing the control bits in the appropriate IPCx register. The priority level will depend on the specific application and type of interrupt source. If multiple priority levels are not desired, the IPCx register control bits for all enabled interrupt sources may be programmed to the same non-zero value.

**Note:** At a device Reset, the IPCx registers are initialized, such that all user interrupt sources are assigned to Priority Level 4.

- 3. Clear the interrupt flag status bit associated with the peripheral in the associated IFSx register.

- 4. Enable the interrupt source by setting the interrupt enable control bit associated with the source in the appropriate IECx register.

### 8.4.2 INTERRUPT SERVICE ROUTINE (ISR)

The method that is used to declare an Interrupt Service Routine (ISR) and initialize the IVT with the correct vector address will depend on the programming language (i.e., 'C' or assembler), and the language development toolsuite that is used to develop the application. In general, the user must clear the interrupt flag in the appropriate IFSx register for the source of the interrupt that the ISR handles; otherwise, the ISR will be reentered immediately after exiting the routine. If the ISR is coded in assembly language, it must be terminated using a RETFIE instruction to unstack the saved PC value, SRL value and old CPU priority level.

# 8.4.3 TRAP SERVICE ROUTINE (TSR)

A Trap Service Routine (TSR) is coded like an ISR, except that the appropriate trap status flag in the INTCON1 register must be cleared to avoid re-entry into the TSR.

#### 8.4.4 INTERRUPT DISABLE

All user interrupts can be disabled using the following procedure:

- 1. Push the current SR value onto the software stack using the PUSH instruction.

- 2. Force the CPU to Priority Level 7 by inclusive ORing the value, 0Eh, with SRL.

To enable user interrupts, the POP instruction may be used to restore the previous SR value.

Note that only user interrupts with a priority level of 7 or less can be disabled. Trap sources (Levels 8-15) cannot be disabled.

The DISI instruction provides a convenient way to disable interrupts of Priority Levels 1-6 for a fixed period of time. Level 7 interrupt sources are not disabled by the DISI instruction.

If a MCLR Reset event occurs during Deep Sleep, the DSGPRx, DSCON and DSWAKE registers will remain valid, and the RELEASE bit will remain set. The state of the SOSC will also be retained. The I/O pins, however, will be reset to their MCLR Reset state. Since RELEASE is still set, changes to the SOSCEN bit (OSCCON<1>) cannot take effect until the RELEASE bit is cleared.

In all other Deep Sleep wake-up cases, application firmware must clear the RELEASE bit in order to reconfigure the I/O pins.

# 10.4.5 DEEP SLEEP WDT

To enable the DSWDT in Deep Sleep mode, program the Configuration bit, DSWDTEN (CW4<7>). The device WDT need not be enabled for the DSWDT to function. Entry into Deep Sleep modes automatically resets the DSWDT.

The DSWDT clock source is selected by the DSWDTOSC Configuration bit (CW4<5>). The postscaler options are programmed by the DSWDTPS<4:0> Configuration bits (CW4<4:0>). The minimum time-out period that can be achieved is 1 ms and the maximum is 25.7 days. For more information on the CW4 Configuration register and DSWDT configuration options, refer to **Section 29.0 "Special Features"**.

### 10.4.5.1 Switching Clocks in Deep Sleep Mode

Both the RTCC and the DSWDT may run from either SOSC or the LPRC clock source. This allows both the RTCC and DSWDT to run without requiring both the LPRC and SOSC to be enabled together, reducing power consumption.

Running the RTCC from LPRC will result in a loss of accuracy in the RTCC of approximately 5 to 10%. If a more accurate RTCC is required, it must be run from the SOSC clock source. The RTCC clock source is selected with the RTCLK<1:0> bits (RTCPWC<11:10>).

Under certain circumstances, it is possible for the DSWDT clock source to be off when entering Deep Sleep mode. In this case, the clock source is turned on automatically (if DSWDT is enabled), without the need for software intervention. However, this can cause a delay in the start of the DSWDT counters. In order to avoid this delay when using SOSC as a clock source, the application can activate SOSC prior to entering Deep Sleep mode.

# 10.4.6 CHECKING AND CLEARING THE STATUS OF DEEP SLEEP

Upon entry into Deep Sleep mode, the status bit, DPSLP (RCON<10>), becomes set and must be cleared by the software.

On power-up, the software should read this status bit to determine if the Reset was due to an exit from Deep Sleep mode and clear the bit if it is set. Of the four possible combinations of DPSLP and POR bit states, the following three cases can be considered:

- Both the DPSLP and POR bits are cleared. In this case, the Reset was due to some event other than a Deep Sleep mode exit.

- The DPSLP bit is clear, but the POR bit is set; this is a normal Power-on Reset.

- Both the DPSLP and POR bits are set. This means that Deep Sleep mode was entered, the device was powered down and Deep Sleep mode was exited.

# 10.4.7 POWER-ON RESETS (PORs)

VDD voltage is monitored to produce PORs. Since exiting from Deep Sleep mode functionally looks like a POR, the technique described in Section 10.4.6 "Checking and Clearing the Status of Deep Sleep" should be used to distinguish between Deep Sleep and a true POR event. When a true POR occurs, the entire device, including all Deep Sleep logic (Deep Sleep registers, RTCC, DSWDT, etc.) is reset.

# 10.5 VBAT Mode

This mode represents the lowest power state that the microcontroller can achieve and still resume operation. VBAT mode is automatically triggered when the micro-controller's main power supply on VDD fails. When this happens, the microcontroller's on-chip power switch connects to a backup power source, such as a battery, supplied to the VBAT pin. This maintains a few key systems at an extremely low-power draw until VDD is restored.

The power supplied on VBAT only runs two systems: the RTCC and the Deep Sleep Semaphore registers (DSGPR0 and DSGPR1). To maintain these systems during a sudden loss of VDD, it is essential to connect a power source, other than VDD or AVDD, to the VBAT pin.

When the RTCC is enabled, it continues to operate with the same clock source (SOSC or LPRC) that was selected prior to entering VBAT mode. There is no provision to switch to a lower power clock source after the mode switch.

Since the loss of VDD is usually an unforeseen event, it is recommended that the contents of the Deep Sleep Semaphore registers be loaded with the data to be retained at an early point in code execution.

### 10.5.1 VBAT MODE WITH NO RTCC

By disabling RTCC operation during VBAT mode, power consumption is reduced to the lowest of all powersaving modes. In this mode, only the Deep Sleep Semaphore registers are maintained.

| U-0                                | U-0 | R/W-1  | R/W-1  | R/W-1                                   | R/W-1  | R/W-1   | R/W-1  |

|------------------------------------|-----|--------|--------|-----------------------------------------|--------|---------|--------|

| —                                  |     | MDC2R5 | MDC2R4 | MDC2R3                                  | MDC2R2 | MDC2R1  | MDC2R0 |

| bit 15                             |     |        |        |                                         |        |         | bit 8  |

|                                    |     |        |        |                                         |        |         |        |

| U-0                                | U-0 | R/W-1  | R/W-1  | R/W-1                                   | R/W-1  | R/W-1   | R/W-1  |

| —                                  |     | MDC1R5 | MDC1R4 | MDC1R3                                  | MDC1R2 | MDC21R1 | MDC1R0 |

| bit 7                              |     |        |        |                                         |        |         | bit 0  |

|                                    |     |        |        |                                         |        |         |        |

| Legend:                            |     |        |        |                                         |        |         |        |

| R = Readable bit W = Writable bit  |     |        | oit    | U = Unimplemented bit, read as '0'      |        |         |        |

| -n = Value at POR (1' = Bit is set |     |        |        | '0' = Bit is cleared x = Bit is unknown |        |         |        |

### REGISTER 11-22: RPINR31: PERIPHERAL PIN SELECT INPUT REGISTER 31

bit 15-14 Unimplemented: Read as '0'

bit 13-8 MDC2R<5:0>: Assign TX Carrier 2 Input (MDCIN2) to Corresponding RPn or RPIn Pin bits

bit 7-6 Unimplemented: Read as '0'

bit 5-0 MDC1R<5:0>: Assign TX Carrier 1 Input (MDCIN1) to Corresponding RPn or RPIn Pin bits

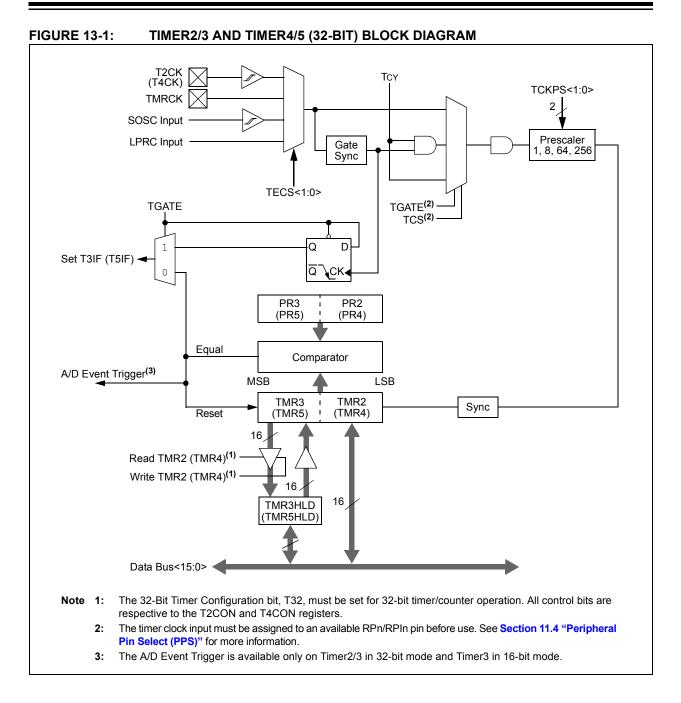

# 13.0 TIMER2/3 AND TIMER4/5

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the *"dsPIC33/PIC24 Family Reference Manual"*, **"Timers"** (DS39704). The information in this data sheet supersedes the information in the FRM.

The Timer2/3 and Timer4/5 modules are 32-bit timers, which can also be configured as four independent, 16-bit timers with selectable operating modes.

As 32-bit timers, Timer2/3 and Timer4/5 can each operate in three modes:

- Two Independent 16-Bit Timers with all 16-Bit Operating modes (except Asynchronous Counter mode)

- Single 32-Bit Timer

- Single 32-Bit Synchronous Counter

They also support these features:

- Timer Gate Operation

- Selectable Prescaler Settings

- Timer Operation during Idle and Sleep modes

- Interrupt on a 32-Bit Period Register Match

- A/D Event Trigger (only on Timer2/3 in 32-bit mode and Timer3 in 16-bit mode)

Individually, all four of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed above, except for the A/D Event Trigger. This trigger is implemented only on Timer2/3 in 32-bit mode and Timer3 in 16-bit mode. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON, T3CON, T4CON and T5CON registers. T2CON and T4CON are shown in generic form in Register 13-1; T3CON and T5CON are shown in Register 13-2.

For 32-bit timer/counter operation, Timer2 and Timer4 are the least significant word; Timer3 and Timer5 are the most significant word of the 32-bit timers.

Note: For 32-bit operation, T3CON and T5CON control bits are ignored. Only T2CON and T4CON control bits are used for setup and control. Timer2 and Timer4 clock and gate inputs are utilized for the 32-bit timer modules, but an interrupt is generated with the Timer3 or Timer5 interrupt flags. To configure Timer2/3 or Timer4/5 for 32-bit operation:

- 1. Set the T32 or T45 bit (T2CON<3> or T4CON<3> = 1).

- 2. Select the prescaler ratio for Timer2 or Timer4 using the TCKPS<1:0> bits.

- Set the Clock and Gating modes using the TCS and TGATE bits. If TCS is set to an external clock, RPINRx (TxCK) must be configured to an available RPn/RPIn pin. For more information, see Section 11.4 "Peripheral Pin Select (PPS)".

- 4. Load the timer period value. PR3 (or PR5) will contain the most significant word (msw) of the value, while PR2 (or PR4) contains the least significant word (lsw).

- 5. If interrupts are required, set the interrupt enable bit, T3IE or T5IE. Use the priority bits, T3IP<2:0> or T5IP<2:0>, to set the interrupt priority. Note that while Timer2 or Timer4 controls the timer, the interrupt appears as a Timer3 or Timer5 interrupt.

- 6. Set the TON bit (= 1).

The timer value, at any point, is stored in the register pair, TMR<3:2> (or TMR<5:4>). TMR3 (TMR5) always contains the most significant word of the count, while TMR2 (TMR4) contains the least significant word.

To configure any of the timers for individual 16-bit operation:

- Clear the T32 bit corresponding to that timer (T2CON<3> for Timer2 and Timer3 or T4CON<3> for Timer4 and Timer5).

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits. See Section 11.4 "Peripheral Pin Select (PPS)" for more information.

- 4. Load the timer period value into the PRx register.

- 5. If interrupts are required, set the interrupt enable bit, TxIE. Use the priority bits, TxIP<2:0>, to set the interrupt priority.

- 6. Set the TON (TxCON<15> = 1) bit.

# 17.0 INTER-INTEGRATED CIRCUIT™ (I<sup>2</sup>C™)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70000195). The information in this data sheet supersedes the information in the FRM.

The Inter-Integrated Circuit<sup>TM</sup> ( $I^2C^{TM}$ ) module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, display drivers, A/D Converters, etc.

The I<sup>2</sup>C module supports these features:

- Independent master and slave logic

- · 7-bit and 10-bit device addresses

- General call address as defined in the I<sup>2</sup>C protocol

- Clock stretching to provide delays for the processor to respond to a slave data request

- Both 100 kHz and 400 kHz bus specifications

- · Configurable address masking

- Multi-Master modes to prevent loss of messages in arbitration

- Bus Repeater mode, allowing the acceptance of all messages as a slave regardless of the address

- Automatic SCL

- A block diagram of the module is shown in Figure 17-1.

# 17.1 Communicating as a Master in a Single Master Environment

The details of sending a message in Master mode depends on the communication protocols for the device being communicated with. Typically, the sequence of events is as follows:

- 1. Assert a Start condition on SDAx and SCLx.

- 2. Send the I<sup>2</sup>C device address byte to the slave with a write indication.

- 3. Wait for and verify an Acknowledge from the slave.

- 4. Send the first data byte (sometimes known as the command) to the slave.

- 5. Wait for and verify an Acknowledge from the slave.

- 6. Send the serial memory address low byte to the slave.

- 7. Repeat Steps 4 and 5 until all data bytes are sent.

- 8. Assert a Repeated Start condition on SDAx and SCLx.

- 9. Send the device address byte to the slave with a read indication.

- 10. Wait for and verify an Acknowledge from the slave.

- 11. Enable master reception to receive serial memory data.

- 12. Generate an ACK or NACK condition at the end of a received byte of data.

- 13. Generate a Stop condition on SDAx and SCLx.

### REGISTER 20-9: PADCFG1: PAD CONFIGURATION CONTROL REGISTER

| U-0                               | U-0 | U-0 | U-0 | U-0          | U-0             | U-0    | U-0    |

|-----------------------------------|-----|-----|-----|--------------|-----------------|--------|--------|

| —                                 | —   | —   | —   | —            | —               | —      | —      |

| bit 15                            |     |     |     |              |                 |        | bit 8  |

|                                   |     |     |     |              |                 |        |        |

| U-0                               | U-0 | U-0 | U-0 | U-0          | U-0             | U-0    | R/W-0  |

| —                                 | —   | —   | —   | —            | —               | —      | PMPTTL |

| bit 7                             |     |     |     |              |                 |        | bit 0  |

|                                   |     |     |     |              |                 |        |        |

| Legend:                           |     |     |     |              |                 |        |        |

| R = Readable bit W = Writable bit |     |     | bit | U = Unimplem | ented bit, read | as '0' |        |

'0' = Bit is cleared

bit 15-1 Unimplemented: Read as '0'

-n = Value at POR

bit 0

PMPTTL: EPMP Module TTL Input Buffer Select bit

'1' = Bit is set

1 = EPMP module inputs (PMDx, PMCS1) use TTL input buffers

0 = EPMP module inputs use Schmitt Trigger input buffers

x = Bit is unknown

#### 21.3.2 RTCVAL REGISTER MAPPINGS

### **REGISTER 21-4:** YEAR: YEAR VALUE REGISTER<sup>(1)</sup>

| U-0    |

|--------|--------|--------|--------|--------|--------|--------|--------|

| —      | —      | —      | —      | —      | —      | —      | —      |

| bit 15 |        |        |        |        |        |        | bit 8  |

|        |        |        |        |        |        |        |        |

| R/W-x  |

| YRTEN3 | YRTEN2 | YRTEN2 | YRTEN1 | YRONE3 | YRONE2 | YRONE1 | YRONE0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 15-8 Unimplemented: Read as '0'

bit 7-4 **YRTEN<3:0>:** Binary Coded Decimal Value of Year's Tens Digit bits Contains a value from 0 to 9.

bit 3-0 **YRONE<3:0>:** Binary Coded Decimal Value of Year's Ones Digit bits Contains a value from 0 to 9.

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

### REGISTER 21-5: MTHDY: MONTH AND DAY VALUE REGISTER<sup>(1)</sup>

| U-0    | U-0 | U-0 | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   |

|--------|-----|-----|---------|---------|---------|---------|---------|

| —      | —   | —   | MTHTEN0 | MTHONE3 | MTHONE2 | MTHONE1 | MTHONE0 |

| bit 15 |     |     |         |         |         |         | bit 8   |

| U-0   | U-0 | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   | R/W-x   |

|-------|-----|---------|---------|---------|---------|---------|---------|

|       | —   | DAYTEN1 | DAYTEN0 | DAYONE3 | DAYONE2 | DAYONE1 | DAYONE0 |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-13 | Unimplemented: Read as '0'                                                                                    |

|-----------|---------------------------------------------------------------------------------------------------------------|

| bit 12    | <b>MTHTEN0:</b> Binary Coded Decimal Value of Month's Tens Digit bit Contains a value of '0' or '1'.          |

| bit 11-8  | <b>MTHONE&lt;3:0&gt;:</b> Binary Coded Decimal Value of Month's Ones Digit bits Contains a value from 0 to 9. |

| bit 7-6   | Unimplemented: Read as '0'                                                                                    |

| bit 5-4   | <b>DAYTEN&lt;1:0&gt;:</b> Binary Coded Decimal Value of Day's Tens Digit bits Contains a value from 0 to 3.   |

| bit 3-0   | <b>DAYONE&lt;3:0&gt;:</b> Binary Coded Decimal Value of Day's Ones Digit bits Contains a value from 0 to 9.   |

**Note 1:** A write to this register is only allowed when RTCWREN = 1.

# REGISTER 21-6: WKDYHR: WEEKDAY AND HOURS VALUE REGISTER<sup>(1)</sup>

| U-0          | U-0           | U-0              | U-0           | U-0                                    | R/W-x     | R/W-x  | R/W-x  |  |

|--------------|---------------|------------------|---------------|----------------------------------------|-----------|--------|--------|--|

| _            | —             | _                | _             | _                                      | WDAY2     | WDAY1  | WDAY0  |  |

| bit 15       |               |                  |               |                                        |           |        | bit 8  |  |

|              |               |                  |               |                                        |           |        |        |  |

| U-0          | U-0           | R/W-x            | R/W-x         | R/W-x                                  | R/W-x     | R/W-x  | R/W-x  |  |

| _            | —             | HRTEN1           | HRTEN0        | HRONE3                                 | HRONE2    | HRONE1 | HRONE0 |  |

| bit 7        |               |                  |               |                                        |           |        | bit 0  |  |

|              |               |                  |               |                                        |           |        |        |  |

| Legend:      |               |                  |               |                                        |           |        |        |  |

| R = Readab   | ole bit       | W = Writable     | bit           | U = Unimplemented bit, read as '0'     |           |        |        |  |

| -n = Value a | it POR        | '1' = Bit is set |               | '0' = Bit is cleared x = Bit is unknow |           |        | nown   |  |

|              |               |                  |               |                                        |           |        |        |  |

| bit 15-11    | Unimplemen    | ted: Read as '   | 0'            |                                        |           |        |        |  |

| bit 10-8     | WDAY<2:0>:    | Binary Coded     | Decimal Value | of Weekday Di                          | igit bits |        |        |  |

|              | Contains a va | alue from 0 to 6 |               |                                        |           |        |        |  |

|              |               |                  |               |                                        |           |        |        |  |

- bit 7-6Unimplemented: Read as '0'bit 5-4HRTEN<1:0>: Binary Coded Decimal Value of Hour's Tens Digit bits<br/>Contains a value from 0 to 2.

- bit 3-0 **HRONE<3:0>:** Binary Coded Decimal Value of Hour's Ones Digit bits Contains a value from 0 to 9.

- **Note 1:** A write to this register is only allowed when RTCWREN = 1.

### REGISTER 21-7: MINSEC: MINUTES AND SECONDS VALUE REGISTER

| U-0     | R/W-x   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| _       | MINTEN2 | MINTEN1 | MINTEN0 | MINONE3 | MINONE2 | MINONE1 | MINONE0 |

| bit 15  |         |         |         |         |         |         | bit 8   |

|         |         |         |         |         |         |         |         |

| U-0     | R/W-x   |

| _       | SECTEN2 | SECTEN1 | SECTEN0 | SECONE3 | SECONE2 | SECONE1 | SECONE0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend: |         |         |         |         |         |         |         |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | id as '0'          |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

|                   |                  |                            |                    |

| bit 15    | Unimplemented: Read as '0'                                          |

|-----------|---------------------------------------------------------------------|

| bit 14-12 | MINTEN<2:0>: Binary Coded Decimal Value of Minute's Tens Digit bits |

|           | Contains a value from 0 to 5.                                       |

| bit 11-8  | MINONE<3:0>: Binary Coded Decimal Value of Minute's Ones Digit bits |

|           | Contains a value from 0 to 9.                                       |

| bit 7     | Unimplemented: Read as '0'                                          |

| bit 6-4   | SECTEN<2:0>: Binary Coded Decimal Value of Second's Tens Digit bits |

|           | Contains a value from 0 to 5.                                       |

| bit 3-0   | SECONE<3:0>: Binary Coded Decimal Value of Second's Ones Digit bits |

|           | Contains a value from 0 to 9.                                       |

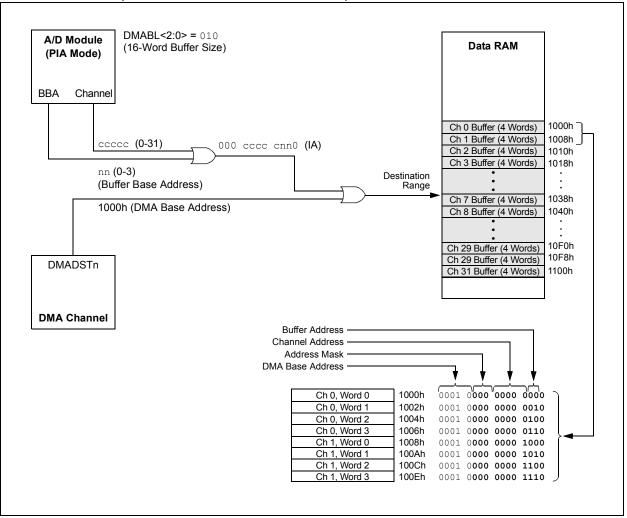

# FIGURE 24-2: EXAMPLE OF BUFFER ADDRESS GENERATION IN PIA MODE (4-WORD BUFFERS PER CHANNEL)

| R/W-0         | U-0                                                                                                                                                                                              | R/W-0            | R/W-0                          | R/W-0             | R/W-0           | R/W-0           | R/W-0      |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------|-------------------|-----------------|-----------------|------------|--|--|--|--|

| ADON          | —                                                                                                                                                                                                | ADSIDL           | DMABM <sup>(1)</sup>           | DMAEN             | MODE12          | FORM1           | FORM0      |  |  |  |  |

| bit 15        |                                                                                                                                                                                                  |                  |                                |                   |                 |                 | bit 8      |  |  |  |  |

|               |                                                                                                                                                                                                  | <b>D</b> 444 A   |                                |                   |                 |                 |            |  |  |  |  |

| R/W-0         | R/W-0                                                                                                                                                                                            | R/W-0            | R/W-0                          | U-0               | R/W-0           | R/W-0, HSC      | R/C-0, HSC |  |  |  |  |

| SSRC3         | SSRC2                                                                                                                                                                                            | SSRC1            | SSRC0                          |                   | ASAM            | SAMP            | DONE       |  |  |  |  |

| bit 7         |                                                                                                                                                                                                  |                  |                                |                   |                 |                 | bit (      |  |  |  |  |

| Legend:       |                                                                                                                                                                                                  | C = Clearable    | e bit                          | U = Unimplen      | nented bit, rea | d as 'O'        |            |  |  |  |  |

| R = Readable  | e bit                                                                                                                                                                                            | W = Writable     | bit                            | HSC = Hardw       | are Settable/C  | learable bit    |            |  |  |  |  |

| -n = Value at | POR                                                                                                                                                                                              | '1' = Bit is set | t                              | '0' = Bit is clea | ared            | x = Bit is unkn | own        |  |  |  |  |

|               |                                                                                                                                                                                                  |                  |                                |                   |                 |                 |            |  |  |  |  |

| bit 15        |                                                                                                                                                                                                  | Operating Mode   |                                |                   |                 |                 |            |  |  |  |  |

|               | 1 = A/D Conv<br>0 = A/D Conv                                                                                                                                                                     | verter module is | soperating                     |                   |                 |                 |            |  |  |  |  |

| bit 14        |                                                                                                                                                                                                  | nted: Read as '  | 0'                             |                   |                 |                 |            |  |  |  |  |

| bit 13        | -                                                                                                                                                                                                |                  |                                |                   |                 |                 |            |  |  |  |  |

|               | ADSIDL: A/D Stop in Idle Mode bit<br>1 = Discontinues module operation when device enters Idle mode                                                                                              |                  |                                |                   |                 |                 |            |  |  |  |  |

|               |                                                                                                                                                                                                  | -                | ation in Idle mod              |                   |                 |                 |            |  |  |  |  |

| bit 12        | DMABM: Extended DMA Buffer Mode Select bit <sup>(1)</sup>                                                                                                                                        |                  |                                |                   |                 |                 |            |  |  |  |  |

|               | <ul> <li>1 = Extended Buffer mode: Buffer address is defined by the DMADSTn register</li> <li>0 = PIA mode: Buffer addresses are defined by the DMA Controller and AD1CON4&lt;2:0&gt;</li> </ul> |                  |                                |                   |                 |                 |            |  |  |  |  |

| bit 11        |                                                                                                                                                                                                  |                  |                                |                   |                 | AD100N4-2.02    |            |  |  |  |  |

|               | <b>DMAEN:</b> Extended DMA/Buffer Enable bit<br>1 = Extended DMA and buffer features are enabled                                                                                                 |                  |                                |                   |                 |                 |            |  |  |  |  |

|               | 0 = Extended                                                                                                                                                                                     | d features are d | lisabled                       |                   |                 |                 |            |  |  |  |  |

| bit 10        | MODE12: 12                                                                                                                                                                                       | 2-Bit Operation  | Mode bit                       |                   |                 |                 |            |  |  |  |  |

|               | 1 = 12-bit A/D operation<br>0 = 10-bit A/D operation                                                                                                                                             |                  |                                |                   |                 |                 |            |  |  |  |  |

| bit 9-8       |                                                                                                                                                                                                  | •                | ormat hits (see                | formats follow    | ina)            |                 |            |  |  |  |  |

| DIL 9-0       | <b>FORM&lt;1:0&gt;:</b> Data Output Format bits (see formats following)<br>11 = Fractional result, signed, left justified                                                                        |                  |                                |                   |                 |                 |            |  |  |  |  |

|               | 10 = Absolute fractional result, unsigned, left justified                                                                                                                                        |                  |                                |                   |                 |                 |            |  |  |  |  |

|               | <ul> <li>01 = Decimal result, signed, right justified</li> <li>00 = Absolute decimal result, unsigned, right justified</li> </ul>                                                                |                  |                                |                   |                 |                 |            |  |  |  |  |

| hit 7 /       |                                                                                                                                                                                                  |                  |                                |                   |                 |                 |            |  |  |  |  |

| bit 7-4       |                                                                                                                                                                                                  |                  | Source Select I                | DITS              |                 |                 |            |  |  |  |  |

|               | 1xxx = Unimplemented, do not use<br>0111 = Internal counter ends sampling and starts conversion (auto-convert); do not use in Auto-Scan mode                                                     |                  |                                |                   |                 |                 |            |  |  |  |  |

|               | 0110 = Unimplemented                                                                                                                                                                             |                  |                                |                   |                 |                 |            |  |  |  |  |

|               | 0101 = TMR1                                                                                                                                                                                      |                  |                                |                   |                 |                 |            |  |  |  |  |

|               | 0100 = CTMU<br>0011 = TMR5                                                                                                                                                                       |                  |                                |                   |                 |                 |            |  |  |  |  |

|               | 0011 - TMRS<br>0010 = TMR3                                                                                                                                                                       |                  |                                |                   |                 |                 |            |  |  |  |  |

|               | 0001 = INTO                                                                                                                                                                                      |                  | he cleared by                  | offware to star   | taanvaraian     |                 |            |  |  |  |  |

| bit 3         |                                                                                                                                                                                                  | nted: Read as '  | be cleared by s                | soliware to star  | t conversion    |                 |            |  |  |  |  |

| bit 2         | -                                                                                                                                                                                                | Sample Auto-Si   |                                |                   |                 |                 |            |  |  |  |  |

|               |                                                                                                                                                                                                  | -                | lart bit<br>liately after last | conversion: SA    | AMP bit is auto | -set            |            |  |  |  |  |

|               |                                                                                                                                                                                                  |                  |                                |                   |                 |                 |            |  |  |  |  |

### REGISTER 24-1: AD1CON1: A/D CONTROL REGISTER 1

Note 1: This bit is only available when Extended DMA/Buffer features are available (DMAEN = 1).

| R/W-0                        | R-0                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W-0                                                       | R/W-0 | R/W-0             | R/W-0            | R/W-0              | R/W-0 |  |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|-------|-------------------|------------------|--------------------|-------|--|

| ADRC                         | EXTSAM                                                                                                                                                                                                                                                                                                                                                                                                              | PUMPEN                                                      | SAMC4 | SAMC3             | SAMC2            | SAMC1              | SAMC0 |  |

| bit 15                       |                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                             |       |                   |                  | •                  | bit 8 |  |

| R/W-0                        | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                               | R/W-0                                                       | R/W-0 | R/W-0             | R/W-0            | R/W-0              | R/W-0 |  |

| ADCS7                        | ADCS6                                                                                                                                                                                                                                                                                                                                                                                                               | ADCS5                                                       | ADCS4 | ADCS3             | ADCS2            | ADCS1              | ADCS0 |  |

| bit 7                        | I                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                             |       |                   |                  |                    | bit ( |  |

| Legend:                      |                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                             |       |                   |                  |                    |       |  |

| R = Readab                   | le bit                                                                                                                                                                                                                                                                                                                                                                                                              | W = Writable                                                | oit   | U = Unimplen      | nented bit, read | d as '0'           |       |  |

| -n = Value a                 | t POR                                                                                                                                                                                                                                                                                                                                                                                                               | '1' = Bit is set                                            |       | '0' = Bit is clea | ared             | x = Bit is unknown |       |  |

| bit 14<br>bit 13<br>bit 12-8 | <ul> <li>1 = RC clock</li> <li>0 = Clock derived from system clock</li> <li>EXTSAM: Extended Sampling Time bit</li> <li>1 = A/D is still sampling after SAMP = 0</li> <li>0 = A/D is finished sampling</li> <li>PUMPEN: Charge Pump Enable bit</li> <li>1 = Charge pump for switches is enabled</li> <li>0 = Charge pump for switches is disabled</li> <li>SAMC&lt;4:0&gt;: Auto-Sample Time Select bits</li> </ul> |                                                             |       |                   |                  |                    |       |  |

| bit 7-0                      |                                                                                                                                                                                                                                                                                                                                                                                                                     | ND<br>ND<br>A/D Conversio<br>256 • Tcy = Tat<br>2•Tcy = Tad |       | bits              |                  |                    |       |  |

# REGISTER 24-3: AD1CON3: A/D CONTROL REGISTER 3

| <b>TABLE 32-6</b> : | DC CHARACTERISTICS: POWER-DOWN CURRENT ( | (IPD) |

|---------------------|------------------------------------------|-------|

|---------------------|------------------------------------------|-------|

| DC CHARACTERISTICS |                        |                       | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                          |              |                                                |  |

|--------------------|------------------------|-----------------------|------------------------------------------------------|--------------------------|--------------|------------------------------------------------|--|

| Parameter<br>No.   | Typical <sup>(1)</sup> | Max                   | Units                                                | Operating<br>Temperature | VDD          | Conditions                                     |  |

| Power-Dow          | /n Current (           | IPD) <sup>(5,6)</sup> |                                                      |                          |              |                                                |  |

| DC60               | 2.9                    | 17                    | μA                                                   | -40°C                    |              |                                                |  |

|                    | 4.3                    | 17                    | μA                                                   | +25°C                    |              |                                                |  |

|                    | 8.3                    | 27.5                  | μA                                                   | +60°C                    | 2.0V         |                                                |  |

|                    | 20                     | 27.5                  | μA                                                   | +85°C                    |              |                                                |  |

|                    | _                      | 79                    | μA                                                   | +125°C                   |              | – Sleep <sup>(2)</sup>                         |  |

|                    | 2.9                    | 18                    | μA                                                   | -40°C                    |              |                                                |  |

|                    | 4.3                    | 18                    | μA                                                   | +25°C                    |              |                                                |  |

|                    | 8.4                    | 28                    | μA                                                   | +60°C                    | 3.3V         |                                                |  |

|                    | 20.5                   | 28                    | μA                                                   | +85°C                    |              |                                                |  |

|                    | _                      | 80                    | μA                                                   | +125°C                   |              |                                                |  |

| DC61               | 0.07                   | _                     | μA                                                   | -40°C                    | 2.0V<br>3.3V |                                                |  |

|                    | 0.38                   | _                     | μA                                                   | +25°C                    |              |                                                |  |

|                    | 2.6                    | _                     | μA                                                   | +60°C                    |              |                                                |  |

|                    | 9.0                    | _                     | μA                                                   | +125°C                   |              | – Low-Voltage Sleep <sup>(3)</sup>             |  |

|                    | 0.09                   | _                     | μA                                                   | -40°C                    |              |                                                |  |

|                    | 0.42                   | _                     | μA                                                   | +25°C                    |              |                                                |  |

|                    | 2.75                   | _                     | μA                                                   | +60°C                    |              |                                                |  |

|                    | 9.0                    | _                     | μA                                                   | +125°C                   |              |                                                |  |

| DC70               | 0.1                    | 700                   | nA                                                   | -40°C                    |              |                                                |  |

|                    | 18                     | 700                   | nA                                                   | +25°C                    |              |                                                |  |

|                    | 230                    | 1700                  | nA                                                   | +60°C                    | 2.0V         |                                                |  |

|                    | 1.8                    | 3.0                   | μA                                                   | +85°C                    |              |                                                |  |

|                    | _                      | 24                    | μA                                                   | +125°C                   |              | Doon Sloop                                     |  |

|                    | 5                      | 900                   | nA                                                   | -40°C                    | 3.3V         | – Deep Sleep                                   |  |

|                    | 75                     | 900                   | nA                                                   | +25°C                    |              |                                                |  |

|                    | 540                    | 3450                  | nA                                                   | +60°C                    |              |                                                |  |

|                    | 1.5                    | 6.0                   | μA                                                   | +85°C                    |              |                                                |  |

|                    | _                      | 48                    | μA                                                   | +125°C                   |              |                                                |  |

| DC74               | 0.4                    | 2.0                   | μA                                                   | -40°C to +125°C          | 0V           | RTCC with VBAT mode (LPRC/SOSC) <sup>(4)</sup> |  |

**Note 1:** Data in the Typical column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: The retention low-voltage regulator is disabled; RETEN (RCON<12>) = 0, LPCFG (CW1<10>) = 1.

**3:** The retention low-voltage regulator is enabled; RETEN (RCON<12>) = 1, <u>LPCFG</u> (CW1<10>) = 0.

4: The VBAT pin is connected to the battery and RTCC is running with VDD = 0.