Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP/PSP, SmartCard, SPI, UART/USART             |

| Peripherals                | AES, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, HLVD, POR, PWM, WDT         |

| Number of I/O              | 35                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                       |

| Data Converters            | A/D 13x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

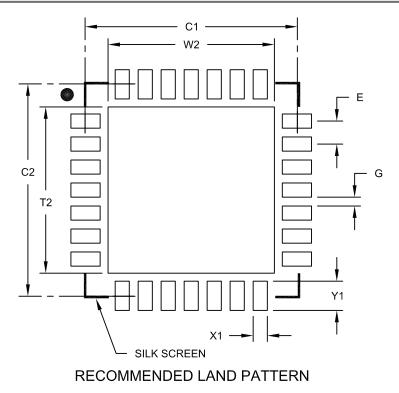

| Package / Case             | 44-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 44-QFN (8x8)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128ga204t-i-ml |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 4-10: UART REGISTER MAP

| IABLE 4        | -10: | UARIF    | KEGIS I |          |         |         |        |       |       |          |          |         |           |        |        |        |       | _             |

|----------------|------|----------|---------|----------|---------|---------|--------|-------|-------|----------|----------|---------|-----------|--------|--------|--------|-------|---------------|

| File<br>Name   | Addr | Bit 15   | Bit 14  | Bit 13   | Bit 12  | Bit 11  | Bit 10 | Bit 9 | Bit 8 | Bit 7    | Bit 6    | Bit 5   | Bit 4     | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

| U1MODE         | 0500 | UARTEN   | —       | USIDL    | IREN    | RTSMD   | —      | UEN1  | UEN0  | WAKE     | LPBACK   | ABAUD   | URXINV    | BRGH   | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U1STA          | 0502 | UTXISEL1 | UTXINV  | UTXISEL0 | URXEN   | UTXBRK  | UTXEN  | UTXBF | TRMT  | URXISEL1 | URXISEL0 | ADDEN   | RIDLE     | PERR   | FERR   | OERR   | URXDA | 0110          |

| U1TXREG        | 0504 | LAST     | _       | _        | _       | —       | _      | _     |       |          |          | U1T     | XREG<8:0> | •      |        |        |       | XXXX          |

| U1RXREG        | 0506 | _        | _       | _        |         | _       | _      |       |       |          |          | U1R     | XREG<8:0> | •      |        |        |       | 0000          |

| U1BRG          | 0508 |          |         |          |         |         |        |       | U1BRG | <15:0>   |          |         |           |        |        |        |       | 0000          |

| U1ADMD         | 050A |          |         |          | ADMMAS  | SK<7:0> |        |       |       |          |          |         | ADMADDR   | R<7:0> |        |        |       | 0000          |

| U1SCCON        | 050C | _        | _       | _        | _       | _       | _      | _     | _     | _        | _        | TXRPT1  | TXRPT0    | CONV   | T0PD   | PTRCL  | SCEN  | 0000          |

| U1SCINT        | 050E | _        | _       | RXRPTIF  | TXRPTIF | —       | _      | WTCIF | GTCIF | _        | PARIE    | RXRPTIE | TXRPTIE   | _      | _      | WTCIE  | GTCIE | 0000          |

| U1GTC          | 0510 | _        | _       | _        | _       | —       | _      | _     |       |          |          | G       | TC<8:0>   |        |        |        |       | 0000          |

| U1WTCL         | 0512 |          |         |          |         |         |        |       | WTC<  | 15:0>    |          |         |           |        |        |        |       | 0000          |

| U1WTCH         | 0514 | _        | _       | _        | _       | _       | _      | _     | _     |          |          |         | WTC<23    | :16>   |        |        |       | 0000          |

| U2MODE         | 0516 | UARTEN   | _       | USIDL    | IREN    | RTSMD   | _      | UEN1  | UEN0  | WAKE     | LPBACK   | ABAUD   | URXINV    | BRGH   | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U2STA          | 0518 | UTXISEL1 | UTXINV  | UTXISEL0 | URXEN   | UTXBRK  | UTXEN  | UTXBF | TRMT  | URXISEL1 | URXISEL0 | ADDEN   | RIDLE     | PERR   | FERR   | OERR   | URXDA | 0110          |

| U2TXREG        | 051A | LAST     | _       | _        | _       | —       | _      | _     |       |          |          | U2T     | XREG<8:0> | •      |        |        |       | XXXX          |

| U2RXREG        | 051C | _        | _       | _        | _       | —       | _      | _     |       |          |          | U2R     | XREG<8:0> | >      |        |        |       | 0000          |

| U2BRG          | 051E |          |         |          |         |         |        |       | U2BRG | <15:0>   |          |         |           |        |        |        |       | 0000          |

| U2ADMD         | 0520 |          |         |          | ADMMAS  | SK<7:0> |        |       |       |          |          |         | ADMADDR   | R<7:0> |        |        |       | 0000          |

| U2SCCON        | 0522 | —        | —       | —        | _       | _       |        | _     |       | —        | _        | TXRPT1  | TXRPT0    | CONV   | T0PD   | PTRCL  | SCEN  | 0000          |

| U2SCINT        | 0524 | —        | —       | RXRPTIF  | TXRPTIF | _       |        | WTCIF | GTCIF | —        | PARIE    | RXRPTIE | TXROTIE   |        | —      | WTCIE  | GTCIE | 0000          |

| U2GTC          | 0526 | —        | —       | —        | _       | _       |        | _     |       |          |          | G       | TC<8:0>   |        |        |        |       | 0000          |

| U2WTCL         | 0528 |          |         |          |         |         |        |       | WTC<  | 15:0>    |          |         |           |        |        |        |       | 0000          |

| U2WTCH         | 052A | —        | —       | —        | _       | _       |        | _     |       |          |          |         | WTC<23    | :16>   |        |        |       | 0000          |

| U3MODE         | 052C | UARTEN   | —       | USIDL    | IREN    | RTSMD   |        | UEN1  | UEN0  | WAKE     | LPBACK   | ABAUD   | URXINV    | BRGH   | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U3STA          | 052E | UTXISEL1 | UTXINV  | UTXISEL0 | URXEN   | UTXBRK  | UTXEN  | UTXBF | TRMT  | URXISEL1 | URXISEL0 | ADDEN   | RIDLE     | PERR   | FERR   | OERR   | URXDA | 0110          |

| U3TXREG        | 0530 | LAST     | —       | —        | _       | _       |        | _     |       |          |          | U3T2    | XREG<8:0> | •      |        |        |       | XXXX          |

| <b>U3RXREG</b> | 0532 | —        | —       | —        | _       | _       |        | _     |       |          |          | U3R     | XREG<8:0> | •      |        |        |       | 0000          |

| U3BRG          | 0534 |          |         |          |         |         |        |       | U3BRG | <15:0>   |          |         |           |        |        |        |       | 0000          |

| U3ADMD         | 0536 |          |         |          | ADMMAS  | SK<7:0> |        |       |       |          |          |         | ADMADDR   | 8<7:0> |        |        |       | 0000          |

| U4MODE         | 0538 | UARTEN   | —       | USIDL    | IREN    | RTSMD   | —      | UEN1  | UEN0  | WAKE     | LPBACK   | ABAUD   | URXINV    | BRGH   | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U4STA          | 053A | UTXISEL1 | UTXINV  | UTXISEL0 | URXEN   | UTXBRK  | UTXEN  | UTXBF | TRMT  | URXISEL1 | URXISEL0 | ADDEN   | RIDLE     | PERR   | FERR   | OERR   | URXDA | 0110          |

| U4TXREG        | 053C | LAST     | —       | —        | _       | —       | -      | _     |       |          |          | U4T     | XREG<8:0> | •      |        |        |       | XXXX          |

| U4RXREG        | 053E | _        | —       | —        | —       | —       | -      | _     |       |          |          | U4R     | XREG<8:0> | •      |        |        |       | 0000          |

| U4BRG          | 0540 |          |         |          |         |         |        |       | U4BRG | <15:0>   |          |         |           |        |        |        |       | 0000          |

| U4ADMD         | 0542 |          |         |          | ADMMAS  | SK<7:0> |        |       |       |          |          |         | ADMADDR   | R<7:0> |        |        |       | 0000          |

|                |      |          |         |          |         |         |        |       |       |          |          |         |           |        |        |        |       |               |

**Legend:** — = unimplemented, read as '0'; x = unknown value on Reset. Reset values are shown in hexadecimal.

### TABLE 4-11: SPI1 REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14    | Bit 13  | Bit 12                                                                                                                                                | Bit 11  | Bit 10 | Bit 9   | Bit 8    | Bit 7     | Bit 6       | Bit 5   | Bit 4  | Bit 3   | Bit 2       | Bit 1    | Bit 0    | All<br>Resets |

|--------------|------|--------|-----------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------|---------|----------|-----------|-------------|---------|--------|---------|-------------|----------|----------|---------------|

| SPI1CON1L    | 0300 | SPIEN  | —         | SPISIDL | DISSDO                                                                                                                                                | MODE32  | MODE16 | SMP     | CKE      | SSEN      | CKP         | MSTEN   | DISSDI | DISSCK  | MCLKEN      | SPIFE    | ENHBUF   | 0000          |

| SPI1CON1H    | 0302 | AUDEN  | SPISGNEXT | IGNROV  | IGNTUR                                                                                                                                                | AUDMONO | URDTEN | AUDMOD1 | AUDMOD0  | FRMEN     | FRMSYNC     | FRMPOL  | MSSEN  | FRMSYPW | FRMCNT2     | FRMCNT1  | FRMCNT0  | 0000          |

| SPI1CON2L    | 0304 | _      | _         | _       | _                                                                                                                                                     | _       | _      | _       | _        | _         | _           | _       |        | V       | VLENGTH<4:0 | >        |          | 0000          |

| SPI1STATL    | 0308 | _      | _         | -       | FRMERR                                                                                                                                                | SPIBUSY | _      | _       | SPITUR   | SRMT      | SPIROV      | SPIRBE  | _      | SPITBE  | _           | SPITBF   | SPIRBF   | 0028          |

| SPI1STATH    | 030A | _      | _         | RXELM5  | RXELM4         RXELM2         RXELM1         RXELM0         —         TXELM5         TXELM4         TXELM2         TXELM1         TXELM0         0000 |         |        |         |          |           |             |         |        |         |             |          |          |               |

| SPI1BUFL     | 030C |        |           |         |                                                                                                                                                       |         |        |         | SPI1BU   | FL<15:0>  |             |         |        |         |             |          |          | 0000          |

| SPI1BUFH     | 030E |        |           |         |                                                                                                                                                       |         |        |         | SPI1BUI  | =H<31:16> |             |         |        |         |             |          |          | 0000          |

| SPI1BRGL     | 0310 | _      | _         | _       |                                                                                                                                                       |         |        |         |          | SP        | 11BRG<12:0> |         |        |         |             |          |          | 0000          |

| SPI1IMSKL    | 0314 | _      | _         | _       | FRMERREN                                                                                                                                              | BUSYEN  | _      | _       | SPITUREN | SRMTEN    | SPIROVEN    | SPIRBEN | _      | SPITBEN | _           | SPITBFEN | SPIRBFEN | 0000          |

| SPI1IMSKH    | 0316 | RXWIEN | _         | RXMSK5  | RXMSK4                                                                                                                                                | RXMSK3  | RXMSK2 | RXMSK1  | RXMSK0   | TXWIEN    | _           | TXMSK5  | TXMSK4 | TXMSK3  | TXMSK2      | TXMSK1   | TXMSK0   | 0000          |

| SPI1URDTL    | 0318 |        |           |         |                                                                                                                                                       |         |        |         | SPI1URI  | DTL<15:0> |             |         |        |         |             |          |          | 0000          |

| SPI1URDTH    | 031A |        |           |         |                                                                                                                                                       |         |        |         | SPI1URD  | TH<31:16> |             |         |        |         |             |          |          | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-12: SPI2 REGISTER MAP

| File      | Addr | Bit 15 | Bit 14    | Bit 13  | Bit 12   | Bit 11              | Bit 10 | Bit 9   | Bit 8    | Bit 7      | Bit 6       | Bit 5   | Bit 4  | Bit 3   | Bit 2       | Bit 1    | Bit 0    | All    |

|-----------|------|--------|-----------|---------|----------|---------------------|--------|---------|----------|------------|-------------|---------|--------|---------|-------------|----------|----------|--------|

| Name      | Auui | Dit 10 | Dit 14    | Dit 10  | DICIZ    | DICH                | Dit IV | Dity    | Ditto    | Diti       | Diro        | Dito    | Dit 4  | Ditto   | Dit 2       | Dit i    | Ditt     | Resets |

| SPI2CON1L | 031C | SPIEN  | _         | SPISIDL | DISSDO   | MODE32              | MODE16 | SMP     | CKE      | SSEN       | CKP         | MSTEN   | DISSDI | DISSCK  | MCLKEN      | SPIFE    | ENHBUF   | 0000   |

| SPI2CON1H | 031E | AUDEN  | SPISGNEXT | IGNROV  | IGNTUR   | AUDMONO             | URDTEN | AUDMOD1 | AUDMOD0  | FRMEN      | FRMSYNC     | FRMPOL  | MSSEN  | FRMSYPW | FRMCNT2     | FRMCNT1  | FRMCNT0  | 0000   |

| SPI2CON2L | 0320 | _      | _         | _       | _        | _                   | _      | _       | _        | _          | _           | -       |        | ۷       | VLENGTH<4:0 | >        |          | 0000   |

| SPI2STATL | 0324 | _      | _         | _       | FRMERR   | SPIBUSY             | _      | _       | SPITUR   | SRMT       | SPIROV      | SPIRBE  | _      | SPITBE  | _           | SPITBF   | SPIRBF   | 0028   |

| SPI2STATH | 0326 | _      | _         | RXELM5  | RXELM4   | RXELM3              | RXELM2 | RXELM1  | RXELM0   | _          | _           | TXELM5  | TXELM4 | TXELM3  | TXELM2      | TXELM1   | TXELM0   | 0000   |

| SPI2BUFL  | 0328 |        |           |         |          | SPI2BUFL<15:0> 0000 |        |         |          |            |             |         |        |         |             |          |          |        |

| SPI2BUFH  | 032A |        |           |         |          |                     |        |         | SPI2BL   | IFH<31:16> |             |         |        |         |             |          |          | 0000   |

| SPI2BRGL  | 032C | _      | _         | _       |          |                     |        |         |          | S          | PI2BRG<12:0 | >       |        |         |             |          |          | 0000   |

| SPI2IMSKL | 0330 |        | _         | _       | FRMERREN | BUSYEN              | _      | _       | SPITUREN | SRMTEN     | SPIROVEN    | SPIRBEN | _      | SPITBEN | _           | SPITBFEN | SPIRBFEN | 0000   |

| SPI2IMSKH | 0332 | RXWIEN | _         | RXMSK5  | RXMSK4   | RXMSK3              | RXMSK2 | RXMSK1  | RXMSK0   | TXWIEN     | _           | TXMSK5  | TXMSK4 | TXMSK3  | TXMSK2      | TXMSK1   | TXMSK0   | 0000   |

| SPI2URDTL | 0334 |        |           |         |          |                     |        |         | SPI2UF   | RDTL<15:0> |             |         |        |         |             |          |          | 0000   |

| SPI2URDTH | 0336 |        |           |         |          |                     |        |         | SPI2UR   | DTH<31:16> |             |         |        |         |             |          |          | 0000   |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

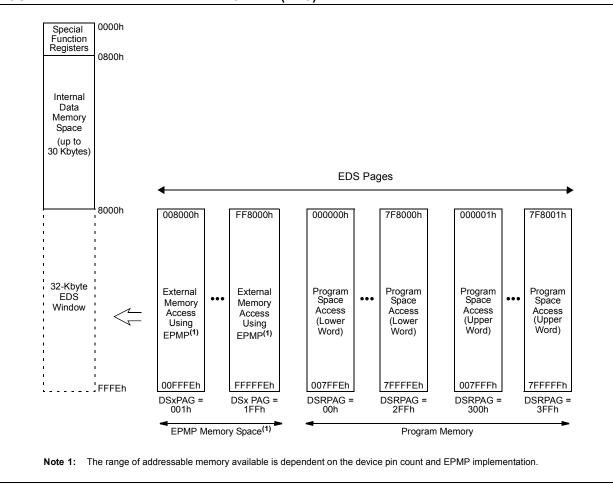

### 4.2.5 EXTENDED DATA SPACE (EDS)

The Extended Data Space (EDS) allows PIC24F devices to address a much larger range of data than would otherwise be possible with a 16-bit address range. EDS includes any additional internal data memory not directly accessible by the lower 32-Kbyte data address space and any external memory through the Enhanced Parallel Master Port (EPMP).

In addition, EDS also allows read access to the program memory space. This feature is called Program Space Visibility (PSV) and is discussed in detail in Section 4.3.3 "Reading Data from Program Memory Using EDS".

Figure 4-4 displays the entire EDS space. The EDS is organized as pages, called EDS pages, with one page equal to the size of the EDS window (32 Kbytes). A particular EDS page is selected through the Data Space Read register (DSRPAG) or Data Space Write register (DSWPAG). For PSV, only the DSRPAG register is used. The combination of the DSRPAG register value and the 16-bit wide data address forms a 24-bit Effective Address (EA). The data addressing range of PIC24FJ128GA204 family devices depends on the version of the Enhanced Parallel Master Port implemented on a particular device; this is, in turn, a function of device pin count. Table 4-33 lists the total memory accessible by each of the devices in this family. For more details on accessing external memory using EPMP, refer to the "*dsPIC33/PIC24 Family Reference Manual*", "Enhanced Parallel Master Port (EPMP)" (DS39730).

| TABLE 4-33: | TOTAL ACCESSIBLE DATA |

|-------------|-----------------------|

|             | MEMORY                |

| Family          | Internal<br>RAM | External RAM<br>Access Using<br>EPMP |

|-----------------|-----------------|--------------------------------------|

| PIC24FJXXXGA204 | 8K              | Up to 16 Mbytes                      |

| PIC24FJXXXGA202 | 8K              | Up to 64K                            |

Note: Accessing Page 0 in the EDS window will generate an address error trap as Page 0 is the base data memory (data locations, 0800h to 7FFFh, in the lower Data Space).

### FIGURE 4-4: EXTENDED DATA SPACE (EDS)

| TABLE 8-2:         IMPLEMENTED INTERRUPT VECTORS |

|--------------------------------------------------|

|--------------------------------------------------|

| Interrupt Source                     | Vector | IRQ | IVT     | ΑΙΥΤ    | Inte     | errupt Bit Locat | tions        |

|--------------------------------------|--------|-----|---------|---------|----------|------------------|--------------|

| Interrupt Source                     | #      | #   | Address | Address | Flag     | Enable           | Priority     |

| ADC1 Interrupt                       | 21     | 13  | 00002Eh | 00012Eh | IFS0<13> | IEC0<13>         | IPC3<6:4>    |

| Comparator Event                     | 26     | 18  | 000038h | 000138h | IFS1<2>  | IEC1<2>          | IPC4<10:8>   |

| CRC Generator                        | 75     | 67  | 00009Ah | 00019Ah | IFS4<3>  | IEC4<3>          | IPC16<14:12> |

| CTMU Event                           | 85     | 77  | 0000AEh | 0001AEh | IFS4<13> | IEC4<13>         | IPC19<6:4>   |

| Cryptographic Operation Done         | 63     | 55  | 000082h | 000182h | IFS3<7>  | IEC3<7>          | IPC13<14:12> |

| Cryptographic Key Store Program Done | 64     | 56  | 000084h | 000184h | IFS3<8>  | IEC3<8>          | IPC14<2:0>   |

| Cryptographic Buffer Ready           | 42     | 34  | 000058h | 000158h | IFS2<2>  | IEC2<2>          | IPC8<10:8>   |

| Cryptographic Rollover               | 43     | 35  | 00005Ah | 00015Ah | IFS2<3>  | IEC2<3>          | IPC8<14:12>  |

| DMA Channel 0                        | 12     | 4   | 00001Ch | 00011Ch | IFS0<4>  | IEC0<4>          | IPC1<2:0>    |

| DMA Channel 1                        | 22     | 14  | 000030h | 000130h | IFS0<14> | IEC0<14>         | IPC3<10:8>   |

| DMA Channel 2                        | 32     | 24  | 000044h | 000144h | IFS1<8>  | IEC1<8>          | IPC6<2:0>    |

| DMA Channel 3                        | 44     | 36  | 00005Ch | 00015Ch | IFS2<4>  | IEC2<4>          | IPC9<2:0>    |

| DMA Channel 4                        | 54     | 46  | 000070h | 000170h | IFS2<14> | IEC2<14>         | IPC11<10:8>  |

| DMA Channel 5                        | 69     | 61  | 00008Eh | 00018Eh | IFS3<13> | IEC3<13>         | IPC15<6:4>   |

| External Interrupt 0                 | 8      | 0   | 000014h | 000114h | IFS0<0>  | IEC0<0>          | IPC0<2:0>    |

| External Interrupt 1                 | 28     | 20  | 00003Ch | 00013Ch | IFS1<4>  | IEC1<4>          | IPC5<2:0>    |

| External Interrupt 2                 | 37     | 29  | 00004Eh | 00014Eh | IFS1<13> | IEC1<13>         | IPC7<6:4>    |

| External Interrupt 3                 | 61     | 53  | 00007Eh | 00017Eh | IFS3<5>  | IEC3<5>          | IPC13<6:4>   |

| External Interrupt 4                 | 62     | 54  | 000080h | 000180h | IFS3<6>  | IEC3<6>          | IPC13<10:8>  |

| FRC Self-Tune                        | 114    | 106 | 0000E8h | 0001E8h | IFS6<10> | IEC6<10>         | IPC26<10:8>  |

| I2C1 Master Event                    | 25     | 17  | 000036h | 000136h | IFS1<1>  | IEC1<1>          | IPC4<6:4>    |

| I2C1 Slave Event                     | 24     | 16  | 000034h | 000134h | IFS1<0>  | IEC1<0>          | IPC4<2:0>    |

| I2C1 Bus Collision                   | 92     | 84  | 0000BC  | 0001BC  | IFS5<4>  | IEC5<4>          | IPC21<2:0>   |

| I2C2 Master Event                    | 58     | 50  | 000078h | 000178h | IFS3<2>  | IEC3<2>          | IPC12<10:8>  |

| I2C2 Slave Event                     | 57     | 49  | 000076h | 000176h | IFS3<1>  | IEC3<1>          | IPC12<6:4>   |

| I2C2 Bus Collision.                  | 93     | 85  | 0000BE  | 0001BE  | IFS5<5>  | IEC5<5>          | IPC21<6:4>   |

| Input Capture 1                      | 9      | 1   | 000016h | 000116h | IFS0<1>  | IEC0<1>          | IPC0<6:4>    |

| Input Capture 2                      | 13     | 5   | 00001Eh | 00011Eh | IFS0<5>  | IEC0<5>          | IPC1<6:4>    |

| Input Capture 3                      | 45     | 37  | 00005Eh | 00015Eh | IFS2<5>  | IEC2<5>          | IPC9<6:4>    |

| Input Capture 4                      | 46     | 38  | 000060h | 000160h | IFS2<6>  | IEC2<6>          | IPC9<10:8>   |

| Input Capture 5                      | 47     | 39  | 000062h | 000162h | IFS2<7>  | IEC2<7>          | IPC9<14:12>  |

| Input Capture 6                      | 48     | 40  | 000064h | 000164h | IFS2<8>  | IEC2<8>          | IPC10<2:0>   |

| JTAG                                 | 125    | 117 | 0000FEh | 0001FEh | IFS7<5>  | IEC7<5>          | IPC29<6:4>   |

| Input Change Notification (ICN)      | 27     | 19  | 00003Ah | 00013Ah | IFS1<3>  | IEC1<3>          | IPC4<14:12>  |

| High/Low-Voltage Detect (HLVD)       | 80     | 72  | 0000A4h | 0001A4h | IFS4<8>  | IEC4<8>          | IPC18<2:0>   |

| Output Compare 1                     | 10     | 2   | 000018h | 000118h | IFS0<2>  | IEC0<2>          | IPC0<10:8>   |

| Output Compare 2                     | 14     | 6   | 000020h | 000120h | IFS0<6>  | IEC0<6>          | IPC1<10:8>   |

| Output Compare 3                     | 33     | 25  | 000046h | 000146h | IFS1<9>  | IEC1<9>          | IPC6<6:4>    |

| Output Compare 4                     | 34     | 26  | 000048h | 000148h | IFS1<10> | IEC1<10>         | IPC6<10:8>   |

| Output Compare 5                     | 49     | 41  | 000066h | 000166h | IFS2<9>  | IEC2<9>          | IPC10<6:4>   |

| Output Compare 6                     | 50     | 42  | 000068h | 000168h | IFS2<10> | IEC2<10>         | IPC10<10:8>  |

| Enhanced Parallel Master Port (EPMP) | 53     | 45  | 00006Eh | 00016Eh | IFS2<13> | IEC2<13>         | IPC11<6:4>   |

| Real-Time Clock and Calendar (RTCC)  | 70     | 62  | 000090h | 000190h | IFS3<14> | IEC3<14>         | IPC15<10:8>  |

### REGISTER 8-14: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1 (CONTINUED)

- bit 2 CMIE: Comparator Interrupt Enable bit

- 1 = Interrupt request is enabled

- 0 = Interrupt request is not enabled

- bit 1 MI2C1IE: Master I2C1 Event Interrupt Enable bit

- 1 = Interrupt request is enabled

- 0 = Interrupt request is not enabled

- bit 0 SI2C1IE: Slave I2C1 Event Interrupt Enable bit

- 1 = Interrupt request is enabled

- 0 = Interrupt request is not enabled

- Note 1: If an external interrupt is enabled, the interrupt input must also be configured to an available RPn or RPIn pin. For more information, see Section 11.4 "Peripheral Pin Select (PPS)".

### **REGISTER 10-1:** DSCON: DEEP SLEEP CONTROL REGISTER<sup>(1)</sup>

| R/W-0         | U-0          | U-0              | U-0                      | U-0              | U-0               | U-0                  | U-0       |

|---------------|--------------|------------------|--------------------------|------------------|-------------------|----------------------|-----------|

| DSEN          | —            | —                | —                        | —                | —                 | —                    | —         |

| bit 15        |              |                  |                          |                  |                   |                      | bit 8     |

|               |              |                  |                          |                  |                   |                      |           |

| U-0           | U-0          | U-0              | U-0                      | U-0              | r-0               | R/W-0                | R/C-0, HS |

|               |              | <u> </u>         |                          | <u> </u>         | <u> </u>          | DSBOR <sup>(2)</sup> | RELEASE   |

| bit 7         |              |                  |                          |                  |                   |                      | bit 0     |

|               |              |                  |                          |                  |                   |                      |           |

| Legend:       |              | C = Clearable    | bit                      | U = Unimplem     | nented bit, read  | as '0'               |           |

| R = Readabl   | le bit       | W = Writable     | bit                      | HS = Hardwa      | re Settable bit   | r = Reserved         | bit       |

| -n = Value at | t POR        | '1' = Bit is set |                          | '0' = Bit is cle | ared              | x = Bit is unkr      | nown      |

|               |              |                  |                          |                  |                   |                      |           |

| bit 15        | DSEN: Deep   | Sleep Enable b   | bit                      |                  |                   |                      |           |

|               |              | ep Sleep on ex   |                          |                  |                   |                      |           |

|               |              | rmal Sleep on    |                          | WRSAV #0         |                   |                      |           |

| bit 14-3      | •            | ted: Read as '   | כ'                       |                  |                   |                      |           |

| bit 2         | Reserved: Ma |                  |                          |                  |                   |                      |           |

| bit 1         | DSBOR: Dee   | p Sleep BOR E    | Event bit <sup>(2)</sup> |                  |                   |                      |           |

|               | 1 = The DSB0 | OR was active    | and a BOR eve            | ent was detecte  | ed during Deep    | Sleep                |           |

|               | 0 = The DSB0 | OR was not act   | ive, or was act          | ive, but did not | t detect a BOR    | event during D       | eep Sleep |

| bit 0         | RELEASE: 1/0 | O Pin State Re   | lease bit                |                  |                   |                      |           |

|               |              |                  |                          |                  | ir states previou |                      | · ·       |

|               |              | bits to control  |                          | ious io Deep S   | leep entry and    |                      |           |

- **Note 1:** All register bits are reset only in the case of a POR event outside of Deep Sleep mode.

- **2:** Unlike all other events, a Deep Sleep BOR event will NOT cause a wake-up from Deep Sleep; this re-arms the POR.

### 11.4.3.3 Mapping Limitations

The control schema of the Peripheral Pin Select is extremely flexible. Other than systematic blocks that prevent signal contention caused by two physical pins being configured as the same functional input or two functional outputs configured as the same pin, there are no hardware enforced lockouts. The flexibility extends to the point of allowing a single input to drive multiple peripherals or a single functional output to drive multiple output pins.

#### 11.4.3.4 Mapping Exceptions for PIC24FJ128GA204 Family Devices

Although the PPS registers theoretically allow for up to 24 remappable I/O pins, not all of these are implemented in all devices. For PIC24FJ128GA204 family devices, the maximum number of remappable pins available is 24, which includes one input only pin. The differences in available remappable pins are summarized in Table 11-5.

When developing applications that use remappable pins, users should also keep these things in mind:

- For the RPINRx registers, bit combinations corresponding to an unimplemented pin for a particular device are treated as invalid; the corresponding module will not have an input mapped to it.

- For RPORx registers, the bit fields corresponding to an unimplemented pin will also be unimplemented; writing to these fields will have no effect.

### 11.4.4 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. PIC24F devices include three features to prevent alterations to the peripheral map:

- Control register lock sequence

- Continuous state monitoring

- Configuration bit remapping lock

### 11.4.4.1 Control Register Lock

Under normal operation, writes to the RPINRx and RPORx registers are not allowed. Attempted writes will appear to execute normally, but the contents of the registers will remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK bit (OSCCON<6>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear IOLOCK, a specific command sequence must be executed:

- 1. Write 46h to OSCCON<7:0>.

- 2. Write 57h to OSCCON<7:0>.

- 3. Clear (or set) IOLOCK as a single operation.

Unlike the similar sequence with the oscillator's LOCK bit, IOLOCK remains in one state until changed. This allows all of the Peripheral Pin Selects to be configured with a single unlock sequence, followed by an update to all control registers, then locked with a second lock sequence.

### 11.4.4.2 Continuous State Monitoring

In addition to being protected from direct writes, the contents of the RPINRx and RPORx registers are constantly monitored in hardware by shadow registers. If an unexpected change in any of the registers occurs (such as cell disturbances caused by ESD or other external events), a Configuration Mismatch Reset will be triggered.

### 11.4.4.3 Configuration Bit Pin Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPINRx and RPORx registers. The IOL1WAY (CW4<15>) Configuration bit blocks the IOLOCK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure will not execute and the Peripheral Pin Select Control registers cannot be written to. The only way to clear the bit and re-enable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session. Programming IOL1WAY allows users unlimited access (with the proper use of the unlock sequence) to the Peripheral Pin Select registers.

### TABLE 11-5: REMAPPABLE PIN EXCEPTIONS FOR PIC24FJ128GA204 FAMILY DEVICES

| Device          |       | RPn Pins (I/O) |       | RPIn Pins     |

|-----------------|-------|----------------|-------|---------------|

| Device          | Total | Unimplemented  | Total | Unimplemented |

| PIC24FJXXXGA202 | 14    | RP4, RP12      | 1     | —             |

| PIC24FJXXXGA204 | 24    | RP4, RP12      | 1     | —             |

#### REGISTER 14-2: ICxCON2: INPUT CAPTURE x CONTROL REGISTER 2 (CONTINUED)

- bit 4-0 SYNCSEL<4:0>: Synchronization/Trigger Source Selection bits

- 1111x = Reserved

- 11101 = Reserved

- 11100 = CTMU<sup>(1)</sup>

- 11011 = A/D<sup>(1)</sup>

- $11010 = \text{Comparator 3}^{(1)}$

- 11001 = Comparator 2<sup>(1)</sup>

- 11000 = Comparator 1<sup>(1)</sup>

- 10111 = Reserved

- 10110 = Reserved

- 10101 = Input Capture  $6^{(2)}$

- 10100 = Input Capture 5<sup>(2)</sup> 10011 = Input Capture 4<sup>(2)</sup>

- $10011 = \text{Input Capture 4}^{(1)}$  $10010 = \text{Input Capture 3}^{(2)}$

- 10010 = Input Capture 3(\*)10001 = Input Capture 2(2)

- $10001 = \text{Input Capture 2}^{(7)}$  $10000 = \text{Input Capture 1}^{(2)}$

- 01111 = Timer5

- 01110 = Timer3

- 01101 = Timer3

- 01100 = Timer3

- 01011 = Timer1

- 01010 = **Reserved**

- 01001 = Reserved

- 01000 = Reserved

- 00111 = **Reserved**

- 00110 = Output Compare 6

- 00101 = Output Compare 5

- 00100 = Output Compare 4

- 00011 = Output Compare 3

- 00010 = Output Compare 2

- 00001 = Output Compare 1

- 00000 = Not synchronized to any other module

- Note 1: Use these inputs as trigger sources only and never as sync sources.

- 2: Never use an ICx module as its own trigger source by selecting this mode.

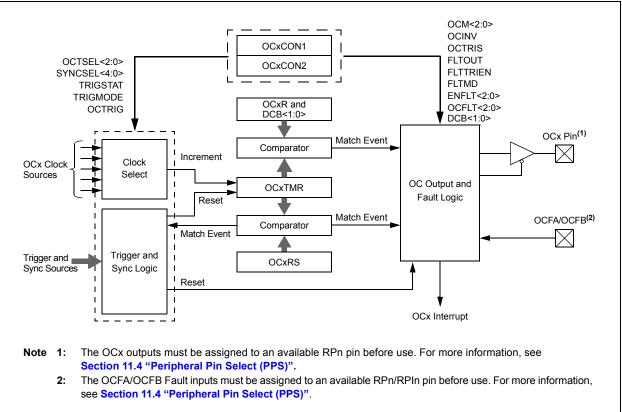

### FIGURE 15-1: OUTPUT COMPARE x BLOCK DIAGRAM (16-BIT MODE)

### 15.2 Compare Operations

In Compare mode (Figure 15-1), the output compare module can be configured for single-shot or continuous pulse generation. It can also repeatedly toggle an output pin on each timer event.

To set up the module for compare operations:

- 1. Configure the OCx output for one of the available Peripheral Pin Select pins.

- Calculate the required values for the OCxR and (for Double Compare modes) OCxRS Duty Cycle registers:

- a) Determine the instruction clock cycle time. Take into account the frequency of the external clock to the timer source (if one is used) and the timer prescaler settings.

- b) Calculate the time to the rising edge of the output pulse relative to the timer start value (0000h).

- c) Calculate the time to the falling edge of the pulse based on the desired pulse width and the time to the rising edge of the pulse.

- 3. Write the rising edge value to OCxR and the falling edge value to OCxRS.

- 4. Set the Timer Period register, PRy, to a value equal to or greater than the value in OCxRS.

- 5. Set the OCM<2:0> bits for the appropriate compare operation ('0xx').

- For Trigger mode operations, set OCTRIG to enable Trigger mode. Set or clear TRIGMODE to configure trigger operation and TRIGSTAT to select a hardware or software trigger. For Synchronous mode, clear OCTRIG.

- Set the SYNCSEL<4:0> bits to configure the trigger or synchronization source. If free-running timer operation is required, set the SYNCSELx bits to '00000' (no sync/trigger source).

- Select the time base source with the OCTSEL<2:0> bits. If necessary, set the TON bit for the selected timer, which enables the compare time base to count. Synchronous mode operation starts as soon as the time base is enabled; Trigger mode operation starts after a trigger source event occurs.

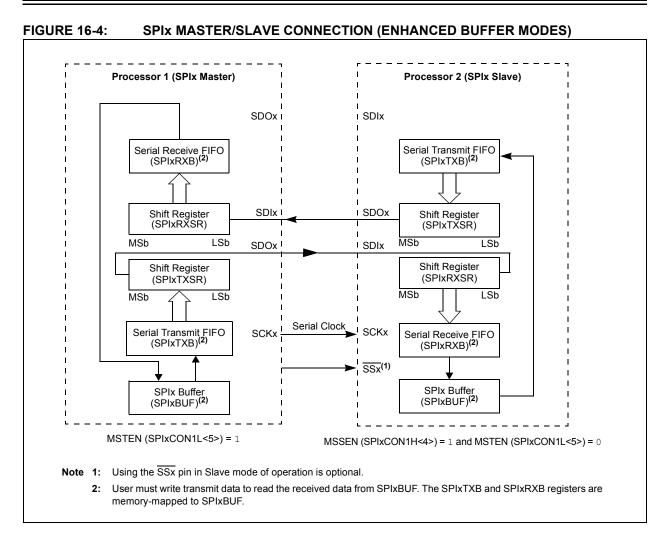

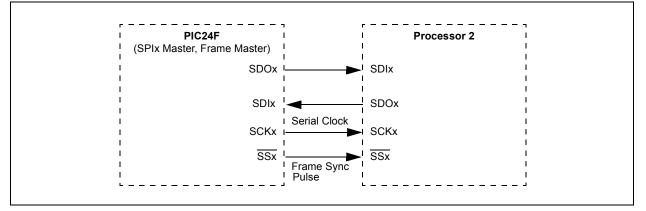

### FIGURE 16-5: SPIX MASTER, FRAME MASTER CONNECTION DIAGRAM

| R/W-0            | U-0                                       | R/W-0                                                                                                                                       | U-0                                                      | U-0              | U-0              | U-0            | U-0                  |  |  |  |

|------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------|------------------|----------------|----------------------|--|--|--|

| MDEN             |                                           | MDSIDL                                                                                                                                      |                                                          |                  | _                | _              | _                    |  |  |  |

| bit 15           |                                           |                                                                                                                                             |                                                          |                  |                  |                | bit 8                |  |  |  |

| U-0              | R/W-0                                     | R/W-1                                                                                                                                       | R/W-0                                                    | U-0              | U-0              | U-0            | R/W-0                |  |  |  |

| _                | MDOE                                      | MDSLR                                                                                                                                       | MDOPOL                                                   | _                | _                | _              | MDBIT <sup>(1)</sup> |  |  |  |

| bit 7            |                                           |                                                                                                                                             |                                                          |                  |                  |                | bit 0                |  |  |  |

| Legend:          |                                           |                                                                                                                                             |                                                          |                  |                  |                |                      |  |  |  |

| R = Readab       | le bit                                    | W = Writable                                                                                                                                | bit                                                      | U = Unimpler     | nented bit, read | d as '0'       |                      |  |  |  |

| -n = Value a     | It POR                                    | '1' = Bit is set                                                                                                                            | :                                                        | '0' = Bit is cle | ared             | x = Bit is unk | nown                 |  |  |  |

| bit 14<br>bit 13 | Unimplemen<br>MDSIDL: DS<br>1 = Discontin | <b>ted:</b> Read as '<br>M Stop in Idle I<br>ues module op                                                                                  | Mode bit<br>eration when d                               | evice enters Id  | lle mode         |                |                      |  |  |  |

| bit 12-7         |                                           | s module opera<br>i <b>ted:</b> Read as '                                                                                                   | ation in Idle mo                                         | ae               |                  |                |                      |  |  |  |

| bit 6            | <b>MDOE:</b> DSM<br>1 = Modulato          |                                                                                                                                             | utput Enable bit<br>enabled                              | t                |                  |                |                      |  |  |  |

| bit 5            | 1 = MDOUT p                               | oin slew rate lir                                                                                                                           | Rate Limiting b<br>niting is enable<br>niting is disable | d                |                  |                |                      |  |  |  |

| bit 4            | 1 = Modulato                              | SM Output Pola<br>r output signal<br>r output signal                                                                                        | is inverted                                              |                  |                  |                |                      |  |  |  |

| bit 3-1          | Unimplemen                                | ted: Read as '                                                                                                                              | 0'                                                       |                  |                  |                |                      |  |  |  |

| bit 0            | 1 = Carrier is                            | Unimplemented: Read as '0'<br>MDBIT: Manual Modulation Input bit <sup>(1)</sup><br>1 = Carrier is modulated<br>0 = Carrier is not modulated |                                                          |                  |                  |                |                      |  |  |  |

### **Note 1:** The MDBIT must be selected as the modulation source (MDSRC<3:0> = 0000).

### REGISTER 19-2: MDSRC: DATA SIGNAL MODULATOR SOURCE CONTROL REGISTER

| U-0                  | U-0                                                           | U-0                                      | U-0                       | U-0                | U-0                | U-0                | U-0                |  |  |  |  |  |

|----------------------|---------------------------------------------------------------|------------------------------------------|---------------------------|--------------------|--------------------|--------------------|--------------------|--|--|--|--|--|

| _                    | _                                                             |                                          |                           |                    | _                  | _                  |                    |  |  |  |  |  |

| bit 15               |                                                               | ·                                        |                           |                    |                    | ·                  | bit 8              |  |  |  |  |  |

| R/W-x                | U-0                                                           | U-0                                      | U-0                       | R/W-x              | R/W-x              | R/W-x              | R/W-x              |  |  |  |  |  |

| SODIS <sup>(1)</sup> | ) _                                                           | _                                        |                           | MS3 <sup>(2)</sup> | MS2 <sup>(2)</sup> | MS1 <sup>(2)</sup> | MS0 <sup>(2)</sup> |  |  |  |  |  |

| bit 7                | L                                                             |                                          |                           |                    |                    |                    | bit 0              |  |  |  |  |  |

| Legend:              |                                                               |                                          |                           |                    |                    |                    |                    |  |  |  |  |  |

| R = Reada            | ble bit                                                       | W = Writable                             | bit                       | U = Unimplen       | nented bit, rea    | d as '0'           |                    |  |  |  |  |  |

| -n = Value           | at POR                                                        | '1' = Bit is set                         |                           | '0' = Bit is clea  | ared               | x = Bit is unkr    | nown               |  |  |  |  |  |

| bit 6-4              | Unimpleme                                                     | nted: Read as '                          | )'                        | · · · ·            | ,                  | ,                  |                    |  |  |  |  |  |

| bit 15-8<br>bit 7    | -                                                             | nted: Read as '<br>M Source Output       |                           |                    |                    |                    |                    |  |  |  |  |  |

|                      |                                                               | signal driving the<br>signal driving the |                           |                    |                    |                    |                    |  |  |  |  |  |

| bit 6-4              | Unimpleme                                                     | nted: Read as 'o                         | )'                        |                    |                    |                    |                    |  |  |  |  |  |

| bit 3-0              |                                                               | SM Source Selec                          | ction bits <sup>(2)</sup> |                    |                    |                    |                    |  |  |  |  |  |

|                      | 1111 <b>= Unin</b>                                            |                                          |                           |                    |                    |                    |                    |  |  |  |  |  |

|                      |                                                               | 3 module output<br>out Compare/PW        |                           | utout              |                    |                    |                    |  |  |  |  |  |

|                      |                                                               | out Compare/PW                           |                           |                    |                    |                    |                    |  |  |  |  |  |

|                      |                                                               | out Compare/PW                           |                           |                    |                    |                    |                    |  |  |  |  |  |

|                      |                                                               | out Compare/PW                           |                           |                    |                    |                    |                    |  |  |  |  |  |

|                      |                                                               | out Compare/PW                           |                           |                    |                    |                    |                    |  |  |  |  |  |

|                      |                                                               | out Compare/PW                           | /M Module 1 o             | utput              |                    |                    |                    |  |  |  |  |  |

|                      |                                                               | RT4 TX output                            |                           |                    |                    |                    |                    |  |  |  |  |  |

|                      |                                                               | RT3 TX output                            |                           |                    |                    |                    |                    |  |  |  |  |  |

|                      |                                                               | RT2 TX output<br>RT1 TX output           |                           |                    |                    |                    |                    |  |  |  |  |  |

|                      |                                                               | 2 module output                          | (SD02)                    |                    |                    |                    |                    |  |  |  |  |  |

|                      |                                                               |                                          | · /                       |                    |                    |                    |                    |  |  |  |  |  |

|                      | 0010 = SPI1 module output (SDO1)<br>0001 = Input on MDMIN pin |                                          |                           |                    |                    |                    |                    |  |  |  |  |  |

|                      |                                                               |                                          | (0201)                    |                    |                    |                    |                    |  |  |  |  |  |

|                      | 0001 <b>= Inpu</b>                                            |                                          | . ,                       | MDCON<0>)          |                    |                    |                    |  |  |  |  |  |

| Note 1:              | 0001 = Inpu<br>0000 = Man                                     | t on MDMIN pin                           | ising MDBIT (I            | MDCON<0>)          |                    |                    |                    |  |  |  |  |  |

**2:** These bits are not affected by a POR.

### REGISTER 20-9: PADCFG1: PAD CONFIGURATION CONTROL REGISTER

| U-0                               | U-0 | U-0 | U-0 | U-0                                | U-0 | U-0 | U-0    |  |

|-----------------------------------|-----|-----|-----|------------------------------------|-----|-----|--------|--|

| _                                 | —   | _   | —   | —                                  | _   | —   |        |  |

| bit 15                            |     | ·   |     |                                    |     |     | bit 8  |  |

|                                   |     |     |     |                                    |     |     |        |  |

| U-0                               | U-0 | U-0 | U-0 | U-0                                | U-0 | U-0 | R/W-0  |  |

| —                                 | —   | —   | —   | —                                  |     | —   | PMPTTL |  |

| bit 7                             |     |     |     |                                    |     |     | bit 0  |  |

|                                   |     |     |     |                                    |     |     |        |  |

| Legend:                           |     |     |     |                                    |     |     |        |  |

| R = Readable bit W = Writable bit |     |     | bit | U = Unimplemented bit, read as '0' |     |     |        |  |

'0' = Bit is cleared

bit 15-1 Unimplemented: Read as '0'

-n = Value at POR

bit 0

PMPTTL: EPMP Module TTL Input Buffer Select bit

'1' = Bit is set

1 = EPMP module inputs (PMDx, PMCS1) use TTL input buffers

0 = EPMP module inputs use Schmitt Trigger input buffers

x = Bit is unknown

### 22.4.2 OPERATION DURING IDLE MODE

When the CRYSIDL bit (CRYCONL<13>) is '0', the engine will continue any ongoing operations without interruption when the device enters Idle mode.

When CRYSIDL is '1', the module behaves as in Sleep modes.

### 22.5 Specific Cryptographic Operations

This section provides the step-wise details for each operation type that is available with the Cryptographic Engine.

### 22.6 Encrypting Data

- 1. If not already set, set the CRYON bit.

- Configure the CPHRSEL, CPHRMODx, KEYMODx and KEYSRCx bits as desired to select the proper mode and key length.

- 3. Set OPMOD<3:0> to '0000'.

- If a software key is being used, write it to the CRYKEY register. It is only necessary to write the lowest *n* bits of CRYKEY for a key length of *n*, as all unused CRYKEY bits are ignored.

- 5. Read the KEYFAIL bit. If this bit is '1', an illegal configuration has been selected and the encrypt operation will NOT be performed.

- 6. Write the data to be encrypted to the appropriate CRYTXT register. For a single DES encrypt operation, it is only necessary to write the lowest 64 bits. However, for data less than the block size (64 bits for DES, 128 bits for AES), it is the responsibility of the software to properly pad the upper bits within the block.

- 7. Set the CRYGO bit.

- In ECB and CBC modes, set the FREEIE bit (CRYCONL<10>) to enable the optional CRYTXTA interrupt to indicate when the next plaintext block can be loaded.

- Poll the CRYGO bit until it is cleared or wait for the CRYDNIF module interrupt (DONEIE must be set). If other Cryptographic Engine interrupts are enabled, it will be necessary to poll the CRYGO bit to verify the interrupt source.

- 10. Read the encrypted block from the appropriate CRYTXT register.

- 11. Repeat Steps 5 through 8 to encrypt further blocks in the message with the same key.

### 22.7 Decrypting Data

- 1. If not already set, set the CRYON bit.

- Configure the CPHRSEL, CPHRMODx, KEYMODx and KEYSRCx bits as desired to select the proper mode and key length.

- 3. Set OPMOD<3:0> to '0001'.

- 4. If a software key is being used, write the CRYKEY register. It is only necessary to write the lowest *n* bits of CRYKEY for a key length of *n*, as all unused CRYKEY bits are ignored.

- 5. If an AES-ECB or AES-CBC mode decryption is being performed, you must first perform an AES decryption key expansion operation.

- 6. Read the KEYFAIL status bit. If this bit is '1', an illegal configuration has been selected and the encrypt operation will not be performed.

- Write the data to be decrypted into the appropriate text/data register. For a DES decrypt operation, it is only necessary to write the lowest 64 bits of CRYTXTB.

- 8. Set the CRYGO bit.

- 9. If this is the first decrypt operation after a Reset, or if a key storage program operation was performed after the last decrypt operation, or if the KEYMODx or KEYSRCx fields are changed, the engine will perform a new key expansion operation. This will result in extra clock cycles for the decrypt operation, but will otherwise be transparent to the application (i.e., the CRYGO bit will be cleared only after the key expansion and the decrypt operation have completed).

- In ECB and CBC modes, set the FREEIE bit (CRYCONL<10>) to enable the optional CRYTXTA interrupt to indicate when the next plaintext block can be loaded.

- 11. Poll the CRYGO bit until it is cleared or wait for the CRYDNIF module interrupt (DONEIE must be set). If other Cryptographic Engine interrupts are enabled, it will be necessary to poll the CRYGO bit to verify the interrupt source.

- 12. Read the decrypted block out of the appropriate text/data register.

- 13. Repeat Steps 6 through 10 to encrypt further blocks in the message with the same key.

### REGISTER 24-4: AD1CON4: A/D CONTROL REGISTER 4

| U-0     | U-0 | U-0 | U-0 | U-0 | U-0                       | U-0   | U-0   |  |  |  |

|---------|-----|-----|-----|-----|---------------------------|-------|-------|--|--|--|

| —       | —   | —   | —   | —   | —                         | —     | —     |  |  |  |

| bit 15  |     |     |     |     |                           |       | bit 8 |  |  |  |

|         |     |     |     |     |                           |       |       |  |  |  |

| U-0     | U-0 | U-0 | U-0 | U-0 | R/W-0                     | R/W-0 | R/W-0 |  |  |  |

| —       | _   | —   | —   | —   | DMABL<2:0> <sup>(1)</sup> |       |       |  |  |  |

| bit 7   |     |     |     |     |                           |       | bit 0 |  |  |  |

|         |     |     |     |     |                           |       |       |  |  |  |

| Legend: |     |     |     |     |                           |       |       |  |  |  |

| Legena:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-3 Unimplemented: Read as '0'

- bit 2-0 DMABL<2:0>: DMA Buffer Size Select bits<sup>(1)</sup>

- 111 = Allocates 128 words of buffer to each analog input

- 110 = Allocates 64 words of buffer to each analog input

- 101 = Allocates 32 words of buffer to each analog input

- 100 = Allocates 16 words of buffer to each analog input

- 011 = Allocates 8 words of buffer to each analog input

- 010 = Allocates 4 words of buffer to each analog input

- 001 = Allocates 2 words of buffer to each analog input

- 000 = Allocates 1 word of buffer to each analog input

- **Note 1:** The DMABL<2:0> bits are only used when AD1CON1<11> = 1 and AD1CON1<12> = 0; otherwise, their value is ignored.

| R/W-0         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0                                                                                                                                                                                                                                                                                        | R/W-0          | R/W-0                                | R/W-0            | R/W-0           | R/W-0  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------------------------|------------------|-----------------|--------|

| CH0NB2        | CH0NB1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CH0NB0                                                                                                                                                                                                                                                                                       | CH0SB4         | CH0SB3                               | CH0SB2           | CH0SB1          | CH0SB0 |

| bit 15        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                              |                |                                      |                  |                 | bit 8  |

| R/W-0         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0                                                                                                                                                                                                                                                                                        | R/W-0          | R/W-0                                | R/W-0            | R/W-0           | R/W-0  |

| CH0NA2        | CH0NA1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CHONAO                                                                                                                                                                                                                                                                                       | CH0SA4         | CH0SA3                               | CH0SA2           | CH0SA1          | CH0SA0 |

| bit 7         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                              |                |                                      |                  |                 | bit    |

| Legend:       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                              |                |                                      |                  |                 |        |

| R = Readabl   | le bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | W = Writable                                                                                                                                                                                                                                                                                 | oit            | U = Unimplen                         | nented bit, read | d as '0'        |        |

| -n = Value at | POR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | '1' = Bit is set                                                                                                                                                                                                                                                                             |                | '0' = Bit is clea                    |                  | x = Bit is unkr | nown   |

| bit 12-8      | 011 = Unimp<br>010 = AN1<br>001 = Unimp<br>000 = VREF-/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | lemented                                                                                                                                                                                                                                                                                     |                |                                      | h. 14-           |                 |        |

| bit 7-5       | 11111       VBA         11101       AVE         11101       AVE         11100       Bar         11011       VBC         01101       CTI         01101       CTI         01101       ANE         01011       ANE         01010       ANE         01001       ANE         01000       ANE         00111       ANE         00101       ANE         00101       ANE         00101       ANE         00101       ANE         00101       ANE         00011       ANE         00011       ANE         00011       ANE         000011       ANE         000011       ANE         000011       ANE         000011       ANE         000001       ANE         000001       ANE         000001       ANE | AT/2 <sup>(1)</sup><br>DD <sup>(1)</sup><br>DD <sup>(1)</sup><br>DD <sup>(1)</sup><br>DD <sup>(1)</sup><br>DD <sup>(1)</sup><br>AT/2 <sup>(1)</sup><br>MU<br>MU temperature<br>12 <sup>(2)</sup><br>11 <sup>(2)</sup><br>10 <sup>(2)</sup><br>9<br>8<br>7<br>6<br>5<br>4<br>3<br>2<br>1<br>0 | (VBG) referend | ce <sup>(1)</sup><br>(does not requi | re AD1CTMEN      | IL<12> to be se | et)    |

| UIL 7-3       | Same definiti                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Sample A Choose as for CHO                                                                                                                                                                                                                                                                   | NB<2:0>.       | ve Input Select                      |                  |                 |        |

| bit 4-0       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                              |                |                                      |                  |                 |        |

2: These channels are unimplemented in 28-pin devices.

| R/W-0                                                                   | R/W-0                                                                                                                                                                                                   | R/W-0            | R/W-0  | R/W-0             | R/W-0           | R/W-0              | R/W-0 |  |  |

|-------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------|-------------------|-----------------|--------------------|-------|--|--|

| ITRIM5                                                                  | ITRIM4                                                                                                                                                                                                  | ITRIM3           | ITRIM2 | ITRIM1            | ITRIM0          | IRNG1              | IRNG0 |  |  |

| bit 15                                                                  |                                                                                                                                                                                                         |                  |        |                   |                 |                    | bit 8 |  |  |