Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Decalls                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART                    |

| Peripherals                | AES, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, HLVD, POR, PWM, WDT       |

| Number of I/O              | 21                                                                            |

| Program Memory Size        | 64KB (64K x 8)                                                                |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                |                                                                               |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 10x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                |

| Supplier Device Package    | 28-SOIC                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64ga202-e-so |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.4 Voltage Regulator Pins (ENVREG/ DISVREG and VCAP/VDDCORE)

Note: This section applies only to PIC24FJ devices with an on-chip voltage regulator.

The on-chip voltage regulator enable/disable pin (ENVREG or DISVREG, depending on the device family) must always be connected directly to either a supply voltage or to ground. The particular connection is determined by whether or not the regulator is to be used:

- For ENVREG, tie to VDD to enable the regulator, or to ground to disable the regulator

- For DISVREG, tie to ground to enable the regulator or to VDD to disable the regulator

Refer to **Section 29.2 "On-Chip Voltage Regulator"** for details on connecting and using the on-chip regulator.

When the regulator is enabled, a low-ESR (< 5 $\Omega$ ) capacitor is required on the VCAP/VDDCORE pin to stabilize the voltage regulator output voltage. The VCAP/VDDCORE pin must not be connected to VDD and must use a capacitor of 10  $\mu$ F connected to ground. The type can be ceramic or tantalum. Suitable examples of capacitors are shown in Table 2-1. Capacitors with equivalent specifications can be used.

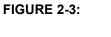

Designers may use Figure 2-3 to evaluate ESR equivalence of candidate devices.

The placement of this capacitor should be close to VCAP/VDDCORE. It is recommended that the trace length not exceed 0.25 inch (6 mm). Refer to **Section 32.0** "Electrical Characteristics" for additional information.

When the regulator is disabled, the VCAP/VDDCORE pin must be tied to a voltage supply at the VDDCORE level. Refer to Section 32.0 "Electrical Characteristics" for information on VDD and VDDCORE.

#### FREQUENCY vs. ESR PERFORMANCE FOR SUGGESTED VCAP

| Make      | Part # Nominal Capacitance Base Tolerance |       | Rated Voltage | Temp. Range |               |

|-----------|-------------------------------------------|-------|---------------|-------------|---------------|

| TDK       | C3216X7R1C106K                            | 10 µF | ±10%          | 16V         | -55 to +125°C |

| TDK       | C3216X5R1C106K                            | 10 µF | ±10%          | 16V         | -55 to +85°C  |

| Panasonic | ECJ-3YX1C106K                             | 10 µF | ±10%          | 16V         | -55 to +125°C |

| Panasonic | ECJ-4YB1C106K                             | 10 µF | ±10%          | 16V         | -55 to +85°C  |

| Murata    | GRM32DR71C106KA01L                        | 10 µF | ±10%          | 16V         | -55 to +125°C |

| Murata    | GRM31CR61C106KC31L                        | 10 µF | ±10%          | 16V         | -55 to +85°C  |

### TABLE 2-1: SUITABLE CAPACITOR EQUIVALENTS

| Reset Type      | Clock Source | SYSRST Delay           | System Clock<br>Delay | Notes         |

|-----------------|--------------|------------------------|-----------------------|---------------|

| POR             | EC           | TPOR + TSTARTUP + TRST |                       | 1, 2, 3       |

|                 | ECPLL        | TPOR + TSTARTUP + TRST | Тьоск                 | 1, 2, 3, 5    |

|                 | XT, HS, SOSC | TPOR + TSTARTUP + TRST | Тоѕт                  | 1, 2, 3, 4    |

|                 | XTPLL, HSPLL | TPOR + TSTARTUP + TRST | Tost + Tlock          | 1, 2, 3, 4, 5 |

|                 | FRC, FRCDIV  | TPOR + TSTARTUP + TRST | TFRC                  | 1, 2, 3, 6, 7 |

|                 | FRCPLL       | TPOR + TSTARTUP + TRST | TFRC + TLOCK          | 1, 2, 3, 5, 6 |

|                 | LPRC         | TPOR + TSTARTUP + TRST | TLPRC                 | 1, 2, 3, 6    |

| BOR             | EC           | TSTARTUP + TRST        | —                     | 2, 3          |

|                 | ECPLL        | TSTARTUP + TRST        | TLOCK                 | 2, 3, 5       |

|                 | XT, HS, SOSC | TSTARTUP + TRST        | Тоѕт                  | 2, 3, 4       |

|                 | XTPLL, HSPLL | TSTARTUP + TRST        | Tost + Tlock          | 2, 3, 4, 5    |

|                 | FRC, FRCDIV  | TSTARTUP + TRST        | TFRC                  | 2, 3, 6, 7    |

|                 | FRCPLL       | TSTARTUP + TRST        | TFRC + TLOCK          | 2, 3, 5, 6    |

|                 | LPRC         | TSTARTUP + TRST        | Tlprc                 | 2, 3, 6       |

| MCLR            | Any Clock    | Trst                   |                       | 3             |

| WDT             | Any Clock    | Trst                   | —                     | 3             |

| Software        | Any clock    | Trst                   | _                     | 3             |

| Illegal Opcode  | Any Clock    | Trst                   | _                     | 3             |

| Uninitialized W | Any Clock    | Trst                   | —                     | 3             |

| Trap Conflict   | Any Clock    | Trst                   | _                     | 3             |

**Note 1:** TPOR = Power-on Reset Delay (10  $\mu$ s nominal).

- 2: TSTARTUP = TVREG.

- 3: TRST = Internal State Reset Time (2 µs nominal).

- **4:** TOST = Oscillator Start-up Timer (OST). A 10-bit counter counts 1024 oscillator periods before releasing the oscillator clock to the system.

- **5:** TLOCK = PLL Lock Time.

- 6: TFRC and TLPRC = RC Oscillator Start-up Times.

- 7: If Two-Speed Start-up is enabled, regardless of the Primary Oscillator selected, the device starts with FRC so the system clock delay is just TFRC, and in such cases, FRC start-up time is valid; it switches to the Primary Oscillator after its respective clock delay.

#### 7.4.1 POR AND LONG OSCILLATOR START-UP TIMES

The oscillator start-up circuitry and its associated delay timers are not linked to the device Reset delays that occur at power-up. Some crystal circuits (especially low-frequency crystals) will have a relatively long start-up time. Therefore, one or more of the following conditions is possible after SYSRST is released:

- The oscillator circuit has not begun to oscillate.

- The Oscillator Start-up Timer has not expired (if a crystal oscillator is used).

- The PLL has not achieved a lock (if PLL is used).

The device will not begin to execute code until a valid clock source has been released to the system. Therefore, the oscillator and PLL start-up delays must be considered when the Reset delay time must be known.

#### 7.4.2 FAIL-SAFE CLOCK MONITOR (FSCM) AND DEVICE RESETS

If the FSCM is enabled, it will begin to monitor the system clock source when SYSRST is released. If a valid clock source is not available at this time, the device will automatically switch to the FRC Oscillator and the user can switch to the desired crystal oscillator in the Trap Service Routine (TSR).

## 8.0 INTERRUPT CONTROLLER

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Interrupts" (DS70000600). The information in this data sheet supersedes the information in the FRM.

The PIC24F interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the PIC24F CPU. It has the following features:

- · Up to 8 processor exceptions and software traps

- Seven user-selectable priority levels

- Interrupt Vector Table (IVT) with up to 118 vectors

- Unique vector for each interrupt or exception source

- · Fixed priority within a specified user priority level

- Alternate Interrupt Vector Table (AIVT) for debug support

- Fixed interrupt entry and return latencies

### 8.1 Interrupt Vector Table

The Interrupt Vector Table (IVT) is shown in Figure 8-1. The IVT resides in program memory, starting at location, 000004h. The IVT contains 126 vectors, consisting of 8 non-maskable trap vectors, plus up to 118 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority; this is linked to their position in the vector table. All other things being equal, lower addresses have a higher natural priority. For example, the interrupt associated with Vector 0 will take priority over interrupts at any other vector address.

PIC24FJ128GA204 family devices implement nonmaskable traps and unique interrupts. These are summarized in Table 8-1 and Table 8-2.

#### 8.1.1 ALTERNATE INTERRUPT VECTOR TABLE

The Alternate Interrupt Vector Table (AIVT) is located after the IVT, as shown in Figure 8-1. The ALTIVT (INTCON2<15>) control bit provides access to the AIVT. If the ALTIVT bit is set, all interrupt and exception processes will use the alternate vectors instead of the default vectors. The alternate vectors are organized in the same manner as the default vectors.

The AIVT supports emulation and debugging efforts by providing a means to switch between an application and a support environment without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications for evaluation of different software algorithms at run time. If the AIVT is not needed, the AIVT should be programmed with the same addresses used in the IVT.

### 8.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The PIC24F devices clear their registers in response to a Reset, which forces the PC to zero. The micro-controller then begins program execution at location, 000000h. The user programs a GOTO instruction at the Reset address, which redirects program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT and AIVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

| R/W-0                   | R/W-0                                                                                          | R/W-0                                                                                      | R/W-0                 | R/W-0             | R/W-0          | R/W-0           | R/W-0   |  |  |  |  |

|-------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------|-------------------|----------------|-----------------|---------|--|--|--|--|

| U2TXIE                  | U2RXIE                                                                                         | INT2IE <sup>(1)</sup>                                                                      | T5IE                  | T4IE              | OC4IE          | OC3IE           | DMA2IE  |  |  |  |  |

| bit 15                  |                                                                                                |                                                                                            |                       |                   |                |                 | bit 8   |  |  |  |  |

| U-0                     | U-0                                                                                            | U-0                                                                                        | R/W-0                 | R/W-0             | R/W-0          | R/W-0           | R/W-0   |  |  |  |  |

|                         |                                                                                                |                                                                                            | INT1IE <sup>(1)</sup> | CNIE              | CMIE           | MI2C1IE         | SI2C1IE |  |  |  |  |

| bit 7                   |                                                                                                |                                                                                            |                       | ONIL              | ONIL           | MIZOTIE         | bit (   |  |  |  |  |

| Logondi                 |                                                                                                |                                                                                            |                       |                   |                |                 |         |  |  |  |  |

| Legend:<br>R = Readable | e hit                                                                                          | W = Writable                                                                               | hit                   | U = Unimplem      | nented bit rea | d as '0'        |         |  |  |  |  |

| -n = Value at           |                                                                                                | '1' = Bit is set                                                                           |                       | '0' = Bit is clea |                | x = Bit is unkn | own     |  |  |  |  |

|                         |                                                                                                |                                                                                            |                       |                   |                |                 |         |  |  |  |  |

| bit 15                  |                                                                                                | RT2 Transmitter<br>request is enab                                                         | •                     | de dit            |                |                 |         |  |  |  |  |

|                         |                                                                                                | equest is chab                                                                             |                       |                   |                |                 |         |  |  |  |  |

| bit 14                  | U2RXIE: UAF                                                                                    | RT2 Receiver Ir                                                                            | nterrupt Enable       | bit               |                |                 |         |  |  |  |  |

|                         |                                                                                                | equest is enab                                                                             |                       |                   |                |                 |         |  |  |  |  |

| bit 13                  | •                                                                                              | equest is not e                                                                            |                       |                   |                |                 |         |  |  |  |  |

| DIL 13                  |                                                                                                | INT2IE: External Interrupt 2 Enable bit <sup>(1)</sup><br>1 = Interrupt request is enabled |                       |                   |                |                 |         |  |  |  |  |

|                         | 0 = Interrupt request is not enabled                                                           |                                                                                            |                       |                   |                |                 |         |  |  |  |  |

| bit 12                  | T5IE: Timer5 Interrupt Enable bit                                                              |                                                                                            |                       |                   |                |                 |         |  |  |  |  |

|                         | •                                                                                              | equest is enab                                                                             |                       |                   |                |                 |         |  |  |  |  |

|                         |                                                                                                | equest is not e                                                                            |                       |                   |                |                 |         |  |  |  |  |

| bit 11                  |                                                                                                | Interrupt Enable<br>request is enable                                                      |                       |                   |                |                 |         |  |  |  |  |

|                         |                                                                                                | equest is enab                                                                             |                       |                   |                |                 |         |  |  |  |  |

| bit 10                  | OC4IE: Outpu                                                                                   | <b>OC4IE:</b> Output Compare Channel 4 Interrupt Enable bit                                |                       |                   |                |                 |         |  |  |  |  |

|                         |                                                                                                | equest is enab                                                                             |                       |                   |                |                 |         |  |  |  |  |

| 1.1.0                   | •                                                                                              | equest is not e                                                                            |                       |                   |                |                 |         |  |  |  |  |

| bit 9                   | •                                                                                              | ut Compare Ch                                                                              |                       | pt Enable bit     |                |                 |         |  |  |  |  |

|                         | <ol> <li>I = Interrupt request is enabled</li> <li>Interrupt request is not enabled</li> </ol> |                                                                                            |                       |                   |                |                 |         |  |  |  |  |

| bit 8                   | DMA2IE: DMA Channel 2 Interrupt Enable bit                                                     |                                                                                            |                       |                   |                |                 |         |  |  |  |  |

|                         |                                                                                                | equest is enab                                                                             |                       |                   |                |                 |         |  |  |  |  |

|                         | •                                                                                              | equest is not e                                                                            |                       |                   |                |                 |         |  |  |  |  |

| bit 7-5                 |                                                                                                | ted: Read as '                                                                             |                       |                   |                |                 |         |  |  |  |  |

| bit 4                   |                                                                                                | nal Interrupt 1                                                                            |                       |                   |                |                 |         |  |  |  |  |

|                         |                                                                                                | equest is enab<br>equest is not e                                                          |                       |                   |                |                 |         |  |  |  |  |

| bit 3                   |                                                                                                | Change Notifica                                                                            |                       | nable bit         |                |                 |         |  |  |  |  |

|                         | •                                                                                              | 0                                                                                          | •                     | -                 |                |                 |         |  |  |  |  |

|                         |                                                                                                | equest is enab<br>equest is not e                                                          |                       |                   |                |                 |         |  |  |  |  |

#### REGISTER 8-14: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1

Note 1: If an external interrupt is enabled, the interrupt input must also be configured to an available RPn or RPIn pin. For more information, see Section 11.4 "Peripheral Pin Select (PPS)".

### 10.4 Deep Sleep Mode

Deep Sleep mode provides the lowest levels of power consumption available from the instruction-based modes.

Deep Sleep mode has these features:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption will be reduced to a minimum.

- The I/O pin directions and states are frozen.

- The Fail-Safe Clock Monitor does not operate during Sleep mode since the system clock source is disabled.

- The LPRC clock will continue to run in Deep Sleep mode if the WDT or RTCC, with LPRC as the clock source, is enabled.

- The dedicated Deep Sleep WDT and BOR systems, if enabled, are used.

- The RTCC and its clock source continue to run, if enabled. All other peripherals are disabled.

Entry into Deep Sleep mode is completely under software control. Exiting from the Deep Sleep mode can be triggered from any of the following events:

- POR event

- MCLR event

- RTCC alarm (If the RTCC is present)

- External Interrupt 0

- Deep Sleep Watchdog Timer (DSWDT) time-out

#### 10.4.1 ENTERING DEEP SLEEP MODE

Deep Sleep mode is entered by setting the DSEN bit in the DSCON register and then executing a Sleep command (PWRSAV #SLEEP\_MODE), within one instruction cycle, to minimize the chance that Deep Sleep will be spuriously entered.

If the PWRSAV command is not given within one instruction cycle, the DSEN bit will be cleared by the hardware and must be set again by the software before entering Deep Sleep mode. The DSEN bit is also automatically cleared when exiting Deep Sleep mode.

**Note:** To re-enter Deep Sleep after a Deep Sleep wake-up, allow a delay of at least 3 TcY after clearing the RELEASE bit.

The sequence to enter Deep Sleep mode is:

- If the application requires the Deep Sleep WDT, enable it and configure its clock source. For more information on Deep Sleep WDT, see Section 10.4.5 "Deep Sleep WDT".

- If the application requires Deep Sleep BOR, enable it by programming the DSBOREN Configuration bit (CW4<6>).

- 3. If the application requires wake-up from Deep Sleep on RTCC alarm, enable and configure the RTCC module. For more information on RTCC, see Section 21.0 "Real-Time Clock and Calendar (RTCC)".

- If needed, save any critical application context data by writing it to the DSGPR0 and DSGPR1 registers (optional).

- 5. Enable Deep Sleep mode by setting the DSEN bit (DSCON<15>).

- Note: A repeat sequence is required to set the DSEN bit. The repeat sequence (repeating the instruction twice) is required to write into any of the Deep Sleep registers (DSCON, DSWAKE, DSGPR0, DSGPR1). This is required to prevent the user from entering Deep Sleep by mistake. Any write to these registers has to be done twice to actually complete the write (see Example 10-2).

- 6. Enter Deep Sleep mode by issuing 3 NOP commands and then a PWRSAV #0 instruction.

Any time the DSEN bit is set, all bits in the DSWAKE register will be automatically cleared.

#### EXAMPLE 10-2: THE REPEAT SEQUENCE

| ; enable DS                       |

|-----------------------------------|

|                                   |

| ; second write required to        |

| actually write to DSCON           |

|                                   |

|                                   |

|                                   |

|                                   |

|                                   |

|                                   |

| ; enable DS (two writes required) |

|                                   |

| U-0             | U-0                               | R/W-1            | R/W-1                                   | R/W-1                              | R/W-1  | R/W-1   | R/W-1  |

|-----------------|-----------------------------------|------------------|-----------------------------------------|------------------------------------|--------|---------|--------|

| —               |                                   | MDC2R5           | MDC2R4                                  | MDC2R3                             | MDC2R2 | MDC2R1  | MDC2R0 |

| bit 15          |                                   |                  |                                         |                                    |        |         | bit 8  |

|                 |                                   |                  |                                         |                                    |        |         |        |

| U-0             | U-0                               | R/W-1            | R/W-1                                   | R/W-1                              | R/W-1  | R/W-1   | R/W-1  |

| —               |                                   | MDC1R5           | MDC1R4                                  | MDC1R3                             | MDC1R2 | MDC21R1 | MDC1R0 |

| bit 7           |                                   |                  |                                         |                                    |        |         | bit 0  |

|                 |                                   |                  |                                         |                                    |        |         |        |

| Legend:         |                                   |                  |                                         |                                    |        |         |        |

| R = Readable    | R = Readable bit W = Writable bit |                  |                                         | U = Unimplemented bit, read as '0' |        |         |        |

| -n = Value at F | POR                               | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |                                    |        | nown    |        |

#### REGISTER 11-22: RPINR31: PERIPHERAL PIN SELECT INPUT REGISTER 31

bit 15-14 Unimplemented: Read as '0'

bit 13-8 MDC2R<5:0>: Assign TX Carrier 2 Input (MDCIN2) to Corresponding RPn or RPIn Pin bits

bit 7-6 Unimplemented: Read as '0'

bit 5-0 MDC1R<5:0>: Assign TX Carrier 1 Input (MDCIN1) to Corresponding RPn or RPIn Pin bits

### 18.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Universal Asynchronous Receiver Transmitter (UART)" (DS70000582). The information in this data sheet supersedes the information in the FRM.

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the PIC24F device family. The UART is a full-duplex, asynchronous system that can communicate with peripheral devices, such as personal computers, LIN/J2602, RS-232 and RS-485 interfaces. The module also supports a hardware flow control option with the UxCTS and UxRTS pins. The UART module includes the ISO 7816 compliant Smart Card support and the IrDA<sup>®</sup> encoder/decoder unit.

The PIC24FJ128GA204 family devices are equipped with four UART modules, referred to as UART1, UART2, UART3 and UART4.

The primary features of the UARTx modules are:

- Full-Duplex, 8 or 9-Bit Data Transmission through the UxTX and UxRX Pins

- Even, Odd or No Parity Options (for 8-bit data)

- One or Two Stop bits

- Hardware Flow Control Option with the UxCTS and UxRTS Pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Range from 61 bps to 4 Mbps at 16 MIPS in 4x mode

- Baud Rates Range from 15 bps to 1 Mbps at 16 MIPS in 16x mode

- 4-Deep, First-In-First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-Bit mode with Address Detect (9<sup>th</sup> bit = 1)

- · Separate Transmit and Receive Interrupts

- · Loopback mode for Diagnostic Support

- · Polarity Control for Transmit and Receive Lines

- · Support for Sync and Break Characters

- Supports Automatic Baud Rate Detection

- IrDA<sup>®</sup> Encoder and Decoder Logic

- Includes DMA Support

- 16x Baud Clock Output for IrDA Support

- Smart Card ISO 7816 Support (UART1 and UART2 only):

- T = 0 protocol with automatic error handling

- T = 1 protocol

- Dedicated Guard Time Counter (GTC)

- Dedicated Waiting Time Counter (WTC)

A simplified block diagram of the UARTx module is shown in Figure 18-1. The UARTx module consists of these key important hardware elements:

- Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

- **Note:** Throughout this section, references to register and bit names that may be associated with a specific UART module are referred to generically by the use of 'x' in place of the specific module number. Thus, "UxSTA" might refer to the Status register for either UART1, UART2, UART3 or UART4.

| R/W-0                      | R/W-0                                                                                                 | R/W-0                                                                                                                                              | R/W-0                            | U-0              | R/W-0            | R/W-0           | R/W-0  |

|----------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------------|------------------|-----------------|--------|

| PTWREN                     | PTRDEN                                                                                                | PTBE1EN                                                                                                                                            | PTBE0EN                          | —                | AWAITM1          | AWAITM0         | AWAITE |

| bit 15                     |                                                                                                       |                                                                                                                                                    |                                  |                  |                  |                 | bit 8  |

| U-0                        | U-0                                                                                                   | U-0                                                                                                                                                | U-0                              | U-0              | U-0              | U-0             | U-0    |

|                            | _                                                                                                     | _                                                                                                                                                  | _                                | _                | _                | _               | _      |

| bit 7                      |                                                                                                       |                                                                                                                                                    |                                  |                  |                  |                 | bit C  |

| Legend:                    |                                                                                                       |                                                                                                                                                    |                                  |                  |                  |                 |        |

| R = Readable               | e bit                                                                                                 | W = Writable                                                                                                                                       | bit                              | U = Unimpler     | mented bit, read | d as '0'        |        |

| -n = Value at              | POR                                                                                                   | '1' = Bit is set                                                                                                                                   |                                  | '0' = Bit is cle | ared             | x = Bit is unkn | own    |

| bit 14<br>bit 13<br>bit 12 | 1 = PMRD/PM<br>0 = PMRD/PM<br>PTBE1EN: El<br>1 = PMBE1 p<br>0 = PMBE1 p<br>PTBE0EN: El<br>1 = PMBE0 p | ort is disabled<br>MP Read/Write<br><u>MWR</u> port is en<br>MWR port is dis<br>PMP High Nibb<br>ort is enabled<br>ort is disabled<br>PMP Low Nibb | abled<br>abled<br>le/Byte Enable | e Port Enable b  |                  |                 |        |

| bit 11                     |                                                                                                       | ted: Read as '                                                                                                                                     | )'                               |                  |                  |                 |        |

| bit 10-9                   | •                                                                                                     | >: Address Lat<br>3½ Tcy<br>2½ Tcy<br>1½ Tcy                                                                                                       |                                  | States bits      |                  |                 |        |

| bit 8                      | <b>AWAITE:</b> Add<br>1 = Wait of 11                                                                  | dress Hold Afte                                                                                                                                    | r Address Latc                   | h Strobe Wait    | States bits      |                 |        |

|                            | $0 = $ Wait of $\frac{1}{4}$                                                                          |                                                                                                                                                    |                                  |                  |                  |                 |        |

#### REGISTER 20-3: PMCON3: EPMP CONTROL REGISTER 3

#### REGISTER 20-5: PMCSxCF: EPMP CHIP SELECT x CONFIGURATION REGISTER

| R/W-0        | R/W-0                                                                                                       | R/W-0                                              | R/W-0        | U-0               | R/W-0            | R/W-0           | R/W-0 |  |  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------|-------------------|------------------|-----------------|-------|--|--|--|--|

| CSDIS        | CSP                                                                                                         | CSPTEN                                             | BEP          |                   | WRSP             | RDSP            | SM    |  |  |  |  |

| bit 15       | ·                                                                                                           | ·                                                  | •            | •                 |                  |                 | bit 8 |  |  |  |  |

|              |                                                                                                             |                                                    |              |                   |                  |                 |       |  |  |  |  |

| R/W-0        | R/W-0                                                                                                       | R/W-0                                              | U-0          | U-0               | U-0              | U-0             | U-0   |  |  |  |  |

| ACKP         | PTSZ1                                                                                                       | PTSZ0                                              | —            | —                 | _                | _               | —     |  |  |  |  |

| bit 7        |                                                                                                             |                                                    |              |                   |                  |                 | bit 0 |  |  |  |  |

|              |                                                                                                             |                                                    |              |                   |                  |                 |       |  |  |  |  |

| Legend:      |                                                                                                             |                                                    |              |                   |                  |                 |       |  |  |  |  |

| R = Readab   | le bit                                                                                                      | W = Writable                                       | bit          |                   | nented bit, read | d as '0'        |       |  |  |  |  |

| -n = Value a | t POR                                                                                                       | '1' = Bit is set                                   |              | '0' = Bit is clea | ared             | x = Bit is unkn | iown  |  |  |  |  |

|              |                                                                                                             |                                                    |              |                   |                  |                 |       |  |  |  |  |

| bit 15       | •                                                                                                           | Select x Disabl                                    |              |                   |                  |                 |       |  |  |  |  |

|              |                                                                                                             | the Chip Select                                    | •            |                   |                  |                 |       |  |  |  |  |

| hit 11       |                                                                                                             | the Chip Select                                    | -            |                   |                  |                 |       |  |  |  |  |

| bit 14       | 1 = Active-hig                                                                                              | elect x Polarity                                   | UIL          |                   |                  |                 |       |  |  |  |  |

|              | 0 = Active-hig                                                                                              |                                                    |              |                   |                  |                 |       |  |  |  |  |

| bit 13       |                                                                                                             | ACSx Port Enab                                     | ole bit      |                   |                  |                 |       |  |  |  |  |

|              | 1 = PMCSx p                                                                                                 | ort is enabled                                     |              |                   |                  |                 |       |  |  |  |  |

|              |                                                                                                             | ort is disabled                                    |              |                   |                  |                 |       |  |  |  |  |

| bit 12       | BEP: Chip Se                                                                                                | BEP: Chip Select x Nibble/Byte Enable Polarity bit |              |                   |                  |                 |       |  |  |  |  |

|              | 1 = Nibble/byte enable is active-high (PMBE0, PMBE1)<br>0 = Nibble/byte enable is active-low (PMBE0, PMBE1) |                                                    |              |                   |                  |                 |       |  |  |  |  |

|              | -                                                                                                           |                                                    | -            | E0, PMBE1)        |                  |                 |       |  |  |  |  |

| bit 11       | -                                                                                                           | ted: Read as '                                     |              |                   |                  |                 |       |  |  |  |  |

| bit 10       | <b>WRSP:</b> Chip Select x Write Strobe Polarity bit<br>For Slave modes and Master mode when SM = 0:        |                                                    |              |                   |                  |                 |       |  |  |  |  |

|              |                                                                                                             | bdes and Maste                                     |              | <u>SM = 0:</u>    |                  |                 |       |  |  |  |  |

|              |                                                                                                             | be is active-ling                                  |              |                   |                  |                 |       |  |  |  |  |

|              |                                                                                                             | ode when SM =                                      | . ,          |                   |                  |                 |       |  |  |  |  |

|              | 1 = Enable st                                                                                               | trobe is active-h                                  | igh          |                   |                  |                 |       |  |  |  |  |

|              | 0 = Enable st                                                                                               | trobe is active-lo                                 | wc           |                   |                  |                 |       |  |  |  |  |

| bit 9        | •                                                                                                           | Select x Read S                                    | ,            |                   |                  |                 |       |  |  |  |  |

|              |                                                                                                             | des and Maste                                      |              | SM = 0:           |                  |                 |       |  |  |  |  |

|              |                                                                                                             | be is active-hig                                   |              |                   |                  |                 |       |  |  |  |  |

|              | 0 = Read strobe is active-low (PMRD)<br>For Master mode when SM = 1:                                        |                                                    |              |                   |                  |                 |       |  |  |  |  |

|              | $1 = \text{Read/write strobe is active-high (PMRD/\overline{\text{PMWR}})$                                  |                                                    |              |                   |                  |                 |       |  |  |  |  |

|              | 0 = Read/Wri                                                                                                | ite strobe is acti                                 | ve-low (PMRD | /PMWR)            |                  |                 |       |  |  |  |  |

| bit 8        | SM: Chip Sel                                                                                                | lect x Strobe Mo                                   | ode bit      |                   |                  |                 |       |  |  |  |  |

|              |                                                                                                             | te and enable s                                    | · ·          | ,                 |                  |                 |       |  |  |  |  |

| L:1 7        |                                                                                                             | d write strobes (                                  |              | -                 |                  |                 |       |  |  |  |  |

| bit 7        |                                                                                                             | Select x Acknow                                    | -            | y DIT             |                  |                 |       |  |  |  |  |

|              |                                                                                                             | ctive-high <u>(PMA</u><br>ctive-low (PMA           |              |                   |                  |                 |       |  |  |  |  |

| bit 6-5      |                                                                                                             | Chip Select x P                                    |              |                   |                  |                 |       |  |  |  |  |

| 2            | 11 = Reserve                                                                                                |                                                    |              |                   |                  |                 |       |  |  |  |  |

|              | 10 = Reserve                                                                                                |                                                    |              |                   |                  |                 |       |  |  |  |  |

|              |                                                                                                             | rt size (PMD<3                                     |              |                   |                  |                 |       |  |  |  |  |

|              | -                                                                                                           | rt size (PMD<7:                                    | -            |                   |                  |                 |       |  |  |  |  |

| bit 4-0      | Unimplemen                                                                                                  | ted: Read as '                                     | Ŋ,           |                   |                  |                 |       |  |  |  |  |

#### REGISTER 20-9: PADCFG1: PAD CONFIGURATION CONTROL REGISTER

| U-0                               | U-0 | U-0 | U-0 | U-0          | U-0             | U-0    | U-0    |

|-----------------------------------|-----|-----|-----|--------------|-----------------|--------|--------|

| —                                 | —   | —   | —   | —            | —               | —      | —      |

| bit 15                            |     |     |     |              |                 |        | bit 8  |

|                                   |     |     |     |              |                 |        |        |

| U-0                               | U-0 | U-0 | U-0 | U-0          | U-0             | U-0    | R/W-0  |

| —                                 | —   | —   | —   | —            | —               | —      | PMPTTL |

| bit 7                             |     |     |     |              |                 |        | bit 0  |

|                                   |     |     |     |              |                 |        |        |

| Legend:                           |     |     |     |              |                 |        |        |

| R = Readable bit W = Writable bit |     |     | bit | U = Unimplem | ented bit, read | as '0' |        |

'0' = Bit is cleared

bit 15-1 Unimplemented: Read as '0'

-n = Value at POR

bit 0

PMPTTL: EPMP Module TTL Input Buffer Select bit

'1' = Bit is set

1 = EPMP module inputs (PMDx, PMCS1) use TTL input buffers

0 = EPMP module inputs use Schmitt Trigger input buffers

x = Bit is unknown

| R/W-0      | R/W-0                                                                                                                 | R/W-0                                           | R/W-0            | R/W-0             | R/W-0                        | R/W-0           | R/W-0                   |  |  |  |

|------------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|------------------|-------------------|------------------------------|-----------------|-------------------------|--|--|--|

| ALRMEN     | CHIME                                                                                                                 | AMASK3                                          | AMASK2           | AMASK1            | AMASK0                       | ALRMPTR1        | ALRMPTR0                |  |  |  |

| bit 15     |                                                                                                                       | •                                               |                  |                   |                              |                 | bit 8                   |  |  |  |

| R/W-0      | R/W-0                                                                                                                 | R/W-0                                           | R/W-0            | R/W-0             | R/W-0                        | R/W-0           | R/W-0                   |  |  |  |

| ARPT7      | ARPT6                                                                                                                 | ARPT5                                           | ARPT4            | ARPT3             | ARPT2                        | ARPT1           | ARPT0                   |  |  |  |

| bit 7      |                                                                                                                       |                                                 |                  |                   |                              |                 | bit C                   |  |  |  |

| Legend:    |                                                                                                                       |                                                 |                  |                   |                              |                 |                         |  |  |  |

| R = Reada  | able bit                                                                                                              | W = Writable b                                  | it               | U = Unimplem      | ented bit, read              | as '0'          |                         |  |  |  |

| -n = Value | at POR                                                                                                                | '1' = Bit is set                                |                  | '0' = Bit is clea |                              | x = Bit is unkn | own                     |  |  |  |

|            |                                                                                                                       |                                                 |                  |                   |                              |                 |                         |  |  |  |

| bit 15     |                                                                                                                       | arm Enable bit<br>enabled (cleared a            | automatically af | er an alarm eve   | nt whenever AF               | PT<7·0> = 00h : | and CHIME = $0^{\circ}$ |  |  |  |

|            | 0 = Alarm is c                                                                                                        |                                                 | automatically an |                   |                              |                 |                         |  |  |  |

| bit 14     | CHIME: Chim                                                                                                           | e Enable bit                                    |                  |                   |                              |                 |                         |  |  |  |

|            |                                                                                                                       | enabled; ARPT<<br>disabled; ARPT<               |                  |                   |                              | FFh             |                         |  |  |  |

| bit 13-10  |                                                                                                                       | : Alarm Mask C                                  | •                | -                 |                              |                 |                         |  |  |  |

|            | 0000 = Every                                                                                                          |                                                 | 5                |                   |                              |                 |                         |  |  |  |

|            | 0001 = Every                                                                                                          |                                                 |                  |                   |                              |                 |                         |  |  |  |

|            | 0010 = Every 10 seconds                                                                                               |                                                 |                  |                   |                              |                 |                         |  |  |  |

|            | 0011 = Every minute<br>0100 = Every 10 minutes                                                                        |                                                 |                  |                   |                              |                 |                         |  |  |  |

|            | 0101 = Every hour                                                                                                     |                                                 |                  |                   |                              |                 |                         |  |  |  |

|            | 0110 = Once<br>0111 = Once                                                                                            |                                                 |                  |                   |                              |                 |                         |  |  |  |

|            | 1000 = Once                                                                                                           |                                                 |                  |                   |                              |                 |                         |  |  |  |

|            | 1001 <b>= Once</b>                                                                                                    | a year (except v                                |                  | d for February    | 29 <sup>th</sup> , once ever | y 4 years)      |                         |  |  |  |

|            |                                                                                                                       | rved – do not us                                |                  |                   |                              |                 |                         |  |  |  |

| bit 9-8    |                                                                                                                       | rved – do not us<br>: <b>0&gt;:</b> Alarm Value |                  | low Pointer hits  | 2                            |                 |                         |  |  |  |

| bit 5-0    |                                                                                                                       | corresponding Al                                | -                |                   |                              | ALH and ALRM    | VALL registers          |  |  |  |

|            |                                                                                                                       | R<1:0> value de                                 |                  |                   |                              |                 |                         |  |  |  |

|            | ALRMVAL<15                                                                                                            |                                                 |                  |                   |                              |                 |                         |  |  |  |

|            | 00 = ALRMM                                                                                                            |                                                 |                  |                   |                              |                 |                         |  |  |  |

|            | 01 = ALRMWD<br>10 = ALRMMNTH                                                                                          |                                                 |                  |                   |                              |                 |                         |  |  |  |

|            | 11 = PWCSTAB                                                                                                          |                                                 |                  |                   |                              |                 |                         |  |  |  |

|            | 11 11000                                                                                                              |                                                 |                  |                   |                              |                 |                         |  |  |  |

|            | ALRMVAL<7:                                                                                                            |                                                 |                  |                   |                              |                 |                         |  |  |  |

|            | ALRMVAL<7:<br>00 = ALRMSE                                                                                             | EC                                              |                  |                   |                              |                 |                         |  |  |  |

|            | ALRMVAL<7:                                                                                                            | EC<br>R                                         |                  |                   |                              |                 |                         |  |  |  |

|            | ALRMVAL<7:<br>00 = ALRMSE<br>01 = ALRMHE                                                                              | EC<br>R<br>AY                                   |                  |                   |                              |                 |                         |  |  |  |

| bit 7-0    | ALRMVAL<7::<br>00 = ALRMSE<br>01 = ALRMHF<br>10 = ALRMD/<br>11 = PWCSA<br>ARPT<7:0>:                                  | EC<br>R<br>AY<br>MP<br>Alarm Repeat C           |                  |                   |                              |                 |                         |  |  |  |

| bit 7-0    | ALRMVAL<7::<br>00 = ALRMSE<br>01 = ALRMHF<br>10 = ALRMD/<br>11 = PWCSA<br>ARPT<7:0>:                                  | EC<br>R<br>AY<br>MP                             |                  |                   |                              |                 |                         |  |  |  |

| bit 7-0    | ALRMVAL<7::<br>00 = ALRMSE<br>01 = ALRMHF<br>10 = ALRMD/<br>11 = PWCSA<br>ARPT<7:0>:                                  | EC<br>R<br>AY<br>MP<br>Alarm Repeat C           |                  |                   |                              |                 |                         |  |  |  |

| bit 7-0    | ALRMVAL<7::<br>00 = ALRMSE<br>01 = ALRMHF<br>10 = ALRMD/<br>11 = PWCSA<br>ARPT<7:0>:                                  | EC<br>R<br>AY<br>MP<br>Alarm Repeat C           |                  |                   |                              |                 |                         |  |  |  |

| bit 7-0    | ALRMVAL<7:<br>00 = ALRMSE<br>01 = ALRMHE<br>10 = ALRMDA<br>11 = PWCSA<br>ARPT<7:0>: A<br>11111111 = A<br>00000000 = A | EC<br>R<br>AY<br>MP<br>Alarm Repeat C           | 255 more time    | es                |                              |                 |                         |  |  |  |

#### REGISTER 21-3: ALCFGRPT: ALARM CONFIGURATION REGISTER

## REGISTER 21-11: RTCCSWT: RTCC POWER CONTROL AND SAMPLE WINDOW TIMER REGISTER<sup>(1)</sup>

| R/W-x    |

|----------|----------|----------|----------|----------|----------|----------|----------|

| PWCSTAB7 | PWCSTAB6 | PWCSTAB5 | PWCSTAB4 | PWCSTAB3 | PWCSTAB2 | PWCSTAB1 | PWCSTAB0 |

| bit 15   |          |          |          |          |          |          | bit 8    |

| R/W-x                   |

|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|

| PWCSAMP7 <sup>(2)</sup> | PWCSAMP6 <sup>(2)</sup> | PWCSAMP5 <sup>(2)</sup> | PWCSAMP4 <sup>(2)</sup> | PWCSAMP3 <sup>(2)</sup> | PWCSAMP2 <sup>(2)</sup> | PWCSAMP1 <sup>(2)</sup> | PWCSAMP0 <sup>(2)</sup> |

| bit 7                   |                         |                         |                         |                         |                         |                         | bit 0                   |

| Legend:                                                                       |                  |                        |                    |  |  |  |  |  |

|-------------------------------------------------------------------------------|------------------|------------------------|--------------------|--|--|--|--|--|

| R = Readable bit                                                              | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |  |  |  |  |

| -n = Value at POR                                                             | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |  |  |  |  |

|                                                                               |                  |                        |                    |  |  |  |  |  |

| hit 15-8 <b>PWCSTAB&lt;7:0&gt;:</b> Power Control Stability Window Timer hits |                  |                        |                    |  |  |  |  |  |

| 01C 15-8 | PWCSTAB<7:0>: Power Control Stability Window Timer bits                            |

|----------|------------------------------------------------------------------------------------|

|          | 11111111 = Stability window is 255 TPWCCLK clock periods                           |

|          | 11111110 = Stability window is 254 TPWCCLK clock periods                           |

|          | •                                                                                  |

|          | •                                                                                  |

|          | •                                                                                  |

|          | 00000001 = Stability window is 1 TPWCCLK clock period                              |

|          | 00000000 = No stability window; sample window starts when the alarm event triggers |

| bit 7-0  | PWCSAMP<7:0>: Power Control Sample Window Timer bits <sup>(2)</sup>                |

|          | 11111111 = Sample window is always enabled, even when PWCEN = 0                    |

|          | 11111110 = Sample window is 254 TPWCCLK clock periods                              |

|          | •                                                                                  |

|          | •                                                                                  |

|          | •                                                                                  |

|          | 00000001 = Sample window is 1 TPWCCLK clock period<br>00000000 = No sample window  |

|          |                                                                                    |

- **Note 1:** A write to this register is only allowed when RTCWREN = 1.

- 2: The sample window always starts when the stability window timer expires, except when its initial value is 00h.

## 24.0 12-BIT A/D CONVERTER WITH THRESHOLD DETECT

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the 12-Bit A/D Converter, refer to the "dsPIC33/PIC24 Family Reference Manual", "12-Bit A/D Converter with Threshold Detect" (DS39739).

The 12-bit A/D Converter has the following key features:

- Successive Approximation Register (SAR) Conversion

- Conversion Speeds of up to 200 ksps

- Up to 20 Analog Input Channels (internal and external)

- Selectable 10-Bit or 12-Bit (default) Conversion Resolution

- Multiple Internal Reference Input Channels

- External Voltage Reference Input Pins

- Unipolar Differential Sample-and-Hold (S/H) Amplifier

- Automated Threshold Scan and Compare

Operation to Pre-Evaluate Conversion Results

- Selectable Conversion Trigger Source

- Fixed Length (one word per channel), Configurable Conversion Result Buffer

- Four Options for Results Alignment

- Configurable Interrupt Generation

- Enhanced DMA Operations with Indirect Address Generation

- Operation During CPU Sleep and Idle modes

The 12-bit A/D Converter module is an enhanced version of the 10-bit module offered in earlier PIC24 devices. It is a Successive Approximation Register (SAR) Converter, enhanced with 12-bit resolution, a wide range of automatic sampling options, tighter integration with other analog modules and a configurable results buffer.

It also includes a unique Threshold Detect feature that allows the module itself to make simple decisions based on the conversion results, and enhanced operation with the DMA Controller through Peripheral Indirect Addressing (PIA).

A simplified block diagram for the module is shown in Figure 24-1.

#### 24.1 Basic Operation

To perform a standard A/D conversion:

- 1. Configure the module:

- a) Configure port pins as analog inputs by setting the appropriate bits in the ANSx registers (see Section 11.2 "Configuring Analog Port Pins (ANSx)" for more information).

- b) Select the voltage reference source to match the expected range on analog inputs (AD1CON2<15:13>).

- c) Select the positive and negative multiplexer inputs for each channel (AD1CHS<15:0>).

- Select the analog conversion clock to match the desired data rate with the processor clock (AD1CON3<7:0>).

- e) Select the appropriate sample/conversion sequence (AD1CON1<7:4> and AD1CON3<12:8>).

- For Channel A scanning operations, select the positive channels to be included (AD1CSSH and AD1CSSL registers).

- g) Select how conversion results are presented in the buffer (AD1CON1<9:8> and AD1CON5 register).

- h) Select the interrupt rate (AD1CON2<5:2>).

- i) Turn on A/D module (AD1CON1<15>).

- 2. Configure the A/D interrupt (if required):

- a) Clear the AD1IF bit (IFS0<13>).

- b) Enable the AD1IE interrupt (IEC0<13>).

- c) Select the A/D interrupt priority (IPC3<6:4>).

- If the module is configured for manual sampling, set the SAMP bit (AD1CON1<1>) to begin sampling.

| R/W-0                                                                                   | U-0                                                                                                                                                                                              | R/W-0            | R/W-0                | R/W-0                                   | R/W-0           | R/W-0      | R/W-0      |  |  |  |

|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------|-----------------------------------------|-----------------|------------|------------|--|--|--|

| ADON                                                                                    | —                                                                                                                                                                                                | ADSIDL           | DMABM <sup>(1)</sup> | DMAEN                                   | MODE12          | FORM1      | FORM0      |  |  |  |

| bit 15                                                                                  |                                                                                                                                                                                                  |                  |                      |                                         |                 |            | bit 8      |  |  |  |

|                                                                                         |                                                                                                                                                                                                  | <b>D</b> 444 A   |                      |                                         |                 |            |            |  |  |  |

| R/W-0                                                                                   | R/W-0                                                                                                                                                                                            | R/W-0            | R/W-0                | U-0                                     | R/W-0           | R/W-0, HSC | R/C-0, HSC |  |  |  |

| SSRC3                                                                                   | SSRC2                                                                                                                                                                                            | SSRC1            | SSRC0                |                                         | ASAM            | SAMP       | DONE       |  |  |  |