Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART                    |

| Peripherals                | AES, Brown-out Detect/Reset, DMA, I2S, HLVD, POR, PWM, WDT                    |

| Number of I/O              | 21                                                                            |

| Program Memory Size        | 64KB (64K x 8)                                                                |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 10x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Through Hole                                                                  |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                       |

| Supplier Device Package    | 28-SPDIP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64ga202-e-sp |

TABLE 4-6: TIMER REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14                                                      | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9       | Bit 8        | Bit 7         | Bit 6        | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|------|--------|-------------------------------------------------------------|--------|--------|--------|--------|-------------|--------------|---------------|--------------|--------|--------|-------|-------|-------|-------|---------------|

| TMR1         | 024C |        | Timer1 Register                                             |        |        |        |        |             |              |               |              |        |        |       | 0000  |       |       |               |

| PR1          | 024E |        | Timer1 Period Register                                      |        |        |        |        |             |              |               |              |        |        | FFFF  |       |       |       |               |

| T1CON        | 0250 | TON    | TON - TSIDL TECS1 TECS0 - TGATE TCKPS1 TCKPS0 - TSYNC TCS - |        |        |        |        |             |              |               |              | 0000   |        |       |       |       |       |               |

| TMR2         | 0252 |        |                                                             |        |        |        |        |             | Timer2 I     | Register      |              |        |        |       |       |       |       | 0000          |

| TMR3HLD      | 0254 |        |                                                             |        |        |        | Timer: | 3 Holding R | egister (for | 32-bit time   | roperations  | only)  |        |       |       |       |       | 0000          |

| TMR3         | 0256 |        |                                                             |        |        |        |        |             | Timer3 I     | Register      |              |        |        |       |       |       |       | 0000          |

| PR2          | 0258 |        | Timer2 Period Register                                      |        |        |        |        |             |              |               |              |        | FFFF   |       |       |       |       |               |

| PR3          | 025A |        |                                                             |        |        |        |        |             | Timer3 Peri  | od Register   | •            |        |        |       |       |       |       | FFFF          |

| T2CON        | 025C | TON    | _                                                           | TSIDL  | _      | _      | _      | TECS1       | TECS0        | _             | TGATE        | TCKPS1 | TCKPS0 | T32   | _     | TCS   | _     | 0000          |

| T3CON        | 025E | TON    | _                                                           | TSIDL  | _      | _      | _      | TECS1       | TECS0        | _             | TGATE        | TCKPS1 | TCKPS0 | _     | _     | TCS   | _     | 0000          |

| TMR4         | 0260 |        |                                                             |        |        |        |        |             | Timer4 I     | Register      |              |        |        |       |       |       |       | 0000          |

| TMR5HLD      | 0262 |        |                                                             |        |        |        | Tim    | er5 Holdin  | g Register ( | for 32-bit op | perations or | nly)   |        |       |       |       |       | 0000          |

| TMR5         | 0264 |        |                                                             |        |        |        |        |             | Timer5 I     | Register      |              |        |        |       |       |       |       | 0000          |

| PR4          | 0266 |        | Timer4 Period Register                                      |        |        |        |        |             |              |               |              |        | FFFF   |       |       |       |       |               |

| PR5          | 0268 |        | Timer5 Period Register                                      |        |        |        |        |             |              |               |              |        | FFFF   |       |       |       |       |               |

| T4CON        | 026A | TON    | DN - TSIDL TECS1 TECS0 - TGATE TCKPS1 TCKPS0 T45 - TCS -    |        |        |        |        |             |              |               | 0000         |        |        |       |       |       |       |               |

| T5CON        | 026C | TON    | _                                                           | TSIDL  | _      | _      | _      | TECS1       | TECS0        | _             | TGATE        | TCKPS1 | TCKPS0 | _     | _     | TCS   | _     | 0000          |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

TABLE 4-34: EDS MEMORY ADDRESS WITH DIFFERENT PAGES AND ADDRESSES

| DSRPAG<br>(Data Space Read<br>Register) | DSWPAG<br>(Data Space Write<br>Register) | Source/Destination<br>Address While<br>Indirect<br>Addressing | 24-Bit EA<br>Pointing to EDS    | Comment                           |

|-----------------------------------------|------------------------------------------|---------------------------------------------------------------|---------------------------------|-----------------------------------|

| x <sup>(1)</sup>                        | x <sup>(1)</sup>                         | 0000h to 1FFFh                                                | 000000h to<br>001FFFh           | Near Data Space <sup>(2)</sup>    |

| χ, ,                                    | X ,                                      | 2000h to 7FFFh                                                | 002000h to<br>007FFFh           |                                   |

| 001h                                    | 001h                                     |                                                               | 008000h to<br>00FFFEh           |                                   |

| 002h                                    | 002h                                     |                                                               | 010000h to<br>017FFEh           |                                   |

| 003h<br>•<br>•                          | 003h<br>•<br>•                           | 8000h to FFFFh                                                | 018000h to<br>0187FEh<br>•<br>• | EPMP Memory Space                 |

| •<br>•<br>1FFh                          | •<br>•<br>1FFh                           |                                                               | •<br>FF8000h to<br>FFFFFEh      |                                   |

| 000h                                    | 000h                                     |                                                               | Invalid Address                 | Address Error Trap <sup>(3)</sup> |

Note 1: If the source/destination address is below 8000h, the DSRPAG and DSWPAG registers are not considered.

- 2: This Data Space can also be accessed by Direct Addressing.

- **3:** When the source/destination address is above 8000h and DSRPAG/DSWPAG are '0', an address error trap will occur.

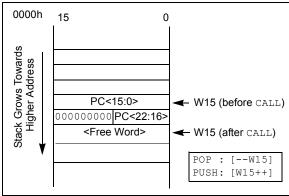

#### 4.2.6 SOFTWARE STACK

Apart from its use as a Working register, the W15 register in PIC24F devices is also used as a Software Stack Pointer (SSP). The pointer always points to the first available free word and grows from lower to higher addresses. It predecrements for stack pops and post-increments for stack pushes, as shown in Figure 4-7. Note that for a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, ensuring that the MSB is always clear.

**Note:** A PC push during exception processing will concatenate the SRL Register to the MSB of the PC prior to the push.

The Stack Pointer Limit Value (SPLIM) register, associated with the Stack Pointer, sets an upper address boundary for the stack. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0' as all stack operations must be word-aligned. Whenever an EA is generated using W15 as a Source or Destination Pointer, the resulting address is compared with the value in SPLIM. If the contents of the Stack Pointer (W15) and the SPLIM register are equal, and a push operation is performed, a stack error trap will not occur. The stack error trap will occur on a subsequent push operation. Thus, for example, if it is

desirable to cause a stack error trap when the stack grows beyond address, 2000h in RAM, initialize the SPLIM with the value, 1FFEh.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0800h. This prevents the stack from interfering with the SFR space.

A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

FIGURE 4-7: CALL STACK FRAME

#### REGISTER 8-8: IFS3: INTERRUPT FLAG STATUS REGISTER 3

| U-0    | R/W-0 | R/W-0  | R/W-0    | R/W-0    | R/W-0    | U-0 | R/W-0    |

|--------|-------|--------|----------|----------|----------|-----|----------|

| _      | RTCIF | DMA5IF | SPI3RXIF | SPI2RXIF | SPI1RXIF | _   | KEYSTRIF |

| bit 15 |       |        |          |          |          |     | bit 8    |

| R/W-0   | R/W-0  | R/W-0  | U-0 | U-0 | R/W-0   | R/W-0   | U-0   |

|---------|--------|--------|-----|-----|---------|---------|-------|

| CRYDNIF | INT4IF | INT3IF | _   | _   | MI2C2IF | SI2C2IF | _     |

| bit 7   |        |        |     |     |         |         | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14 RTCIF: Real-Time Clock/Calendar Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 13 DMA5IF: DMA Channel 5 Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 12 SPI3RXIF: SPI3 Receive Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 11 SPI2RXIF: SPI2 Receive Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 10 SPI1RXIF: SPI1 Receive Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 9 **Unimplemented:** Read as '0'

bit 8 KEYSTRIF: Cryptographic Key Store Program Done Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 7 CRYDNIF: Cryptographic Operation Done Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 6 INT4IF: External Interrupt 4 Flag Status bit

1 = Interrupt request has occurred

0 = Interrupt request has not occurred

bit 5 INT3IF: External Interrupt 3 Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 4-3 **Unimplemented:** Read as '0'

bit 2 MI2C2IF: Master I2C2 Event Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 1 SI2C2IF: Slave I2C2 Event Interrupt Flag Status bit

1 = Interrupt request has occurred0 = Interrupt request has not occurred

bit 0 **Unimplemented:** Read as '0'

### REGISTER 8-45: INTTREG: INTERRUPT CONTROLLER TEST REGISTER

| R-0    | r-0 | R/W-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|--------|-----|-------|-----|-------|-------|-------|-------|

| CPUIRQ | _   | VHOLD | _   | ILR3  | ILR2  | ILR1  | ILR0  |

| bit 15 |     |       |     |       |       |       | bit 8 |

| R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| VECNUM7 | VECNUM6 | VECNUM5 | VECNUM4 | VECNUM3 | VECNUM2 | VECNUM1 | VECNUM0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           | r = Reserved bit |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 15 **CPUIRQ:** CPU Interrupt Request from Interrupt Controller bit

1 = An interrupt request has occurred but has not yet been Acknowledged by the CPU

0 = No interrupt request is unacknowledged

bit 14 Reserved: Maintain as '0'

bit 13 VHOLD: Vector Number Capture Configuration bit

1 = VECNUM<7:0> contain the value of the highest priority pending interrupt

0 = VECNUM<7:0> contain the value of the last Acknowledged interrupt (i.e., the last interrupt that has occurred with higher priority than the CPU, even if other interrupts are pending)

bit 12 **Unimplemented:** Read as '0'

bit 11-8 ILR<3:0>: New CPU Interrupt Priority Level bits

1111 = CPU Interrupt Priority Level is 15

.

•

0001 = CPU Interrupt Priority Level is 1 0000 = CPU Interrupt Priority Level is 0

bit 7-0 **VECNUM<7:0>:** Vector Number of Pending Interrupt or Last Acknowledged Interrupt bits

When VHOLD = 1:

Indicates the vector number (from 0 to 118) of the last interrupt to occur.

When VHOLD = 0:

Indicates the vector number (from 0 to 118) of the interrupt request currently being handled.

NOTES:

### REGISTER 11-10: RPINR11: PERIPHERAL PIN SELECT INPUT REGISTER 11

| U-0    | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| _      | _   | OCFBR5 | OCFBR4 | OCFBR3 | OCFBR2 | OCFBR1 | OCFBR0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| _     | _   | OCFAR5 | OCFAR4 | OCFAR3 | OCFAR2 | OCFAR1 | OCFAR0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 **Unimplemented:** Read as '0'

bit 13-8 OCFBR<5:0>: Assign Output Compare Fault B (OCFB) to Corresponding RPn or RPIn Pin bits

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 OCFAR<5:0>: Assign Output Compare Fault A (OCFA) to Corresponding RPn or RPIn Pin bits

#### REGISTER 11-11: RPINR17: PERIPHERAL PIN SELECT INPUT REGISTER 17

| U-0    | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1  | R/W-1 | R/W-1 |

|--------|-----|-------|-------|-------|--------|-------|-------|

| _      | _   |       |       | U3RXI | R<5:0> |       |       |

| bit 15 |     |       |       |       |        |       | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| _     | _   | _   | _   | _   | _   | _   | _     |

| bit 7 |     |     |     |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 Unimplemented: Read as '0'

bit 13-8 U3RXR<5:0>: Assign UART3 Receive (U3RX) to Corresponding RPn or RPIn Pin bits

bit 7-0 **Unimplemented:** Read as '0'

### REGISTER 11-22: RPINR31: PERIPHERAL PIN SELECT INPUT REGISTER 31

| U-0    | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| _      | _   | MDC2R5 | MDC2R4 | MDC2R3 | MDC2R2 | MDC2R1 | MDC2R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

| U-0   | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1   | R/W-1  |

|-------|-----|--------|--------|--------|--------|---------|--------|

| _     | _   | MDC1R5 | MDC1R4 | MDC1R3 | MDC1R2 | MDC21R1 | MDC1R0 |

| bit 7 |     |        |        |        |        |         | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-14 **Unimplemented:** Read as '0'

bit 13-8 MDC2R<5:0>: Assign TX Carrier 2 Input (MDCIN2) to Corresponding RPn or RPIn Pin bits

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 MDC1R<5:0>: Assign TX Carrier 1 Input (MDCIN1) to Corresponding RPn or RPIn Pin bits

### REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER<sup>(1)</sup>

| R/W-0  | U-0 | R/W-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 |

|--------|-----|-------|-----|-----|-----|-------|-------|

| TON    | _   | TSIDL | _   | _   | _   | TECS1 | TECS0 |

| bit 15 |     |       |     |     |     |       | bit 8 |

| U-0   | R/W-0 | R/W-0  | R/W-0  | U-0 | R/W-0 | R/W-0 | U-0   |

|-------|-------|--------|--------|-----|-------|-------|-------|

| _     | TGATE | TCKPS1 | TCKPS0 | _   | TSYNC | TCS   | _     |

| bit 7 |       |        |        |     |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **TON:** Timer1 On bit

1 = Starts 16-bit Timer1

0 = Stops 16-bit Timer1

bit 14 **Unimplemented:** Read as '0'

bit 13 TSIDL: Timer1 Stop in Idle Mode bit

1 = Discontinues module operation when device enters Idle mode

0 = Continues module operation in Idle mode

bit 12-10 Unimplemented: Read as '0'

bit 9-8 **TECS<1:0>:** Timer1 Extended Clock Source Select bits (selected when TCS = 1)

When TCS = 1:

11 = Generic Timer (TMRCK) External Input

10 = LPRC Oscillator

01 = T1CK External Clock Input

00 = SOSC

When TCS = 0:

These bits are ignored; the Timer is clocked from the internal system clock (Fosc/2).

bit 7 **Unimplemented:** Read as '0'

bit 6 TGATE: Timer1 Gated Time Accumulation Enable bit

$\frac{\text{When TCS} = 1:}{\text{This bit is ignored.}}$

When TCS = 0:

1 = Gated time accumulation is enabled0 = Gated time accumulation is disabled

bit 5-4 TCKPS<1:0>: Timer1 Input Clock Prescale Select bits

11 = 1:256

10 = 1:64

01 = 1:8

00 = 1:1

bit 3 Unimplemented: Read as '0'

**Note 1:** Changing the value of T1CON while the timer is running (TON = 1) causes the timer prescale counter to reset and is not recommended.

NOTES:

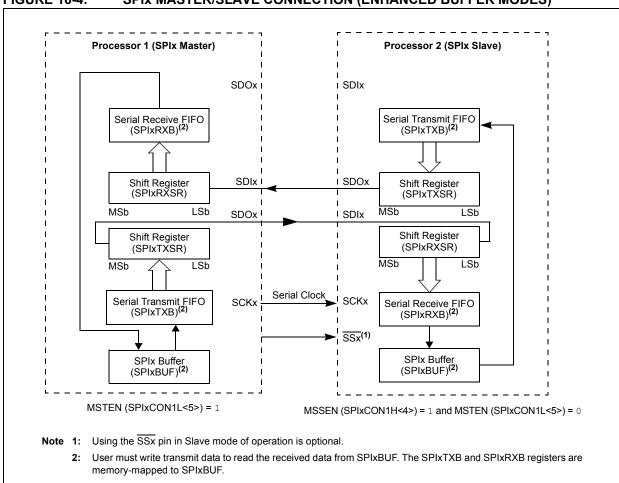

FIGURE 16-4: SPIX MASTER/SLAVE CONNECTION (ENHANCED BUFFER MODES)

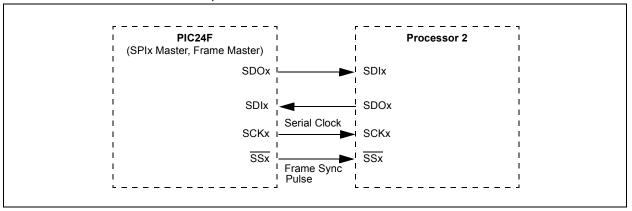

### FIGURE 16-5: SPIX MASTER, FRAME MASTER CONNECTION DIAGRAM

# 17.2 Setting Baud Rate when Operating as a Bus Master

To compute the Baud Rate Generator reload value, use Equation 17-1.

# EQUATION 17-1: COMPUTING BAUD RATE RELOAD VALUE<sup>(1)</sup>

$$I2CxBRG = \left(\left(\frac{1}{FSCL} - PGDX\right) \times \frac{FCY}{2}\right) - 2$$

Note 1: Based on Fcy = Fosc/2; Doze mode and PLL are disabled.

#### 17.3 Slave Address Masking

The I2CxMSK register (Register 17-4) designates address bit positions as "don't care" for both 7-Bit and 10-Bit Addressing modes. Setting a particular bit location (= 1) in the I2CxMSK register causes the slave module to respond, whether the corresponding address bit value is a '0' or a '1'. For example, when I2CxMSK is set to '00100000000', the slave module will detect both addresses, '00000000000' and '0010000000'.

To enable address masking, the Intelligent Peripheral Management Interface (IPMI) must be disabled by clearing the STRICT bit (I2CxCONL<11>).

As a result of changes in the I<sup>2</sup>C<sup>™</sup> protocol, the addresses in Table 17-1 are reserved and will not be Acknowledged in Slave mode. This includes any address mask settings that include any of these addresses.

### TABLE 17-1: I2Cx RESERVED ADDRESSES<sup>(1)</sup>

| Slave Address | R/W Bit | Description                            |

|---------------|---------|----------------------------------------|

| 0000 000      | 0       | General Call Address <sup>(2)</sup>    |

| 0000 000      | 1       | Start Byte                             |

| 0000 001      | Х       | Cbus Address                           |

| 0000 01x      | Х       | Reserved                               |

| 0000 1xx      | Х       | HS Mode Master Code                    |

| 1111 0xx      | Х       | 10-Bit Slave Upper Byte <sup>(3)</sup> |

| 1111 1xx      | Х       | Reserved                               |

Note:

- Note 1: The address bits listed here will never cause an address match independent of address mask settings.

- 2: This address will be Acknowledged only if GCEN = 1.

- 3: A match on this address can only occur on the upper byte in 10-Bit Addressing mode.

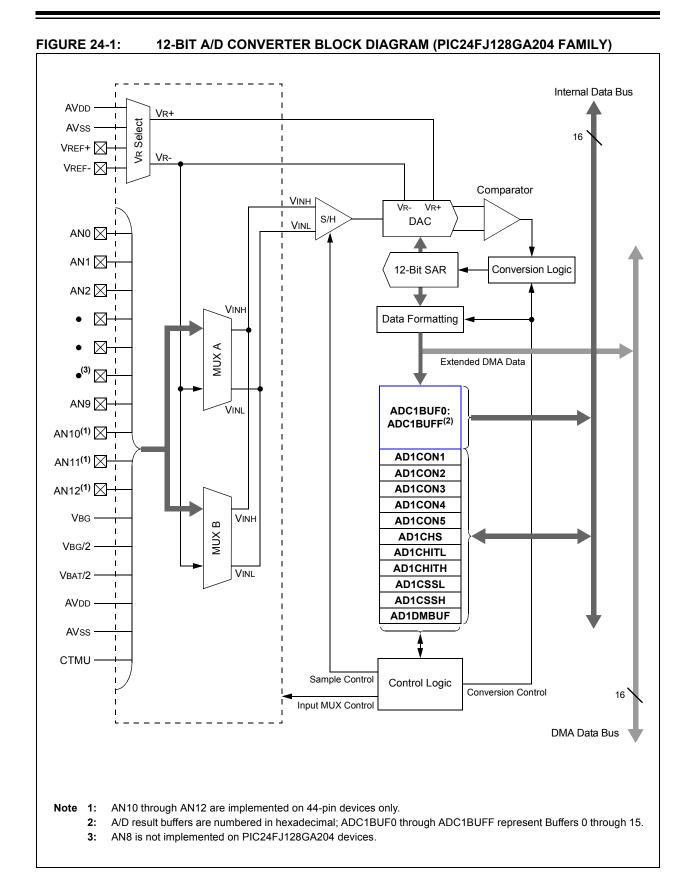

### REGISTER 24-1: AD1CON1: A/D CONTROL REGISTER 1 (CONTINUED)

bit 1 SAMP: A/D Sample Enable bit

1 = A/D Sample-and-Hold amplifiers are sampling 0 = A/D Sample-and-Hold amplifiers are holding

bit 0 **DONE:** A/D Conversion Status bit

1 = A/D conversion cycle has completed

0 = A/D conversion cycle has not started or is in progress

Note 1: This bit is only available when Extended DMA/Buffer features are available (DMAEN = 1).

#### REGISTER 27-2: CTMUCON2: CTMU CONTROL REGISTER 2

| R/W-0   | R/W-0   | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0    |

|---------|---------|----------|----------|----------|----------|----------|----------|

| EDG1MOD | EDG1POL | EDG1SEL3 | EDG1SEL2 | EDG1SEL1 | EDG1SEL0 | EDG2STAT | EDG1STAT |

| bit 15  |         |          |          |          |          |          | bit 8    |

| R/W-0   | R/W-0   | R/W-0    | R/W-0    | R/W-0    | R/W-0    | U-0 | U-0   |

|---------|---------|----------|----------|----------|----------|-----|-------|

| EDG2MOD | EDG2POL | EDG2SEL3 | EDG2SEL2 | EDG2SEL1 | EDG2SEL0 |     | _     |

| bit 7   |         |          |          |          |          |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **EDG1MOD:** Edge 1 Edge-Sensitive Select bit

1 = Input is edge-sensitive0 = Input is level-sensitive

bit 14 EDG1POL: Edge 1 Polarity Select bit

${\tt 1}$  = Edge 1 is programmed for a positive edge response

0 = Edge 1 is programmed for a negative edge response

bit 13-10 EDG1SEL<3:0>: Edge 1 Source Select bits

1111 = Edge 1 source is Comparator 3 output

1110 = Edge 1 source is Comparator 2 output

1101 = Edge 1 source is Comparator 1 output

1100 = Edge 1 source is IC3

1011 = Edge 1 source is IC2

1010 = Edge 1 source is IC1

1001 = Edge 1 source is CTED8

1000 = Edge 1 source is CTED7<sup>(1)</sup>

0111 = Edge 1 source is CTED6

0110 = Edge 1 source is CTED5

0101 = Edge 1 source is CTED4

0100 = Edge 1 source is CTED3

0011 = Edge 1 source is CTED1

0010 = Edge 1 source is CTED2

0001 = Edge 1 source is OC1

0000 = Edge 1 source is Timer1

bit 9 **EDG2STAT:** Edge 2 Status bit

Indicates the status of Edge 2 and can be written to control current source.

1 = Edge 2 has occurred

0 = Edge 2 has not occurred

bit 8 EDG1STAT: Edge 1 Status bit

Indicates the status of Edge 1 and can be written to control current source.

1 = Edge 1 has occurred

0 = Edge 1 has not occurred

bit 7 **EDG2MOD:** Edge 2 Edge-Sensitive Select bit

1 = Input is edge-sensitive

0 = Input is level-sensitive

bit 6 EDG2POL: Edge 2 Polarity Select bit

1 = Edge 2 is programmed for a positive edge response

0 = Edge 2 is programmed for a negative edge response

Note 1: Edge source, CTED7, is not available in 28-pin packages.

### REGISTER 29-2: CW2: FLASH CONFIGURATION WORD 2 (CONTINUED)

bit 4-3 WDTCLK<1:0>: WDT Clock Source Select bits

When WDTCMX = 1:

11 = LPRC

10 = Either the 31 kHz FRC source or LPRC, depending on device configuration (1)

01 = SOSC input

00 = System clock when active, LPRC while in Sleep mode

When WDTCMX = 0:

LPRC is always the WDT clock source.

bit 2 Reserved: Configure as '1'

bit 1-0 **POSCMD<1:0>:** Primary Oscillator Configuration bits

11 = Primary Oscillator mode is disabled10 = HS Oscillator mode is selected

01 = XT Oscillator mode is selected00 = EC Oscillator mode is selected

**Note 1:** The 31 kHz FRC source is used when a Windowed WDT mode is selected and the LPRC is not being used as the system clock. The LPRC is used when the device is in Sleep mode and in all other cases.

### 30.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- · Integrated Development Environment

- MPLAB® X IDE Software

- · Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>TM</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- · Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- · Third-party development tools

# 30.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac OS<sup>®</sup> X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

#### Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

Project-Based Workspaces:

- · Multiple projects

- · Multiple tools

- · Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- · Built-in support for Bugzilla issue tracker

#### TABLE 32-11: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS

**Operating Conditions:**  $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$  for Industrial  $-40^{\circ}\text{C} < \text{TA} < +125^{\circ}\text{C}$  for Extended

|              | -40 C S IA S + 123 C IOI Exteriueu |                                         |     |     |     |       |                                                                 |  |  |  |  |

|--------------|------------------------------------|-----------------------------------------|-----|-----|-----|-------|-----------------------------------------------------------------|--|--|--|--|

| Param<br>No. | Symbol                             | Characteristics                         | Min | Тур | Max | Units | Comments                                                        |  |  |  |  |

| DVR          | TVREG                              | Voltage Regulator Start-up Time         | _   | 10  | _   | μS    | VREGS = 1 with any POR or BOR                                   |  |  |  |  |

| DVR10        | VBG                                | Internal Band Gap Reference             | _   | 1.2 | _   | V     |                                                                 |  |  |  |  |

| DVR11        | TBG                                | Band Gap Reference<br>Start-up Time     | _   | 1   | _   | ms    |                                                                 |  |  |  |  |

| DVR20        | VRGOUT                             | Regulator Output Voltage                | _   | 1.8 | _   | V     | VDD > 1.9V                                                      |  |  |  |  |

| DVR21        | CEFC                               | External Filter Capacitor Value         | 4.7 | 10  | _   | μF    | Series resistance $< 3\Omega$ recommended; $< 5\Omega$ required |  |  |  |  |

| DVR30        | VLVR                               | Low-Voltage Regulator<br>Output Voltage | _   | 1.2 | _   | V     | RETEN = 1, LPCFG = 0                                            |  |  |  |  |

#### TABLE 32-12: HIGH/LOW-VOLTAGE DETECT CHARACTERISTICS

**Operating Conditions:**  $-40^{\circ}C \le TA \le +85^{\circ}C$  for Industrial  $-40^{\circ}C \le TA \le +125^{\circ}C$  for Extended

**Param** Symbol Characteristic Min Тур Max **Units** Conditions No. HLVDL<3:0> = 0100<sup>(1)</sup> DC18 VHLVD HLVD Voltage on VDD 3.45 3.59 3.74 V Transition HLVDL<3:0> = 0101 3.58 ٧ 3.33 3.45 HLVDL<3:0> = 0110 3.0 3.125 3.25 ٧ ٧ HLVDL<3:0> = 0111 2.8 2.92 3.04 HLVDL<3:0> = 1000 2.81 2.93 ٧ 2.7 HLVDL<3:0> = 1001 2.50 2.6 2.70 ٧ ٧ 2.4 2.52 2.64 HLVDL<3:0> = 1010 HLVDL<3:0> = 1011 2.30 2.4 2.50 V ٧ HLVDL<3:0> = 1100 2.20 2.29 2.39 ٧ HLVDL<3:0> = 1101 2.1 2.19 2.28 HLVDL<3:0> = 1110 2.0 2.08 2.17 ٧ DC101 VTHL **HLVD Voltage on** HLVDL<3:0> = 1111 1.2 V **HLVDIN Pin Transition**

**Note 1:** Trip points for values of HLVD<3:0> from '0000' to '0011' are not implemented.

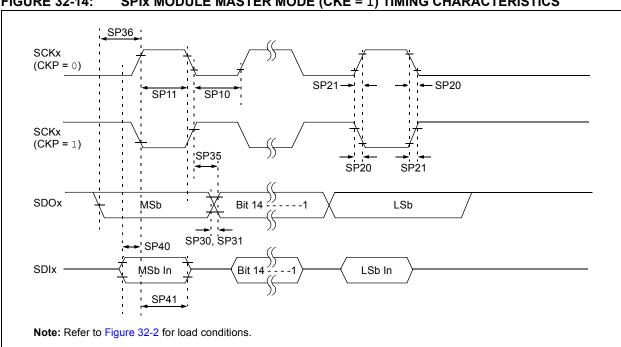

FIGURE 32-14: SPIX MODULE MASTER MODE (CKE = 1) TIMING CHARACTERISTICS

TABLE 32-36: SPIX MODULE MASTER MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHADACTEDISTICS |                       |                                              | Standard Operating Conditions: 2.0V to 3.6V (unless otherwise stated)<br>Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |                    |     |       |                    |  |

|--------------------|-----------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|--------------------|--|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>                | Min                                                                                                                                                                                                                                                 | Typ <sup>(2)</sup> | Max | Units | Conditions         |  |

| SP10               | TscL                  | SCKx Output Low Time(3)                      | Tcy/2                                                                                                                                                                                                                                               | _                  | _   | ns    |                    |  |

| SP11               | TscH                  | SCKx Output High Time(3)                     | Tcy/2                                                                                                                                                                                                                                               | _                  | _   | ns    |                    |  |

| SP20               | TscF                  | SCKx Output Fall Time(4)                     | _                                                                                                                                                                                                                                                   | _                  | _   | ns    | See Parameter DO32 |  |

| SP21               | TscR                  | SCKx Output Rise Time(4)                     | _                                                                                                                                                                                                                                                   | _                  | _   | ns    | See Parameter DO31 |  |

| SP30               | TdoF                  | SDOx Data Output Fall<br>Time <sup>(4)</sup> | _                                                                                                                                                                                                                                                   | _                  | _   | ns    | See Parameter DO32 |  |

| SP31               | TdoR                  | SDOx Data Output Rise<br>Time <sup>(4)</sup> | _                                                                                                                                                                                                                                                   | _                  | _   | ns    | See Parameter DO31 |  |

| SP35               | TscH2doV,<br>TscL2doV | SDOx Data Output Valid After SCKx Edge       | _                                                                                                                                                                                                                                                   | 6                  | 20  | ns    |                    |  |

| SP36               | TdoV2sc,<br>TdoV2scL  | SDOx Data Output Setup to First SCKx Edge    | 30                                                                                                                                                                                                                                                  | _                  | _   | ns    |                    |  |

| SP40               | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge   | 23                                                                                                                                                                                                                                                  | _                  | _   | ns    |                    |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge    | 30                                                                                                                                                                                                                                                  | _                  | _   | ns    |                    |  |

- Note 1: These parameters are characterized but not tested in manufacturing.

- 2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

- 3: The minimum clock period for SCKx is 100 ns. Therefore, the clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPIx pins.

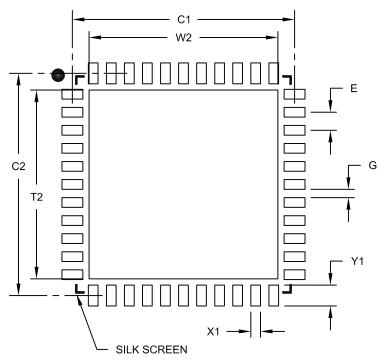

### 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                            | MILLIMETERS |      |          |      |

|----------------------------|-------------|------|----------|------|

| Dimension                  | MIN         | NOM  | MAX      |      |

| Contact Pitch              | Е           |      | 0.65 BSC |      |

| Optional Center Pad Width  | W2          |      |          | 6.60 |

| Optional Center Pad Length | T2          |      |          | 6.60 |

| Contact Pad Spacing        | C1          |      | 8.00     |      |

| Contact Pad Spacing        | C2          |      | 8.00     |      |

| Contact Pad Width (X44)    | X1          |      |          | 0.35 |

| Contact Pad Length (X44)   | Y1          |      |          | 0.85 |

| Distance Between Pads      | G           | 0.25 |          |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2103B

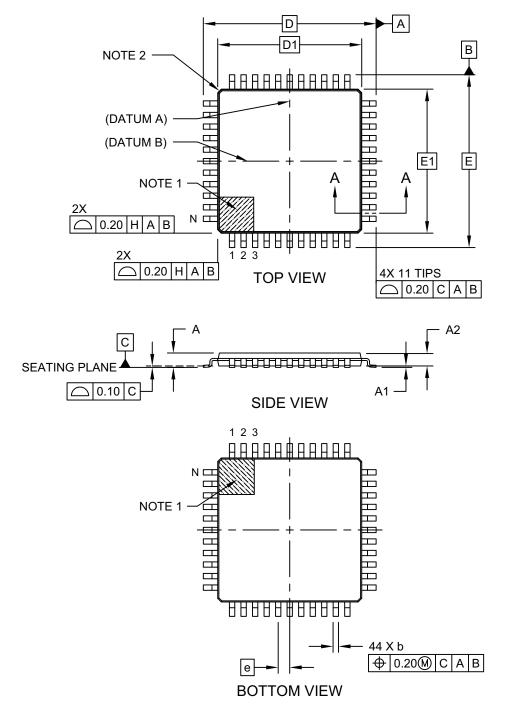

### 44-Lead Plastic Thin Quad Flatpack (PT) - 10x10x1.0 mm Body [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-076C Sheet 1 of 2