Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2014110                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART                    |

| Peripherals                | AES, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, HLVD, POR, PWM, WDT       |

| Number of I/O              | 21                                                                            |

| Program Memory Size        | 64KB (64K x 8)                                                                |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 10x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 28-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 28-QFN-S (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64ga202-i-mm |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT MICROCONTROLLERS

### 2.1 Basic Connection Requirements

Getting started with the PIC24FJ128GA204 family of 16-bit microcontrollers requires attention to a minimal set of device pin connections before proceeding with development.

The following pins must always be connected:

- All VDD and Vss pins (see Section 2.2 "Power Supply Pins")

- All AVDD and AVss pins, regardless of whether or not the analog device features are used (see Section 2.2 "Power Supply Pins")

- MCLR pin

(see Section 2.3 "Master Clear (MCLR) Pin")

- ENVREG/DISVREG and VCAP/VDDCORE pins (see Section 2.4 "Voltage Regulator Pins (ENVREG/DISVREG and VCAP/VDDCORE)")

These pins must also be connected if they are being used in the end application:

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see Section 2.5 "ICSP Pins")

- OSCI and OSCO pins when an external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins used when external voltage reference for analog modules is implemented

**Note:** The AVDD and AVss pins must always be connected, regardless of whether any of the analog modules are being used.

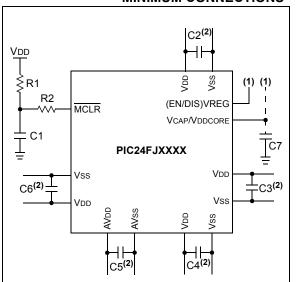

The minimum mandatory connections are shown in Figure 2-1.

### FIGURE 2-1: RECOMMENDED MINIMUM CONNECTIONS

#### Key (all values are recommendations):

C1 through C6: 0.1 µF, 20V ceramic

C7: 10  $\mu\text{F},$  6.3V or greater, tantalum or ceramic

R1: 10 kΩ

R2: 100 $\Omega$  to 470 $\Omega$

- Note 1: See Section 2.4 "Voltage Regulator Pins (ENVREG/DISVREG and VCAP/VDDCORE)" for explanation of the ENVREG/DISVREG pin connections.

- 2: The example shown is for a PIC24F device with five VDD/VSS and AVDD/AVSS pairs. Other devices may have more or less pairs; adjust the number of decoupling capacitors appropriately.

### TABLE 4-10: UART REGISTER MAP

| IABLE 4        | -10: | UARIF             | KEGIS I |          |         |         |        |       |       |              |          |         |           |        |        |        |       | _             |

|----------------|------|-------------------|---------|----------|---------|---------|--------|-------|-------|--------------|----------|---------|-----------|--------|--------|--------|-------|---------------|

| File<br>Name   | Addr | Bit 15            | Bit 14  | Bit 13   | Bit 12  | Bit 11  | Bit 10 | Bit 9 | Bit 8 | Bit 7        | Bit 6    | Bit 5   | Bit 4     | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

| U1MODE         | 0500 | UARTEN            | —       | USIDL    | IREN    | RTSMD   | —      | UEN1  | UEN0  | WAKE         | LPBACK   | ABAUD   | URXINV    | BRGH   | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U1STA          | 0502 | UTXISEL1          | UTXINV  | UTXISEL0 | URXEN   | UTXBRK  | UTXEN  | UTXBF | TRMT  | URXISEL1     | URXISEL0 | ADDEN   | RIDLE     | PERR   | FERR   | OERR   | URXDA | 0110          |

| U1TXREG        | 0504 | LAST              | _       | _        | _       | —       | _      | _     |       |              |          | U1T     | XREG<8:0> | •      |        |        |       | XXXX          |

| U1RXREG        | 0506 | _                 | _       | _        |         | _       | _      |       |       |              |          | U1R     | XREG<8:0> | •      |        |        |       | 0000          |

| U1BRG          | 0508 |                   |         |          |         |         |        |       | U1BRG | <15:0>       |          |         |           |        |        |        |       | 0000          |

| U1ADMD         | 050A | ADMMASK<7:0>      |         |          |         |         |        |       |       |              |          | ADMADDR | R<7:0>    |        |        |        | 0000  |               |

| U1SCCON        | 050C | _                 | _       | _        | _       | _       | _      | _     | _     | _            | _        | TXRPT1  | TXRPT0    | CONV   | T0PD   | PTRCL  | SCEN  | 0000          |

| U1SCINT        | 050E | _                 | _       | RXRPTIF  | TXRPTIF | —       | _      | WTCIF | GTCIF | _            | PARIE    | RXRPTIE | TXRPTIE   | _      | _      | WTCIE  | GTCIE | 0000          |

| U1GTC          | 0510 | _                 | _       | _        | _       | —       | _      | _     |       |              |          | G       | TC<8:0>   |        |        |        |       | 0000          |

| U1WTCL         | 0512 |                   |         |          |         |         |        |       | WTC<  | 15:0>        |          |         |           |        |        |        |       | 0000          |

| U1WTCH         | 0514 | _                 | _       | _        | _       | _       | _      | _     | _     |              |          |         | WTC<23    | :16>   |        |        |       | 0000          |

| U2MODE         | 0516 | UARTEN            | _       | USIDL    | IREN    | RTSMD   | _      | UEN1  | UEN0  | WAKE         | LPBACK   | ABAUD   | URXINV    | BRGH   | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U2STA          | 0518 | UTXISEL1          | UTXINV  | UTXISEL0 | URXEN   | UTXBRK  | UTXEN  | UTXBF | TRMT  | URXISEL1     | URXISEL0 | ADDEN   | RIDLE     | PERR   | FERR   | OERR   | URXDA | 0110          |

| U2TXREG        | 051A | LAST U2TXREG<8:0> |         |          |         |         |        |       | XXXX  |              |          |         |           |        |        |        |       |               |

| U2RXREG        | 051C | U2RXREG<8:0>      |         |          |         |         |        |       | 0000  |              |          |         |           |        |        |        |       |               |

| U2BRG          | 051E |                   |         |          |         |         |        |       | U2BRG | <15:0>       |          |         |           |        |        |        |       | 0000          |

| U2ADMD         | 0520 |                   |         |          | ADMMAS  | SK<7:0> |        |       |       | ADMADDR<7:0> |          |         |           | 0000   |        |        |       |               |

| U2SCCON        | 0522 | —                 | —       | —        | _       | _       |        | _     |       | —            | _        | TXRPT1  | TXRPT0    | CONV   | T0PD   | PTRCL  | SCEN  | 0000          |

| U2SCINT        | 0524 | —                 | —       | RXRPTIF  | TXRPTIF | _       |        | WTCIF | GTCIF | —            | PARIE    | RXRPTIE | TXROTIE   | -      | —      | WTCIE  | GTCIE | 0000          |

| U2GTC          | 0526 | —                 | —       | —        | _       | _       |        | _     |       |              |          | G       | TC<8:0>   |        |        |        |       | 0000          |

| U2WTCL         | 0528 |                   |         |          |         |         |        |       | WTC<  | 15:0>        |          |         |           |        |        |        |       | 0000          |

| U2WTCH         | 052A | —                 | —       | —        | _       | _       |        | _     |       |              |          |         | WTC<23    | :16>   |        |        |       | 0000          |

| U3MODE         | 052C | UARTEN            | —       | USIDL    | IREN    | RTSMD   |        | UEN1  | UEN0  | WAKE         | LPBACK   | ABAUD   | URXINV    | BRGH   | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U3STA          | 052E | UTXISEL1          | UTXINV  | UTXISEL0 | URXEN   | UTXBRK  | UTXEN  | UTXBF | TRMT  | URXISEL1     | URXISEL0 | ADDEN   | RIDLE     | PERR   | FERR   | OERR   | URXDA | 0110          |

| U3TXREG        | 0530 | LAST              | —       | —        | _       | _       |        | _     |       |              |          | U3T2    | XREG<8:0> | •      |        |        |       | XXXX          |

| <b>U3RXREG</b> | 0532 | —                 | —       | —        | _       | _       |        | _     |       |              |          | U3R     | XREG<8:0> | •      |        |        |       | 0000          |

| U3BRG          | 0534 |                   |         |          |         |         |        |       | U3BRG | <15:0>       |          |         |           |        |        |        |       | 0000          |

| U3ADMD         | 0536 |                   |         |          | ADMMAS  | SK<7:0> |        |       |       |              |          |         | ADMADDR   | 8<7:0> |        |        |       | 0000          |

| U4MODE         | 0538 | UARTEN            | —       | USIDL    | IREN    | RTSMD   | —      | UEN1  | UEN0  | WAKE         | LPBACK   | ABAUD   | URXINV    | BRGH   | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U4STA          | 053A | UTXISEL1          | UTXINV  | UTXISEL0 | URXEN   | UTXBRK  | UTXEN  | UTXBF | TRMT  | URXISEL1     | URXISEL0 | ADDEN   | RIDLE     | PERR   | FERR   | OERR   | URXDA | 0110          |

| U4TXREG        | 053C | LAST              | —       | —        | _       | —       | -      | _     |       |              |          | U4T     | XREG<8:0> | •      |        |        |       | XXXX          |

| U4RXREG        | 053E | _                 | —       | —        | —       | —       | -      | _     |       |              |          | U4R     | XREG<8:0> | •      |        |        |       | 0000          |

| U4BRG          | 0540 |                   |         |          |         |         |        |       | U4BRG | <15:0>       |          |         |           |        |        |        |       | 0000          |

| U4ADMD         | 0542 |                   |         |          | ADMMAS  | SK<7:0> |        |       |       |              |          |         | ADMADDR   | R<7:0> |        |        |       | 0000          |

|                |      |                   |         |          |         |         |        |       |       |              |          |         |           |        |        |        |       |               |

**Legend:** — = unimplemented, read as '0'; x = unknown value on Reset. Reset values are shown in hexadecimal.

# PIC24FJ128GA204 FAMILY

### REGISTER 8-2: CORCON: CPU CORE CONTROL REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | —   | —   | _   | —   | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

|        |     |     |     |     |     |     |       |

| U-0   | U-0 | U-0 | U-0 | R/C-0               | r-1 | U-0 | U-0   |

|-------|-----|-----|-----|---------------------|-----|-----|-------|

| —     | —   | —   | —   | IPL3 <sup>(1)</sup> | —   | —   | —     |

| bit 7 |     |     |     |                     |     |     | bit 0 |

| Legend:           | r = Reserved bit | C = Clearable bit      |                                    |  |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |  |

bit 15-4 Unimplemented: Read as '0'

bit 3 IPL3: CPU Interrupt Priority Level Status bit<sup>(1)</sup> 1 = CPU Interrupt Priority Level is greater than 7 0 = CPU Interrupt Priority Level is 7 or less

bit 2 Reserved: Read as PSV bit

bit 1-0 Unimplemented: Read as '0'

**Note 1:** The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level; see Register 3-2 for bit description.

### REGISTER 9-6: REFOTRIML: REFERENCE OSCILLATOR TRIM REGISTER

| R/W-0         | R/W-0                   | R/W-0                                | R/W-0           | R/W-0             | R/W-0           | R/W-0              | R/W-0 |  |

|---------------|-------------------------|--------------------------------------|-----------------|-------------------|-----------------|--------------------|-------|--|

|               |                         |                                      | ROTR            | M<15:8>           |                 |                    |       |  |

| bit 15        |                         |                                      |                 |                   |                 |                    | bit 8 |  |

|               |                         |                                      |                 |                   |                 |                    |       |  |

| R/W-0         | U-0                     | U-0                                  | U-0             | U-0               | U-0             | U-0                | U-0   |  |

| ROTRIM7       |                         | —                                    |                 | —                 | —               | _                  | _     |  |

| bit 7         |                         |                                      |                 |                   |                 | ·                  | bit 0 |  |

|               |                         |                                      |                 |                   |                 |                    |       |  |

| Legend:       |                         |                                      |                 |                   |                 |                    |       |  |

| R = Readable  | e bit                   | W = Writable t                       | bit             | U = Unimplen      | nented bit, rea | d as '0'           |       |  |

| -n = Value at | POR                     | '1' = Bit is set                     |                 | '0' = Bit is clea | ared            | x = Bit is unknown |       |  |

|               |                         |                                      |                 |                   |                 |                    |       |  |

| bit 15-7      | ROTRIM<15               | :7>: Reference (                     | Oscillator Trin | n bits            |                 |                    |       |  |

|               | Provides frac           | ctional additive to                  | the RODIVx      | value for the 1/  | 2 period of the | REFO clock.        |       |  |

|               |                         | = 511/512 (0.998                     |                 |                   | •               |                    |       |  |

|               | 111111110               | = 510/512 (0.99                      | 609375) divis   | or added to RO    | DIVx value      |                    |       |  |

|               | •                       |                                      |                 |                   |                 |                    |       |  |

|               | •                       |                                      |                 |                   |                 |                    |       |  |

|               | •                       |                                      |                 |                   |                 |                    |       |  |

|               | 100000000               | = 256/512 (0.50                      | 00) divisor ad  | ded to RODIVx     | value           |                    |       |  |

|               | •                       |                                      |                 |                   |                 |                    |       |  |

|               | •                       |                                      |                 |                   |                 |                    |       |  |

|               | •                       |                                      |                 |                   |                 |                    |       |  |

|               | 000000010               | = 2/512 (0.0039                      | 0625) divisor   | added to RODI     | Vx value        |                    |       |  |

|               |                         | = 1/512 (0.0019<br>= 0/512 (0.0) div |                 |                   | IVx value       |                    |       |  |

| bit 6-0       | Unimpleme               | nted: Read as '0                     | ,               |                   |                 |                    |       |  |

|               | ommplemented. Read as 0 |                                      |                 |                   |                 |                    |       |  |

# PIC24FJ128GA204 FAMILY

### REGISTER 11-16: RPINR22: PERIPHERAL PIN SELECT INPUT REGISTER 22

| U-0    | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----|--------|--------|--------|--------|--------|--------|

| —      | —   | SCK2R5 | SCK2R4 | SCK2R3 | SCK2R2 | SCK2R1 | SCK2R0 |

| bit 15 |     |        |        |        |        |        | bit 8  |

|        |     |        |        |        |        |        |        |

| U-0   | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | SDI2R5 | SDI2R4 | SDI2R3 | SDI2R2 | SDI2R1 | SDI2R0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

| bit 15-14 | Unimplemented: Read as '0'                                                         |

|-----------|------------------------------------------------------------------------------------|

| bit 13-8  | SCK2R<5:0>: Assign SPI2 Clock Input (SCK2IN) to Corresponding RPn or RPIn Pin bits |

| bit 7-6   | Unimplemented: Read as '0'                                                         |

| bit 5-0   | SDI2R<5:0>: Assign SPI2 Data Input (SDI2) to Corresponding RPn or RPIn Pin bits    |

### REGISTER 11-17: RPINR23: PERIPHERAL PIN SELECT INPUT REGISTER 23

| U-0    | U-0 | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   |

|--------|-----|---------|---------|---------|---------|---------|---------|

| —      | —   | TMRCKR5 | TMRCKR4 | TMRCKR3 | TMRCKR2 | TMRCKR1 | TMRCKR0 |

| bit 15 |     |         |         |         |         |         | bit 8   |

| U-0   | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     | —   | SS2R5 | SS2R4 | SS2R3 | SS2R2 | SS2R1 | SS2R0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-14 Unimplemented: Read as '0'

bit 13-8 TMRCKR<5:0>: Assign General Timer External Input (TMRCK) to Corresponding RPn or RPIn Pin bits

bit 7-6 Unimplemented: Read as '0'

bit 5-0 SS2R<5:0>: Assign SPI2 Slave Select Input (SS2IN) to Corresponding RPn or RPIn Pin bits

### 15.3.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the OCxRS and OCxR registers. The OCxRS and OCxR registers can be written to at any time, but the duty cycle value is not latched until a match between PRy and TMRy occurs (i.e., the period is complete). This provides a double buffer for the PWM duty cycle and is essential for glitchless PWM operation.

Some important boundary parameters of the PWM duty cycle include:

- If OCxR, OCxRS and PRy are all loaded with 0000h, the OCx pin will remain low (0% duty cycle).

- If OCxRS is greater than PRy, the pin will remain high (100% duty cycle).

See Example 15-1 for PWM mode timing details. Table 15-1 and Table 15-2 show example PWM frequencies and resolutions for a device operating at 4 MIPS and 10 MIPS, respectively.

### EQUATION 15-2: CALCULATION FOR MAXIMUM PWM RESOLUTION<sup>(1)</sup>

$$Maximum PWM Resolution (bits) = \frac{\log_{10} \left(\frac{FCY}{FPWM \bullet (Timer Prescale Value)}\right)}{\log_{10}} bits$$

**Note 1:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

### EXAMPLE 15-1: PWM PERIOD AND DUTY CYCLE CALCULATIONS<sup>(1)</sup>

| Find the Timer Period register value for a desired PWM frequency of 52.08 kHz, where Fosc = 8 MHz with PLL (32 MHz device clock rate) and a Timer2 prescaler setting of 1:1. |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                              |

| TCY = 2 * TOSC = 62.5  ns                                                                                                                                                    |

| PWM Period = $1/PWM$ Frequency = $1/52.08$ kHz = $19.2$ ms                                                                                                                   |

| PWM Period = $(PR2 + 1) \cdot TCY \cdot (Timer2 Prescale Value)$                                                                                                             |

| $19.2 \ \mu s = (PR2 + 1) \cdot 62.5 \ ns \cdot 1$                                                                                                                           |

| PR2 = 306                                                                                                                                                                    |

| Find the maximum resolution of the duty cycle that can be used with a 52.08 kHz frequency and a 32 MHz device clock rate:                                                    |

| PWM Resolution = $\log_{10}(FCY/FPWM)/\log_{10}2)$ bits                                                                                                                      |

| = $(\log_{10}(16 \text{ MHz}/52.08 \text{ kHz})/\log_{10}2)$ bits                                                                                                            |

| = 8.3 bits                                                                                                                                                                   |

|                                                                                                                                                                              |

| TABLE 15-1: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 4 MIPS (Fcy = 4 MHz) <sup>(1</sup> | <b>TABLE 15-1</b> : | EXAMPLE PWM FREQUENCIES | AND RESOLUTIONS AT 4 MIPS | $(FCY = 4 MHz)^{(1)}$ |

|-------------------------------------------------------------------------------------------|---------------------|-------------------------|---------------------------|-----------------------|

|-------------------------------------------------------------------------------------------|---------------------|-------------------------|---------------------------|-----------------------|

| PWM Frequency         | 7.6 Hz | 61 Hz | 122 Hz | 977 Hz | 3.9 kHz | 31.3 kHz | 125 kHz |

|-----------------------|--------|-------|--------|--------|---------|----------|---------|

| Timer Prescaler Ratio | 8      | 1     | 1      | 1      | 1       | 1        | 1       |

| Period Register Value | FFFFh  | FFFFh | 7FFFh  | 0FFFh  | 03FFh   | 007Fh    | 001Fh   |

| Resolution (bits)     | 16     | 16    | 15     | 12     | 10      | 7        | 5       |

**Note 1:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

### TABLE 15-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 16 MIPS (Fcy = 16 MHz)<sup>(1)</sup>

| PWM Frequency         | 30.5 Hz | 244 Hz | 488 Hz | 3.9 kHz | 15.6 kHz | 125 kHz | 500 kHz |

|-----------------------|---------|--------|--------|---------|----------|---------|---------|

| Timer Prescaler Ratio | 8       | 1      | 1      | 1       | 1        | 1       | 1       |

| Period Register Value | FFFFh   | FFFFh  | 7FFFh  | 0FFFh   | 03FFh    | 007Fh   | 001Fh   |

| Resolution (bits)     | 16      | 16     | 15     | 12      | 10       | 7       | 5       |

**Note 1:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

<sup>© 2013-2015</sup> Microchip Technology Inc.

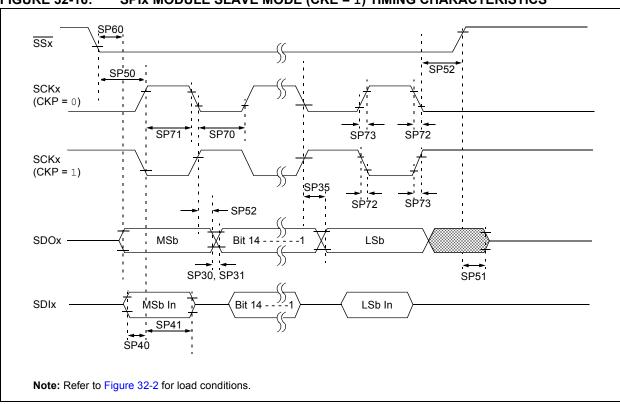

### 16.0 SERIAL PERIPHERAL INTERFACE (SPI)

Note: This data sheet summarizes the features of the PIC24FJ128GA204 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33/PIC24 Family Reference Manual", "Serial Peripheral Interface (SPI) with Audio Codec Support" (DS70005136) which is available from the Microchip web site (www.microchip.com).

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, A/D Converters, etc. The SPI module is compatible with the Motorola<sup>®</sup> SPI and SIOP interfaces. All devices in the PIC24FJ128GA204 family include three SPI modules.

The module supports operation in two buffer modes. In Standard Buffer mode, data is shifted through a single serial buffer. In Enhanced Buffer mode, data is shifted through a FIFO buffer. The FIFO level depends on the configured mode.

Variable length data can be transmitted and received, from 2 to 32-bits.

| Note: | Do not perform Read-Modify-Write opera-      |

|-------|----------------------------------------------|

|       | tions (such as bit-oriented instructions) on |

|       | the SPIxBUF register in either Standard or   |

|       | Enhanced Buffer mode.                        |

The module also supports a basic framed SPI protocol while operating in either Master or Slave mode. A total of four framed SPI configurations are supported.

The module also supports Audio modes. Four different Audio modes are available.

- I<sup>2</sup>S mode

- · Left Justified

- Right Justified

- PCM/DSP

In each of these modes, the serial clock is free-running and audio data is always transferred.

If an audio protocol data transfer takes place between two devices, then usually one device is the master and the other is the slave. However, audio data can be transferred between two slaves. Because the audio protocols require free-running clocks, the master can be a third party controller. In either case, the master generates two free-running clocks: SCKx and LRC (Left, Right Channel Clock/SSx/FSYNC). The SPI serial interface consists of four pins:

- SDIx: Serial Data Input

- SDOx: Serial Data Output

- SCKx: Shift Clock Input or Output

- SSx: Active-Low Slave Select or Frame Synchronization I/O Pulse

The SPI module can be configured to operate using 2, 3 or 4 pins. In the 3-pin mode,  $\overline{SSx}$  is not used. In the 2-pin mode, both SDOx and  $\overline{SSx}$  are not used.

The SPI module has the ability to generate three interrupts, reflecting the events that occur during the data communication. The following types of interrupts can be generated:

- 1. Receive interrupts are signalled by SPIxRXIF. This event occurs when:

- RX watermark interrupt

- SPIROV = 1

- SPIRBF = 1

- **SPIRBE =** 1

provided the respective mask bits are enabled in SPIxIMSKL/H.

- 2. Transmit interrupts are signalled by SPIxTXIF. This event occurs when:

- TX watermark interrupt

- SPITUR = 1

- SPITBF = 1

- SPITBE = 1

provided the respective mask bits are enabled in SPIxIMSKL/H.

- 3. General interrupts are signalled by SPIxIF. This event occurs when

- FRMERR = 1

- SPIBUSY = 1

- SRMT = 1

provided the respective mask bits are enabled in SPIxIMSKL/H.

Block diagrams of the module in Standard and Enhanced modes are shown in Figure 16-1 and Figure 16-2.

Note: In this section, the SPI modules are referred to together as SPIx, or separately as SPI1, SPI2 or SPI3. Special Function Registers will follow a similar notation. For example, SPIxCON1L and SPIxCON1H refer to the control registers for any of the three SPI modules.

### 17.2 Setting Baud Rate when Operating as a Bus Master

To compute the Baud Rate Generator reload value, use Equation 17-1.

### EQUATION 17-1: COMPUTING BAUD RATE RELOAD VALUE<sup>(1)</sup>

$$I2CxBRG = \left( \left( \frac{1}{FSCL} - PGDx \right) \times \frac{FCY}{2} \right) - 2$$

**Note 1:** Based on FCY = FOSC/2; Doze mode and PLL are disabled.

### 17.3 Slave Address Masking

The I2CxMSK register (Register 17-4) designates address bit positions as "don't care" for both 7-Bit and 10-Bit Addressing modes. Setting a particular bit location (= 1) in the I2CxMSK register causes the slave module to respond, whether the corresponding address bit value is a '0' or a '1'. For example, when I2CxMSK is set to '0010000000', the slave module will detect both addresses, '000000000' and '001000000'.

To enable address masking, the Intelligent Peripheral Management Interface (IPMI) must be disabled by clearing the STRICT bit (I2CxCONL<11>).

Note: As a result of changes in the I<sup>2</sup>C<sup>™</sup> protocol, the addresses in Table 17-1 are reserved and will not be Acknowledged in Slave mode. This includes any address mask settings that include any of these addresses.

| Slave Address | R/W Bit | Description                            |

|---------------|---------|----------------------------------------|

| 000 000       | 0       | General Call Address <sup>(2)</sup>    |

| 0000 000      | 1       | Start Byte                             |

| 0000 001      | х       | Cbus Address                           |

| 0000 01x      | х       | Reserved                               |

| 0000 1xx      | Х       | HS Mode Master Code                    |

| 1111 0xx      | х       | 10-Bit Slave Upper Byte <sup>(3)</sup> |

| 1111 1xx      | Х       | Reserved                               |

Note 1: The address bits listed here will never cause an address match independent of address mask settings.

2: This address will be Acknowledged only if GCEN = 1.

3: A match on this address can only occur on the upper byte in 10-Bit Addressing mode.

### PIC24FJ128GA204 FAMILY

| U-0                               | R/W-x                                                               | R/W-x            | R/W-x          | R/W-x             | R/W-x            | R/W-x              | R/W-x   |  |  |  |  |  |  |  |  |  |

|-----------------------------------|---------------------------------------------------------------------|------------------|----------------|-------------------|------------------|--------------------|---------|--|--|--|--|--|--|--|--|--|

| _                                 | MINTEN2                                                             | MINTEN1          | MINTEN0        | MINONE3           | MINONE2          | MINONE1            | MINONE0 |  |  |  |  |  |  |  |  |  |

| bit 15                            |                                                                     | •                |                |                   |                  |                    | bit 8   |  |  |  |  |  |  |  |  |  |

|                                   |                                                                     |                  |                |                   |                  |                    |         |  |  |  |  |  |  |  |  |  |

| U-0                               | R/W-x                                                               | R/W-x            | R/W-x          | R/W-x             | R/W-x            | R/W-x              | R/W-x   |  |  |  |  |  |  |  |  |  |

| —                                 | SECTEN2 SECTEN1 SECT                                                |                  | SECTEN0        | SECONE3           | SECONE2          | SECONE1            | SECONE0 |  |  |  |  |  |  |  |  |  |

| bit 7                             |                                                                     |                  |                |                   | bit 0            |                    |         |  |  |  |  |  |  |  |  |  |

|                                   |                                                                     |                  |                |                   |                  |                    |         |  |  |  |  |  |  |  |  |  |

| Legend:                           |                                                                     |                  |                |                   |                  |                    |         |  |  |  |  |  |  |  |  |  |

| R = Readabl                       | e bit                                                               | W = Writable bit |                | U = Unimplem      | nented bit, read | l as '0'           |         |  |  |  |  |  |  |  |  |  |

| -n = Value at POR '1' = Bit is se |                                                                     |                  |                | '0' = Bit is clea | ared             | x = Bit is unknown |         |  |  |  |  |  |  |  |  |  |

|                                   |                                                                     |                  |                |                   |                  |                    |         |  |  |  |  |  |  |  |  |  |

| bit 15                            | Unimplement                                                         | ed: Read as '0'  |                |                   |                  |                    |         |  |  |  |  |  |  |  |  |  |

| bit 14-12                         | MINTEN<2:0                                                          | Binary Code      | d Decimal Valu | ue of Minute's T  | ens Digit bits   |                    |         |  |  |  |  |  |  |  |  |  |

|                                   | Contains a va                                                       | lue from 0 to 5  |                |                   |                  |                    |         |  |  |  |  |  |  |  |  |  |

| bit 11-8                          | MINONE<3:0                                                          | >: Binary Code   | d Decimal Val  | ue of Minute's (  | Ones Digit bits  |                    |         |  |  |  |  |  |  |  |  |  |

|                                   | Contains a va                                                       | lue from 0 to 9  |                |                   |                  |                    |         |  |  |  |  |  |  |  |  |  |

| bit 7                             | Unimplemen                                                          | ted: Read as '   | )'             |                   |                  |                    |         |  |  |  |  |  |  |  |  |  |

| bit 6-4                           | SECTEN<2:0>: Binary Coded Decimal Value of Second's Tens Digit bits |                  |                |                   |                  |                    |         |  |  |  |  |  |  |  |  |  |

|                                   | Contains a va                                                       | lue from 0 to 5  |                |                   |                  |                    |         |  |  |  |  |  |  |  |  |  |

| bit 3-0                           | SECONE<3:0                                                          | >: Binary Code   | ed Decimal Val | lue of Second's   | Ones Digit bits  | 6                  |         |  |  |  |  |  |  |  |  |  |

|                                   | Contains a va                                                       | lue from 0 to 9  |                |                   |                  |                    |         |  |  |  |  |  |  |  |  |  |

|                                   |                                                                     |                  |                |                   |                  |                    |         |  |  |  |  |  |  |  |  |  |

### REGISTER 21-10: ALMINSEC: ALARM MINUTES AND SECONDS VALUE REGISTER

| Alarm Mask Setting<br>(AMASK<3:0>)              | Day of<br>the<br>Week | Month          | Day | Hours | Minutes | Seconds |

|-------------------------------------------------|-----------------------|----------------|-----|-------|---------|---------|

| 0000 - Every half second<br>0001 - Every second |                       |                |     |       |         | :       |

| 0010 - Every 10 seconds                         |                       |                |     |       |         | s       |

| 0011 - Every minute                             |                       |                |     |       |         | s s     |

| 0100 - Every 10 minutes                         |                       |                |     |       | m       | s s     |

| 0101 - Every hour                               |                       |                |     |       | mm      | s s     |

| 0110 - Every day                                |                       |                |     | h h   | mm      | ss      |

| 0111 - Every week                               | d                     |                |     | h h   | mm      | ss      |

| 1000 - Every month                              |                       |                | d d | h h   | mm      | ss      |

| 1001 - Every year <sup>(1)</sup>                |                       | <b>m m</b> /   | d d | h h   | mm      | ss      |

| Note 1: Annually, except wh                     | en configured fo      | r February 29. |     |       |         |         |

### 21.6 Power Control

The RTCC includes a power control feature that allows the device to periodically wake-up an external device, wait for the device to be stable before sampling wake-up events from that device and then shut down the external device. This can be done completely autonomously by the RTCC, without the need to wake from the current lower power mode (Sleep, Deep Sleep, etc.).

To use this feature:

- 1. Enable the RTCC (RTCEN = 1).

- 2. Set the PWCEN bit (RTCPWC<15>).

- 3. Configure the RTCC pin to drive the PWC control signal (RTCOE = 1 and RTCOUT<1:0> = 11).

The polarity of the PWC control signal may be chosen using the PWCPOL bit (RTCPWC<14>). An active-low or active-high signal may be used with the appropriate

external switch to turn on or off the power to one or more external devices. The active-low setting may also be used in conjunction with an open-drain setting on the RTCC pin, in order to drive the ground pin(s) of the external device directly (with the appropriate external VDD pull-up device), without the need for external switches. Finally, the CHIME bit should be set to enable the PWC periodicity.

### 21.7 RTCC VBAT Operation

The RTCC can operate in VBAT mode when there is a power loss on the VDD pin. The RTCC will continue to operate if the VBAT pin is powered on (it is usually connected to the battery).

Note: It is recommended to connect the VBAT pin to VDD if the VBAT mode is not used (not connected to the battery).

### REGISTER 22-5: CFGPAGE: SECURE ARRAY CONFIGURATION BITS (OTP PAGE 0) REGISTER (CONTINUED)

| bit 19    | SKEYEN: Session Key Enable bit                                                                                                                                                                                                                                                         |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | <ul> <li>1 = Stored Key #1 may be used only as a Key Encryption Key</li> <li>0 = Stored Key #1 may be used for any operation</li> </ul>                                                                                                                                                |

| bit 18-11 | LKYSRC<7:0>: Locked Key Source Configuration bits                                                                                                                                                                                                                                      |

|           | If SRCLCK = 1:                                                                                                                                                                                                                                                                         |

|           | 1xxxxxxx = Key Source is as if KEYSRC<3:0> = 1111                                                                                                                                                                                                                                      |

|           | 01xxxxxx = Key Source is as if KEYSRC<3:0> = 0111                                                                                                                                                                                                                                      |

|           | 001xxxxx = Key Source is as if KEYSRC<3:0> = 0110                                                                                                                                                                                                                                      |

|           | 0001xxxx = Key Source is as if KEYSRC<3:0> = 0101                                                                                                                                                                                                                                      |

|           | 00001xxx = Key Source is as if KEYSRC<3:0> = 0100                                                                                                                                                                                                                                      |

|           | 000001xx = Key Source is as if KEYSRC<3:0> = 0011                                                                                                                                                                                                                                      |

|           | 0000001x = Key Source is as if KEYSRC<3:0> = 0010                                                                                                                                                                                                                                      |

|           | 00000001 = Key Source is as if KEYSRC<3:0> = 0001                                                                                                                                                                                                                                      |

|           | 0000000 = Key Source is as if KEYSRC<3:0> = 0000                                                                                                                                                                                                                                       |

|           | If SRCLCK = 0:                                                                                                                                                                                                                                                                         |

|           | These bits are ignored.                                                                                                                                                                                                                                                                |

| bit 10    | SRCLCK: Key Source Lock bit                                                                                                                                                                                                                                                            |

|           | 1 = The key source is determined by the KEYSRC<3:0> (CRYCONH<3:0>) bits (software key selection<br>is disabled)                                                                                                                                                                        |

|           | <ul> <li>The key source is determined by the KEYSRC&lt;3:0&gt; (CRYCONH&lt;3:0&gt;) bits (locked key selection<br/>is disabled)</li> </ul>                                                                                                                                             |

| bit 9-1   | WRLOCK<8:0>: Write Lock Page Enable bits                                                                                                                                                                                                                                               |

|           | For OTP Pages 0 (CFGPAGE) through 8:                                                                                                                                                                                                                                                   |

|           | 1 = OTP Page is permanently locked and may not be programmed                                                                                                                                                                                                                           |

|           | 0 = OTP Page is unlocked and may be programmed                                                                                                                                                                                                                                         |

| bit 0     | SWKYDIS: Software Key Disable bit                                                                                                                                                                                                                                                      |

|           | <ul> <li>1 = Software key (CRYKEY register) is disabled; when KEYSRC&lt;3:0&gt; = 0000, the KEYFAIL status bit<br/>will be set and no encryption/decryption/session key operations can be started until KEYSRC&lt;3:0&gt;<br/>bits are changed to a value other than '0000'</li> </ul> |

|           | 0 = Software key (CRYKEY register) can be used as a key source when KEYSRC<3:0> = 0000                                                                                                                                                                                                 |

**Note 1:** This bit's state is mirrored by the PGMTST bit (CRYOTP<7>).

| R/W-0         | U-0                                                                                                                              | R/W-0             | R/W-0                          | R/W-0            | R/W-0            | R/W-0              | R/W-0        |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------------------|------------------|------------------|--------------------|--------------|--|--|--|

| ADON          | —                                                                                                                                | ADSIDL            | DMABM <sup>(1)</sup>           | DMAEN            | MODE12           | FORM1              | FORM0        |  |  |  |

| bit 15        |                                                                                                                                  |                   |                                |                  |                  |                    | bit 8        |  |  |  |

|               |                                                                                                                                  | <b>D</b> 444 A    |                                |                  |                  |                    |              |  |  |  |

| R/W-0         | R/W-0                                                                                                                            | R/W-0             | R/W-0                          | U-0              | R/W-0            | R/W-0, HSC         | R/C-0, HSC   |  |  |  |

| SSRC3         | SSRC2                                                                                                                            | SSRC1             | SSRC0                          | —                | ASAM             | SAMP               | DONE         |  |  |  |

| bit 7         |                                                                                                                                  |                   |                                |                  |                  |                    | bit (        |  |  |  |

| Legend:       |                                                                                                                                  | C = Clearable     | e bit                          | U = Unimpler     | nented bit, rea  | d as 'O'           |              |  |  |  |

| R = Readabl   | e bit                                                                                                                            | W = Writable      | bit                            | HSC = Hardv      | vare Settable/C  | learable bit       |              |  |  |  |

| -n = Value at | POR                                                                                                                              | '1' = Bit is set  | t                              | '0' = Bit is cle | ared             | x = Bit is unkn    | own          |  |  |  |

|               |                                                                                                                                  |                   |                                |                  |                  |                    |              |  |  |  |

| bit 15        |                                                                                                                                  | Operating Mode    |                                |                  |                  |                    |              |  |  |  |

|               | 1 = A/D Con<br>0 = A/D Con                                                                                                       | verter module is  | soperating                     |                  |                  |                    |              |  |  |  |

| bit 14        |                                                                                                                                  | nted: Read as '   | 0'                             |                  |                  |                    |              |  |  |  |

| bit 13        | -                                                                                                                                | D Stop in Idle M  |                                |                  |                  |                    |              |  |  |  |

|               |                                                                                                                                  | •                 | eration when d                 | evice enters Id  | lle mode         |                    |              |  |  |  |

|               |                                                                                                                                  | -                 | ation in Idle mo               |                  |                  |                    |              |  |  |  |

| bit 12        |                                                                                                                                  |                   | uffer Mode Sele                |                  |                  |                    |              |  |  |  |

|               |                                                                                                                                  | ne DMADSTn r      | egister<br>AD1CON4<2:0         |                  |                  |                    |              |  |  |  |

| bit 11        |                                                                                                                                  | tended DMA/Bu     |                                |                  |                  | AD100N4~2.0        |              |  |  |  |

|               | 1 = Extended DMA and buffer features are enabled                                                                                 |                   |                                |                  |                  |                    |              |  |  |  |

|               | 0 = Extended                                                                                                                     | d features are d  | lisabled                       |                  |                  |                    |              |  |  |  |

| bit 10        | MODE12: 12                                                                                                                       | 2-Bit Operation   | Mode bit                       |                  |                  |                    |              |  |  |  |

|               | 1 = 12-bit A/I                                                                                                                   |                   |                                |                  |                  |                    |              |  |  |  |

| bit 9-8       | 0 = 10-bit A/l                                                                                                                   | -                 | ormat bits (see                | formats follow   | (ina)            |                    |              |  |  |  |

| Dit 9-0       |                                                                                                                                  | nal result, signe | -                              |                  | ing)             |                    |              |  |  |  |

|               |                                                                                                                                  | •                 | ult, unsigned, le              | eft justified    |                  |                    |              |  |  |  |

|               |                                                                                                                                  | I result, signed  |                                |                  |                  |                    |              |  |  |  |

| bit 7 4       |                                                                                                                                  |                   | t, unsigned, rig               | •                |                  |                    |              |  |  |  |

| bit 7-4       |                                                                                                                                  | nplemented, do    | Source Select                  | DIIS             |                  |                    |              |  |  |  |

|               |                                                                                                                                  |                   |                                | tarts conversio  | n (auto-convert) | ; do not use in Aı | uto-Scan mod |  |  |  |

|               | 0111 = Internal counter ends sampling and starts conversion (auto-convert); do not use in Auto-Scan mode<br>0110 = Unimplemented |                   |                                |                  |                  |                    |              |  |  |  |

|               | 0101 = TMR1                                                                                                                      |                   |                                |                  |                  |                    |              |  |  |  |

|               | 0100 = CTMU<br>0011 = TMR5                                                                                                       |                   |                                |                  |                  |                    |              |  |  |  |

|               | 0010 = TMR                                                                                                                       |                   |                                |                  |                  |                    |              |  |  |  |

|               | 0001 = INTC                                                                                                                      |                   | he cleared by                  | offwara ta ata   | rt conversion    |                    |              |  |  |  |

| bit 3         |                                                                                                                                  | nted: Read as '   | be cleared by s                | soltware to sta  | rt conversion    |                    |              |  |  |  |

| bit 2         | -                                                                                                                                | Sample Auto-Si    |                                |                  |                  |                    |              |  |  |  |

|               |                                                                                                                                  | -                 | lart bit<br>liately after last | conversion: SA   | AMP bit is auto  | -set               |              |  |  |  |

|               |                                                                                                                                  |                   | SAMP bit is mai                |                  |                  |                    |              |  |  |  |

|               |                                                                                                                                  | vailable when F   |                                |                  |                  |                    |              |  |  |  |

### REGISTER 24-1: AD1CON1: A/D CONTROL REGISTER 1

Note 1: This bit is only available when Extended DMA/Buffer features are available (DMAEN = 1).

### REGISTER 24-1: AD1CON1: A/D CONTROL REGISTER 1 (CONTINUED)

- bit 1 SAMP: A/D Sample Enable bit 1 = A/D Sample-and-Hold amplifiers are sampling 0 = A/D Sample-and-Hold amplifiers are holding

- bit 0 **DONE:** A/D Conversion Status bit 1 = A/D conversion cycle has completed

- 0 = A/D conversion cycle has not started or is in progress

- Note 1: This bit is only available when Extended DMA/Buffer features are available (DMAEN = 1).

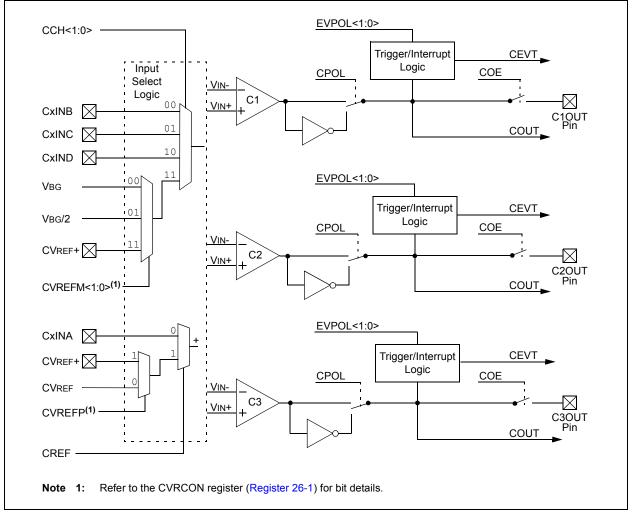

### 25.0 TRIPLE COMPARATOR MODULE

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information, refer to the "dsPIC33/PIC24 Family Reference Manual", "Scalable Comparator Module" (DS39734). The information in this data sheet supersedes the information in the FRM.

The triple comparator module provides three dual input comparators. The inputs to the comparator can be configured to use any one of five external analog inputs (CxINA, CxINB, CxINC, CxIND and VREF+) and a

voltage reference input from one of the internal band gap references or the comparator voltage reference generator (VBG, VBG/2 and CVREF).

The comparator outputs may be directly connected to the CxOUT pins. When the respective COE bit equals '1', the I/O pad logic makes the unsynchronized output of the comparator available on the pin.

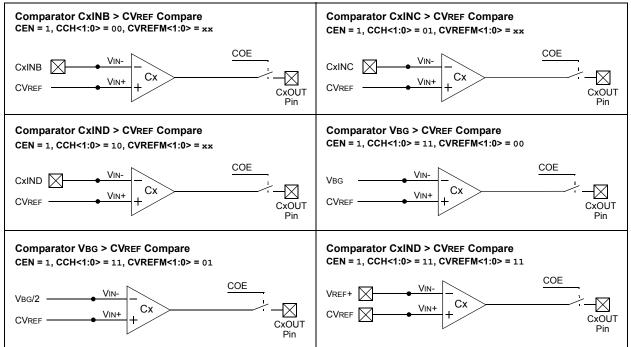

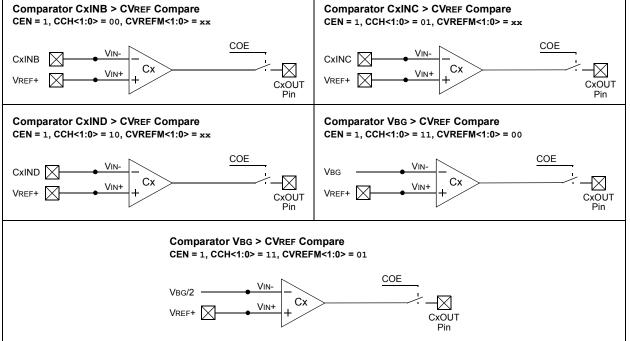

A simplified block diagram of the module in shown in Figure 25-1. Diagrams of the possible individual comparator configurations are shown in Figure 25-2.

Each comparator has its own control register, CMxCON (Register 25-1), for enabling and configuring its operation. The output and event status of all three comparators is provided in the CMSTAT register (Register 25-2).

### FIGURE 25-1: TRIPLE COMPARATOR MODULE BLOCK DIAGRAM

### FIGURE 25-3: INDIVIDUAL COMPARATOR CONFIGURATIONS WHEN CREF = 1 AND CVREFP = 0

### PIC24FJ128GA204 FAMILY

| Assembly<br>Mnemonic | Assembly Syntax |          | Description                                 | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|----------------------|-----------------|----------|---------------------------------------------|---------------|----------------|--------------------------|

| BTSS                 | BTSS            | f,#bit4  | Bit Test f, Skip if Set                     | 1             | 1<br>(2 or 3)  | None                     |

|                      | BTSS            | Ws,#bit4 | Bit Test Ws, Skip if Set                    | 1             | 1<br>(2 or 3)  | None                     |

| BTST                 | BTST            | f,#bit4  | Bit Test f                                  | 1             | 1              | Z                        |

|                      | BTST.C          | Ws,#bit4 | Bit Test Ws to C                            | 1             | 1              | С                        |

|                      | BTST.Z          | Ws,#bit4 | Bit Test Ws to Z                            | 1             | 1              | Z                        |

|                      | BTST.C          | Ws,Wb    | Bit Test Ws <wb> to C</wb>                  | 1             | 1              | С                        |

|                      | BTST.Z          | Ws,Wb    | Bit Test Ws <wb> to Z</wb>                  | 1             | 1              | Z                        |

| BTSTS                | BTSTS           | f,#bit4  | Bit Test then Set f                         | 1             | 1              | Z                        |

|                      | BTSTS.C         | Ws,#bit4 | Bit Test Ws to C, then Set                  | 1             | 1              | С                        |

|                      | BTSTS.Z         | Ws,#bit4 | Bit Test Ws to Z, then Set                  | 1             | 1              | Z                        |

| CALL                 | CALL            | lit23    | Call Subroutine                             | 2             | 2              | None                     |

|                      | CALL            | Wn       | Call Indirect Subroutine                    | 1             | 2              | None                     |

| CLR                  | CLR             | f        | f = 0x0000                                  | 1             | 1              | None                     |

|                      | CLR             | WREG     | WREG = 0x0000                               | 1             | 1              | None                     |

|                      | CLR             | Ws       | Ws = 0x0000                                 | 1             | 1              | None                     |

| CLRWDT               | CLRWDT          |          | Clear Watchdog Timer                        | 1             | 1              | WDTO, Sleep              |

| COM                  | COM             | f        | f = f                                       | 1             | 1              | N, Z                     |

|                      | COM             | f,WREG   | WREG = $\overline{f}$                       | 1             | 1              | N, Z                     |

|                      | COM             | Ws,Wd    | $Wd = \overline{Ws}$                        | 1             | 1              | N, Z                     |

| CP                   | CP              | f        | Compare f with WREG                         | 1             | 1              | C, DC, N, OV, Z          |

|                      | CP              | Wb,#lit5 | Compare Wb with lit5                        | 1             | 1              | C, DC, N, OV, Z          |

|                      | CP              | Wb,Ws    | Compare Wb with Ws (Wb – Ws)                | 1             | 1              | C, DC, N, OV, Z          |

| CP0                  | CPO             | f        | Compare f with 0x0000                       | 1             | 1              | C, DC, N, OV, Z          |

| 010                  | CPO             | Ws       | Compare Ws with 0x0000                      | 1             | 1              | C, DC, N, OV, Z          |

| CPB                  | CPB             | f        | Compare f with WREG, with Borrow            | 1             | 1              | C, DC, N, OV, Z          |

|                      | CPB             | Wb,#lit5 | Compare Wb with lit5, with Borrow           | 1             | 1              | C, DC, N, OV, Z          |

|                      | CPB             | Wb,Ws    | Compare Wb with Ws, with Borrow             | 1             | 1              | C, DC, N, OV, Z          |

|                      |                 |          | $(Wb - Ws - \overline{C})$                  |               |                | -,, -, -, -, -           |

| CPSEQ                | CPSEQ           | Wb,Wn    | Compare Wb with Wn, Skip if =               | 1             | 1<br>(2 or 3)  | None                     |

| CPSGT                | CPSGT           | Wb,Wn    | Compare Wb with Wn, Skip if >               | 1             | 1<br>(2 or 3)  | None                     |

| CPSLT                | CPSLT           | Wb,Wn    | Compare Wb with Wn, Skip if <               | 1             | 1<br>(2 or 3)  | None                     |

| CPSNE                | CPSNE           | Wb,Wn    | Compare Wb with Wn, Skip if ≠               | 1             | 1<br>(2 or 3)  | None                     |

| DAW                  | DAW.B           | Wn       | Wn = Decimal Adjust Wn                      | 1             | 1              | С                        |

| DEC                  | DEC             | f        | f = f -1                                    | 1             | 1              | C, DC, N, OV, Z          |

|                      | DEC             | f,WREG   | WREG = f-1                                  | 1             | 1              | C, DC, N, OV, Z          |

|                      | DEC             | Ws,Wd    | Wd = Ws - 1                                 | 1             | 1              | C, DC, N, OV, Z          |

| DEC2                 | DEC2            | f        | f = f - 2                                   | 1             | 1              | C, DC, N, OV, Z          |

|                      | DEC2            | f,WREG   | WREG = f – 2                                | 1             | 1              | C, DC, N, OV, Z          |

|                      | DEC2            | Ws,Wd    | Wd = Ws - 2                                 | 1             | 1              | C, DC, N, OV, Z          |

| DISI                 | DISI            | #lit14   | Disable Interrupts for k Instruction Cycles | 1             | 1              | None                     |

| DIV                  | DIV.SW          | Wm,Wn    | Signed 16/16-bit Integer Divide             | 1             | 18             | N, Z, C, OV              |

|                      | DIV.SD          | Wm,Wn    | Signed 32/16-bit Integer Divide             | 1             | 18             | N, Z, C, OV              |

|                      | DIV.UW          | Wm,Wn    | Unsigned 16/16-bit Integer Divide           | 1             | 18             | N, Z, C, OV              |

|                      | DIV.UD          | Wm,Wn    | Unsigned 32/16-bit Integer Divide           | 1             | 18             | N, Z, C, OV              |

| EXCH                 | EXCH            | Wns,Wnd  | Swap Wns with Wnd                           | 1             | 1              | None                     |

| FF1L                 | FF1L            | Ws,Wnd   | Find First One from Left (MSb) Side         | 1             | 1              | С                        |

| FF1R                 | FF1R            | Ws,Wnd   | Find First One from Right (LSb) Side        | 1             | 1              | С                        |

### TABLE 31-2: INSTRUCTION SET OVERVIEW (CONTINUED)

| DC CHARACTERISTICS                          |                       |                                | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                            |                   |                                    |  |  |

|---------------------------------------------|-----------------------|--------------------------------|------------------------------------------------------|----------------------------|-------------------|------------------------------------|--|--|

| Parameter<br>No. Typical <sup>(1)</sup> Max |                       | Units Operating<br>Temperature |                                                      | Vdd                        | Conditions        |                                    |  |  |

| Incremental                                 | Current Bro           | wn-out Res                     | et (∆BOR) <sup>(2)</sup>                             |                            |                   |                                    |  |  |

| DC25                                        | 3.1                   | 5.0                            | μA                                                   | -40°C to +125°C            | 2.0V              | ∆BOR <sup>(2)</sup>                |  |  |

|                                             | 4.3                   | 6.0                            | μA                                                   | -40°C to +125°C            | 3.3V              |                                    |  |  |

| Incremental                                 | Current Wat           | chdog Time                     | er (AWDT) <sup>(2)</sup>                             |                            |                   | •                                  |  |  |

| DC71                                        | 0.8                   | 1.5                            | μA                                                   | -40°C to +125°C            | 2.0V              |                                    |  |  |

|                                             | 0.8                   | 1.5                            | μA                                                   | -40°C to +125°C            | 3.3V              |                                    |  |  |

| Incremental                                 | Current Hig           | h/Low-Volta                    | ge Detect (A                                         | HLVD) <sup>(2)</sup>       |                   | •                                  |  |  |

| DC75                                        | 4.2                   | 15                             | μA                                                   | -40°C to +125°C            | 2.0V              |                                    |  |  |

|                                             | 4.2                   | 15                             | μA                                                   | -40°C to +125°C            | 3.3V              |                                    |  |  |

| Incremental                                 | Current Rea           | I-Time Cloc                    | k and Calen                                          | dar (∆RTCC) <sup>(2)</sup> |                   |                                    |  |  |

| DC77                                        | 0.3                   | 1.0                            | μA                                                   | -40°C to +125°C            | 2.0V              | ∆RTCC (with SOSC) <sup>(2)</sup>   |  |  |

|                                             | 0.35                  | 1.0                            | μA                                                   | -40°C to +125°C            | 3.3V              |                                    |  |  |

| DC77A                                       | 0.3                   | 1.0                            | μA                                                   | -40°C to +125°C            | 2.0V              | _ ∆RTCC (with LPRC) <sup>(2)</sup> |  |  |

|                                             | 0.35                  | 1.0                            | μA                                                   | -40°C to +125°C            | 3.3V              |                                    |  |  |

| Incremental                                 | Current Dee           | p Sleep BO                     |                                                      | ) <sup>(2)</sup>           |                   |                                    |  |  |

| DC81                                        | 0.11                  | 0.40                           | μA                                                   | -40°C to +125°C            | 2.0V              | △Deep Sleep BOR <sup>(2)</sup>     |  |  |

|                                             | 0.12                  | 0.40                           | μA                                                   | -40°C to +125°C            | 3.3V              |                                    |  |  |