#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 32MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SmartCard, SPI, UART/USART                     |

| Peripherals                | AES, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, HLVD, POR, PWM, WDT        |

| Number of I/O              | 21                                                                             |

| Program Memory Size        | 64KB (64K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 10x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                 |

| Supplier Device Package    | 28-SSOP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64ga202t-i-ss |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 3.2 CPU Control Registers

#### REGISTER 3-1: SR: ALU STATUS REGISTER

| U-0                  | U-0                                                                                                                                                 | U-0                          | U-0                       | U-0                        | U-0              | U-0              | R/W-0  |  |  |  |  |  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|---------------------------|----------------------------|------------------|------------------|--------|--|--|--|--|--|

| _                    | _                                                                                                                                                   | _                            |                           | _                          |                  |                  | DC     |  |  |  |  |  |

| bit 15               |                                                                                                                                                     |                              |                           | 1                          |                  |                  | bit    |  |  |  |  |  |

| R/W-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup>                                                                                                                                | D 444 o(1)                   |                           | <b>D</b> /// 0             | <b>D</b> 444.0   | <b>D</b> 4440    | DAALO  |  |  |  |  |  |

| IPL2 <sup>(2)</sup>  | IPL1 <sup>(2)</sup>                                                                                                                                 | R/W-0 <sup>(1)</sup>         | R-0                       | R/W-0                      | R/W-0            | R/W-0            | R/W-0  |  |  |  |  |  |

|                      | IPL1-                                                                                                                                               | IPL0 <sup>-/</sup>           | RA                        | N                          | OV               | Z                | C      |  |  |  |  |  |

| bit 7                |                                                                                                                                                     |                              |                           |                            |                  |                  | bit    |  |  |  |  |  |

| Legend:              |                                                                                                                                                     |                              |                           |                            |                  |                  |        |  |  |  |  |  |

| R = Readabl          | e bit                                                                                                                                               | W = Writable b               | it                        | U = Unimplem               | nented bit, read | d as '0'         |        |  |  |  |  |  |

| -n = Value at        | POR                                                                                                                                                 | '1' = Bit is set             |                           | '0' = Bit is clea          | ared             | x = Bit is unkr  | nown   |  |  |  |  |  |

|                      |                                                                                                                                                     |                              |                           |                            |                  |                  |        |  |  |  |  |  |

| bit 15-9             | Unimplemer                                                                                                                                          | nted: Read as '0             | ,                         |                            |                  |                  |        |  |  |  |  |  |

| oit 8                | DC: ALU Half Carry/Borrow bit                                                                                                                       |                              |                           |                            |                  |                  |        |  |  |  |  |  |

|                      | 1 = A carry out from the 4 <sup>th</sup> low-order bit (for byte-sized data) or 8 <sup>th</sup> low-order bit (for word-sized data                  |                              |                           |                            |                  |                  |        |  |  |  |  |  |

|                      | of the result occurred<br>0 = No carry out from the 4 <sup>th</sup> or 8 <sup>th</sup> low-order bit of the result has occurred                     |                              |                           |                            |                  |                  |        |  |  |  |  |  |

|                      | 0 = No carry                                                                                                                                        | out from the 4 <sup>th</sup> | or 8 <sup>th</sup> low-or | der bit of the res         | sult has occurre | ed               |        |  |  |  |  |  |

| bit 7-5              | IPL<2:0>: CI                                                                                                                                        | PU Interrupt Prio            | rity Level Sta            | atus bits <sup>(1,2)</sup> |                  |                  |        |  |  |  |  |  |

|                      | 111 = CPU I                                                                                                                                         | nterrupt Priority            | Level is 7 (1             | 5); user interrupt         | s are disabled   |                  |        |  |  |  |  |  |

|                      |                                                                                                                                                     | nterrupt Priority            |                           |                            |                  |                  |        |  |  |  |  |  |

|                      | 101 = CPU Interrupt Priority Level is 5 (13)                                                                                                        |                              |                           |                            |                  |                  |        |  |  |  |  |  |

|                      | 100 = CPU Interrupt Priority Level is 4 (12)                                                                                                        |                              |                           |                            |                  |                  |        |  |  |  |  |  |

|                      | 011 = CPU Interrupt Priority Level is 3 (11)<br>010 = CPU Interrupt Priority Level is 2 (10)                                                        |                              |                           |                            |                  |                  |        |  |  |  |  |  |

|                      |                                                                                                                                                     |                              |                           |                            |                  |                  |        |  |  |  |  |  |

|                      |                                                                                                                                                     | nterrupt Priority            |                           |                            |                  |                  |        |  |  |  |  |  |

| L:1 1                | 000 = CPU Interrupt Priority Level is 0 (8)                                                                                                         |                              |                           |                            |                  |                  |        |  |  |  |  |  |

| bit 4                | RA: REPEAT Loop Active bit                                                                                                                          |                              |                           |                            |                  |                  |        |  |  |  |  |  |

|                      | 1 = REPEAT loop in progress<br>0 = REPEAT loop not in progress                                                                                      |                              |                           |                            |                  |                  |        |  |  |  |  |  |

| bit 3                | N: ALU Negative bit                                                                                                                                 |                              |                           |                            |                  |                  |        |  |  |  |  |  |

|                      | 1 = Result was negative                                                                                                                             |                              |                           |                            |                  |                  |        |  |  |  |  |  |

| 1.1.0                | <ul> <li>0 = Result was not negative (zero or positive)</li> <li>OV: ALU Overflow bit</li> </ul>                                                    |                              |                           |                            |                  |                  |        |  |  |  |  |  |

| bit 2                |                                                                                                                                                     |                              |                           |                            |                  |                  |        |  |  |  |  |  |

|                      | <ul> <li>1 = Overflow occurred for signed (2's complement) arithmetic in this arithmetic operation</li> <li>0 = No overflow has occurred</li> </ul> |                              |                           |                            |                  |                  |        |  |  |  |  |  |

| bit 1                | Z: ALU Zero                                                                                                                                         |                              |                           |                            |                  |                  |        |  |  |  |  |  |

|                      | 1 = An opera                                                                                                                                        | tion, which affec            | ts the Z bit, h           | nas set it at some         | e time in the pa | ast              |        |  |  |  |  |  |

|                      | •                                                                                                                                                   | t recent operation           |                           |                            | •                |                  | esult) |  |  |  |  |  |

| bit 0                | C: ALU Carry                                                                                                                                        | /Borrow bit                  |                           |                            |                  |                  |        |  |  |  |  |  |

|                      | -                                                                                                                                                   | ut from the Most             | Significant b             | oit (MSb) of the r         | esult occurred   |                  |        |  |  |  |  |  |

|                      |                                                                                                                                                     | out from the Mos             |                           |                            |                  |                  |        |  |  |  |  |  |

| Note 1: Th           | no IDI v Statuc I                                                                                                                                   | bits are read-only           |                           |                            | 15>) = 1         |                  |        |  |  |  |  |  |

|                      |                                                                                                                                                     | bits are read-only           | •                         |                            | ,                | it to form the C |        |  |  |  |  |  |

2: The IPLx Status bits are concatenated with the IPL3 Status (CORCON<3>) bit to form the CPU Interrupt Priority Level (IPL). The value in parentheses indicates the IPL when IPL3 = 1.

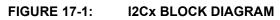

## TABLE 4-9: I<sup>2</sup>C<sup>™</sup> REGISTER MAP

| File<br>Name | Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10                       | Bit 9  | Bit 8                                                | Bit 7 | Bit 6      | Bit 5       | Bit 4       | Bit 3        | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|--------------|------|---------|--------|---------|--------|--------|------------------------------|--------|------------------------------------------------------|-------|------------|-------------|-------------|--------------|-------|-------|-------|---------------|

| I2C1RCV      | 02DA | —       |        | —       | _      | _      |                              | —      | —                                                    |       |            | I           | 2C1 Receiv  | ve Register  |       |       |       | 0000          |

| I2C1TRN      | 02DC | _       | _      | _       | _      | _      | _                            | _      | _                                                    |       |            | l:          | 2C1 Transn  | nit Register |       |       |       | OOFF          |

| I2C1BRG      | 02DE | _       | _      | _       | _      |        | Baud Rate Generator Register |        |                                                      |       |            |             |             |              | 0000  |       |       |               |

| I2C1CONL     | 02E0 | I2CEN   | _      | I2CSIDL | SCLREL | STRICT | A10M                         | DISSLW | DISSLW SMEN GCEN STREN ACKDT ACKEN RCEN PEN RSEN SEN |       |            |             |             | 1000         |       |       |       |               |

| I2C1CONH     | 02E2 | _       | _      | _       | _      | _      | _                            | _      | _                                                    | _     | PCIE       | SCIE        | BOEN        | SDAHT        | SBCDE | AHEN  | DHEN  | 0000          |

| I2C1STAT     | 02E4 | ACKSTAT | TRSTAT | ACKTIM  | _      | _      | BCL                          | GCSTAT | ADD10                                                | IWCOL | I2COV      | D/A         | Р           | S            | R/W   | RBF   | TBF   | 0000          |

| I2C1ADD      | 02E6 | —       | —      | _       | _      | —      | I2C1 Address Register        |        |                                                      |       |            |             |             |              | 0000  |       |       |               |

| I2C1MSK      | 02E8 | —       | _      | —       | _      | —      | -                            |        |                                                      |       | I2C        | 1 Address I | Mask Regis  | ter          |       |       |       | 0000          |

| I2C2RCV      | 02EA | —       | _      | —       | _      | —      | -                            | _      | _                                                    |       |            | I           | 2C2 Receiv  | e Register   |       |       |       | 0000          |

| I2C2TRN      | 02EC | _       | _      | _       | _      | _      | _                            | _      | _                                                    |       |            | l:          | 2C2 Transn  | nit Register |       |       |       | OOFF          |

| I2C2BRG      | 02EE | _       | —      | _       | _      |        |                              |        |                                                      | Bau   | d Rate Gen | erator Regi | ster        |              |       |       |       | 0000          |

| I2C2CONL     | 02F0 | I2CEN   | _      | I2CSIDL | SCLREL | STRICT | A10M                         | DISSLW | SMEN                                                 | GCEN  | STREN      | ACKDT       | ACKEN       | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C2CONH     | 02F2 | _       | _      | _       | _      | _      | _                            | _      | _                                                    | _     | PCIE       | SCIE        | BOEN        | SDAHT        | SBCDE | AHEN  | DHEN  | 0000          |

| I2C2STAT     | 02F4 | ACKSTAT | TRSTAT | ACKTIM  | _      | _      | BCL                          | GCSTAT | ADD10                                                | IWCOL | I2COV      | D/A         | Р           | S            | R/W   | RBF   | TBF   | 0000          |

| I2C2ADD      | 02F6 | —       | _      | —       | _      | —      | -                            |        |                                                      |       |            | 2C2 Addres  | ss Register |              |       |       |       | 0000          |

| I2C2MSK      | 02F8 | —       | _      | _       | _      | —      | _                            |        |                                                      |       | I2C        | 2 Address I | Mask Regis  | ter          |       |       |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| <b>TABLE 4-18</b> : | A/D CONVERTER REGISTER MAP |

|---------------------|----------------------------|

|---------------------|----------------------------|

| Name         Addr         Bit 19         Bit 19         Bit 9         Bit 9         Bit 8         Bit 7         Bit 6         Bit 7         Bit 7         Bit 6         Bit 7         Bit 7 <th< th=""><th></th><th>10.</th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th></th<>                                                                                                                                                                                                                                                                                                                              |           | 10.  |        |                                                                                                               |          |        |                 |                |             |              |                      |                       |          |                        |        |        |           |        |               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------|--------|---------------------------------------------------------------------------------------------------------------|----------|--------|-----------------|----------------|-------------|--------------|----------------------|-----------------------|----------|------------------------|--------|--------|-----------|--------|---------------|

| ADC1BUF1       0202       ADC1BUF2       0204       ADC1BUF2       0204       ADC       ADC         ADC1BUF2       0206       ADD Data Buffer 3/Threshold for Channel 3       ADC       ADC         ADC1BUF5       0208       ADD Data Buffer 5/Threshold for Channel 4       XXX         ADC1BUF6       0206       ADD Data Buffer 6/Threshold for Channel 6       XXX         ADC1BUF6       0206       ADD Data Buffer 6/Threshold for Channel 6       XXX         ADC1BUF6       0206       ADD Data Buffer 6/Threshold for Channel 6       XXX         ADC1BUF6       0206       ADD Data Buffer 6/Threshold for Channel 0 in Windowed Compare mode       XXX         ADC1BUF7       0210       ADD Data Buffer 10/Threshold for Channel 1 in Windowed Compare mode <sup>(1)</sup> XXX         ADC1BUF10       0212       A/D Data Buffer 10/Threshold for Channel 1 in Windowed Compare mode <sup>(1)</sup> XXX         ADC1BUF10       0212       A/D Data Buffer 10/Threshold for Channel 1 in Windowed Compare mode <sup>(1)</sup> XXX         ADC1BUF10       0214       A/D Data Buffer 10/Threshold for Channel 1 in Windowed Compare mode <sup>(1)</sup> XXX         ADC1BUF12       0214       A/D Data Buffer 10/Threshold for Channel 1 in Windowed Compare mode <sup>(1)</sup> XXX         ADC1BUF12       0214       A/D Data Buffer 10/Threshold for Channel 1 in Win                                                                                                                                                                                                                                                                                                                                                                                                             |           | Addr | Bit 15 | Bit 14                                                                                                        | Bit 13   | Bit 12 | Bit 11          | Bit 10         | Bit 9       | Bit 8        | Bit 7                | Bit 6                 | Bit 5    | Bit 4                  | Bit 3  | Bit 2  | Bit 1     | Bit 0  | All<br>Resets |

| ADC18UF2       0204       AVC 18UF2       AVD Data Buffer 2/Threshold for Channel 3       xxxx         ADC18UF4       0208       AVC Data Buffer 4/Threshold for Channel 3       xxxx         ADC18UF4       0200       AVD Data Buffer 4/Threshold for Channel 5       xxxx         ADC18UF6       0200       AVD Data Buffer 6/Threshold for Channel 6       xxxx         ADC18UF7       0206       AVD Data Buffer 6/Threshold for Channel 0 in Windowed Compare mode       xxxx         ADC18UF7       0202       AVD Data Buffer 8/Threshold for Channel 0 in Windowed Compare mode       xxxx         ADC18UF8       0210       AVD Data Buffer 9/Threshold for Channel 0 in Windowed Compare mode <sup>(1)</sup> xxxx         ADC18UF10       0214       AVD Data Buffer 10/Threshold for Channel 0 in Windowed Compare mode <sup>(1)</sup> xxxx         ADC18UF10       0214       AVD Data Buffer 10/Threshold for Channel 1/Threshold for Channel 3 in Windowed Compare mode <sup>(1)</sup> xxxx         ADC18UF11       0216       AVD Data Buffer 1/Threshold for Channel 4 in Windowed Compare mode <sup>(1)</sup> xxxx         ADC18UF12       0218       AVD Data Buffer 1/Threshold for Channel 4 in Windowed Compare mode <sup>(1)</sup> xxxx         ADC18UF13       0214       AVD Data Buffer 1/Threshold for Channel 4 in Windowed Compare mode <sup>(1)</sup> xxxx         ADC18UF13       0216       AVD                                                                                                                                                                                                                                                                                                                                                                      | ADC1BUF0  | 0200 |        |                                                                                                               |          |        |                 | A/D            | Data Buffer | 0/Thresho    | ld for Chan          | nel 0                 |          |                        |        |        |           |        | XXXX          |

| ADC1BUF3       0206       ADC1BUF4       0208       ADC1BUF4       0208       ADC1BUF4       0208       ADC1BUF4       0208       ADD Data Buffer 4Threshold for Channel 4       xxxx         ADC1BUF5       0200       ADD Data Buffer 5Threshold for Channel 5       Xxxx       Xxxx         ADC1BUF5       0200       ADD Data Buffer 6Threshold for Channel 6       Xxxx         ADC1BUF7       0202       ADD Data Buffer 9Threshold for Channel 6       Xxxx         ADC1BUF7       0202       ADD Data Buffer 9Threshold for Channel 9 Threshold for Channel 1 in Windowed Compare mode       Xxxx         ADC1BUF10       0214       ADD Data Buffer 10Threshold for Channel 9 Threshold for Channel 2 in Windowed Compare mode <sup>(1)</sup> Xxxx         ADC1BUF11       0216       ADD Data Buffer 10Threshold for Channel 1 In Windowed Compare mode <sup>(1)</sup> Xxxx         ADC1BUF12       0218       ADD Data Buffer 112Threshold for Channel 2 in Windowed Compare mode <sup>(1)</sup> Xxxx         ADC1BUF13       0210       ADD Data Buffer 12Threshold for Channel 2 in Windowed Compare mode <sup>(1)</sup> Xxxx         ADC1BUF13       0218       ADD Data Buffer 12Threshold for Channel 2 in Windowed Compare mode <sup>(1)</sup> Xxxx         ADC1BUF14       0216       ADD Data Buffer 12Threshold for Channel 2 in Windowed Compare mode <sup>(1)</sup> Xxxx         ADC1BUF14 <t< td=""><td>ADC1BUF1</td><td>0202</td><td></td><td></td><td></td><td></td><td></td><td>A/D</td><td>Data Buffer</td><td>1/Thresho</td><td>ld for Chan</td><td>nel 1</td><td></td><td></td><td></td><td></td><td></td><td></td><td>XXXX</td></t<>                                                                                                                                   | ADC1BUF1  | 0202 |        |                                                                                                               |          |        |                 | A/D            | Data Buffer | 1/Thresho    | ld for Chan          | nel 1                 |          |                        |        |        |           |        | XXXX          |

| ADC18UF4       0208       ADC18UF5       20A       ADC18UF5       20A       ADC18UF5       ADC18UF1       ADC18UF1       ADC18UF1       ADC18UF10       ADC18UF10       ADC18UF10       ADC18UF10       ADC18UF10       ADC18UF11       ADC18UF11       ADC18UF11       ADC18UF12       Q18       ADC18UF11       ADC18UF13       ADC18UF14       ADC18U                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ADC1BUF2  | 0204 |        |                                                                                                               |          |        |                 | A/D            | Data Buffer | 2/Thresho    | ld for Chan          | nel 2                 |          |                        |        |        |           |        | XXXX          |

| ADC18UF5       020A       ADC18UF6       020C       ADC18UF6       020C       ADC18UF6       020C       ADC18UF7       020E       ADC18UF6       021C       ADC18UF6       0210       ADD Data Buffer 10/Threshold for Channel 0 in Windowed Compare mode       XXX       XXX         ADC18UF10       0214       ADD Data Buffer 10/Threshold for Channel 10/Threshold for Channel 1 in Windowed Compare mode <sup>(1)</sup> XXX       XXX         ADC18UF12       0218       ADD Data Buffer 11/Threshold for Channel 12/Threshold for Channel 1 in Windowed Compare mode <sup>(1)</sup> XXX         ADC18UF13       021A       ADD Data Buffer 12/Threshold for Channel 12/Threshold for Channel 3 in Windowed Compare mode <sup>(1)</sup> XXX         ADC18UF13       021A       ADC18UF13       021A       ADC18UF13       SSSC2       SSSC1       SSSC0       -       ASAM       SAMP       DONE                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ADC1BUF3  | 0206 |        | A/D Data Buffer 3/Threshold for Channel 3                                                                     |          |        |                 |                |             |              |                      |                       |          |                        |        | XXXX   |           |        |               |

| ADC18UF6       020C       ADC18UF7       020E       ADC18UF7       020E       ADC18UF7       020E       ADC18UF7       020E       ADC18UF7       021E       ADC18UF7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ADC1BUF4  | 0208 |        | A/D Data Buffer 4/Threshold for Channel 4                                                                     |          |        |                 |                |             |              |                      |                       |          |                        |        | XXXX   |           |        |               |

| ADC18UF7       020E       ADC18UF8       0210       ADC18UF8       0210       ADC18UF9       0210       ADC18UF9       0210       ADC18UF9       0210       ADC18UF9       0212       ADC18UF9       0212       ADC18UF9       0212       ADC18UF9       0212       ADD Data Buffer 3/Threshold for Channel 3/Threshold for Channel 1/Threshold for Channel 10/Threshold for Channel 3 in Windowed Compare mode <sup>(1)</sup> xxxx         ADC18UF10       0216       ADD Data Buffer 10/Threshold for Channel 10/Threshold for Channel 11/Threshold for Channel 3 in Windowed Compare mode <sup>(1)</sup> xxxx         ADC18UF12       0218       A/D Data Buffer 12/Threshold for Channel 4 in Windowed Compare mode <sup>(1)</sup> xxxx         ADC18UF13       0214       A/D Data Buffer 12/Threshold for Channel 4 in Windowed Compare mode <sup>(1)</sup> xxxx         ADC18UF14       0210       A/D Data Buffer 12/Threshold for Channel 4 in Windowed Compare mode <sup>(1)</sup> xxxx         ADC18UF14       0212       ADON       ADD AB       MDDE12       FORM       SSRC3       SSRC2       SSRC1       SSRC0       ASAM       SAMP       DONE       000         AD1C0N1       0222       PVCF60       NVCF60       OFFCAL       BUFREGEN       SAMC2       <                                                                                                                                                                                                                                                                                                                                        | ADC1BUF5  | 020A |        | A/D Data Buffer 5/Threshold for Channel 5                                                                     |          |        |                 |                |             |              |                      |                       |          |                        |        | XXXX   |           |        |               |

| ADC18UF8       0210       A/D Data Buffer 8/Threshold for Channel 9/Threshold for Channel 0 in Windowed Compare mode       xxxx         ADC18UF9       0212       A/D Data Buffer 9/Threshold for Channel 1 in Windowed Compare mode       xxxx         ADC18UF10       0214       A/D Data Buffer 10/Threshold for Channel 1 in/Threshold for Channel 2 in Windowed Compare mode <sup>(1)</sup> xxxx         ADC18UF11       0216       A/D Data Buffer 11/Threshold for Channel 1 in/Threshold for Channel 3 in Windowed Compare mode <sup>(1)</sup> xxxx         ADC18UF12       0218       A/D Data Buffer 12/Threshold for Channel 12/Threshold for Channel 4 in Windowed Compare mode <sup>(1)</sup> xxxx         ADC18UF13       021A       X/D Data Buffer 12/Threshold for Channel 12/Threshold for Channel 4 in Windowed Compare mode <sup>(1)</sup> xxxx         ADC18UF13       021A       X/D Data Buffer 12/Threshold for Channel 12/Threshold for Channel 4 in Windowed Compare mode <sup>(1)</sup> xxxx         ADC18UF13       021A       X/D Data Buffer 12/Threshold for Channel 12/Threshold for Channel 5 to X/D Data Buffer 13       XXX         ADC18UF14       021C       X/D Cala Buffer 10/Threshold for Channel 12/Threshold for Channel 4 in Windowed Compare mode <sup>(1)</sup> XXX         ADC18UF14       021C       X/D Data Buffer 13/Threshold for Channel 5 to X/D Data Buffer 13       XXX         ADC18UF15       021E       X/D Data Buffer 13/Threshold for Channel 5 to X/D Data Buffer 13 <td< td=""><td>ADC1BUF6</td><td>020C</td><td></td><td></td><td></td><td></td><td></td><td>A/D</td><td>Data Buffer</td><td>6/Thresho</td><td>ld for Chan</td><td>nel 6</td><td></td><td></td><td></td><td></td><td></td><td></td><td>XXXX</td></td<>              | ADC1BUF6  | 020C |        |                                                                                                               |          |        |                 | A/D            | Data Buffer | 6/Thresho    | ld for Chan          | nel 6                 |          |                        |        |        |           |        | XXXX          |

| ADC18UF9       0212       A/D Data Buffer 9/Threshold for Channel 9/Threshold for Channel 1 in Windowed Compare mode       xxxx         ADC18UF10       0214       A/D Data Buffer 10/Threshold for Channel 10/Threshold for Channel 2 in Windowed Compare mode <sup>(1)</sup> xxxx         ADC18UF10       0216       A/D Data Buffer 11/Threshold for Channel 10/Threshold for Channel 3 in Windowed Compare mode <sup>(1)</sup> xxxx         ADC18UF12       0218       A/D Data Buffer 12/Threshold for Channel 12/Threshold for Channel 4 in Windowed Compare mode <sup>(1)</sup> xxxx         ADC18UF13       021A       A/D Data Buffer 12/Threshold for Channel 12/Threshold for Channel 4 in Windowed Compare mode <sup>(1)</sup> xxxx         ADC18UF14       021C       A/D Data Buffer 12/Threshold for Channel 12/Threshold for Channel 4 in Windowed Compare mode <sup>(1)</sup> xxxx         ADC18UF14       021C       A/D Data Buffer 13       XXX       XXXX         ADC18UF15       021E       A/D Data Buffer 14       XXXX         ADC10N1       0220       ADON       A/D AND       MARN       MODE12       FORM1       FORM0       SSRC3       SSRC1       SSRC0       ASAM       SAMP       DONE       000         AD1C0N2       0222       PVCFG1       PVCFG0       NVCFG0       OFFCAL       BUFREGEN       CSCNA       -       -       BUFS       SMPI4       SMPI                                                                                                                                                                                                                                                                                                                                                                                                       | ADC1BUF7  | 020E |        |                                                                                                               |          |        |                 | A/D            | Data Buffer | 7/Thresho    | ld for Chan          | nel 7                 |          |                        |        |        |           |        | XXXX          |

| ADC1BUF10       0214       ADD Data Buffer 10/Threshold for Channel 10/Threshold for Channel 2 in Windowed Compare mode <sup>(1)</sup> xxxx         ADC1BUF11       0216       A/D Data Buffer 11/Threshold for Channel 11/Threshold for Channel 3 in Windowed Compare mode <sup>(1)</sup> xxxx         ADC1BUF12       0218       A/D Data Buffer 12/Threshold for Channel 12/Threshold for Channel 4 in Windowed Compare mode <sup>(1)</sup> xxxx         ADC1BUF13       021A       A/D Data Buffer 12/Threshold for Channel 12/Threshold for Channel 4 in Windowed Compare mode <sup>(1)</sup> xxxx         ADC1BUF13       021A       A/D Data Buffer 12/Threshold for Channel 12/Threshold for Channel 4 in Windowed Compare mode <sup>(1)</sup> xxxx         ADC1BUF13       021A       A/D Data Buffer 12/Threshold for Channel 12/Threshold for Channel 4 in Windowed Compare mode <sup>(1)</sup> xxxx         ADC1BUF14       021C       A/D Data Buffer 12/Threshold for Channel 12/Threshold for Channel 4 in Windowed Compare mode <sup>(1)</sup> xxxx         ADC1BUF14       021C       A/D Data Buffer 12/Threshold for Channel 4 in Windowed Compare mode <sup>(1)</sup> xxx         ADC1BUF15       021E       A/D Data Buffer 12/Threshold for Channel 4 in Windowed Compare mode <sup>(1)</sup> xxx         AD1C0N1       0220       ADON       ADSID       DMABM       MOAEN       MODE12       FORM1       FORM0       SSRC3       SSRC1       SSRC1       SSRV1       SMPI2 <td< td=""><td>ADC1BUF8</td><td>0210</td><td></td><td></td><td></td><td>A/D</td><td>Data Buffer 8/</td><td>Threshold for</td><td>Channel 8/</td><td>Threshold</td><td>for Channe</td><td>0 in Windo</td><td>wed Comp</td><td>are mode</td><td></td><td></td><td></td><td></td><td>XXXX</td></td<> | ADC1BUF8  | 0210 |        |                                                                                                               |          | A/D    | Data Buffer 8/  | Threshold for  | Channel 8/  | Threshold    | for Channe           | 0 in Windo            | wed Comp | are mode               |        |        |           |        | XXXX          |

| ADC1BUF11       0216       ADD Data Buffer 11/Threshold for Channel 11/Threshold for Channel 3 in Windowed Compare mode <sup>(1)</sup> xxxx         ADC1BUF12       0218       A/D Data Buffer 12/Threshold for Channel 12/Threshold for Channel 4 in Windowed Compare mode <sup>(1)</sup> xxxx         ADC1BUF13       021A       A/D Data Buffer 12/Threshold for Channel 12/Threshold for Channel 4 in Windowed Compare mode <sup>(1)</sup> xxxx         ADC1BUF14       021C       A/D Data Buffer 12/Threshold for Channel 12/Threshold for Channel 4 in Windowed Compare mode <sup>(1)</sup> xxx         ADC1BUF14       021C       A/D Data Buffer 13       XXX         ADC1BUF15       021E       A/D Data Buffer 15       XXX         AD1CON1       0220       ADON       ADSID       DMABM       DMAEN       MODE12       FORM1       FORM0       SSRC3       SSRC1       SSRC0       ASAM       SAMP       DONE       000         AD1CON1       0220       ADON       ADSID       DMABM       DMAEN       MODE12       FORM1       FORM0       SSRC3       SSRC1       SSRC0       ASAM       MPI0       BUFM       ALTS       000         AD1CON3       0224       ADCC       EXTSAM       PUMPEN       SAMC3       SAMC2       SAMC1       SAMC0       ADCS5       ADCS5       ADCS4       ADCS3       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ADC1BUF9  | 0212 |        | A/D Data Buffer 9/Threshold for Channel 9/Threshold for Channel 1 in Windowed Compare mode                    |          |        |                 |                |             |              |                      |                       |          |                        | xxxx   |        |           |        |               |

| ADC18UF12       0218               A/D Data Buffer 12/Threshold for Channel 12/Threshold for Channel 4 in Windowed Compare mode <sup>(1)</sup> xxxx          ADC18UF13       021A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ADC1BUF10 | 0214 |        | A/D Data Buffer 10/Threshold for Channel 10/Threshold for Channel 2 in Windowed Compare mode <sup>(1)</sup> : |          |        |                 |                |             |              |                      |                       |          |                        | xxxx   |        |           |        |               |

| ADC1BUF13       021A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ADC1BUF11 | 0216 |        |                                                                                                               |          | A/D Da | ata Buffer 11/T | hreshold for ( | Channel 11/ | Threshold    | for Channe           | 3 in Windo            | wed Comp | are mode <sup>(1</sup> | )      |        |           |        | xxxx          |

| ADC1BUF14       021C       VACUAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ADC1BUF12 | 0218 |        | A/D Data Buffer 12/Threshold for Channel 12/Threshold for Channel 4 in Windowed Compare mode <sup>(1)</sup>   |          |        |                 |                |             |              |                      |                       |          |                        | xxxx   |        |           |        |               |

| ADC1BUF15021EO210ADON—ADSIDLDMABMDMAENMODE12FORM1FORM0SSRC3SSRC2SSRC1SSRC0—ASAMSAMPDONE000AD1CON10222PVCFG1PVCFG0NVCFG0OFFCALBUFREGENCSCNA——BUFSSMPI4SMPI3SMPI2SMP11SMP10BUFMALTS000AD1CON20222PVCFG1PVCFG0NVCFG0OFFCALBUFREGENCSCNA———BUFSSMP14SMP13SMP12SMP10BUFMALTS000AD1CON30224ADRCEXTSAMPUMPENSAMC4SAMC3SAMC2SAMC1SAMC0ADC57ADC56ADC55ADC54ADC53ADC52ADC51ADC50000AD1CN30228CH0NB2CH0NB1CH0SB3CH0SB2CH0SB1CH0SB0CH0NA2CH0NA1CH0NA0CH0SA4CH0SA3CH0SA2CH0SA0000AD1CSSL022C—————————————000AD1CON4022E—————————————000AD1CON4022E————————————000AD1CON4022E————————————…000 <td>ADC1BUF13</td> <td>021A</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>A/D</td> <td>Data Buffe</td> <td>er 13</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>xxxx</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ADC1BUF13 | 021A |        |                                                                                                               |          |        |                 |                | A/D         | Data Buffe   | er 13                |                       |          |                        |        |        |           |        | xxxx          |

| AD1CON1       0220       ADON       —       ADSIDL       DMABM       DMAEN       MODE12       FORM1       FORM0       SSRC3       SSRC1       SSRC0       —       ASAM       SAMP       DONE       000         AD1CON2       0222       PVCFG1       PVCFG0       NVCFG0       OFFCAL       BUFREGEN       CSCNA       —       —       BUFS       SMPI4       SMPI3       SMPI2       SMPI1       SMP0       BUFM       ALTS       000         AD1CON3       0224       ADRC       EXTSAM       PUMPEN       SAMC4       SAMC3       SAMC2       SAMC1       SAMC0       ADCS7       ADCS6       ADCS5       ADCS4       ADCS3       ADCS2       ADCS1       ADCS0       000         AD1CHS       0228       CH0NB1       CH0NB0       CH0SB3       CH0SB3       CH0SB1       CH0SB0       CH0NA2       CH0NA2       CH0NA1       CH0NA3       CH0SA3       CH0SA0       CH0NA2       CH0NA1       CH0NA3       CH0SA3       CH0SB0       CH0NA2       CH0NA1       CH0NA3       CH0SA3       CH0NA2       CH0NA1       CH0NA3       CH0SA3       CH0SA3       CH0NA2       CH0NA1       CH0NA3       CH0SA3       CH0SA3       CH0NA1       CH0NA3       CH0SA3       CH0SA1 <td>ADC1BUF14</td> <td>021C</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>A/D</td> <td>Data Buffe</td> <td>er 14</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>xxxx</td>                                                                                                                                                                                                                                                                                                                                                                                       | ADC1BUF14 | 021C |        |                                                                                                               |          |        |                 |                | A/D         | Data Buffe   | er 14                |                       |          |                        |        |        |           |        | xxxx          |

| AD1CON20222PVCFG1PVCFG0NVCFG0OFFCALBUFREGENCSCNA——BUFSSMPI4SMPI3SMPI2SMPI1SMPI0BUFMALTS000AD1CON30224ADRCEXTSAMPUMPENSAMC4SAMC3SAMC2SAMC1SAMC0ADCS7ADCS6ADCS5ADCS4ADCS3ADCS2ADCS1ADCS0000AD1CHS0228CH0NB2CH0NB1CH0NB0CH0SB4CH0SB3CH0SB2CH0SB1CH0SB0CH0NA2CH0NA1CH0NA0CH0SA4CH0SA3CH0SA2CH0SA0000AD1CSH022C000AD1CON4022E000AD1CON50230ASENLPENCTMREQBGREQ000AD1CHTL0238000AD1CON50230ASENLPENCTMREQBGREQASINT1ASINT0000AD1CTMENL0238000AD1CON50230ASENLPENCTMREQBGREQASINT1ASINT0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ADC1BUF15 | 021E |        |                                                                                                               |          |        |                 |                | A/D         | Data Buffe   | r 15                 |                       |          |                        |        |        |           |        | XXXX          |

| AD1CON3       0224       ADRC       EXTSAM       PUMPEN       SAMC4       SAMC3       SAMC2       SAMC1       SAMC0       ADCS7       ADCS6       ADCS5       ADCS4       ADCS3       ADCS2       ADCS1       ADCS0       000         AD1CHS       0228       CH0NB2       CH0NB1       CH0NB0       CH0SB4       CH0SB3       CH0SB2       CH0SB1       CH0SB0       CH0NA2       CH0NA1       CH0NA0       CH0SA3       CH0SA2       CH0SA0       000         AD1CSSH       0220       C       CSS<31:27>       —       —       —       —       —       —       —       —       —       —       —       000       ADCS3       ADCS2       ADCS1       ADCS0       000         AD1CSSH       0220       —       CSS<31:27>       —       —       —       —       —       —       —       —       —       —       —       000       AD1CS1       020       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       … </td <td>AD1CON1</td> <td>0220</td> <td>ADON</td> <td>—</td> <td>ADSIDL</td> <td>DMABM</td> <td>DMAEN</td> <td>MODE12</td> <td>FORM1</td> <td>FORM0</td> <td>SSRC3</td> <td>SSRC2</td> <td>SSRC1</td> <td>SSRC0</td> <td>_</td> <td>ASAM</td> <td>SAMP</td> <td>DONE</td> <td>0000</td>                                                                                                                                                                                                                                                                                                                                                                                                                         | AD1CON1   | 0220 | ADON   | —                                                                                                             | ADSIDL   | DMABM  | DMAEN           | MODE12         | FORM1       | FORM0        | SSRC3                | SSRC2                 | SSRC1    | SSRC0                  | _      | ASAM   | SAMP      | DONE   | 0000          |

| AD1CHS       0228       CH0NB2       CH0NB1       CH0NB0       CH0SB4       CH0SB3       CH0SB2       CH0SB1       CH0SB0       CH0NA2       CH0NA1       CH0NA0       CH0SA4       CH0SA3       CH0SA2       CH0SA1       CH0SA3       CH0SA3       CH0SA4       CH0SA3       CH0SA3       CH0SA4       CH0SA4       CH0SA3       CH0SA4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | AD1CON2   | 0222 | PVCFG1 | PVCFG0                                                                                                        | NVCFG0   | OFFCAL | BUFREGEN        | CSCNA          |             | —            | BUFS                 | SMPI4                 | SMPI3    | SMPI2                  | SMPI1  | SMPI0  | BUFM      | ALTS   | 0000          |

| AD1CSSH       022A       CSS<31:27>       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       000         AD1CSSL       022C       -       -       -       -       -       -       -       -       -       -       000         AD1CON4       022E       -       -       -       -       -       -       -       -       DMABL<2:0>       000         AD1CON5       0230       ASEN       LPEN       CTMREQ       BGREQ       -       -       -       -       -       -       -       DMABL<2:0>       000         AD1CHITL       0234       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       D000       D00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | AD1CON3   | 0224 | ADRC   | EXTSAM                                                                                                        | PUMPEN   | SAMC4  | SAMC3           | SAMC2          | SAMC1       | SAMC0        | ADCS7                | ADCS6                 | ADCS5    | ADCS4                  | ADCS3  | ADCS2  | ADCS1     | ADCS0  | 0000          |

| AD1CSSL       022C          CSS<14:0>(1) <th< td=""><td>AD1CHS</td><td>0228</td><td>CH0NB2</td><td>CH0NB1</td><td>CH0NB0</td><td>CH0SB4</td><td>CH0SB3</td><td>CH0SB2</td><td>CH0SB1</td><td>CH0SB0</td><td>CH0NA2</td><td>CH0NA1</td><td>CH0NA0</td><td>CH0SA4</td><td>CH0SA3</td><td>CH0SA2</td><td>CH0SA1</td><td>CH0SA0</td><td>0000</td></th<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | AD1CHS    | 0228 | CH0NB2 | CH0NB1                                                                                                        | CH0NB0   | CH0SB4 | CH0SB3          | CH0SB2         | CH0SB1      | CH0SB0       | CH0NA2               | CH0NA1                | CH0NA0   | CH0SA4                 | CH0SA3 | CH0SA2 | CH0SA1    | CH0SA0 | 0000          |

| AD1CON4       022E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | AD1CSSH   | 022A |        |                                                                                                               | CSS<31:2 | 7>     |                 | _              | _           | —            |                      | _                     | —        |                        |        | —      | —         | —      | 0000          |

| AD1CON5     0230     ASEN     LPEN     CTMREQ     BGREQ     —     ASINT1     ASINT0     —     —     —     —     WM1     WM0     CM1     CM0     000       AD1CHITL     0234     —     —     —     —     ASINT1     ASINT0     —     —     —     —     WM1     WM0     CM1     CM0     000       AD1CHITL     0234     —     —     —     —     —     —     —     —     W00     CM1     CM0     000       AD1CTMENL     0238     —     —     —     —     —     CTMEN     CTMEN     CTMEN     US00     US00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | AD1CSSL   | 022C | —      |                                                                                                               |          |        |                 |                |             | CSS<1        | 14:0> <sup>(1)</sup> |                       |          |                        |        |        |           |        | 0000          |

| AD1CHITL         0234           CHH<12:0>(1)         000           AD1CTMENL         0238           CTMEN<12:0>(1)         000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | AD1CON4   | 022E | —      | —                                                                                                             | —        | —      | —               | —              | —           | —            | —                    | —                     | —        | —                      | —      | [      | DMABL<2:0 | >      | 0000          |

| AD1CTMENL 0238 CTMEN<12:0> <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           | 0230 | ASEN   | LPEN                                                                                                          | CTMREQ   | BGREQ  | —               | _              | ASINT1      | ASINT0       | —                    | —                     | —        | —                      | WM1    | WM0    | CM1       | CM0    | 0000          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | AD1CHITL  | 0234 | —      | —                                                                                                             | —        |        |                 |                |             |              |                      |                       |          |                        |        |        |           |        | 0000          |

| AD1DMBUF 023A A/D Conversion Data Buffer (Extended Buffer mode) xxx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | AD1CTMENL | 0238 | —      | —                                                                                                             | —        |        |                 |                |             |              | CTMEN                | <12:0> <sup>(1)</sup> |          |                        |        |        |           |        | 0000          |