Welcome to E-XFL.COM

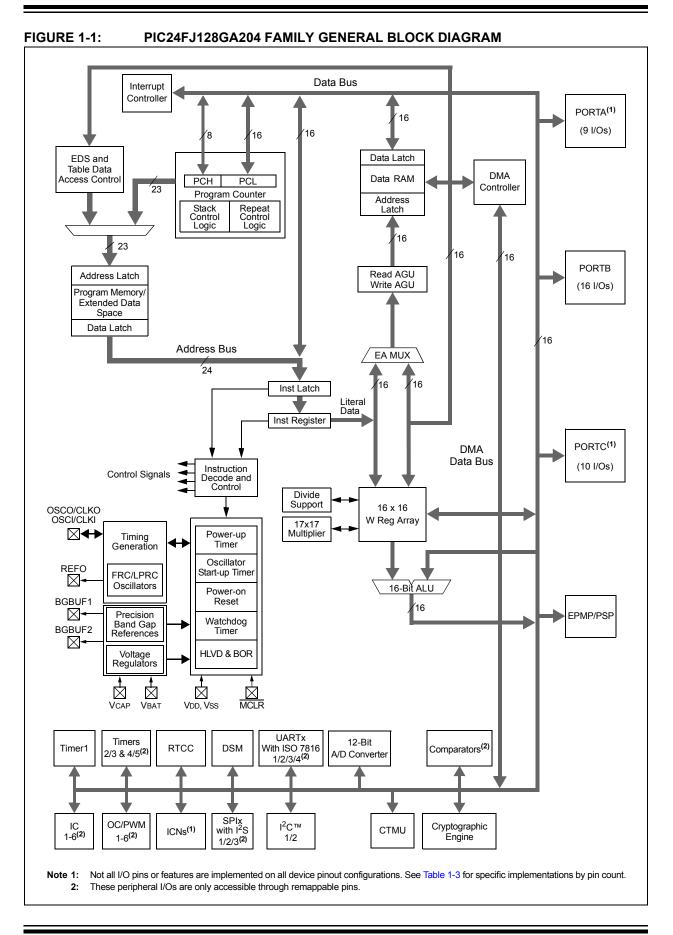

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Decalis                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP/PSP, SmartCard, SPI, UART/USART           |

| Peripherals                | AES, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, HLVD, POR, PWM, WDT       |

| Number of I/O              | 35                                                                            |

| Program Memory Size        | 64KB (64K x 8)                                                                |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                     |

| Data Converters            | A/D 13x10b/12b                                                                |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-VQFN Exposed Pad                                                           |

| Supplier Device Package    | 44-QFN (8x8)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj64ga204-i-ml |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                | Pin Num                       | ber/Grid        | Locator            |     |                 |                                                                               |

|----------------|-------------------------------|-----------------|--------------------|-----|-----------------|-------------------------------------------------------------------------------|

| Pin Function   | 28-Pin<br>SPDIP/SOIC/<br>SSOP | 28-Pin<br>QFN-S | 44-Pin<br>TQFP/QFN | I/O | Input<br>Buffer | Description                                                                   |

| CTED1          | 2                             | 27              | 19                 | I   | ANA             | CTMU External Edge Inputs.                                                    |

| CTED2          | 3                             | 28              | 20                 | Ι   | ANA             |                                                                               |

| CTED3          | 16                            | 13              | 43                 | Ι   | ANA             |                                                                               |

| CTED4          | 18                            | 15              | 1                  | Ι   | ANA             |                                                                               |

| CTED5          | 25                            | 22              | 14                 | Ι   | ANA             |                                                                               |

| CTED6          | 26                            | 23              | 15                 | Ι   | ANA             |                                                                               |

| CTED7          | —                             | —               | 5                  | Ι   | ANA             |                                                                               |

| CTED8          | 7                             | 4               | 24                 | Ι   | ANA             |                                                                               |

| CTED9          | 22                            | 19              | 9                  | Ι   | ANA             |                                                                               |

| CTED10         | 17                            | 14              | 44                 | Ι   | ANA             |                                                                               |

| CTED11         | 21                            | 18              | 8                  | Ι   | ANA             |                                                                               |

| CTED12         | 5                             | 2               | 22                 | Ι   | ANA             |                                                                               |

| CTED13         | 6                             | 3               | 23                 | Ι   | ANA             |                                                                               |

| CTPLS          | 24                            | 21              | 11                 | 0   |                 | CTMU Pulse Output.                                                            |

| CVREF          | 25                            | 22              | 14                 | 0   | ANA             | Comparator Voltage Reference Output.                                          |

| CVREF+         | 2                             | 27              | 19                 | Ι   | ANA             | Comparator Reference Voltage (high) Input.                                    |

| CVREF-         | 3                             | 28              | 20                 | Ι   | ANA             | Comparator Reference Voltage (low) Input.                                     |

| INT0           | 16                            | 13              | 43                 | Ι   | ST              | External Interrupt Input 0.                                                   |

| HLVDIN         | 23                            | 20              | 10                 | I   | ANA             | High/Low-Voltage Detect Input.                                                |

| MCLR           | 1                             | 26              | 18                 | I   | ST              | Master Clear (device Reset) Input. This line is brought low to cause a Reset. |

| OSCI           | 9                             | 6               | 30                 | I   | ANA             | Main Oscillator Input Connection.                                             |

| OSCO           | 10                            | 7               | 31                 | 0   |                 | Main Oscillator Output Connection.                                            |

| PGC1           | 5                             | 2               | 22                 | I/O | ST              | In-Circuit Debugger/Emulator/ICSP™                                            |

| PGC2           | 22                            | 19              | 9                  | I/O | ST              | Programming Clock.                                                            |

| PGC3           | 15                            | 12              | 42                 | I/O | ST              | 1                                                                             |

| PGD1           | 4                             | 1               | 21                 | I/O | ST              | ]                                                                             |

| PGD2           | 21                            | 18              | 8                  | I/O | ST              | 1                                                                             |

| PGD3           | 14                            | 11              | 41                 | I/O | ST              | 1                                                                             |

| Legend: ST = S | Schmitt Trigger               | input           |                    |     |                 | mpatible input I = Input<br>P = Power                                         |

#### **TABLE 1-3**: PIC24FJ128GA204 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

ANA = Analog input  $I^2C$  = ST with  $I^2C^{TM}$  or SMBus levels

O = Output

P = Power

|              | Pin Num                       | per/Grid        | Locator            |     |                  |                                            |

|--------------|-------------------------------|-----------------|--------------------|-----|------------------|--------------------------------------------|

| Pin Function | 28-Pin<br>SPDIP/SOIC/<br>SSOP | 28-Pin<br>QFN-S | 44-Pin<br>TQFP/QFN | I/O | Input<br>Buffer  | Description                                |

| RP0          | 4                             | 1               | 21                 | I/O | ST               | Remappable Peripherals (input or output).  |

| RP1          | 5                             | 2               | 22                 | I/O | ST               |                                            |

| RP2          | 6                             | 3               | 23                 | I/O | ST               |                                            |

| RP3          | 7                             | 4               | 24                 | I/O | ST               |                                            |

| RP5          | 14                            | 11              | 41                 | I/O | ST               |                                            |

| RP6          | 3,15                          | 12              | 42                 | I/O | ST               |                                            |

| RP7          | 16                            | 13              | 43                 | I/O | ST               |                                            |

| RP8          | 17                            | 14              | 44                 | I/O | ST               |                                            |

| RP9          | 18                            | 15              | 1                  | I/O | ST               |                                            |

| RP10         | 21                            | 18              | 8                  | I/O | ST               | 1                                          |

| RP11         | 22                            | 19              | 9                  | I/O | ST               |                                            |

| RP12         | 23                            | 20              | 10                 | I/O | ST               |                                            |

| RP13         | 24                            | 21              | 11                 | I/O | ST               |                                            |

| RP14         | 25                            | 22              | 14                 | I/O | ST               |                                            |

| RP15         | 26                            | 23              | 15                 | I/O | ST               |                                            |

| RP16         | _                             |                 | 25                 | I/O | ST               |                                            |

| RP17         | _                             |                 | 26                 | I/O | ST               |                                            |

| RP18         | _                             |                 | 27                 | I/O | ST               |                                            |

| RP19         | _                             |                 | 36                 | I/O | ST               |                                            |

| RP20         | _                             |                 | 37                 | I/O | ST               |                                            |

| RP21         | _                             |                 | 38                 | I/O | ST               |                                            |

| RP22         | _                             |                 | 2                  | I/O | ST               |                                            |

| RP23         | _                             |                 | 3                  | I/O | ST               |                                            |

| RP24         | _                             |                 | 4                  | I/O | ST               |                                            |

| RP25         | _                             | _               | 5                  | I/O | ST               | 1                                          |

| RPI4         | 11                            | 8               | 33                 | I   | ST               | Remappable Peripheral (input).             |

| RTCC         | 25                            | 22              | 14                 | 0   | —                | Real-Time Clock Alarm/Seconds Pulse Output |

| SCL1         | 17                            | 14              | 44                 | I/O | l <sup>2</sup> C | I2C1 Synchronous Serial Clock Input/Output |

| SCL2         | 7                             | 4               | 24                 | I/O | l <sup>2</sup> C | I2C2 Synchronous Serial Clock Input/Output |

| SCLKI        | 12                            | 9               | 34                 | Ι   | —                | Secondary Oscillator Digital Clock Input.  |

| SDA1         | 18                            | 15              | 1                  | I/O | l <sup>2</sup> C | I2C1 Data Input/Output.                    |

| SDA2         | 6                             | 3               | 23                 | I/O | l <sup>2</sup> C | I2C2 Data Input/Output.                    |

| SOSCI        | 11                            | 8               | 33                 | Ι   | ANA              | Secondary Oscillator/Timer1 Clock Input.   |

|              | 12                            | 9               | 34                 | 0   | ANA              | Secondary Oscillator/Timer1 Clock Output.  |

#### **TABLE 1-3:** PIC24FJ128GA204 FAMILY PINOUT DESCRIPTIONS (CONTINUED)

ANA = Analog input  $I^2C$  = ST with  $I^2C^{TM}$  or SMBus levels

#### TABLE 4-21: DMA REGISTER MAP

|              | <del>,</del> - <u>2</u>   . |        |                            |        |        |        |        |         |              |               |              |         |         |         |         |       |        |                                        |

|--------------|-----------------------------|--------|----------------------------|--------|--------|--------|--------|---------|--------------|---------------|--------------|---------|---------|---------|---------|-------|--------|----------------------------------------|

| File<br>Name | Addr                        | Bit 15 | Bit 14                     | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8        | Bit 7         | Bit 6        | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1 | Bit 0  | All<br>Resets                          |

| DMACON       | 0450                        | DMAEN  | —                          | —      | —      | —      | —      | —       | —            | —             | —            | —       | —       | —       | _       | —     | PRSSEL | 0000                                   |

| DMABUF       | 0452                        |        | DMA Transfer Data Buffer 0 |        |        |        |        |         |              |               |              |         |         | 0000    |         |       |        |                                        |

| DMAL         | 0454                        |        |                            |        |        |        |        |         |              |               |              |         | 0000    |         |         |       |        |                                        |

| DMAH         | 0456                        |        |                            |        |        |        |        | DN      | 1A Low Add   | ress Limit Re | gister       |         |         |         |         |       |        | 0000                                   |

| DMACH0       | 0458                        | _      | _                          | _      | r      | _      | NULLW  | RELOAD  | CHREQ        | SAMODE1       | SAMODE0      | DAMODE1 | DAMODE0 | TRMODE1 | TRMODE0 | SIZE  | CHEN   | 0000                                   |

| DMAINT0      | 045A                        | DBUFWF | _                          | CHSEL5 | CHSEL4 | CHSEL3 | CHSEL2 | CHSEL1  | CHSEL0       | HIGHIF        | LOWIF        | DONEIF  | HALFIF  | OVRUNIF | —       | _     | HALFEN | 0000                                   |

| DMASRC0      | 045C                        |        |                            | •      |        | •      | •      | DMA C   | hannel 0 Sc  | urce Addres   | s Register   |         | •       | •       |         |       |        | 0000                                   |

| DMADST0      | 045E                        |        |                            |        |        |        |        | DMA Cha | annel 0 Dest | ination Addre | ess Register |         |         |         |         |       |        | 0000                                   |

| DMACNT0      | 0460                        |        |                            |        |        |        |        | DMA Ch  | annel 0 Tra  | nsaction Cou  | int Register |         |         |         |         |       |        | 0001                                   |

| DMACH1       | 0462                        | _      | _                          | _      | r      | —      | NULLW  | RELOAD  | CHREQ        | SAMODE1       | SAMODE0      | DAMODE1 | DAMODE0 | TRMODE1 | TRMODE0 | SIZE  | CHEN   | 0000                                   |

| DMAINT1      | 0464                        | DBUFWF | _                          | CHSEL5 | CHSEL4 | CHSEL3 | CHSEL2 | CHSEL1  | CHSEL0       | HIGHIF        | LOWIF        | DONEIF  | HALFIF  | OVRUNIF | _       | —     | HALFEN | 0000                                   |

| DMASRC1      | 0466                        |        |                            |        |        |        |        | DMA C   | hannel 1 So  | ource Address | s Register   |         |         |         |         |       |        | 0000                                   |

| DMADST1      | 0468                        |        |                            |        |        |        |        | DMA Ch  | annel 1 Dest | ination Addre | ess Register |         |         |         |         |       |        | 0000                                   |

| DMACNT1      | 046A                        |        |                            |        |        |        |        | DMA Ch  | nannel 1 Tra | nsaction Cou  | nt Register  |         |         |         |         |       |        | 0001                                   |

| DMACH2       | 046C                        | _      | —                          | _      | r      | —      | NULLW  | RELOAD  | CHREQ        | SAMODE1       | SAMODE0      | DAMODE1 | DAMODE0 | TRMODE1 | TRMODE0 | SIZE  | CHEN   | 0000                                   |

| DMAINT2      | 046E                        | DBUFWF | _                          | CHSEL5 | CHSEL4 | CHSEL3 | CHSEL2 | CHSEL1  | CHSEL0       | HIGHIF        | LOWIF        | DONEIF  | HALFIF  | OVRUNIF | _       | —     | HALFEN | 0000                                   |

| DMASRC2      | 0470                        |        |                            |        |        |        |        | DMA C   | hannel 2 Sc  | urce Addres   | s Register   |         |         |         |         |       |        | 0000                                   |

| DMADST2      | 0472                        |        |                            |        |        |        |        | DMA Cha | annel 2 Dest | ination Addre | ess Register |         |         |         |         |       |        | 0000                                   |

| DMACNT2      | 0474                        |        |                            |        |        |        |        | DMA Ch  | annel 2 Tra  | nsaction Cou  | int Register |         |         |         |         |       |        | 0001                                   |

| DMACH3       | 0476                        | _      | —                          | _      | r      | —      | NULLW  | RELOAD  | CHREQ        | SAMODE1       | SAMODE0      | DAMODE1 | DAMODE0 | TRMODE1 | TRMODE0 | SIZE  | CHEN   | 0000                                   |

| DMAINT3      | 0478                        | DBUFWF | _                          | CHSEL5 | CHSEL4 | CHSEL3 | CHSEL2 | CHSEL1  | CHSEL0       | HIGHIF        | LOWIF        | DONEIF  | HALFIF  | OVRUNIF | _       | —     | HALFEN | 0000                                   |

| DMASRC3      | 047A                        |        |                            |        |        |        |        | DMA C   | hannel 3 Sc  | urce Addres   | s Register   |         |         |         |         |       |        | 0000                                   |

| DMADST3      | 047C                        |        |                            |        |        |        |        | DMA Cha | annel 3 Dest | ination Addre | ess Register |         |         |         |         |       |        | 0000                                   |

| DMACNT3      | 047E                        |        |                            |        |        |        |        | DMA Ch  | annel 3 Tra  | nsaction Cou  | int Register |         |         |         |         |       |        | 0001                                   |

| DMACH4       | 0480                        | _      | _                          | _      | r      | _      | NULLW  | RELOAD  | CHREQ        | SAMODE1       | SAMODE0      | DAMODE1 | DAMODE0 | TRMODE1 | TRMODE0 | SIZE  | CHEN   | 0000                                   |

| DMAINT4      | 0482                        | DBUFWF | _                          | CHSEL5 | CHSEL4 | CHSEL3 | CHSEL2 | CHSEL1  | CHSEL0       | HIGHIF        | LOWIF        | DONEIF  | HALFIF  | OVRUNIF | _       | _     | HALFEN | 0000                                   |

| DMASRC4      | 0484                        |        |                            |        |        |        |        | DMA C   | hannel 4 Sc  | urce Addres   | s Register   |         |         |         |         |       |        | 0000                                   |

| DMADST4      | 0486                        |        |                            |        |        |        |        | DMA Cha | annel 4 Dest | ination Addre | ess Register |         |         |         |         |       |        | 0000                                   |

| DMACNT4      | 0488                        |        |                            |        |        |        |        | DMA Ch  | annel 4 Tra  | nsaction Cou  | int Register |         |         |         |         |       |        | 0001                                   |

| DMACH5       | 048A                        | _      | _                          |        | r      | _      | NULLW  | RELOAD  | CHREQ        | SAMODE1       | SAMODE0      | DAMODE1 | DAMODE0 | TRMODE1 | TRMODE0 | SIZE  | CHEN   | 0000                                   |

| DMAINT5      | 048C                        | DBUFWF | _                          | CHSEL5 | CHSEL4 | CHSEL3 | CHSEL2 | CHSEL1  | CHSEL0       | HIGHIF        | LOWIF        | DONEIF  | HALFIF  | OVRUNIF | _       | _     | HALFEN | 0000                                   |

| DMASRC5      | 048E                        |        |                            | •      |        |        |        | DMA C   | hannel 5 Sc  | urce Addres   | s Register   |         |         |         |         |       |        | 0000                                   |

| DMADST5      | 0490                        | İ      |                            |        |        |        |        | DMA Cha | annel 5 Dest | ination Addre | ess Register |         |         |         |         |       |        | 0000                                   |

| DMACNT5      | 0492                        | İ      |                            |        |        |        |        | DMA Ch  | annel 5 Tra  | nsaction Cou  | int Register |         |         |         |         |       |        | 0001                                   |

| L            | 1                           | 1      |                            |        |        |        |        |         |              |               | <b>U</b> -   |         |         |         |         |       |        | لـــــــــــــــــــــــــــــــــــــ |

Legend: — = unimplemented, read as '0'; r = reserved. Reset values are shown in hexadecimal.

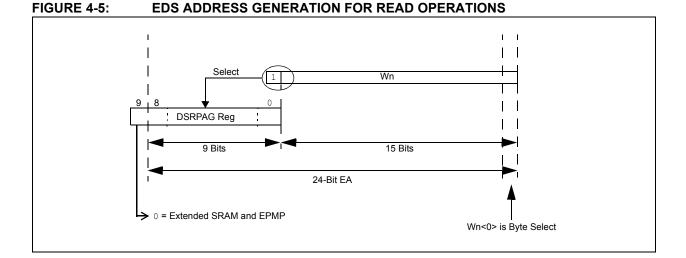

#### 4.2.5.1 Data Read from EDS

In order to read the data from the EDS space first, an Address Pointer is set up by loading the required EDS page number into the DSRPAG register and assigning the offset address to one of the W registers. Once the above assignment is done, the EDS window is enabled by setting bit 15 of the Working register assigned with the offset address; then, the contents of the pointed EDS location can be read.

Figure 4-5 illustrates how the EDS space address is generated for read operations.

When the Most Significant bit of the EA is '1' and DSRPAG<9> = 0, the lower 9 bits of DSRPAG are concatenated to the lower 15 bits of the EA to form a 24-bit EDS space address for read operations.

Example 4-1 shows how to read a byte, word and double-word from EDS.

Note: All read operations from EDS space have an overhead of one instruction cycle. Therefore, a minimum of two instruction cycles are required to complete an EDS read. EDS reads under the REPEAT instruction; the first two accesses take three cycles and the subsequent accesses take one cycle.

#### EXAMPLE 4-1: EDS READ CODE IN ASSEMBLY

| ; Set the EDS mov | <pre>g page from where #0x0002, w0</pre> | e the data to be read                                    |

|-------------------|------------------------------------------|----------------------------------------------------------|

| mov               | w0, DSRPAG                               | ;page 2 is selected for read                             |

| mov               | #0x0800, w1                              | ;select the location (0x800) to be read                  |

| bset              | w1, #15                                  | ;set the MSB of the base address, enable EDS mode        |

| ;Read a byte      | from the selecte                         | ed location                                              |

| mov.b             | [w1++], w2                               | ;read Low byte                                           |

| mov.b             | [w1++], w3                               | ;read High byte                                          |

| ;Read a word      | from the selecte                         | d location                                               |

| mov               | [w1], w2                                 | ;                                                        |

| ,                 |                                          | selected location<br>;two word read, stored in w2 and w3 |

| <b>REGISTER 6-1:</b> NVMCON: FLASH MEMORY CONTROL REGISTER |

|------------------------------------------------------------|

|------------------------------------------------------------|

| R/S-0, HC <sup>(1)</sup>                                                | R/W-0 <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                         | R-0, HSC <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | U-0                                                                                                                                                                                                                                                                                    | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | U-0                                                                                         | U-0                                                                                 | U-0                            |

|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------|

| WR                                                                      | WREN                                                                                                                                                                                                                                                                                                                                                                                                         | WRERR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _                                                                                                                                                                                                                                                                                      | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _                                                                                           | _                                                                                   | _                              |

| bit 15                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                              | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                             |                                                                                     | bit                            |

|                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                             |                                                                                     |                                |

| U-0                                                                     | R/W-0 <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                         | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | U-0                                                                                                                                                                                                                                                                                    | R/W-0 <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R/W-0 <sup>(1)</sup>                                                                        | R/W-0 <sup>(1)</sup>                                                                | R/W-0 <sup>(1)</sup>           |

| _                                                                       | ERASE                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | —                                                                                                                                                                                                                                                                                      | NVMOP3 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | NVMOP2 <sup>(2)</sup>                                                                       | NVMOP1 <sup>(2)</sup>                                                               | NVMOP0 <sup>(2)</sup>          |

| bit 7                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                             |                                                                                     | bit                            |

|                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                             |                                                                                     |                                |