Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 6144                                                        |

| Number of Logic Elements/Cells | 27648                                                       |

| Total RAM Bits                 | 131072                                                      |

| Number of I/O                  | 404                                                         |

| Number of Gates                | 1124022                                                     |

| Voltage - Supply               | 2.375V ~ 2.625V                                             |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                          |

| Package / Case                 | 560-LBGA Exposed Pad, Metal                                 |

| Supplier Device Package        | 560-MBGA (42.5x42.5)                                        |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xcv1000-5bg560i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

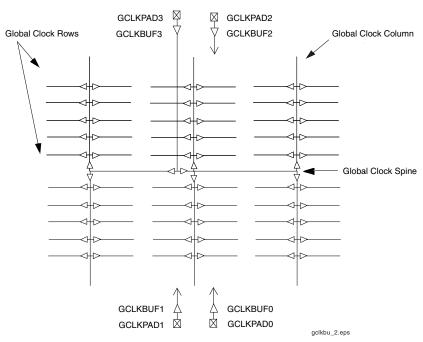

Four dedicated clock pads are provided, one adjacent to each of the global buffers. The input to the global buffer is

selected either from these pads or from signals in the general purpose routing.

Figure 9: Global Clock Distribution Network

#### Delay-Locked Loop (DLL)

Associated with each global clock input buffer is a fully digital Delay-Locked Loop (DLL) that can eliminate skew between the clock input pad and internal clock-input pins throughout the device. Each DLL can drive two global clock networks. The DLL monitors the input clock and the distributed clock, and automatically adjusts a clock delay element. Clock edges reach internal flip-flops one to four clock periods after they arrive at the input. This closed-loop system effectively eliminates clock-distribution delay by ensuring that clock edges arrive at internal flip-flops in synchronism with clock edges arriving at the input.

In addition to eliminating clock-distribution delay, the DLL provides advanced control of multiple clock domains. The DLL provides four quadrature phases of the source clock, can double the clock, or divide the clock by 1.5, 2, 2.5, 3, 4, 5, 8, or 16.

The DLL also operates as a clock mirror. By driving the output from a DLL off-chip and then back on again, the DLL can be used to de-skew a board level clock among multiple Virtex devices.

In order to guarantee that the system clock is operating correctly prior to the FPGA starting up after configuration, the DLL can delay the completion of the configuration process until after it has achieved lock.

See **DLL Timing Parameters**, page 21 of Module 3, for frequency range information.

## **Boundary Scan**

Virtex devices support all the mandatory boundary-scan instructions specified in the IEEE standard 1149.1. A Test Access Port (TAP) and registers are provided that implement the EXTEST, INTEST, SAMPLE/PRELOAD, BYPASS, IDCODE, USERCODE, and HIGHZ instructions. The TAP also supports two internal scan chains and configuration/readback of the device.The TAP uses dedicated package pins that always operate using LVTTL. For TDO to operate using LVTTL, the  $\rm V_{CCO}$  for Bank 2 should be 3.3 V. Otherwise, TDO switches rail-to-rail between ground and  $\rm V_{CCO}$ .

Boundary-scan operation is independent of individual IOB configurations, and unaffected by package type. All IOBs, including un-bonded ones, are treated as independent 3-state bidirectional pins in a single scan chain. Retention of the bidirectional test capability after configuration facilitates the testing of external interconnections, provided the user design or application is turned off.

Table 5 lists the boundary-scan instructions supported in Virtex FPGAs. Internal signals can be captured during EXTEST by connecting them to un-bonded or unused IOBs. They can also be connected to the unused outputs of IOBs defined as unidirectional input pins.

Before the device is configured, all instructions except USER1 and USER2 are available. After configuration, all instructions are available. During configuration, it is recommended that those operations using the boundary-scan register (SAMPLE/PRELOAD, INTEST, EXTEST) not be performed.

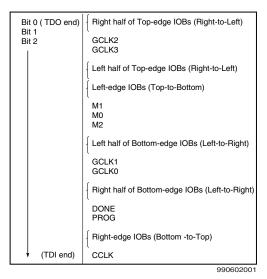

Figure 11: Boundary Scan Bit Sequence

Table 5: Boundary Scan Instructions

| Boundary-Scan<br>Command | Binary<br>Code(4:0) | Description                                              |

|--------------------------|---------------------|----------------------------------------------------------|

| EXTEST                   | 00000               | Enables boundary-scan EXTEST operation                   |

| SAMPLE/PRELOAD           | 00001               | Enables boundary-scan<br>SAMPLE/PRELOAD<br>operation     |

| USER 1                   | 00010               | Access user-defined register 1                           |

| USER 2                   | 00011               | Access user-defined register 2                           |

| CFG_OUT                  | 00100               | Access the configuration bus for read operations.        |

| CFG_IN                   | 00101               | Access the configuration bus for write operations.       |

| INTEST                   | 00111               | Enables boundary-scan INTEST operation                   |

| USERCODE                 | 01000               | Enables shifting out<br>USER code                        |

| IDCODE                   | 01001               | Enables shifting out of ID Code                          |

| HIGHZ                    | 01010               | 3-states output pins while enabling the Bypass Register  |

| JSTART                   | 01100               | Clock the start-up<br>sequence when<br>StartupClk is TCK |

| BYPASS                   | 11111               | Enables BYPASS                                           |

| RESERVED                 | All other codes     | Xilinx reserved instructions                             |

### Identification Registers

The IDCODE register is supported. By using the IDCODE, the device connected to the JTAG port can be determined.

The IDCODE register has the following binary format:

vvvv:ffff:fffa:aaaa:aaaa:cccc:cccc1

where

v = the die version number

f = the family code (03h for Virtex family)

a = the number of CLB rows (ranges from 010h for XCV50 to 040h for XCV1000)

c = the company code (49h for Xilinx)

The USERCODE register is supported. By using the USER-CODE, a user-programmable identification code can be loaded and shifted out for examination. The identification code is embedded in the bitstream during bitstream generation and is valid only after configuration.

Table 6: IDCODEs Assigned to Virtex FPGAs

| FPGA    | IDCODE    |

|---------|-----------|

| XCV50   | v0610093h |

| XCV100  | v0614093h |

| XCV150  | v0618093h |

| XCV200  | v061C093h |

| XCV300  | v0620093h |

| XCV400  | v0628093h |

| XCV600  | v0630093h |

| XCV800  | v0638093h |

| XCV1000 | v0640093h |

#### Including Boundary Scan in a Design

Since the boundary scan pins are dedicated, no special element needs to be added to the design unless an internal data register (USER1 or USER2) is desired.

If an internal data register is used, insert the boundary scan symbol and connect the necessary pins as appropriate.

# **Development System**

Virtex FPGAs are supported by the Xilinx Foundation and Alliance CAE tools. The basic methodology for Virtex design consists of three interrelated steps: design entry, implementation, and verification. Industry-standard tools are used for design entry and simulation (for example, Synopsys FPGA Express), while Xilinx provides proprietary architecture-specific tools for implementation.

The Xilinx development system is integrated under the Xilinx Design Manager (XDM™) software, providing design-

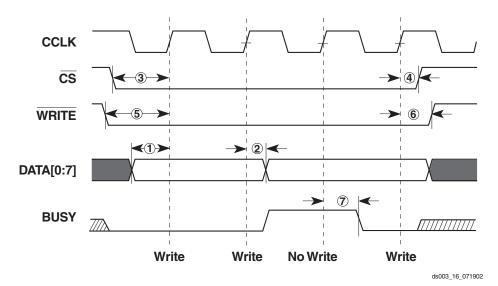

- At the rising edge of CCLK: If BUSY is Low, the data is accepted on this clock. If BUSY is High (from a previous write), the data is not accepted. Acceptance will instead occur on the first clock after BUSY goes Low, and the data must be held until this has happened.

- 4. Repeat steps 2 and 3 until all the data has been sent.

- 5. De-assert  $\overline{\text{CS}}$  and  $\overline{\text{WRITE}}$ .

A flowchart for the write operation appears in Figure 17. Note that if CCLK is slower than  $f_{\text{CCNH}}$ , the FPGA never asserts BUSY. In this case, the above handshake is unnecessary, and data can simply be entered into the FPGA every CCLK cycle.

Figure 16: Write Operations

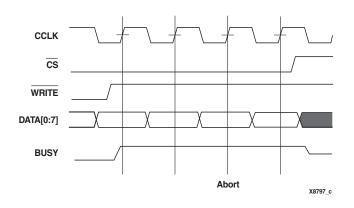

Figure 18: SelectMAP Write Abort Waveforms

## Boundary-Scan Mode

In the boundary-scan mode, configuration is done through the IEEE 1149.1 Test Access Port. Note that the PROGRAM pin must be pulled High prior to reconfiguration. A Low on the PROGRAM pin resets the TAP controller and no JTAG operations can be performed.

Configuration through the TAP uses the CFG\_IN instruction. This instruction allows data input on TDI to be converted into data packets for the internal configuration bus.

The following steps are required to configure the FPGA through the boundary-scan port (when using TCK as a start-up clock).

- Load the CFG\_IN instruction into the boundary-scan instruction register (IR)

- 2. Enter the Shift-DR (SDR) state

- 3. Shift a configuration bitstream into TDI

- 4. Return to Run-Test-Idle (RTI)

- 5. Load the JSTART instruction into IR

- 6. Enter the SDR state

- 7. Clock TCK through the startup sequence

- 8. Return to RTI

Configuration and readback via the TAP is always available. The boundary-scan mode is selected by a <101> or 001> on the mode pins (M2, M1, M0). For details on TAP characteristics, refer to XAPP139.

## **Configuration Sequence**

The configuration of Virtex devices is a three-phase process. First, the configuration memory is cleared. Next, configuration data is loaded into the memory, and finally, the logic is activated by a start-up process.

Configuration is automatically initiated on power-up unless it is delayed by the user, as described below. The configuration process can also be initiated by asserting  $\overline{\mathsf{PROGRAM}}$ .

The end of the memory-clearing phase is signalled by INIT going High, and the completion of the entire process is signalled by DONE going High.

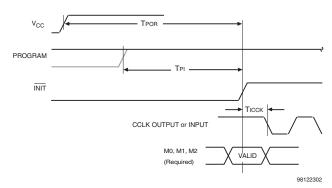

The power-up timing of configuration signals is shown in Figure 19. The corresponding timing characteristics are listed in Table 10.

Figure 19: Power-Up Timing Configuration Signals

Table 10: Power-up Timing Characteristics

| Description         | Symbol               | Value | Units   |

|---------------------|----------------------|-------|---------|

| Power-on Reset      | T <sub>POR</sub>     | 2.0   | ms, max |

| Program Latency     | T <sub>PL</sub>      | 100.0 | μs, max |

| CCLK (output) Delay | T <sub>ICCK</sub>    | 0.5   | μs, min |

|                     |                      | 4.0   | μs, max |

| Program Pulse Width | T <sub>PROGRAM</sub> | 300   | ns, min |

### **Delaying Configuration**

INIT can be held Low using an open-drain driver. An open-drain is required since INIT is a bidirectional open-drain pin that is held Low by the FPGA while the configuration memory is being cleared. Extending the time that the pin is Low causes the configuration sequencer to wait. Thus, configuration is delayed by preventing entry into the phase where data is loaded.

#### Start-Up Sequence

The default Start-up sequence is that one CCLK cycle after DONE goes High, the global 3-state signal (GTS) is released. This permits device outputs to turn on as necessary.

One CCLK cycle later, the Global Set/Reset (GSR) and Global Write Enable (GWE) signals are released. This permits the internal storage elements to begin changing state in response to the logic and the user clock.

The relative timing of these events can be changed. In addition, the GTS, GSR, and GWE events can be made dependent on the DONE pins of multiple devices all going High, forcing the devices to start in synchronism. The sequence can also be paused at any stage until lock has been achieved on any or all DLLs.

#### **Data Stream Format**

Virtex devices are configured by sequentially loading frames of data. Table 11 lists the total number of bits required to configure each device. For more detailed information, see application note XAPP151 "Virtex Configuration Architecture Advanced Users Guide".

Table 11: Virtex Bit-Stream Lengths

| Device  | # of Configuration Bits |

|---------|-------------------------|

| XCV50   | 559,200                 |

| XCV100  | 781,216                 |

| XCV150  | 1,040,096               |

| XCV200  | 1,335,840               |

| XCV300  | 1,751,808               |

| XCV400  | 2,546,048               |

| XCV600  | 3,607,968               |

| XCV800  | 4,715,616               |

| XCV1000 | 6,127,744               |

## Readback

The configuration data stored in the Virtex configuration memory can be readback for verification. Along with the configuration data it is possible to readback the contents all flip-flops/latches, LUTRAMs, and block RAMs. This capability is used for real-time debugging.

For more detailed information, see Application Note XAPP138: *Virtex FPGA Series Configuration and Readback*, available online at <a href="https://www.xilinx.com">www.xilinx.com</a>.

# **Revision History**

| Date  | Version | Revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11/98 | 1.0     | Initial Xilinx release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 01/99 | 1.2     | Updated package drawings and specs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 02/99 | 1.3     | Update of package drawings, updated specifications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 05/99 | 1.4     | Addition of package drawings and specifications.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 05/99 | 1.5     | Replaced FG 676 & FG680 package drawings.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 07/99 | 1.6     | Changed Boundary Scan Information and changed Figure 11, Boundary Scan Bit Sequence. Updated IOB Input & Output delays. Added Capacitance info for different I/O Standards. Added 5 V tolerant information. Added DLL Parameters and waveforms and new Pin-to-pin Input and Output Parameter tables for Global Clock Input to Output and Setup and Hold. Changed Configuration Information including Figures 12, 14, 17 & 19. Added device-dependent listings for quiescent currents ICCINTQ and ICCOQ. Updated IOB Input and Output Delays based on default standard of LVTTL, 12 mA, Fast Slew Rate. Added IOB Input Switching Characteristics Standard Adjustments. |

| 09/99 | 1.7     | Speed grade update to preliminary status, Power-on specification and Clock-to-Out Minimums additions, "0" hold time listing explanation, quiescent current listing update, and Figure 6 ADDRA input label correction. Added T <sub>IJITCC</sub> parameter, changed T <sub>OJIT</sub> to T <sub>OPHASE</sub> .                                                                                                                                                                                                                                                                                                                                                          |

| 01/00 | 1.8     | Update to speed.txt file 1.96. Corrections for CRs 111036,111137, 112697, 115479, 117153, 117154, and 117612. Modified notes for Recommended Operating Conditions (voltage and temperature). Changed Bank information for V <sub>CCO</sub> in CS144 package on p.43.                                                                                                                                                                                                                                                                                                                                                                                                   |

## **CLB Switching Characteristics**

Delays originating at F/G inputs vary slightly according to the input used. The values listed below are worst-case. Precise values are provided by the timing analyzer.

|                                                                      |                                          | Speed Grade |           |         |         |         |

|----------------------------------------------------------------------|------------------------------------------|-------------|-----------|---------|---------|---------|

| Description                                                          | Symbol                                   | Min         | -6        | -5      | -4      | Units   |

| Combinatorial Delays                                                 |                                          | •           |           |         |         |         |

| 4-input function: F/G inputs to X/Y outputs                          | T <sub>ILO</sub>                         | 0.29        | 0.6       | 0.7     | 0.8     | ns, max |

| 5-input function: F/G inputs to F5 output                            | T <sub>IF5</sub>                         | 0.32        | 0.7       | 0.8     | 0.9     | ns, max |

| 5-input function: F/G inputs to X output                             | T <sub>IF5X</sub>                        | 0.36        | 0.8       | 0.8     | 1.0     | ns, max |

| 6-input function: F/G inputs to Y output via F6 MUX                  | T <sub>IF6Y</sub>                        | 0.44        | 0.9       | 1.0     | 1.2     | ns, max |

| 6-input function: F5IN input to Y output                             | T <sub>F5INY</sub>                       | 0.17        | 0.32      | 0.36    | 0.42    | ns, max |

| Incremental delay routing through transparent latch to XQ/YQ outputs | T <sub>IFNCTL</sub>                      | 0.31        | 0.7       | 0.7     | 0.8     | ns, max |

| BY input to YB output                                                | T <sub>BYYB</sub>                        | 0.27        | 0.53      | 0.6     | 0.7     | ns, max |

| Sequential Delays                                                    |                                          |             |           |         |         | T.      |

| FF Clock CLK to XQ/YQ outputs                                        | T <sub>CKO</sub>                         | 0.54        | 1.1       | 1.2     | 1.4     | ns, max |

| Latch Clock CLK to XQ/YQ outputs                                     | T <sub>CKLO</sub>                        | 0.6         | 1.2       | 1.4     | 1.6     | ns, max |

| Setup and Hold Times before/after Clock CLK <sup>(1)</sup>           |                                          | Setup T     | ime / Hol | d Time  |         |         |

| 4-input function: F/G Inputs                                         | T <sub>ICK</sub> /T <sub>CKI</sub>       | 0.6 / 0     | 1.2 / 0   | 1.4 / 0 | 1.5 / 0 | ns, min |

| 5-input function: F/G inputs                                         | T <sub>IF5CK</sub> /T <sub>CKIF5</sub>   | 0.7 / 0     | 1.3 / 0   | 1.5 / 0 | 1.7 / 0 | ns, min |

| 6-input function: F5IN input                                         | T <sub>F5INCK</sub> /T <sub>CKF5IN</sub> | 0.46 / 0    | 1.0 / 0   | 1.1 / 0 | 1.2 / 0 | ns, min |

| 6-input function: F/G inputs via F6 MUX                              | T <sub>IF6CK</sub> /T <sub>CKIF6</sub>   | 0.8 / 0     | 1.5 / 0   | 1.7 / 0 | 1.9 / 0 | ns, min |

| BX/BY inputs                                                         | $T_{DICK}/T_{CKDI}$                      | 0.30 / 0    | 0.6 / 0   | 0.7 / 0 | 0.8 / 0 | ns, min |

| CE input                                                             | $T_{CECK}/T_{CKCE}$                      | 0.37 / 0    | 0.8 / 0   | 0.9 / 0 | 1.0 / 0 | ns, min |

| SR/BY inputs (synchronous)                                           | $T_{RCK}T_{CKR}$                         | 0.33 / 0    | 0.7 / 0   | 0.8 / 0 | 0.9 / 0 | ns, min |

| Clock CLK                                                            |                                          |             |           |         |         |         |

| Minimum Pulse Width, High                                            | T <sub>CH</sub>                          | 0.8         | 1.5       | 1.7     | 2.0     | ns, min |

| Minimum Pulse Width, Low                                             | $T_CL$                                   | 0.8         | 1.5       | 1.7     | 2.0     | ns, min |

| Set/Reset                                                            |                                          |             |           |         |         |         |

| Minimum Pulse Width, SR/BY inputs                                    | T <sub>RPW</sub>                         | 1.3         | 2.5       | 2.8     | 3.3     | ns, min |

| Delay from SR/BY inputs to XQ/YQ outputs (asynchronous)              | T <sub>RQ</sub>                          | 0.54        | 1.1       | 1.3     | 1.4     | ns, max |

| Delay from GSR to XQ/YQ outputs                                      | T <sub>IOGSRQ</sub>                      | 4.9         | 9.7       | 10.9    | 12.5    | ns, max |

| Toggle Frequency (MHz) (for export control)                          | F <sub>TOG</sub> (MHz)                   | 625         | 333       | 294     | 250     | MHz     |

#### Notes:

<sup>1.</sup> A Zero "0" Hold Time listing indicates no hold time or a negative hold time. Negative values cannot be guaranteed "best-case", but if a "0" is listed, there is no positive hold time.

## **CLB Arithmetic Switching Characteristics**

Setup times not listed explicitly can be approximated by decreasing the combinatorial delays by the setup time adjustment listed. Precise values are provided by the timing analyzer.

|                                                            | Speed Grade                          |          |             |           |         |         |

|------------------------------------------------------------|--------------------------------------|----------|-------------|-----------|---------|---------|

| Description                                                | Symbol                               | Min      | -6          | -5        | -4      | Units   |

| Combinatorial Delays                                       |                                      |          |             |           | •       | •       |

| F operand inputs to X via XOR                              | T <sub>OPX</sub>                     | 0.37     | 0.8         | 0.9       | 1.0     | ns, max |

| F operand input to XB output                               | T <sub>OPXB</sub>                    | 0.54     | 1.1         | 1.3       | 1.4     | ns, max |

| F operand input to Y via XOR                               | T <sub>OPY</sub>                     | 0.8      | 1.5         | 1.7       | 2.0     | ns, max |

| F operand input to YB output                               | T <sub>OPYB</sub>                    | 0.8      | 1.5         | 1.7       | 2.0     | ns, max |

| F operand input to COUT output                             | T <sub>OPCYF</sub>                   | 0.6      | 1.2         | 1.3       | 1.5     | ns, max |

| G operand inputs to Y via XOR                              | T <sub>OPGY</sub>                    | 0.46     | 1.0         | 1.1       | 1.2     | ns, max |

| G operand input to YB output                               | T <sub>OPGYB</sub>                   | 0.8      | 1.6         | 1.8       | 2.1     | ns, max |

| G operand input to COUT output                             | T <sub>OPCYG</sub>                   | 0.7      | 1.3         | 1.4       | 1.6     | ns, max |

| BX initialization input to COUT                            | T <sub>BXCY</sub>                    | 0.41     | 0.9         | 1.0       | 1.1     | ns, max |

| CIN input to X output via XOR                              | T <sub>CINX</sub>                    | 0.21     | 0.41        | 0.46      | 0.53    | ns, max |

| CIN input to XB                                            | T <sub>CINXB</sub>                   | 0.02     | 0.04        | 0.05      | 0.06    | ns, max |

| CIN input to Y via XOR                                     | T <sub>CINY</sub>                    | 0.23     | 0.46        | 0.52      | 0.6     | ns, max |

| CIN input to YB                                            | T <sub>CINYB</sub>                   | 0.23     | 0.45        | 0.51      | 0.6     | ns, max |

| CIN input to COUT output                                   | T <sub>BYP</sub>                     | 0.05     | 0.09        | 0.10      | 0.11    | ns, max |

| Multiplier Operation                                       |                                      |          |             |           |         | •       |

| F1/2 operand inputs to XB output via AND                   | T <sub>FANDXB</sub>                  | 0.18     | 0.36        | 0.40      | 0.46    | ns, max |

| F1/2 operand inputs to YB output via AND                   | T <sub>FANDYB</sub>                  | 0.40     | 0.8         | 0.9       | 1.1     | ns, max |

| F1/2 operand inputs to COUT output via AND                 | T <sub>FANDCY</sub>                  | 0.22     | 0.43        | 0.48      | 0.6     | ns, max |

| G1/2 operand inputs to YB output via AND                   | T <sub>GANDYB</sub>                  | 0.25     | 0.50        | 0.6       | 0.7     | ns, max |

| G1/2 operand inputs to COUT output via AND                 | T <sub>GANDCY</sub>                  | 0.07     | 0.13        | 0.15      | 0.17    | ns, max |

| Setup and Hold Times before/after Clock CLK <sup>(1)</sup> |                                      | Set      | up Time / F | lold Time | •       | •       |

| CIN input to FFX                                           | T <sub>CCKX</sub> /T <sub>CKCX</sub> | 0.50 / 0 | 1.0 / 0     | 1.2 / 0   | 1.3 / 0 | ns, min |

| CIN input to FFY                                           | T <sub>CCKY</sub> /T <sub>CKCY</sub> | 0.53 / 0 | 1.1 / 0     | 1.2 / 0   | 1.4 / 0 | ns, min |

#### Notes:

<sup>1.</sup> A Zero "0" Hold Time listing indicates no hold time or a negative hold time. Negative values can not be guaranteed "best-case", but if a "0" is listed, there is no positive hold time.

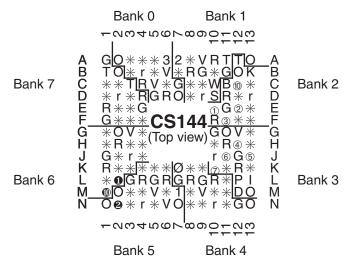

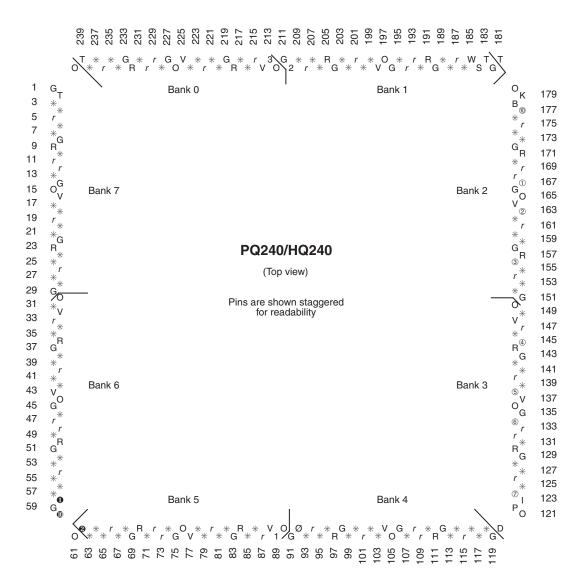

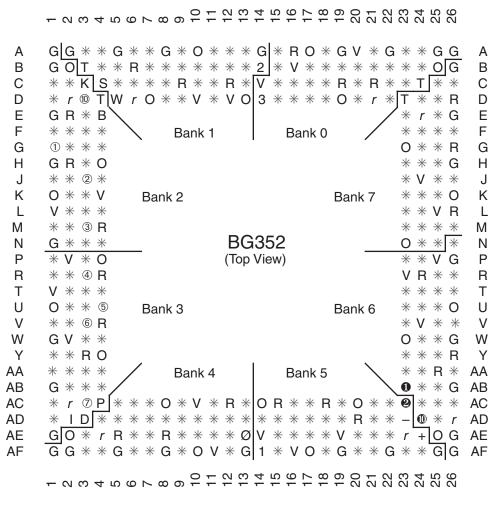

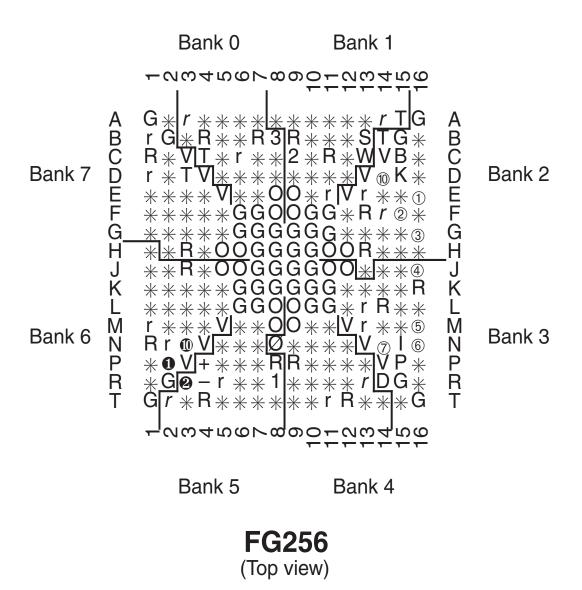

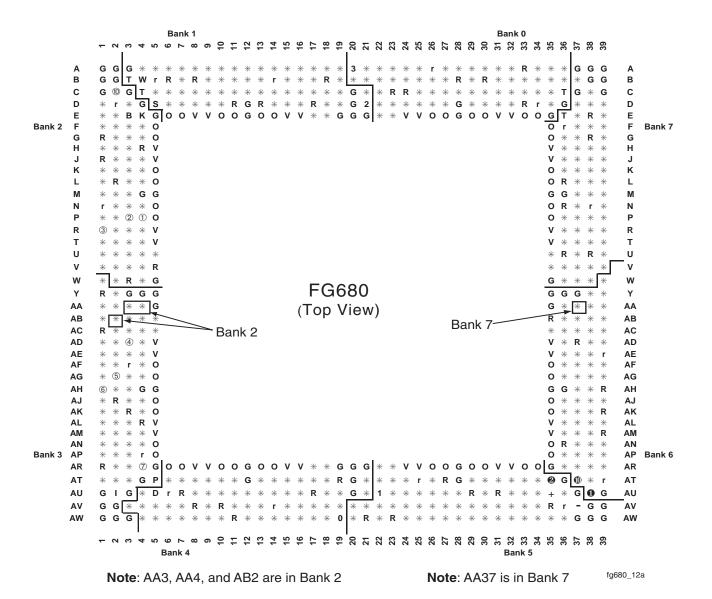

## **Virtex Pinout Information**

### **Pinout Tables**

See <a href="https://www.xilinx.com">www.xilinx.com</a> for updates or additional pinout information. For convenience, Table 2, Table 3 and Table 4 list the locations of special-purpose and power-supply pins. Pins not listed are either user I/Os or not connected, depending on the device/package combination. See the Pinout Diagrams starting on page 17 for any pins not listed for a particular part/package combination.

Table 2: Virtex Pinout Tables (Chip-Scale and QFP Packages)

| Pin Name           | Device | CS144                              | TQ144                              | PQ/HQ240                                              |

|--------------------|--------|------------------------------------|------------------------------------|-------------------------------------------------------|

| GCK0               | All    | K7                                 | 90                                 | 92                                                    |

| GCK1               | All    | M7                                 | 93                                 | 89                                                    |

| GCK2               | All    | A7                                 | 19                                 | 210                                                   |

| GCK3               | All    | A6                                 | 16                                 | 213                                                   |

| MO                 | All    | M1                                 | 110                                | 60                                                    |

| M1                 | All    | L2                                 | 112                                | 58                                                    |

| M2                 | All    | N2                                 | 108                                | 62                                                    |

| CCLK               | All    | B13                                | 38                                 | 179                                                   |

| PROGRAM            | All    | L12                                | 72                                 | 122                                                   |

| DONE               | All    | M12                                | 74                                 | 120                                                   |

| INIT               | All    | L13                                | 71                                 | 123                                                   |

| BUSY/DOUT          | All    | C11                                | 39                                 | 178                                                   |

| D0/DIN             | All    | C12                                | 40                                 | 177                                                   |

| D1                 | All    | E10                                | 45                                 | 167                                                   |

| D2                 | All    | E12                                | 47                                 | 163                                                   |

| D3                 | All    | F11                                | 51                                 | 156                                                   |

| D4                 | All    | H12                                | 59                                 | 145                                                   |

| D5                 | All    | J13                                | 63                                 | 138                                                   |

| D6                 | All    | J11                                | 65                                 | 134                                                   |

| D7                 | All    | K10                                | 70                                 | 124                                                   |

| WRITE              | All    | C10                                | 32                                 | 185                                                   |

| CS                 | All    | D10                                | 33                                 | 184                                                   |

| TDI                | All    | A11                                | 34                                 | 183                                                   |

| TDO                | All    | A12                                | 36                                 | 181                                                   |

| TMS                | All    | B1                                 | 143                                | 2                                                     |

| TCK                | All    | C3                                 | 2                                  | 239                                                   |

| V <sub>CCINT</sub> | All    | A9, B6, C5, G3,<br>G12, M5, M9, N6 | 10, 15, 25, 57, 84, 94,<br>99, 126 | 16, 32, 43, 77, 88, 104, 137, 148, 164, 198, 214, 225 |

Table 2: Virtex Pinout Tables (Chip-Scale and QFP Packages) (Continued)

| Pin Name                                                                                                           | Device     | CS144                                                                              | TQ144                                                         | PQ/HQ240                                                                                               |

|--------------------------------------------------------------------------------------------------------------------|------------|------------------------------------------------------------------------------------|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| V <sub>cco</sub>                                                                                                   | All        | Banks 0 and 1:<br>A2, A13, D7<br>Banks 2 and 3:<br>B12, G11, M13<br>Banks 4 and 5: | No I/O Banks in this package: 1, 17, 37, 55, 73, 92, 109, 128 | No I/O Banks in this package: 15, 30, 44, 61, 76, 90, 105, 121, 136, 150, 165, 180, 197, 212, 226, 240 |

|                                                                                                                    |            | N1, N7, N13  Banks 6 and 7: B2, G2, M2                                             |                                                               |                                                                                                        |

| V <sub>REF</sub> , Bank 0                                                                                          | XCV50      | C4, D6                                                                             | 5, 13                                                         | 218, 232                                                                                               |

| (V <sub>REF</sub> pins are listed                                                                                  | XCV100/150 | + B4                                                                               | + 7                                                           | + 229                                                                                                  |

| incrementally. Connect all pins listed for both                                                                    | XCV200/300 | N/A                                                                                | N/A                                                           | + 236                                                                                                  |

| the required device                                                                                                | XCV400     | N/A                                                                                | N/A                                                           | + 215                                                                                                  |

| and all smaller devices listed in the same                                                                         | XCV600     | N/A                                                                                | N/A                                                           | + 230                                                                                                  |

| package.)                                                                                                          | XCV800     | N/A                                                                                | N/A                                                           | + 222                                                                                                  |

| Within each bank, if input reference voltage is not required, all V <sub>REF</sub> pins are general I/O.           |            |                                                                                    |                                                               |                                                                                                        |

| V <sub>REF</sub> , Bank 1                                                                                          | XCV50      | A10, B8                                                                            | 22, 30                                                        | 191, 205                                                                                               |

| (V <sub>REF</sub> pins are listed                                                                                  | XCV100/150 | + D9                                                                               | + 28                                                          | + 194                                                                                                  |

| incrementally. Connect all pins listed for both                                                                    | XCV200/300 | N/A                                                                                | N/A                                                           | + 187                                                                                                  |

| the required device and all smaller devices                                                                        | XCV400     | N/A                                                                                | N/A                                                           | + 208                                                                                                  |

| listed in the same                                                                                                 | XCV600     | N/A                                                                                | N/A                                                           | + 193                                                                                                  |

| package.) Within each bank, if input reference voltage is not required, all V <sub>REF</sub> pins are general I/O. | XCV800     | N/A                                                                                | N/A                                                           | + 201                                                                                                  |

| V <sub>REF</sub> , Bank 2                                                                                          | XCV50      | D11, F10                                                                           | 42, 50                                                        | 157, 171                                                                                               |

| (V <sub>REF</sub> pins are listed                                                                                  | XCV100/150 | + D13                                                                              | + 44                                                          | + 168                                                                                                  |

| incrementally. Connect all pins listed for both                                                                    | XCV200/300 | N/A                                                                                | N/A                                                           | + 175                                                                                                  |

| the required device and all smaller devices                                                                        | XCV400     | N/A                                                                                | N/A                                                           | + 154                                                                                                  |

| listed in the same                                                                                                 | XCV600     | N/A                                                                                | N/A                                                           | + 169                                                                                                  |

| package.) Within each bank, if input reference voltage is not required, all V <sub>REF</sub> pins are general I/O. | XCV800     | N/A                                                                                | N/A                                                           | + 161                                                                                                  |

Table 3: Virtex Pinout Tables (BGA) (Continued)

| Pin Name                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Device              | BG256                                                                | BG352                                                                                                                         | BG432                                                                                                                                                                      | BG560                                                                                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCCINT  Notes:  Superset includes all pins, including the ones in bold type. Subset excludes pins in bold type.  In BG352, for XCV300 all the VCINT pins in the superset must be connected. For XCV150/200, VCINT pins in the subset must be connected, and pins in bold type can be left unconnected (these unconnected pins cannot be used as user I/O.)  In BG432, for XCV400/600/800 all VCINT pins in the superset must be                                        | XCV50/100           | C10, D6,<br>D15, F4,<br>F17, L3,<br>L18, R4,<br>R17, U6,<br>U15, V10 | N/A                                                                                                                           | N/A                                                                                                                                                                        | N/A                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | XCV150/200/300      | Same as<br>above                                                     | A20, C14,<br>D10, J24,<br>K4, P2, P25,<br>V24, W2,<br>AC10, AE14,<br>AE19,<br>B16, D12,<br>L1, L25,<br>R23, T1,<br>AF11, AF16 | A10, A17, B23,<br>C14, C19, K3,<br>K29, N2, N29,<br>T1, T29, W2,<br>W31, AB2,<br>AB30, AJ10,<br>AJ16, AK13,<br>AK19, AK22,<br>B26, C7, F1,<br>F30, AE29, AF1,<br>AH8, AH24 | N/A                                                                                                                                                                                                                              |

| connected. For XCV300, V <sub>CCINT</sub> pins in the subset must be connected, and pins in <b>bold</b> type can be left unconnected (these unconnected pins cannot be used as user I/O.)  In BG560, for XCV800/1000 all V <sub>CCINT</sub> pins in the superset must be connected. For XCV400/600, V <sub>CCINT</sub> pins in the subset must be connected, and pins in <b>bold</b> type can be left unconnected (these unconnected pins cannot be used as user I/O.) | XCV400/600/800/1000 | N/A                                                                  | N/A                                                                                                                           | Same as above                                                                                                                                                              | A21, B14, B18,<br>B28, C24, E9,<br>E12, F2, H30,<br>J1, K32, N1,<br>N33, U5, U30,<br>Y2, Y31, AD2,<br>AD32, AG3,<br>AG31, AK8,<br>AK11, AK17,<br>AK20, AL14,<br>AL27, AN25,<br>B12, C22, M3,<br>N29, AB2,<br>AB32, AJ13,<br>AL22 |

| V <sub>CCO</sub> , Bank 0                                                                                                                                                                                                                                                                                                                                                                                                                                              | All                 | D7, D8                                                               | A17, B25,<br>D19                                                                                                              | A21, C29, D21                                                                                                                                                              | A22, A26, A30,<br>B19, B32                                                                                                                                                                                                       |

| V <sub>CCO</sub> , Bank 1                                                                                                                                                                                                                                                                                                                                                                                                                                              | All                 | D13, D14                                                             | A10, D7,<br>D13                                                                                                               | A1, A11, D11                                                                                                                                                               | A10, A16, B13,<br>C3, E5                                                                                                                                                                                                         |

| V <sub>CCO</sub> , Bank 2                                                                                                                                                                                                                                                                                                                                                                                                                                              | All                 | G17, H17                                                             | B2, H4, K1                                                                                                                    | C3, L1, L4                                                                                                                                                                 | B2, D1, H1, M1,<br>R2                                                                                                                                                                                                            |

| V <sub>CCO</sub> , Bank 3                                                                                                                                                                                                                                                                                                                                                                                                                                              | All                 | N17, P17                                                             | P4, U1, Y4                                                                                                                    | AA1, AA4, AJ3                                                                                                                                                              | V1, AA2, AD1,<br>AK1, AL2                                                                                                                                                                                                        |

| V <sub>CCO</sub> , Bank 4                                                                                                                                                                                                                                                                                                                                                                                                                                              | All                 | U13, U14                                                             | AC8, AE2,<br>AF10                                                                                                             | AH11, AL1,<br>AL11                                                                                                                                                         | AM2, AM15,<br>AN4, AN8, AN12                                                                                                                                                                                                     |

| V <sub>CCO</sub> , Bank 5                                                                                                                                                                                                                                                                                                                                                                                                                                              | All                 | U7, U8                                                               | AC14, AC20,<br>AF17                                                                                                           | AH21, AJ29,<br>AL21                                                                                                                                                        | AL31, AM21,<br>AN18, AN24,<br>AN30                                                                                                                                                                                               |

| V <sub>CCO</sub> , Bank 6                                                                                                                                                                                                                                                                                                                                                                                                                                              | All                 | N4, P4                                                               | U26, W23,<br>AE25                                                                                                             | AA28, AA31,<br>AL31                                                                                                                                                        | W32, AB33,<br>AF33, AK33,<br>AM32                                                                                                                                                                                                |

Table 3: Virtex Pinout Tables (BGA) (Continued)

| Pin Name                                                                                    | Device     | BG256                                                                                                                                            | BG352                                                                                                                                                                                    | BG432                                                                                                                                                                                                                                        | BG560                                                                                                                                                                                                                                                                                                         |

|---------------------------------------------------------------------------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>REF</sub> Bank 7                                                                     | XCV50      | G3, H1                                                                                                                                           | N/A                                                                                                                                                                                      | N/A                                                                                                                                                                                                                                          | N/A                                                                                                                                                                                                                                                                                                           |

| (V <sub>REF</sub> pins are listed                                                           | XCV100/150 | + D1                                                                                                                                             | D26, G26,                                                                                                                                                                                | N/A                                                                                                                                                                                                                                          | N/A                                                                                                                                                                                                                                                                                                           |

| incrementally. Connect all pins listed for both the                                         |            |                                                                                                                                                  | L26                                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                               |

| required device and all                                                                     | XCV200/300 | + B2                                                                                                                                             | + E24                                                                                                                                                                                    | F28, F31,                                                                                                                                                                                                                                    | N/A                                                                                                                                                                                                                                                                                                           |

| smaller devices listed in the same package.)                                                |            |                                                                                                                                                  |                                                                                                                                                                                          | J30, N30                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                               |

| Within each bank, if input reference voltage is not required, all V <sub>REF</sub> pins are | XCV400     | N/A                                                                                                                                              | N/A                                                                                                                                                                                      | + R31                                                                                                                                                                                                                                        | E31, G31, K31,<br>P31, T31                                                                                                                                                                                                                                                                                    |

| general I/O.                                                                                | XCV600     | N/A                                                                                                                                              | N/A                                                                                                                                                                                      | + J28                                                                                                                                                                                                                                        | + H32                                                                                                                                                                                                                                                                                                         |

|                                                                                             | XCV800     | N/A                                                                                                                                              | N/A                                                                                                                                                                                      | + M28                                                                                                                                                                                                                                        | + L33                                                                                                                                                                                                                                                                                                         |

|                                                                                             | XCV1000    | N/A                                                                                                                                              | N/A                                                                                                                                                                                      | N/A                                                                                                                                                                                                                                          | + D31                                                                                                                                                                                                                                                                                                         |

| GND                                                                                         | All        | C3, C18, D4, D5, D9, D10, D11, D12, D16, D17, E4, E17, J4, J17, K4, K17, L4, L17, M4, M17, T4, T17, U4, U5, U9, U10, U11, U12, U16, U17, V3, V18 | A1, A2, A5,<br>A8, A14,<br>A19, A22,<br>A25, A26,<br>B1, B26, E1,<br>E26, H1,<br>H26, N1,<br>P26, W1,<br>W26, AB1,<br>AB26, AF1,<br>AF2, AF5,<br>AF8, AF13,<br>AF19, AF22,<br>AF25, AF26 | A2, A3, A7, A9, A14, A18, A23, A25, A29, A30, B1, B2, B30, B31, C1, C31, D16, G1, G31, J1, J31, P1, P31, T4, T28, V1, V31, AC1, AC31, AE1, AE31, AH16, AJ1, AJ31, AK1, AK2, AK30, AK31, AL2, AL3, AL7, AL9 AL14, AL18 AL23, AL25, AL29, AL30 | A1, A7, A12, A14, A18, A20, A24, A29, A32, A33, B1, B6, B9, B15, B23, B27, B31, C2, E1, F32, G2, G33, J32, K1, L2, M33, P1, P33, R32, T1, V33, W2, Y1, Y33, AB1, AC32, AD33, AE2, AG1, AG32, AH2, AJ33, AL32, AM3, AM7, AM11, AM19, AM25, AM28, AM33, AN1, AN2, AN5, AN10, AN14, AN16, AN20, AN22, AN27, AN33 |

| GND <sup>(1)</sup>                                                                          | All        | J9, J10,<br>J11, J12,<br>K9, K10,<br>K11, K12,<br>L9, L10,<br>L11, L12,<br>M9, M10,<br>M11, M12                                                  | N/A                                                                                                                                                                                      | N/A                                                                                                                                                                                                                                          | N/A                                                                                                                                                                                                                                                                                                           |

| No Connect                                                                                  | All        | N/A                                                                                                                                              | N/A                                                                                                                                                                                      | N/A                                                                                                                                                                                                                                          | C31, AC2, AK4,<br>AL3                                                                                                                                                                                                                                                                                         |

### Notes:

1. 16 extra balls (grounded) at package center.

Table 4: Virtex Pinout Tables (Fine-Pitch BGA)

| Pin Name  | Device | FG256 | FG456 | FG676 | FG680 |

|-----------|--------|-------|-------|-------|-------|

| GCK0      | All    | N8    | W12   | AA14  | AW19  |

| GCK1      | All    | R8    | Y11   | AB13  | AU22  |

| GCK2      | All    | C9    | A11   | C13   | D21   |

| GCK3      | All    | B8    | C11   | E13   | A20   |

| M0        | All    | N3    | AB2   | AD4   | AT37  |

| M1        | All    | P2    | U5    | W7    | AU38  |

| M2        | All    | R3    | Y4    | AB6   | AT35  |

| CCLK      | All    | D15   | B22   | D24   | E4    |

| PROGRAM   | All    | P15   | W20   | AA22  | AT5   |

| DONE      | All    | R14   | Y19   | AB21  | AU5   |

| INIT      | All    | N15   | V19   | Y21   | AU2   |

| BUSY/DOUT | All    | C15   | C21   | E23   | E3    |

| D0/DIN    | All    | D14   | D20   | F22   | C2    |

| D1        | All    | E16   | H22   | K24   | P4    |

| D2        | All    | F15   | H20   | K22   | P3    |

| D3        | All    | G16   | K20   | M22   | R1    |

| D4        | All    | J16   | N22   | R24   | AD3   |

| D5        | All    | M16   | R21   | U23   | AG2   |

| D6        | All    | N16   | T22   | V24   | AH1   |

| D7        | All    | N14   | Y21   | AB23  | AR4   |

| WRITE     | All    | C13   | A20   | C22   | B4    |

| CS        | All    | B13   | C19   | E21   | D5    |

| TDI       | All    | A15   | B20   | D22   | В3    |

| TDO       | All    | B14   | A21   | C23   | C4    |

| TMS       | All    | D3    | D3    | F5    | E36   |

| TCK       | All    | C4    | C4    | E6    | C36   |

| DXN       | All    | R4    | Y5    | AB7   | AV37  |

| DXP       | All    | P4    | V6    | Y8    | AU35  |

Table 4: Virtex Pinout Tables (Fine-Pitch BGA) (Continued)

| Pin Name                                                                                                                                                                                                | Device     | FG256   | FG456               | FG676                              | FG680                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------|---------------------|------------------------------------|------------------------------------------|

| V <sub>REF</sub> Bank 4                                                                                                                                                                                 | XCV50      | P9, T12 | N/A                 | N/A                                | N/A                                      |

| (V <sub>REF</sub> pins are listed incrementally. Connect                                                                                                                                                | XCV100/150 | + T11   | AA13, AB16,<br>AB19 | N/A                                | N/A                                      |

| all pins listed for both the required device and                                                                                                                                                        | XCV200/300 | + R13   | + AB20              | N/A                                | N/A                                      |

| all smaller devices<br>listed in the same<br>package.)                                                                                                                                                  | XCV400     | N/A     | N/A                 | AC15, AD18,<br>AD21, AD22,<br>AF15 | N/A                                      |

| Within each bank, if input reference voltage is not required, all V <sub>REF</sub> pins are general I/O.                                                                                                | XCV600     | N/A     | N/A                 | + AF20                             | AT19, AU7,<br>AU17, AV8,<br>AV10, AW11   |

| pins are general i/o.                                                                                                                                                                                   | XCV800     | N/A     | N/A                 | + AF17                             | + AV14                                   |

|                                                                                                                                                                                                         | XCV1000    | N/A     | N/A                 | N/A                                | + AU6                                    |

| V <sub>REF</sub> Bank 5                                                                                                                                                                                 | XCV50      | T4, P8  | N/A                 | N/A                                | N/A                                      |

| (V <sub>REF</sub> pins are listed                                                                                                                                                                       | XCV100/150 | + R5    | W8, Y10, AA5        | N/A                                | N/A                                      |