Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 3456                                                       |

| Number of Logic Elements/Cells | 15552                                                      |

| Total RAM Bits                 | 98304                                                      |

| Number of I/O                  | 512                                                        |

| Number of Gates                | 661111                                                     |

| Voltage - Supply               | 2.375V ~ 2.625V                                            |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                         |

| Package / Case                 | 680-LBGA Exposed Pad                                       |

| Supplier Device Package        | 680-FTEBGA (40x40)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/xcv600-5fg680i |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Virtex Architecture**

Virtex devices feature a flexible, regular architecture that comprises an array of configurable logic blocks (CLBs) surrounded by programmable input/output blocks (IOBs), all interconnected by a rich hierarchy of fast, versatile routing resources. The abundance of routing resources permits the Virtex family to accommodate even the largest and most complex designs.

Virtex FPGAs are SRAM-based, and are customized by loading configuration data into internal memory cells. In some modes, the FPGA reads its own configuration data from an external PROM (master serial mode). Otherwise, the configuration data is written into the FPGA (Select-MAP<sup>TM</sup>, slave serial, and JTAG modes).

The standard Xilinx Foundation™ and Alliance Series™ Development systems deliver complete design support for Virtex, covering every aspect from behavioral and schematic entry, through simulation, automatic design translation and implementation, to the creation, downloading, and readback of a configuration bit stream.

### **Higher Performance**

Virtex devices provide better performance than previous generations of FPGA. Designs can achieve synchronous system clock rates up to 200 MHz including I/O. Virtex inputs and outputs comply fully with PCI specifications, and interfaces can be implemented that operate at 33 MHz or 66 MHz. Additionally, Virtex supports the hot-swapping requirements of Compact PCI.

Xilinx thoroughly benchmarked the Virtex family. While performance is design-dependent, many designs operated internally at speeds in excess of 100 MHz and can achieve 200 MHz. Table 2 shows performance data for representative circuits, using worst-case timing parameters.

Table 2: Performance for Common Circuit Functions

| Function              | Bits    | Virtex -6 |

|-----------------------|---------|-----------|

| Register-to-Register  |         |           |

| Adder                 | 16      | 5.0 ns    |

| Audei                 | 64      | 7.2 ns    |

| Pipelined Multiplier  | 8 x 8   | 5.1 ns    |

|                       | 16 x 16 | 6.0 ns    |

| Address Decoder       | 16      | 4.4 ns    |

|                       | 64      | 6.4 ns    |

| 16:1 Multiplexer      |         | 5.4 ns    |

| Parity Tree           | 9       | 4.1 ns    |

|                       | 18      | 5.0 ns    |

|                       | 36      | 6.9 ns    |

| Chip-to-Chip          |         |           |

| HSTL Class IV         |         | 200 MHz   |

| LVTTL,16mA, fast slew |         | 180 MHz   |

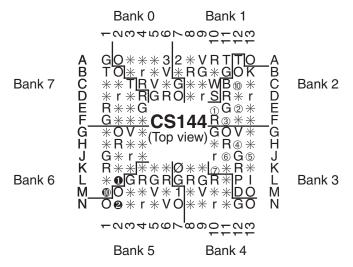

### Virtex Device/Package Combinations and Maximum I/O

Table 3: Virtex Family Maximum User I/O by Device/Package (Excluding Dedicated Clock Pins)

| Package | XCV50 | XCV100 | XCV150 | XCV200 | XCV300 | XCV400 | XCV600 | XCV800 | XCV1000 |

|---------|-------|--------|--------|--------|--------|--------|--------|--------|---------|

| CS144   | 94    | 94     |        |        |        |        |        |        |         |

| TQ144   | 98    | 98     |        |        |        |        |        |        |         |

| PQ240   | 166   | 166    | 166    | 166    | 166    |        |        |        |         |

| HQ240   |       |        |        |        |        | 166    | 166    | 166    |         |

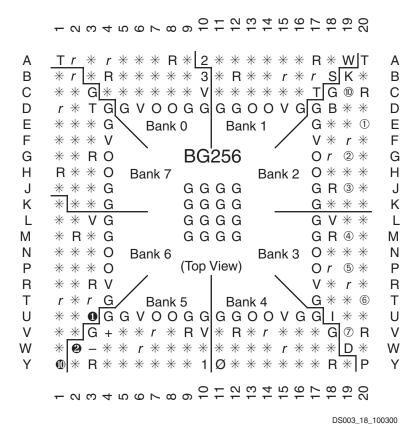

| BG256   | 180   | 180    | 180    | 180    |        |        |        |        |         |

| BG352   |       |        | 260    | 260    | 260    |        |        |        |         |

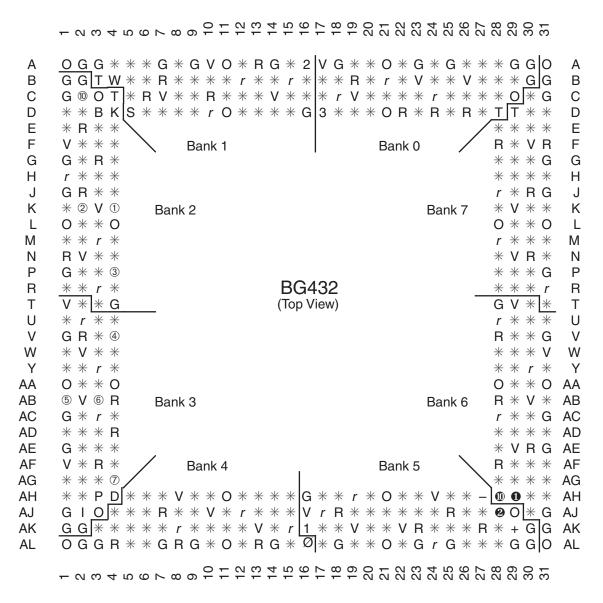

| BG432   |       |        |        |        | 316    | 316    | 316    | 316    |         |

| BG560   |       |        |        |        |        | 404    | 404    | 404    | 404     |

| FG256   | 176   | 176    | 176    | 176    |        |        |        |        |         |

| FG456   |       |        | 260    | 284    | 312    |        |        |        |         |

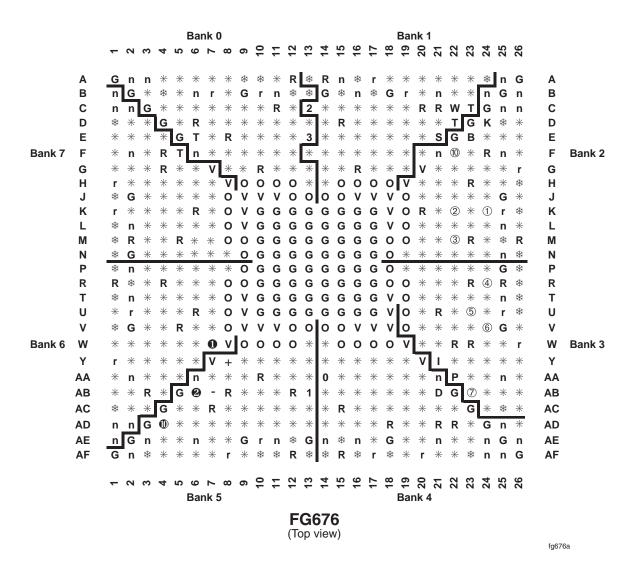

| FG676   |       |        |        |        |        | 404    | 444    | 444    |         |

| FG680   |       |        |        |        |        |        | 512    | 512    | 512     |

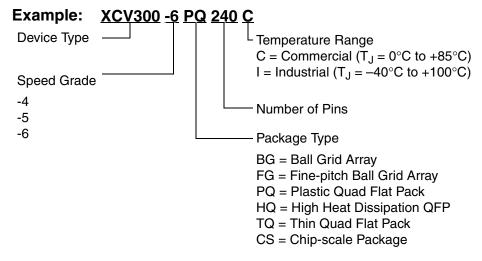

## **Virtex Ordering Information**

Figure 1: Virtex Ordering Information

#### General Purpose Routing

Most Virtex signals are routed on the general purpose routing, and consequently, the majority of interconnect resources are associated with this level of the routing hierarchy. The general routing resources are located in horizontal and vertical routing channels associated with the rows and columns CLBs. The general-purpose routing resources are listed below.

- Adjacent to each CLB is a General Routing Matrix (GRM). The GRM is the switch matrix through which horizontal and vertical routing resources connect, and is also the means by which the CLB gains access to the general purpose routing.

- 24 single-length lines route GRM signals to adjacent GRMs in each of the four directions.

- 12 buffered Hex lines route GRM signals to another GRMs six-blocks away in each one of the four directions. Organized in a staggered pattern, Hex lines can be driven only at their endpoints. Hex-line signals can be accessed either at the endpoints or at the midpoint (three blocks from the source). One third of the Hex lines are bidirectional, while the remaining ones are uni-directional.

12 Longlines are buffered, bidirectional wires that distribute signals across the device quickly and efficiently. Vertical Longlines span the full height of the device, and horizontal ones span the full width of the device.

#### I/O Routing

Virtex devices have additional routing resources around their periphery that form an interface between the CLB array and the IOBs. This additional routing, called the VersaRing, facilitates pin-swapping and pin-locking, such that logic redesigns can adapt to existing PCB layouts. Time-to-market is reduced, since PCBs and other system components can be manufactured while the logic design is still in progress.

#### **Dedicated Routing**

Some classes of signal require dedicated routing resources to maximize performance. In the Virtex architecture, dedicated routing resources are provided for two classes of signal.

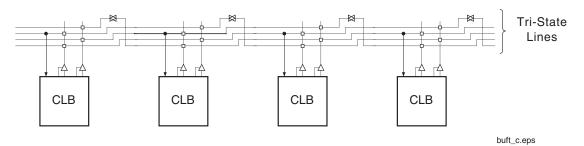

- Horizontal routing resources are provided for on-chip 3-state busses. Four partitionable bus lines are provided per CLB row, permitting multiple busses within a row, as shown in Figure 8.

- Two dedicated nets per CLB propagate carry signals vertically to the adjacent CLB.

Figure 8: BUFT Connections to Dedicated Horizontal Bus Lines

#### Global Routing

Global Routing resources distribute clocks and other signals with very high fanout throughout the device. Virtex devices include two tiers of global routing resources referred to as primary global and secondary local clock routing resources.

• The primary global routing resources are four dedicated global nets with dedicated input pins that are designed to distribute high-fanout clock signals with minimal skew. Each global clock net can drive all CLB, IOB, and block RAM clock pins. The primary global nets can only be driven by global buffers. There are four global buffers, one for each global net.  The secondary local clock routing resources consist of 24 backbone lines, 12 across the top of the chip and 12 across bottom. From these lines, up to 12 unique signals per column can be distributed via the 12 longlines in the column. These secondary resources are more flexible than the primary resources since they are not restricted to routing only to clock pins.

#### **Clock Distribution**

Virtex provides high-speed, low-skew clock distribution through the primary global routing resources described above. A typical clock distribution net is shown in Figure 9.

Four global buffers are provided, two at the top center of the device and two at the bottom center. These drive the four primary global nets that in turn drive any clock pin.

## **Configuration**

Virtex devices are configured by loading configuration data into the internal configuration memory. Some of the pins used for this are dedicated configuration pins, while others can be re-used as general purpose inputs and outputs once configuration is complete.

The following are dedicated pins:

- Mode pins (M2, M1, M0)

- Configuration clock pin (CCLK)

- PROGRAM pin

- DONE pin

- Boundary-scan pins (TDI, TDO, TMS, TCK)

Depending on the configuration mode chosen, CCLK can be an output generated by the FPGA, or it can be generated externally and provided to the FPGA as an input. The PROGRAM pin must be pulled High prior to reconfiguration.

Note that some configuration pins can act as outputs. For correct operation, these pins can require a  $V_{CCO}$  of 3.3 V to permit LVTTL operation. All the pins affected are in banks 2 or 3. The configuration pins needed for SelectMap (CS, Write) are located in bank 1.

After Virtex devices are configured, unused IOBs function as 3-state OBUFTs with weak pull downs. For a more detailed description than that given below, see the XAPP138, Virtex Configuration and Readback.

### **Configuration Modes**

Virtex supports the following four configuration modes.

- Slave-serial mode

- Master-serial mode

- SelectMAP mode

- · Boundary-scan mode

The Configuration mode pins (M2, M1, M0) select among these configuration modes with the option in each case of having the IOB pins either pulled up or left floating prior to configuration. The selection codes are listed in Table 7.

Configuration through the boundary-scan port is always available, independent of the mode selection. Selecting the boundary-scan mode simply turns off the other modes. The three mode pins have internal pull-up resistors, and default to a logic High if left unconnected. However, it is recommended to drive the configuration mode pins externally.

Table 7: Configuration Codes

| Configuration Mode | M2 | M1 | МО | <b>CCLK Direction</b> | Data Width | Serial D <sub>out</sub> | Configuration Pull-ups |

|--------------------|----|----|----|-----------------------|------------|-------------------------|------------------------|

| Master-serial mode | 0  | 0  | 0  | Out                   | 1          | Yes                     | No                     |

| Boundary-scan mode | 1  | 0  | 1  | N/A                   | 1          | No                      | No                     |

| SelectMAP mode     | 1  | 1  | 0  | In                    | 8          | No                      | No                     |

| Slave-serial mode  | 1  | 1  | 1  | In                    | 1          | Yes                     | No                     |

| Master-serial mode | 1  | 0  | 0  | Out                   | 1          | Yes                     | Yes                    |

| Boundary-scan mode | 0  | 0  | 1  | N/A                   | 1          | No                      | Yes                    |

| SelectMAP mode     | 0  | 1  | 0  | In                    | 8          | No                      | Yes                    |

| Slave-serial mode  | 0  | 1  | 1  | In                    | 1          | Yes                     | Yes                    |

#### Slave-Serial Mode

In slave-serial mode, the FPGA receives configuration data in bit-serial form from a serial PROM or other source of serial configuration data. The serial bitstream must be setup at the DIN input pin a short time before each rising edge of an externally generated CCLK.

For more information on serial PROMs, see the PROM data sheet at:

http://www.xilinx.com/bvdocs/publications/ds026.pdf.

Multiple FPGAs can be daisy-chained for configuration from a single source. After a particular FPGA has been configured, the data for the next device is routed to the DOUT pin. The data on the DOUT pin changes on the rising edge of CCLK.

The change of DOUT on the rising edge of CCLK differs from previous families, but does not cause a problem for

mixed configuration chains. This change was made to improve serial configuration rates for Virtex-only chains.

Figure 12 shows a full master/slave system. A Virtex device in slave-serial mode should be connected as shown in the third device from the left.

Slave-serial mode is selected by applying <111> or <011> to the mode pins (M2, M1, M0). A weak pull-up on the mode pins makes slave-serial the default mode if the pins are left unconnected. However, it is recommended to drive the configuration mode pins externally. Figure 13 shows slave-serial mode programming switching characteristics.

Table 8 provides more detail about the characteristics shown in Figure 13. Configuration must be delayed until the INIT pins of all daisy-chained FPGAs are High.

#### Master-Serial Mode

In master-serial mode, the CCLK output of the FPGA drives a Xilinx Serial PROM that feeds bit-serial data to the DIN input. The FPGA accepts this data on each rising CCLK edge. After the FPGA has been loaded, the data for the next device in a daisy-chain is presented on the DOUT pin after the rising CCLK edge.

The interface is identical to slave-serial except that an internal oscillator is used to generate the configuration clock (CCLK). A wide range of frequencies can be selected for CCLK which always starts at a slow default frequency. Configuration bits then switch CCLK to a higher frequency for the remainder of the configuration. Switching to a lower frequency is prohibited.

The CCLK frequency is set using the ConfigRate option in the bitstream generation software. The maximum CCLK frequency that can be selected is 60 MHz. When selecting a CCLK frequency, ensure that the serial PROM and any daisy-chained FPGAs are fast enough to support the clock rate.

On power-up, the CCLK frequency is 2.5 MHz. This frequency is used until the ConfigRate bits have been loaded when the frequency changes to the selected ConfigRate. Unless a different frequency is specified in the design, the default ConfigRate is 4 MHz.

Figure 12 shows a full master/slave system. In this system, the left-most device operates in master-serial mode. The remaining devices operate in slave-serial mode. The SPROM RESET pin is driven by  $\overline{\text{INIT}}$ , and the  $\overline{\text{CE}}$  input is driven by DONE. There is the potential for contention on the DONE pin, depending on the start-up sequence options chosen.

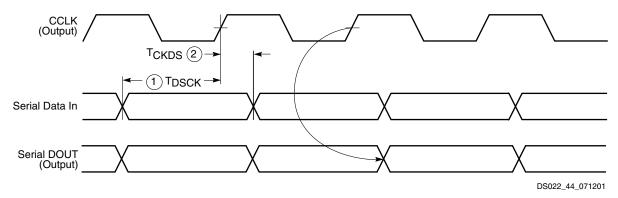

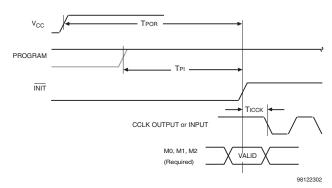

Figure 14 shows the timing of master-serial configuration. Master-serial mode is selected by a <000> or <100> on the mode pins (M2, M1, M0). Table 8 shows the timing information for Figure 14.

Figure 14: Master-Serial Mode Programming Switching Characteristics

At power-up,  $V_{CC}$  must rise from 1.0 V to  $V_{CC}$  min in less than 50 ms, otherwise delay configuration by pulling PROGRAM Low until  $V_{CC}$  is valid.

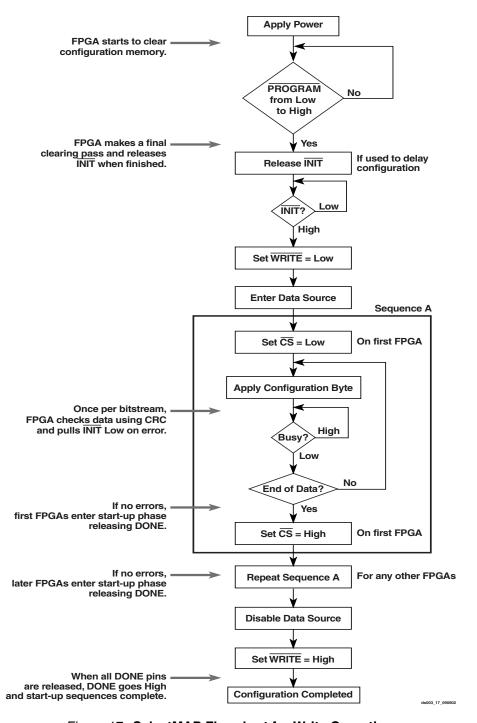

The sequence of operations necessary to configure a Virtex FPGA serially appears in Figure 15.

#### SelectMAP Mode

The SelectMAP mode is the fastest configuration option. Byte-wide data is written into the FPGA with a BUSY flag controlling the flow of data.

An external data source provides a byte stream, CCLK, a Chip Select  $(\overline{CS})$  signal and a Write signal  $(\overline{WRITE})$ . If BUSY is asserted (High) by the FPGA, the data must be held until BUSY goes Low.

Data can also be read using the SelectMAP mode. If WRITE is not asserted, configuration data is read out of the FPGA as part of a readback operation.

In the SelectMAP mode, multiple Virtex devices can be chained in parallel. DATA pins (D7:D0), CCLK, WRITE, BUSY, PROGRAM, DONE, and INIT can be connected in parallel between all the FPGAs. Note that the data is organized with the MSB of each byte on pin DO and the LSB of each byte on D7. The CS pins are kept separate, insuring that each FPGA can be selected individually. WRITE should be Low before loading the first bitstream and returned High after the last device has been programmed. Use  $\overline{\text{CS}}$  to select the appropriate FPGA for loading the bitstream and sending the configuration data. at the end of the bitstream, deselect the loaded device and select the next target FPGA by setting its  $\overline{\text{CS}}$  pin High. A free-running oscillator or other externally generated signal can be used for CCLK. The BUSY signal can be ignored for frequencies below 50 MHz. For details about frequencies above 50 MHz, see XAPP138, Virtex Configuration and Readback. Once all the devices have been programmed, the DONE pin goes High.

Figure 17: SelectMAP Flowchart for Write Operation

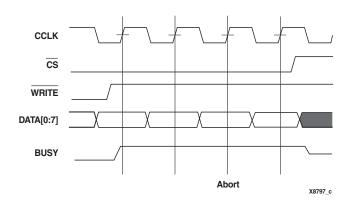

#### **Abort**

During a given assertion of  $\overline{\text{CS}}$ , the user cannot switch from a write to a read, or vice-versa. This action causes the current packet command to be aborted. The device will remain BUSY until the aborted operation has completed. Following an abort, data is assumed to be unaligned to word boundar-

ies, and the FPGA requires a new synchronization word prior to accepting any new packets.

To initiate an abort during a write operation, de-assert WRITE. At the rising edge of CCLK, an abort is initiated, as shown in Figure 18.

Figure 18: SelectMAP Write Abort Waveforms

#### Boundary-Scan Mode

In the boundary-scan mode, configuration is done through the IEEE 1149.1 Test Access Port. Note that the PROGRAM pin must be pulled High prior to reconfiguration. A Low on the PROGRAM pin resets the TAP controller and no JTAG operations can be performed.

Configuration through the TAP uses the CFG\_IN instruction. This instruction allows data input on TDI to be converted into data packets for the internal configuration bus.

The following steps are required to configure the FPGA through the boundary-scan port (when using TCK as a start-up clock).

- Load the CFG\_IN instruction into the boundary-scan instruction register (IR)

- 2. Enter the Shift-DR (SDR) state

- 3. Shift a configuration bitstream into TDI

- 4. Return to Run-Test-Idle (RTI)

- 5. Load the JSTART instruction into IR

- 6. Enter the SDR state

- 7. Clock TCK through the startup sequence

- 8. Return to RTI

Configuration and readback via the TAP is always available. The boundary-scan mode is selected by a <101> or 001> on the mode pins (M2, M1, M0). For details on TAP characteristics, refer to XAPP139.

### **Configuration Sequence**

The configuration of Virtex devices is a three-phase process. First, the configuration memory is cleared. Next, configuration data is loaded into the memory, and finally, the logic is activated by a start-up process.

Configuration is automatically initiated on power-up unless it is delayed by the user, as described below. The configuration process can also be initiated by asserting  $\overline{\mathsf{PROGRAM}}$ .

The end of the memory-clearing phase is signalled by INIT going High, and the completion of the entire process is signalled by DONE going High.

The power-up timing of configuration signals is shown in Figure 19. The corresponding timing characteristics are listed in Table 10.

Figure 19: Power-Up Timing Configuration Signals

Table 10: Power-up Timing Characteristics

| Description         | Symbol               | Value | Units   |

|---------------------|----------------------|-------|---------|

| Power-on Reset      | T <sub>POR</sub>     | 2.0   | ms, max |

| Program Latency     | T <sub>PL</sub>      | 100.0 | μs, max |

| CCLK (output) Delay | T <sub>ICCK</sub>    | 0.5   | μs, min |

|                     |                      | 4.0   | μs, max |

| Program Pulse Width | T <sub>PROGRAM</sub> | 300   | ns, min |

#### **Delaying Configuration**

INIT can be held Low using an open-drain driver. An open-drain is required since INIT is a bidirectional open-drain pin that is held Low by the FPGA while the configuration memory is being cleared. Extending the time that the pin is Low causes the configuration sequencer to wait. Thus, configuration is delayed by preventing entry into the phase where data is loaded.

#### Start-Up Sequence

The default Start-up sequence is that one CCLK cycle after DONE goes High, the global 3-state signal (GTS) is released. This permits device outputs to turn on as necessary.

One CCLK cycle later, the Global Set/Reset (GSR) and Global Write Enable (GWE) signals are released. This permits the internal storage elements to begin changing state in response to the logic and the user clock.

The relative timing of these events can be changed. In addition, the GTS, GSR, and GWE events can be made dependent on the DONE pins of multiple devices all going High, forcing the devices to start in synchronism. The sequence can also be paused at any stage until lock has been achieved on any or all DLLs.

### **IOB Output Switching Characteristics Standard Adjustments**

Output delays terminating at a pad are specified for LVTTL with 12 mA drive and fast slew rate. For other standards, adjust the delays by the values shown.

|                                                                       |                         |                         |       | Speed | Grade |       | Unit |

|-----------------------------------------------------------------------|-------------------------|-------------------------|-------|-------|-------|-------|------|

| Description                                                           | Symbol                  | Standard <sup>(1)</sup> | Min   | -6    | -5    | -4    | s    |

| Output Delay Adjustments                                              |                         |                         |       |       |       |       |      |

| Standard-specific adjustments for                                     | T <sub>OLVTTL_S2</sub>  | LVTTL, Slow, 2 mA       | 4.2   | 14.7  | 15.8  | 17.0  | ns   |

| output delays terminating at pads (based on standard capacitive load, | T <sub>OLVTTL_S4</sub>  | 4 mA                    | 2.5   | 7.5   | 8.0   | 8.6   | ns   |

| Csl)                                                                  | T <sub>OLVTTL_S6</sub>  | 6 mA                    | 1.8   | 4.8   | 5.1   | 5.6   | ns   |

|                                                                       | T <sub>OLVTTL_S8</sub>  | 8 mA                    | 1.2   | 3.0   | 3.3   | 3.5   | ns   |

|                                                                       | T <sub>OLVTTL_S12</sub> | 12 mA                   | 1.0   | 1.9   | 2.1   | 2.2   | ns   |

|                                                                       | T <sub>OLVTTL_S16</sub> | 16 mA                   | 0.9   | 1.7   | 1.9   | 2.0   | ns   |

|                                                                       | T <sub>OLVTTL_S24</sub> | 24 mA                   | 0.8   | 1.3   | 1.4   | 1.6   | ns   |

|                                                                       | T <sub>OLVTTL_F2</sub>  | LVTTL, Fast, 2mA        | 1.9   | 13.1  | 14.0  | 15.1  | ns   |

|                                                                       | T <sub>OLVTTL_F4</sub>  | 4 mA                    | 0.7   | 5.3   | 5.7   | 6.1   | ns   |

|                                                                       | T <sub>OLVTTL_F6</sub>  | 6 mA                    | 0.2   | 3.1   | 3.3   | 3.6   | ns   |

|                                                                       | T <sub>OLVTTL_F8</sub>  | 8 mA                    | 0.1   | 1.0   | 1.1   | 1.2   | ns   |

|                                                                       | T <sub>OLVTTL_F12</sub> | 12 mA                   | 0     | 0     | 0     | 0     | ns   |

|                                                                       | T <sub>OLVTTL_F16</sub> | 16 mA                   | -0.10 | -0.05 | -0.05 | -0.05 | ns   |

|                                                                       | T <sub>OLVTTL_F24</sub> | 24 mA                   | -0.10 | -0.20 | -0.21 | -0.23 | ns   |

|                                                                       | T <sub>OLVCMOS2</sub>   | LVCMOS2                 | 0.10  | 0.10  | 0.11  | 0.12  | ns   |

|                                                                       | T <sub>OPCl33_3</sub>   | PCI, 33 MHz, 3.3 V      | 0.50  | 2.3   | 2.5   | 2.7   | ns   |

|                                                                       | T <sub>OPCl33_5</sub>   | PCI, 33 MHz, 5.0 V      | 0.40  | 2.8   | 3.0   | 3.3   | ns   |

|                                                                       | T <sub>OPCI66_3</sub>   | PCI, 66 MHz, 3.3 V      | 0.10  | -0.40 | -0.42 | -0.46 | ns   |

|                                                                       | T <sub>OGTL</sub>       | GTL                     | 0.6   | 0.50  | 0.54  | 0.6   | ns   |

|                                                                       | T <sub>OGTLP</sub>      | GTL+                    | 0.7   | 0.8   | 0.9   | 1.0   | ns   |

|                                                                       | T <sub>OHSTL_I</sub>    | HSTL I                  | 0.10  | -0.50 | -0.53 | -0.5  | ns   |

|                                                                       | T <sub>OHSTL_III</sub>  | HSTL III                | -0.10 | -0.9  | -0.9  | -1.0  | ns   |

|                                                                       | T <sub>OHSTL_IV</sub>   | HSTL IV                 | -0.20 | -1.0  | -1.0  | -1.1  | ns   |

|                                                                       | T <sub>OSSTL2_I</sub>   | SSTL2 I                 | -0.10 | -0.50 | -0.53 | -0.5  | ns   |

|                                                                       | T <sub>OSSLT2_II</sub>  | SSTL2 II                | -0.20 | -0.9  | -0.9  | -1.0  | ns   |

|                                                                       | T <sub>OSSTL3_I</sub>   | SSTL3 I                 | -0.20 | -0.50 | -0.53 | -0.5  | ns   |

|                                                                       | T <sub>OSSTL3_II</sub>  | SSTL3 II                | -0.30 | -1.0  | -1.0  | -1.1  | ns   |

|                                                                       | T <sub>OCTT</sub>       | CTT                     | 0     | -0.6  | -0.6  | -0.6  | ns   |

|                                                                       | T <sub>OAGP</sub>       | AGP                     | 0     | -0.9  | -0.9  | -1.0  | ns   |

#### Notes:

<sup>1.</sup> Output timing is measured at 1.4 V with 35 pF external capacitive load for LVTTL. For other I/O standards and different loads, see Table 2 and Table 3.

### **Clock Distribution Guidelines**

|                                          |         |                       | Sp   | Speed Grade |      |         |

|------------------------------------------|---------|-----------------------|------|-------------|------|---------|

| Description                              | Device  | Symbol                | -6   | -5          | -4   | Units   |

| Global Clock Skew <sup>(1)</sup>         |         |                       |      |             |      |         |

| Global Clock Skew between IOB Flip-flops | XCV50   | T <sub>GSKEWIOB</sub> | 0.10 | 0.12        | 0.14 | ns, max |

|                                          | XCV100  |                       | 0.12 | 0.13        | 0.15 | ns, max |

|                                          | XCV150  |                       | 0.12 | 0.13        | 0.15 | ns, max |

|                                          | XCV200  |                       | 0.13 | 0.14        | 0.16 | ns, max |

|                                          | XCV300  |                       | 0.14 | 0.16        | 0.18 | ns, max |

|                                          | XCV400  |                       | 0.13 | 0.13        | 0.14 | ns, max |

|                                          | XCV600  |                       | 0.14 | 0.15        | 0.17 | ns, max |

|                                          | XCV800  |                       | 0.16 | 0.17        | 0.20 | ns, max |

|                                          | XCV1000 |                       | 0.20 | 0.23        | 0.25 | ns, max |

#### Notes:

### **Clock Distribution Switching Characteristics**

|                                         |                   | Speed Grade |     |            |     |         |

|-----------------------------------------|-------------------|-------------|-----|------------|-----|---------|

| Description                             | Symbol            | Min         | -6  | <b>-</b> 5 | -4  | Units   |

| GCLK IOB and Buffer                     |                   |             |     |            |     |         |

| Global Clock PAD to output.             | T <sub>GPIO</sub> | 0.33        | 0.7 | 0.8        | 0.9 | ns, max |

| Global Clock Buffer I input to O output | T <sub>GIO</sub>  | 0.34        | 0.7 | 0.8        | 0.9 | ns, max |

<sup>1.</sup> These clock-skew delays are provided for guidance only. They reflect the delays encountered in a typical design under worst-case conditions. Precise values for a particular design are provided by the timing analyzer.

### **CLB Switching Characteristics**

Delays originating at F/G inputs vary slightly according to the input used. The values listed below are worst-case. Precise values are provided by the timing analyzer.

|                                                                      |                                          |          | Speed     | Grade   |         |         |

|----------------------------------------------------------------------|------------------------------------------|----------|-----------|---------|---------|---------|

| Description                                                          | Symbol                                   | Min      | -6        | -5      | -4      | Units   |

| Combinatorial Delays                                                 |                                          | •        |           |         |         |         |

| 4-input function: F/G inputs to X/Y outputs                          | T <sub>ILO</sub>                         | 0.29     | 0.6       | 0.7     | 0.8     | ns, max |

| 5-input function: F/G inputs to F5 output                            | T <sub>IF5</sub>                         | 0.32     | 0.7       | 0.8     | 0.9     | ns, max |

| 5-input function: F/G inputs to X output                             | T <sub>IF5X</sub>                        | 0.36     | 0.8       | 0.8     | 1.0     | ns, max |

| 6-input function: F/G inputs to Y output via F6 MUX                  | T <sub>IF6Y</sub>                        | 0.44     | 0.9       | 1.0     | 1.2     | ns, max |

| 6-input function: F5IN input to Y output                             | T <sub>F5INY</sub>                       | 0.17     | 0.32      | 0.36    | 0.42    | ns, max |

| Incremental delay routing through transparent latch to XQ/YQ outputs | T <sub>IFNCTL</sub>                      | 0.31     | 0.7       | 0.7     | 0.8     | ns, max |

| BY input to YB output                                                | T <sub>BYYB</sub>                        | 0.27     | 0.53      | 0.6     | 0.7     | ns, max |

| Sequential Delays                                                    |                                          |          |           |         |         | 1       |

| FF Clock CLK to XQ/YQ outputs                                        | T <sub>CKO</sub>                         | 0.54     | 1.1       | 1.2     | 1.4     | ns, max |

| Latch Clock CLK to XQ/YQ outputs                                     | T <sub>CKLO</sub>                        | 0.6      | 1.2       | 1.4     | 1.6     | ns, max |

| Setup and Hold Times before/after Clock CLK <sup>(1)</sup>           |                                          | Setup T  | ime / Hol | d Time  |         |         |

| 4-input function: F/G Inputs                                         | T <sub>ICK</sub> /T <sub>CKI</sub>       | 0.6 / 0  | 1.2 / 0   | 1.4 / 0 | 1.5 / 0 | ns, min |

| 5-input function: F/G inputs                                         | T <sub>IF5CK</sub> /T <sub>CKIF5</sub>   | 0.7 / 0  | 1.3 / 0   | 1.5 / 0 | 1.7 / 0 | ns, min |

| 6-input function: F5IN input                                         | T <sub>F5INCK</sub> /T <sub>CKF5IN</sub> | 0.46 / 0 | 1.0 / 0   | 1.1 / 0 | 1.2 / 0 | ns, min |

| 6-input function: F/G inputs via F6 MUX                              | T <sub>IF6CK</sub> /T <sub>CKIF6</sub>   | 0.8 / 0  | 1.5 / 0   | 1.7 / 0 | 1.9 / 0 | ns, min |

| BX/BY inputs                                                         | $T_{DICK}/T_{CKDI}$                      | 0.30 / 0 | 0.6 / 0   | 0.7 / 0 | 0.8 / 0 | ns, min |

| CE input                                                             | $T_{CECK}/T_{CKCE}$                      | 0.37 / 0 | 0.8 / 0   | 0.9 / 0 | 1.0 / 0 | ns, min |

| SR/BY inputs (synchronous)                                           | $T_{RCK}T_{CKR}$                         | 0.33 / 0 | 0.7 / 0   | 0.8 / 0 | 0.9 / 0 | ns, min |

| Clock CLK                                                            |                                          |          |           |         |         |         |

| Minimum Pulse Width, High                                            | T <sub>CH</sub>                          | 0.8      | 1.5       | 1.7     | 2.0     | ns, min |

| Minimum Pulse Width, Low                                             | $T_CL$                                   | 0.8      | 1.5       | 1.7     | 2.0     | ns, min |

| Set/Reset                                                            |                                          |          |           |         |         |         |

| Minimum Pulse Width, SR/BY inputs                                    | T <sub>RPW</sub>                         | 1.3      | 2.5       | 2.8     | 3.3     | ns, min |

| Delay from SR/BY inputs to XQ/YQ outputs (asynchronous)              | T <sub>RQ</sub>                          | 0.54     | 1.1       | 1.3     | 1.4     | ns, max |

| Delay from GSR to XQ/YQ outputs                                      | T <sub>IOGSRQ</sub>                      | 4.9      | 9.7       | 10.9    | 12.5    | ns, max |

| Toggle Frequency (MHz) (for export control)                          | F <sub>TOG</sub> (MHz)                   | 625      | 333       | 294     | 250     | MHz     |

#### Notes:

<sup>1.</sup> A Zero "0" Hold Time listing indicates no hold time or a negative hold time. Negative values cannot be guaranteed "best-case", but if a "0" is listed, there is no positive hold time.

### **CLB Arithmetic Switching Characteristics**

Setup times not listed explicitly can be approximated by decreasing the combinatorial delays by the setup time adjustment listed. Precise values are provided by the timing analyzer.

|                                                            |                                      | Speed Grade |         |         |         |         |

|------------------------------------------------------------|--------------------------------------|-------------|---------|---------|---------|---------|

| Description                                                | Symbol                               | Min         | -6      | -5      | -4      | Units   |

| Combinatorial Delays                                       |                                      |             |         |         | •       | •       |

| F operand inputs to X via XOR                              | T <sub>OPX</sub>                     | 0.37        | 0.8     | 0.9     | 1.0     | ns, max |

| F operand input to XB output                               | T <sub>OPXB</sub>                    | 0.54        | 1.1     | 1.3     | 1.4     | ns, max |

| F operand input to Y via XOR                               | T <sub>OPY</sub>                     | 0.8         | 1.5     | 1.7     | 2.0     | ns, max |

| F operand input to YB output                               | T <sub>OPYB</sub>                    | 0.8         | 1.5     | 1.7     | 2.0     | ns, max |

| F operand input to COUT output                             | T <sub>OPCYF</sub>                   | 0.6         | 1.2     | 1.3     | 1.5     | ns, max |

| G operand inputs to Y via XOR                              | T <sub>OPGY</sub>                    | 0.46        | 1.0     | 1.1     | 1.2     | ns, max |

| G operand input to YB output                               | T <sub>OPGYB</sub>                   | 0.8         | 1.6     | 1.8     | 2.1     | ns, max |

| G operand input to COUT output                             | T <sub>OPCYG</sub>                   | 0.7         | 1.3     | 1.4     | 1.6     | ns, max |

| BX initialization input to COUT                            | T <sub>BXCY</sub>                    | 0.41        | 0.9     | 1.0     | 1.1     | ns, max |

| CIN input to X output via XOR                              | T <sub>CINX</sub>                    | 0.21        | 0.41    | 0.46    | 0.53    | ns, max |

| CIN input to XB                                            | T <sub>CINXB</sub>                   | 0.02        | 0.04    | 0.05    | 0.06    | ns, max |

| CIN input to Y via XOR                                     | T <sub>CINY</sub>                    | 0.23        | 0.46    | 0.52    | 0.6     | ns, max |

| CIN input to YB                                            | T <sub>CINYB</sub>                   | 0.23        | 0.45    | 0.51    | 0.6     | ns, max |

| CIN input to COUT output                                   | T <sub>BYP</sub>                     | 0.05        | 0.09    | 0.10    | 0.11    | ns, max |

| Multiplier Operation                                       |                                      |             |         |         |         | •       |

| F1/2 operand inputs to XB output via AND                   | T <sub>FANDXB</sub>                  | 0.18        | 0.36    | 0.40    | 0.46    | ns, max |

| F1/2 operand inputs to YB output via AND                   | T <sub>FANDYB</sub>                  | 0.40        | 0.8     | 0.9     | 1.1     | ns, max |

| F1/2 operand inputs to COUT output via AND                 | T <sub>FANDCY</sub>                  | 0.22        | 0.43    | 0.48    | 0.6     | ns, max |

| G1/2 operand inputs to YB output via AND                   | T <sub>GANDYB</sub>                  | 0.25        | 0.50    | 0.6     | 0.7     | ns, max |

| G1/2 operand inputs to COUT output via AND                 | T <sub>GANDCY</sub>                  | 0.07        | 0.13    | 0.15    | 0.17    | ns, max |

| Setup and Hold Times before/after Clock CLK <sup>(1)</sup> |                                      |             |         |         |         | •       |

| CIN input to FFX                                           | T <sub>CCKX</sub> /T <sub>CKCX</sub> | 0.50 / 0    | 1.0 / 0 | 1.2 / 0 | 1.3 / 0 | ns, min |

| CIN input to FFY                                           | T <sub>CCKY</sub> /T <sub>CKCY</sub> | 0.53 / 0    | 1.1 / 0 | 1.2 / 0 | 1.4 / 0 | ns, min |

#### Notes:

<sup>1.</sup> A Zero "0" Hold Time listing indicates no hold time or a negative hold time. Negative values can not be guaranteed "best-case", but if a "0" is listed, there is no positive hold time.

## Virtex<sup>™</sup> 2.5 V Field Programmable Gate Arrays

DS003-4 (v4.0) March 1, 2013

**Production Product Specification**

### **Virtex Pin Definitions**

Table 1: Special Purpose Pins

| Pin Name                                       | Dedicated<br>Pin | Direction                     | Description                                                                                                                                                                                                                |

|------------------------------------------------|------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GCK0, GCK1,<br>GCK2, GCK3                      | Yes              | Input                         | Clock input pins that connect to Global Clock Buffers. These pins become user inputs when not needed for clocks.                                                                                                           |

| M0, M1, M2                                     | Yes              | Input                         | Mode pins are used to specify the configuration mode.                                                                                                                                                                      |

| CCLK                                           | Yes              | Input or<br>Output            | The configuration Clock I/O pin: it is an input for SelectMAP and slave-serial modes, and output in master-serial mode. After configuration, it is input only, logic level = Don't Care.                                   |

| PROGRAM                                        | Yes              | Input                         | Initiates a configuration sequence when asserted Low.                                                                                                                                                                      |

| DONE                                           | Yes              | Bidirectional                 | Indicates that configuration loading is complete, and that the start-up sequence is in progress. The output can be open drain.                                                                                             |

| INIT                                           | No               | Bidirectional<br>(Open-drain) | When Low, indicates that the configuration memory is being cleared. The pin becomes a user I/O after configuration.                                                                                                        |

| BUSY/<br>DOUT                                  | No               | Output                        | In SelectMAP mode, BUSY controls the rate at which configuration data is loaded. The pin becomes a user I/O after configuration unless the SelectMAP port is retained.                                                     |

|                                                |                  |                               | In bit-serial modes, DOUT provides header information to downstream devices in a daisy-chain. The pin becomes a user I/O after configuration.                                                                              |

| D0/DIN,<br>D1, D2,<br>D3, D4,<br>D5, D6,<br>D7 | No               | Input or<br>Output            | In SelectMAP mode, D0 - D7 are configuration data pins. These pins become user I/Os after configuration unless the SelectMAP port is retained.  In bit-serial modes, DIN is the single data input. This pin becomes a user |

| WRITE                                          | No               | Input                         | I/O after configuration.  In SelectMAP mode, the active-low Write Enable signal. The pin becomes a user I/O after configuration unless the SelectMAP port is retained.                                                     |

| CS                                             | No               | Input                         | In SelectMAP mode, the active-low Chip Select signal. The pin becomes a user I/O after configuration unless the SelectMAP port is retained.                                                                                |

| TDI, TDO,<br>TMS, TCK                          | Yes              | Mixed                         | Boundary-scan Test-Access-Port pins, as defined in IEEE 1149.1.                                                                                                                                                            |

| DXN, DXP                                       | Yes              | N/A                           | Temperature-sensing diode pins. (Anode: DXP, cathode: DXN)                                                                                                                                                                 |

| V <sub>CCINT</sub>                             | Yes              | Input                         | Power-supply pins for the internal core logic.                                                                                                                                                                             |

| V <sub>CCO</sub>                               | Yes              | Input                         | Power-supply pins for the output drivers (subject to banking rules)                                                                                                                                                        |

| V <sub>REF</sub>                               | No               | Input                         | Input threshold voltage pins. Become user I/Os when an external threshold voltage is not needed (subject to banking rules).                                                                                                |

| GND                                            | Yes              | Input                         | Ground                                                                                                                                                                                                                     |

<sup>© 1999-2013</sup> Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at <a href="http://www.xilinx.com/legal.htm">http://www.xilinx.com/legal.htm</a>.

All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

Table 2: Virtex Pinout Tables (Chip-Scale and QFP Packages) (Continued)

| Pin Name                                                                                                 | Device     | CS144                                                                        | TQ144                                                                      | PQ/HQ240                                                                                                                                       |

|----------------------------------------------------------------------------------------------------------|------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>REF</sub> , Bank 6                                                                                | XCV50      | H2, K1                                                                       | 116, 123                                                                   | 36, 50                                                                                                                                         |

| (V <sub>REF</sub> pins are listed                                                                        | XCV100/150 | + J3                                                                         | + 118                                                                      | + 47                                                                                                                                           |

| incrementally. Connect all pins listed for both                                                          | XCV200/300 | N/A                                                                          | N/A                                                                        | + 54                                                                                                                                           |

| the required device                                                                                      | XCV400     | N/A                                                                          | N/A                                                                        | + 33                                                                                                                                           |

| and all smaller devices listed in the same                                                               | XCV600     | N/A                                                                          | N/A                                                                        | + 48                                                                                                                                           |

| package.)                                                                                                | XCV800     | N/A                                                                          | N/A                                                                        | + 40                                                                                                                                           |

| Within each bank, if input reference voltage is not required, all V <sub>REF</sub> pins are general I/O. |            |                                                                              |                                                                            |                                                                                                                                                |

| V <sub>REF</sub> , Bank 7                                                                                | XCV50      | D4, E1                                                                       | 133, 140                                                                   | 9, 23                                                                                                                                          |

| (V <sub>REF</sub> pins are listed                                                                        | XCV100/150 | + D2                                                                         | + 138                                                                      | + 12                                                                                                                                           |

| incrementally. Connect all pins listed for both                                                          | XCV200/300 | N/A                                                                          | N/A                                                                        | + 5                                                                                                                                            |

| the required device                                                                                      | XCV400     | N/A                                                                          | N/A                                                                        | + 26                                                                                                                                           |

| and all smaller devices listed in the same                                                               | XCV600     | N/A                                                                          | N/A                                                                        | + 11                                                                                                                                           |

| package.)                                                                                                | XCV800     | N/A                                                                          | N/A                                                                        | + 19                                                                                                                                           |

| Within each bank, if input reference voltage is not required, all V <sub>REF</sub> pins are general I/O. |            |                                                                              |                                                                            |                                                                                                                                                |

| GND                                                                                                      | All        | A1, B9, B11, C7,<br>D5, E4, E11, F1,<br>G10, J1, J12, L3,<br>L5, L7, L9, N12 | 9, 18, 26, 35, 46, 54, 64,<br>75, 83, 91, 100, 111, 120,<br>129, 136, 144, | 1, 8, 14, 22, 29, 37, 45, 51, 59, 69, 75, 83, 91, 98, 106, 112, 119, 129, 135, 143, 151, 158, 166, 172, 182, 190, 196, 204, 211, 219, 227, 233 |

Table 3: Virtex Pinout Tables (BGA)

| Pin Name  | Device | BG256 | BG352 | BG432 | BG560 |

|-----------|--------|-------|-------|-------|-------|

| GCK0      | All    | Y11   | AE13  | AL16  | AL17  |

| GCK1      | All    | Y10   | AF14  | AK16  | AJ17  |

| GCK2      | All    | A10   | B14   | A16   | D17   |

| GCK3      | All    | B10   | D14   | D17   | A17   |

| MO        | All    | Y1    | AD24  | AH28  | AJ29  |

| M1        | All    | U3    | AB23  | AH29  | AK30  |

| M2        | All    | W2    | AC23  | AJ28  | AN32  |

| CCLK      | All    | B19   | C3    | D4    | C4    |

| PROGRAM   | All    | Y20   | AC4   | АН3   | AM1   |

| DONE      | All    | W19   | AD3   | AH4   | AJ5   |

| INIT      | All    | U18   | AD2   | AJ2   | AH5   |

| BUSY/DOUT | All    | D18   | E4    | D3    | D4    |

| D0/DIN    | All    | C19   | D3    | C2    | E4    |

| D1        | All    | E20   | G1    | K4    | K3    |

| D2        | All    | G19   | J3    | K2    | L4    |

| D3        | All    | J19   | M3    | P4    | P3    |

| D4        | All    | M19   | R3    | V4    | W4    |

| D5        | All    | P19   | U4    | AB1   | AB5   |

| D6        | All    | T20   | V3    | AB3   | AC4   |

| D7        | All    | V19   | AC3   | AG4   | AJ4   |

| WRITE     | All    | A19   | D5    | B4    | D6    |

| CS        | All    | B18   | C4    | D5    | A2    |

| TDI       | All    | C17   | В3    | В3    | D5    |

| TDO       | All    | A20   | D4    | C4    | E6    |

| TMS       | All    | D3    | D23   | D29   | B33   |

| TCK       | All    | A1    | C24   | D28   | E29   |

| DXN       | All    | W3    | AD23  | AH27  | AK29  |

| DXP       | All    | V4    | AE24  | AK29  | AJ28  |

Table 3: Virtex Pinout Tables (BGA) (Continued)

| Pin Name                                                                                    | Device     | BG256                                                                                                                                            | BG352                                                                                                                                                                                    | BG432                                                                                                                                                                                                                                        | BG560                                                                                                                                                                                                                                                                                                         |

|---------------------------------------------------------------------------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>REF</sub> , Bank 7                                                                   | XCV50      | G3, H1                                                                                                                                           | N/A                                                                                                                                                                                      | N/A                                                                                                                                                                                                                                          | N/A                                                                                                                                                                                                                                                                                                           |

| (V <sub>REF</sub> pins are listed                                                           | XCV100/150 | + D1                                                                                                                                             | D26, G26,                                                                                                                                                                                | N/A                                                                                                                                                                                                                                          | N/A                                                                                                                                                                                                                                                                                                           |

| incrementally. Connect all pins listed for both the                                         |            |                                                                                                                                                  | L26                                                                                                                                                                                      |                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                               |

| required device and all                                                                     | XCV200/300 | + B2                                                                                                                                             | + E24                                                                                                                                                                                    | F28, F31,                                                                                                                                                                                                                                    | N/A                                                                                                                                                                                                                                                                                                           |

| smaller devices listed in the same package.)                                                |            |                                                                                                                                                  |                                                                                                                                                                                          | J30, N30                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                               |

| Within each bank, if input reference voltage is not required, all V <sub>REF</sub> pins are | XCV400     | N/A                                                                                                                                              | N/A                                                                                                                                                                                      | + R31                                                                                                                                                                                                                                        | E31, G31, K31,<br>P31, T31                                                                                                                                                                                                                                                                                    |

| general I/O.                                                                                | XCV600     | N/A                                                                                                                                              | N/A                                                                                                                                                                                      | + J28                                                                                                                                                                                                                                        | + H32                                                                                                                                                                                                                                                                                                         |

|                                                                                             | XCV800     | N/A                                                                                                                                              | N/A                                                                                                                                                                                      | + M28                                                                                                                                                                                                                                        | + L33                                                                                                                                                                                                                                                                                                         |

|                                                                                             | XCV1000    | N/A                                                                                                                                              | N/A                                                                                                                                                                                      | N/A                                                                                                                                                                                                                                          | + D31                                                                                                                                                                                                                                                                                                         |

| GND                                                                                         | All        | C3, C18, D4, D5, D9, D10, D11, D12, D16, D17, E4, E17, J4, J17, K4, K17, L4, L17, M4, M17, T4, T17, U4, U5, U9, U10, U11, U12, U16, U17, V3, V18 | A1, A2, A5,<br>A8, A14,<br>A19, A22,<br>A25, A26,<br>B1, B26, E1,<br>E26, H1,<br>H26, N1,<br>P26, W1,<br>W26, AB1,<br>AB26, AE1,<br>AF2, AF5,<br>AF8, AF13,<br>AF19, AF22,<br>AF25, AF26 | A2, A3, A7, A9, A14, A18, A23, A25, A29, A30, B1, B2, B30, B31, C1, C31, D16, G1, G31, J1, J31, P1, P31, T4, T28, V1, V31, AC1, AC31, AE1, AE31, AH16, AJ1, AJ31, AK1, AK2, AK30, AK31, AL2, AL3, AL7, AL9 AL14, AL18 AL23, AL25, AL29, AL30 | A1, A7, A12, A14, A18, A20, A24, A29, A32, A33, B1, B6, B9, B15, B23, B27, B31, C2, E1, F32, G2, G33, J32, K1, L2, M33, P1, P33, R32, T1, V33, W2, Y1, Y33, AB1, AC32, AD33, AE2, AG1, AG32, AH2, AJ33, AL32, AM3, AM7, AM11, AM19, AM25, AM28, AM33, AN1, AN2, AN5, AN10, AN14, AN16, AN20, AN22, AN27, AN33 |

| GND <sup>(1)</sup>                                                                          | All        | J9, J10,<br>J11, J12,<br>K9, K10,<br>K11, K12,<br>L9, L10,<br>L11, L12,<br>M9, M10,<br>M11, M12                                                  | N/A                                                                                                                                                                                      | N/A                                                                                                                                                                                                                                          | N/A                                                                                                                                                                                                                                                                                                           |

| No Connect                                                                                  | All        | N/A                                                                                                                                              | N/A                                                                                                                                                                                      | N/A                                                                                                                                                                                                                                          | C31, AC2, AK4,<br>AL3                                                                                                                                                                                                                                                                                         |

#### Notes:

1. 16 extra balls (grounded) at package center.

Table 4: Virtex Pinout Tables (Fine-Pitch BGA) (Continued)

| Pin Name                                                                                                                                                             | Device     | FG256                                                               | FG456                                                                                                                                                | FG676                                                                                                                                                 | FG680                                                                                                                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CCINT</sub>                                                                                                                                                   | All        | C3, C14, D4,<br>D13, E5,<br>E12, M5,<br>M12, N4,<br>N13, P3,<br>P14 | E5, E18, F6,<br>F17, G7, G8, G9,<br>G14, G15, G16,<br>H7, H16, J7,<br>J16, P7, P16,<br>R7, R16, T7, T8,<br>T9, T14, T15,<br>T16, U6, U17,<br>V5, V18 | G7, G20, H8, H19,<br>J9, J10, J11, J16,<br>J17, J18, K9, K18,<br>L9, L18, T9, T18,<br>U9, U18, V9, V10,<br>V11, V16, V17,<br>V18, W8, W19, Y7,<br>Y20 | AD5, AD35,<br>AE5, AE35, AL5,<br>AL35, AM5,<br>AM35, AR8,<br>AR9, AR15,<br>AR16, AR24,<br>AR25, AR31,<br>AR32, E8, E9,<br>E15, E16, E24,<br>E25, E31, E32,<br>H5, H35, J5,<br>J35, R5, R35,<br>T5, T35 |

| V <sub>CCO</sub> , Bank 0                                                                                                                                            | All        | E8, F8                                                              | F7, F8, F9, F10<br>G10, G11                                                                                                                          | H9, H10, H11,<br>H12, J12, J13                                                                                                                        | E26, E27, E29,<br>E30, E33, E34                                                                                                                                                                        |

| V <sub>CCO</sub> , Bank 1                                                                                                                                            | All        | E9, F9                                                              | F13, F14, F15,<br>F16, G12, G13                                                                                                                      | H15, H16, H17,<br>H18, J14, J15                                                                                                                       | E6, E7, E10,<br>E11, E13, E14                                                                                                                                                                          |

| V <sub>CCO</sub> , Bank 2                                                                                                                                            | All        | H11, H12                                                            | G17, H17, J17,<br>K16, K17, L16                                                                                                                      | J19, K19, L19,<br>M18, M19, N18                                                                                                                       | F5, G5, K5, L5,<br>N5, P5                                                                                                                                                                              |

| V <sub>CCO</sub> , Bank 3                                                                                                                                            | All        | J11, J12                                                            | M16, N16, N17,<br>P17, R17, T17                                                                                                                      | P18, R18, R19,<br>T19, U19, V19                                                                                                                       | AF5, AG5, AN5,<br>AK5, AJ5, AP5                                                                                                                                                                        |

| V <sub>CCO</sub> , Bank 4                                                                                                                                            | All        | L9. M9                                                              | T12, T13, U13,<br>U14, U15, U16,                                                                                                                     | V14, V15, W15,<br>W16, W17, W18                                                                                                                       | AR6, AR7,<br>AR10, AR11,<br>AR13, AR14                                                                                                                                                                 |

| V <sub>CCO</sub> , Bank 5                                                                                                                                            | All        | L8, M8                                                              | T10, T11, U7,<br>U8, U9, U10                                                                                                                         | V12, V13,<br>W9,W10, W11,<br>W12                                                                                                                      | AR26, AR27,<br>AR29, AR30,<br>AR33, AR34                                                                                                                                                               |