Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                        |

|----------------------------|--------------------------------------------------------|

| Product Status             | Obsolete                                               |

| Core Processor             | Z8                                                     |

| Core Size                  | 8-Bit                                                  |

| Speed                      | 16MHz                                                  |

| Connectivity               | -                                                      |

| Peripherals                | LVD, POR, WDT                                          |

| Number of I/O              | 31                                                     |

| Program Memory Size        | 32KB (32K x 8)                                         |

| Program Memory Type        | OTP                                                    |

| EEPROM Size                | -                                                      |

| RAM Size                   | 236 x 8                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                              |

| Data Converters            | -                                                      |

| Oscillator Type            | Internal                                               |

| Operating Temperature      | 0°C ~ 70°C (TA)                                        |

| Mounting Type              | Surface Mount                                          |

| Package / Case             | 44-LCC (J-Lead)                                        |

| Supplier Device Package    | -                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z86e7316vsg |

|                            |                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Z86E72/73 OTP Microcontroller

| Power-On Reset (POR) 6                          | 35 |

|-------------------------------------------------|----|

| HALT                                            | 36 |

| STOP                                            | 36 |

| Port Configuration Register (PCON) 6            | 36 |

| Stop-Mode Recovery Register (SMR) 6             | 37 |

| Stop-Mode Recovery Register 2 (SMR2) 7          |    |

| Watch-Dog Timer Mode Register (WDTMR) 7         |    |

| Low-Voltage Protection7                         | 74 |

| Software-Selectable Options 7                   | 75 |

| Low-Voltage Detection                           | 75 |

| EPROM Programming                               | 76 |

| Expanded Register File Control Registers (0D) 8 | 32 |

| Expanded Register File Control Registers (0F) 8 | 35 |

| Z8 Standard Control Register Diagrams 8         | 39 |

| Package Information                             | 94 |

| Ordering Information                            | 97 |

| Customer Support                                | 98 |

Power connections follow the conventions listed in Table 2.

#### **Table 2. Power Connections**

| Connection | Circuit         | Device          |

|------------|-----------------|-----------------|

| Power      | V <sub>CC</sub> | V <sub>DD</sub> |

| Ground     | GND             | V <sub>SS</sub> |

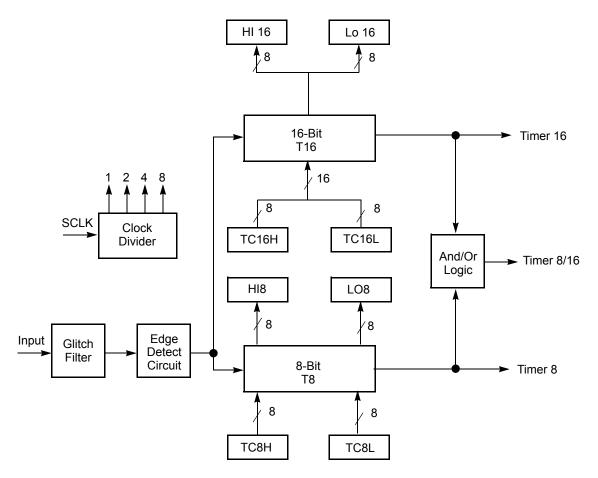

Figure 2 displays the functional block diagram.

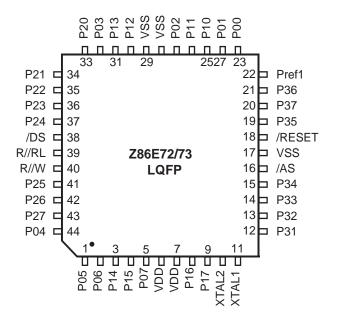

Figure 7 displays the pin assignments for the standard mode of the 44-pin low-profile quad flat pack (LQFP). Figure 8 on page 9 shows the pin assignments for the EPROM mode of the 44-pin LQFP.

Figure 7. 44-Pin LQFP Pin Assignments (Standard Mode)

# AC Characteristics

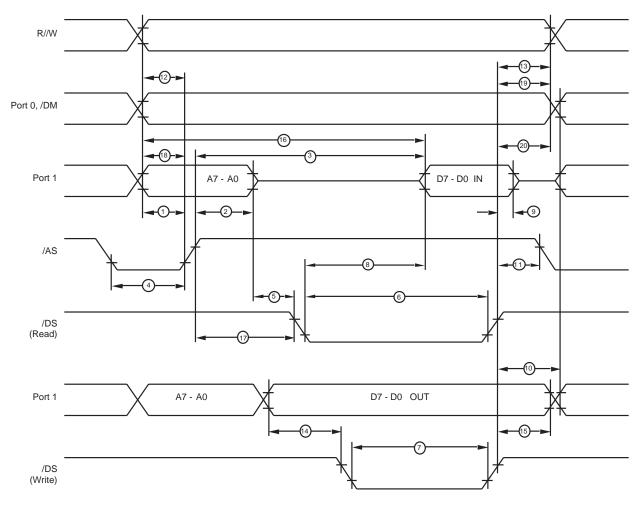

Figure 10 shows the external input/output (I/O) or memory read and write timing. Table 9 describes the I/O or memory read and write timing.

Figure 10. External I/O or Memory Read/Write Timing

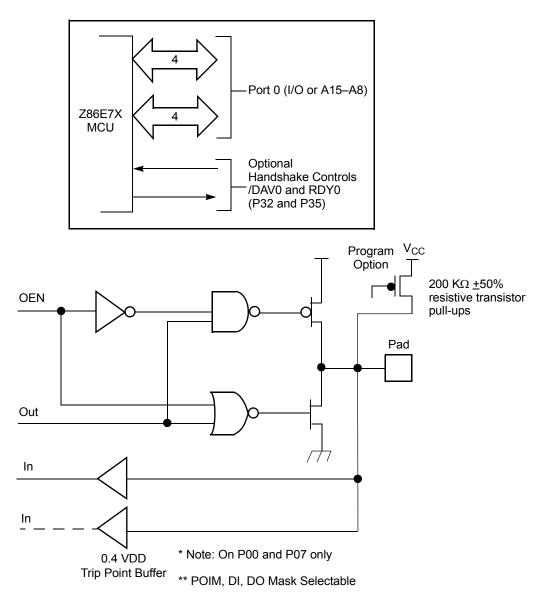

Figure 14. Port 0 Configuration

## **Expanded Register File**

The register file has been expanded to allow for additional system control registers and for mapping of additional peripheral devices into the register address area. The Z8 register address space R0 through R15 has been implemented as 16 banks of 16 registers per bank. These register groups are known as the Expanded Register File (ERF).

Bits 7-4 of register RP select the working register group. Bits 3-0 of register RP select the expanded register file bank.

Note: The expanded register bank is also referred to as the expanded register group (see Figure 22).

## Counter\_INT\_Mask

Set this bit to allow interrupt when T8 has a time out.

### P34\_Out

This bit defines whether P34 is used as a normal output pin or the T8 output.

## CTR1(D)01h Register

This register (Table 23) controls the functions in common with the T8 and T16.

| Field                          | Bit Position | )   | Value    | Description                  |

|--------------------------------|--------------|-----|----------|------------------------------|

| Mode                           | 7            | R/W | 0*       | Transmit Mode                |

|                                |              |     | 1        | Demodulation Mode            |

| P36_Out/Demodulator_Input      | -6           | R/W |          | Transmit Mode                |

|                                |              |     | 0*       | Port Output                  |

|                                |              |     | 1        | T8/16 Output                 |

|                                |              |     |          | Demodulation Mode            |

|                                |              |     | 0        | P31                          |

|                                |              |     | 1        | P20                          |

| T8/T16_Logic/Edge _Detect      | 54           | R/W |          | Transmit Mode                |

|                                |              |     | 00       | AND                          |

|                                |              |     | 01       | OR                           |

|                                |              |     | 10       | NOR                          |

|                                |              |     | 11       | NAND                         |

|                                |              |     |          | Demodulation Mode            |

|                                |              |     | 00       | Falling Edge                 |

|                                |              |     | 01       | Rising Edge                  |

|                                |              |     | 10       | Both Edges                   |

|                                |              |     | 11       | Reserved                     |

| Transmit_Submode/Glitch_Filter | r32          | R/W |          | Transmit Mode                |

|                                |              |     | 00       | Normal Operation             |

|                                |              |     | 01       | Ping-Pong Mode               |

|                                |              |     | 10       | T16_OUT = 0                  |

|                                |              |     | 11       | T16_OUT = 1                  |

|                                |              |     | 0.0      | Demodulation Mode            |

|                                |              |     | 00       | No Filter                    |

|                                |              |     | 01       | 4 SCLK Cycle<br>8 SCLK Cycle |

|                                |              |     | 10<br>11 | 16 SCLK Cycle                |

|                                |              |     | 11       | IU SOLK CYCIE                |

## Table 23. CTR1(D)01h Register

| Field                         | Bit Position |     | Value | Description            |

|-------------------------------|--------------|-----|-------|------------------------|

| Initial_T8_Out/Rising_Edge    | 1-           |     |       | Transmit Mode          |

|                               |              | R/W | 0     | T8_OUT is 0 Initially  |

|                               |              |     | 1     | T8_OUT is 1 Initially  |

|                               |              |     |       | Demodulation Mode      |

|                               |              | R   | 0     | No Rising Edge         |

|                               |              |     | 1     | Rising Edge Detected   |

|                               |              | W   | 0     | No Effect              |

|                               |              |     | 1     | Reset Flag to 0        |

| Initial_T16_Out/Falling _Edge | 0            |     |       | Transmit Mode          |

|                               |              | R/W | 0     | T16_OUT is 0 Initially |

|                               |              |     | 1     | T16_OUT is 1 Initially |

|                               |              |     |       | Demodulation Mode      |

|                               |              | R   | 0     | No Falling Edge        |

|                               |              |     | 1     | Falling Edge Detected  |

|                               |              | W   | 0     | No Effect              |

|                               |              |     | 1     | Reset Flag to 0        |

#### Table 23. CTR1(D)01h Register (Continued)

Note: \* Indicates the value upon Power-On Reset.

#### Mode

If it is 0, the counter/timers are in the transmit mode; otherwise, they are in the demodulation mode.

#### P36\_Out/Demodulator\_Input

In transmit mode, this bit defines whether P36 is used as a normal output pin or the combined output of T8 and T16.

In demodulation mode, this bit defines whether the input signal to the counter/timers is from P20 or P31.

#### T8/T16\_Logic/Edge \_Detect

In transmit mode, this field defines how the outputs of T8 and T16 are combined (AND, OR, NOR, NAND).

In demodulation mode, this field defines which edge needs to be detected by the edge detector.

#### Transmit\_Submode/Glitch Filter

In transmit mode, this field defines whether T8 and T16 are in the "Ping-Pong" mode or in independent normal operation mode. Setting this field to "Normal

In demodulation mode, when set to 0, T16 captures and reloads on detection of all the edges. When set to 1, T16 captures and detects on the first edge, but ignores the subsequent edges. For details, see "T16 Demodulation Mode" on page 60.

### Time\_Out

This bit is set when T16 times out (terminal count reached). To reset it, a 1 must be written to this location.

## T16\_Clock

This bit defines the frequency of the input signal to Counter/Timer16.

## Capture\_INT\_Mask

Set this bit to allow interrupt when data is captured into LO16 and HI16.

## Counter\_INT\_Mask

Set this bit to allow interrupt when T16 times out.

## P35\_Out

This bit defines whether P35 is used as a normal output pin or T16 output.

#### SMR2(F)0Dh Register

Table 25 describes Stop-Mode Recovery Register 2.

#### Table 25. SMR2(F)0Dh Register

| Field                 | Bit Position      |           | Value | Description                  |

|-----------------------|-------------------|-----------|-------|------------------------------|

| Reserved              | 7                 |           | 0     | Reserved (Must be 0)         |

| Recovery Level        | -6                | W         | 0*    | Low                          |

| -                     |                   |           | 1     | High                         |

| Reserved              | 5                 |           | 0     | Reserved (Must be 0)         |

| Source                | 432               | W         | 000*  | A. POR Only                  |

|                       |                   |           | 001   | B. NAND of P23–P20           |

|                       |                   |           | 010   | C. NAND or P27–P20           |

|                       |                   |           | 011   | D. NOR of P33–P31            |

|                       |                   |           | 100   | E. NAND of P33–P31           |

|                       |                   |           | 101   | F. NOR of P33–P31, P00, P07  |

|                       |                   |           | 110   | G. NAND of P33–P31, P00, P07 |

|                       |                   |           | 111   | H. NAND of P33–P31, P22–P20  |

| Reserved              | 10                |           | 00    | Reserved (Must be 0)         |

| Note: * Indicates the | e value upon Powe | r-On Rese | ət.   |                              |

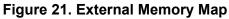

### **Eight-Bit Counter/Timer Circuits**

Figure 26 shows the 8-bit counter/timer circuits.

Figure 26. Eight-Bit Counter/Timer Circuits

## T8 Transmit Mode

When T8 is enabled, the output of T8 depends on CTR1, D1. If it is 0, T8\_OUT is 1. If it is 1, T8\_OUT is 0.

When T8 is enabled, the output T8\_OUT switches to the initial value (CTR1 D1). If the initial value (CTR1 D1) is 0, TC8L is loaded; otherwise, TC8H is loaded into the counter (see Figure 27). In Single-Pass Mode (CTR0 D6), T8 counts down to 0 and stops, T8\_OUT toggles, the time-out status bit (CTR0 D5) is set, and a time-out interrupt can be generated if it is enabled (CTR0 D1). See Figure 28. In Modulo-N Mode, upon reaching terminal count, T8\_OUT is toggled, but no interrupt is generated. Then T8 loads a new count (if the T8\_OUT level now is 0), TC8L is loaded; if it is 1, TC8H is loaded. T8 counts down to 0, toggles T8\_OUT, sets the time-out status bit (CTR0 D5), and generates an interrupt if enabled (CTR0 D1). See Figure 29. This completes one cycle. T8 then loads from TC8H or TC8L according to the T8\_OUT level, and repeats the cycle.

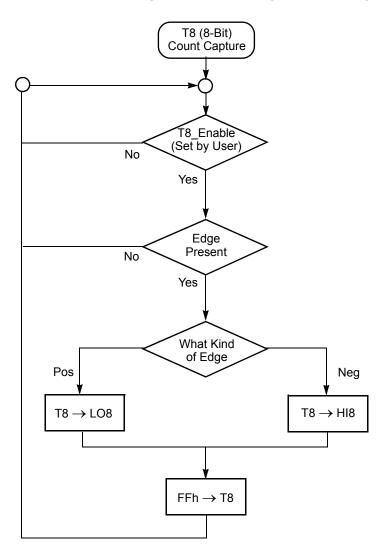

#### **T8 Demodulation Mode**

You need to program TC8L and TC8H to FFh. After T8 is enabled, when the first edge (rising, falling, or both depending on CTR1 D5, D4) is detected, it starts to count down. When a subsequent edge (rising, falling, or both depending on CTR1 D5, D4) is detected during counting, the current value of T8 is one's complemented and put into one of the capture registers. If it is a positive edge, data is put into LO8; if negative edge, HI8. One of the edge-detect status bits (CTR1 D1, D0) is set, and an interrupt can be generated if enabled (CTR0 D2). Meanwhile, T8 is loaded with FFh and starts counting again. When T8 reaches 0, the time-out status bit (CTR0 D5) is set, an interrupt can be generated if enabled (CTR0 D1), and T8 continues counting from FFh (see Figure 30 and Figure 31).

## If D6 of CTR2 Is 1

T16 ignores the subsequent edges in the input signal and continues counting down. A time out of T8 causes T16 to capture its current value and generate an interrupt if enabled (CTR2, D2). In this case, T16 does not reload and continues counting. If D6 bit of CTR2 is toggled (by writing a 0 and then a 1 to it), T16 captures and reloads on the next edge (rising, falling, or both, depending on CTR1 D5, D4) but continues to ignore subsequent edges.

When T16 reaches 0, it continues counting from FFFFh. Meanwhile, a status bit (CTR2 D5) is set, and an interrupt time-out can be generated if enabled (CTR2 D1).

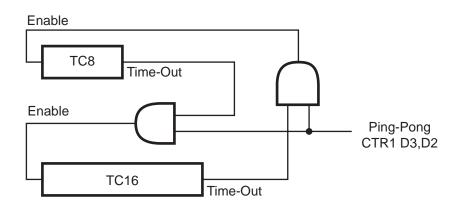

#### **Ping-Pong Mode**

This operation mode is only valid in transmit mode. T8 and T16 need to be programmed in Single-Pass Mode (CTR0 D6, CTR2 D6), and Ping-Pong Mode needs to be programmed in CTR1 D3, D2. You can begin the operation by enabling either T8 or T16 (CTR0 D7 or CTR2 D7). For example, if T8 is enabled, T8\_OUT is set to this initial value (CTR1 D1). According to T8\_OUT's level, TC8H or TC8L is loaded into T8. After the terminal count is reached, T8 is disabled and T16 is enabled. T16\_OUT switches to its initial value (CTR1 D0), data from TC16H and TC16L is loaded, and T16 starts to count. After T16 reaches the terminal count, it stops, T8 is enabled again, and the whole cycle repeats. Interrupts can be allowed when T8 or T16 reaches terminal control (CTR0 D1, CTR2 D1). To stop the Ping-Pong operation, write 00 to bits D3 and D2 of CTR1. See Figure 35.

**Note:** Enabling Ping-Pong operation while the counter/timers are running might cause intermittent counter/timer function. Disable the counter/timers and then reset the status flags before instituting this operation.

Figure 35. Ping-Pong Mode

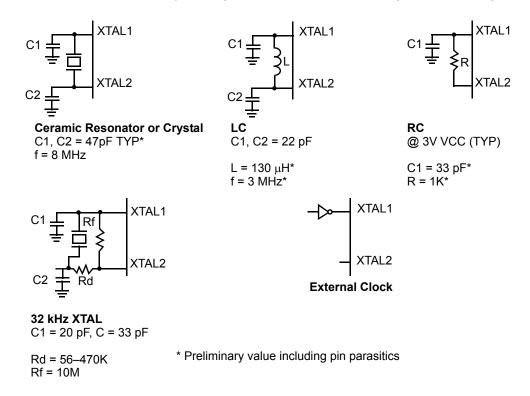

The crystal must be connected across XTAL1 and XTAL2 using the recommended capacitors (capacitance greater than or equal to 22 pF) from each pin to ground. The RC oscillator configuration is an external resistor connected from XTAL1 to XTAL2, with a frequency-setting capacitor from XTAL1 to ground (see Figure 38).

#### Figure 38. Oscillator Configuration

## **Power-On Reset (POR)**

A timer circuit clocked by a dedicated on-board RC oscillator is used for the Power-On Reset (POR) timer function. The POR time allows VCC and the oscillator circuit to stabilize before instruction execution begins.

The POR timer circuit is a one-shot timer triggered by one of three conditions:

- Power Fail to Power OK status.

- Stop-Mode Recovery (if D5 of SMR = 1).

- WDT Time-Out.

The POR time is a nominal 5 ms. Bit 5 of the Stop-Mode Register determines whether the POR timer is bypassed after Stop-Mode Recovery (typical for external clock, RC, and LC oscillators).

## **Comparator Output Port 3 (D0)**

Bit 0 controls the comparator used in Port 3. A 1 in this location brings the comparator outputs to P34 and P37, and a 0 releases the port to its standard I/O configuration.

### Port 0 Output Mode (D2)

Bit 2 controls the output mode of Port 0. A 1 in this location sets the output to push-pull, and a 0 sets the output to open-drain.

## Stop-Mode Recovery Register (SMR)

This register selects the clock divide value and determines the mode of Stop-Mode Recovery (Figure 40). All bits are write only except bit 7, which is read only. Bit 7 is a flag bit that is hardware set on the condition of STOP recovery and reset by a power-on cycle. Bit 6 controls whether a low level or a high level is required from the recovery source. Bit 5 controls the reset delay after recovery. Bits D2, D3, and D4 of the SMR register specify the source of the Stop-Mode Recovery signal. Bit D0 determines if SCLK/TCLK are divided by 16 or not. The SMR is located in Bank F of the Expanded Register Group at address 0BH.

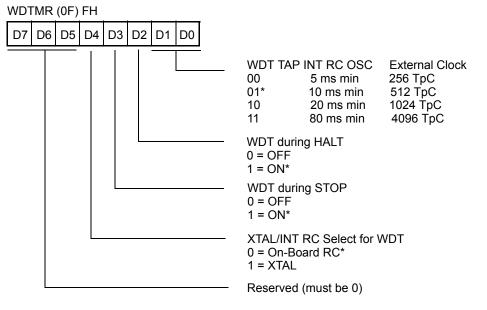

## Watch-Dog Timer Mode Register (WDTMR)

The WDT is a retriggerable one-shot timer that resets the Z8 if it reaches its terminal count. The WDT must initially be enabled by executing the WDT instruction and refreshed on subsequent executions of the WDT instruction. The WDT circuit is driven by an on-board RC oscillator or external oscillator from the XTAL1 pin. The WDT instruction affects the Zero (Z), Sign (S), and Overflow (V) flags.

The POR clock source is selected with bit 4 of the WDT register. Bit 0 and 1 control a tap circuit that determines the time-out period. Bit 2 determines whether the WDT is active during HALT, and Bit 3 determines WDT activity during STOP. Bits 5 through 7 are reserved. See Figure 43.

\* Default setting after reset

## Figure 43. Watch-Dog Timer Mode Register—Write Only

This register is accessible only during the first 60 processor cycles (SCLK) from the execution of the first instruction after Power-On-Reset, Watch-Dog Reset, or a Stop-Mode Recovery (Figure 40 on page 68). After this point, the register cannot be modified by any means, intentional or otherwise. The WDTMR cannot be read and is located in Bank F of the Expanded Register Group at address location 0FH. It is organized as shown in Figure 43.

# **EPROM Programming**

Table 31 describes the programming and test modes.

|                                              |                        |                | Device          | Pins            |                 |      |                 |                        |                       |      |

|----------------------------------------------|------------------------|----------------|-----------------|-----------------|-----------------|------|-----------------|------------------------|-----------------------|------|

| User/Test Mode<br>Device Pin #<br>User Modes | P33<br>V <sub>PP</sub> | P32<br>EPM     | Pref1<br>/CE    | P31<br>/OE      | P20<br>/PGM     | Addr | v <sub>cc</sub> | Port 1<br>CNFG<br>DATA | Test<br>ADDR<br>A0–A3 | Note |

| EPROM Read                                   | $V_{CC}$               | V <sub>H</sub> | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | Addr | 3.0 V           | Out                    | XX                    |      |

| Program                                      | $V_{PP}$               | $V_{CC}$       | V <sub>IL</sub> | $V_{\text{IH}}$ | V <sub>IL</sub> | Addr | 6.0 V           | In                     | XX                    |      |

| Program Verify                               | $V_{PP}$               | $V_{CC}$       | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | Addr | 6.0 V           | Out                    | XX                    |      |

| RC Option                                    | $V_{PP}$               | $V_{CC}$       | V <sub>H</sub>  | $V_{\text{IH}}$ | V <sub>IL</sub> | XX   | 6.0 V           | XX                     | XX                    |      |

| Margin Read                                  | $V_{VA}$               | $V_{H}$        | V <sub>IL</sub> | $V_{H}$         | V <sub>IH</sub> | Addr | 6.0 V           | Out                    | 00                    | 1    |

| Shadow Row Rd                                | $V_{CC}$               | $V_{H}$        | V <sub>IL</sub> | $V_{IL}$        | V <sub>IH</sub> | COL  | 3.0 V           | Out                    | 01                    | 1    |

| Shadow Row Prg                               | $V_{PP}$               | $V_{H}$        | V <sub>IL</sub> | $V_{\text{IH}}$ | V <sub>IL</sub> | COL  | 6.0 V           | In                     | 01                    | 1    |

| Shadow Row Ver                               | $V_{PP}$               | $V_{H}$        | V <sub>IL</sub> | $V_{IL}$        | V <sub>IH</sub> | COL  | 6.0 V           | Out                    | 01                    | 1    |

| Shadow Col Rd                                | $V_{CC}$               | $V_{H}$        | V <sub>IL</sub> | $V_{IL}$        | V <sub>IH</sub> | ROW  | 3.0 V           | Out                    | 02                    | 1    |

| Shadow Col Prg                               | $V_{PP}$               | $V_{H}$        | $V_{IL}$        | $V_{\text{IH}}$ | V <sub>IL</sub> | ROW  | 6.0 V           | In                     | 03                    | 1    |

| Shadow Col Ver                               | $V_{PP}$               | $V_{H}$        | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | ROW  | 6.0 V           | Out                    | 02                    | 1    |

| Page Prg 2 Byte                              | $V_{PP}$               | $V_{H}$        | V <sub>IL</sub> | $V_{\text{IH}}$ | V <sub>IL</sub> | TBD  | 6.0 V           | In                     | 04                    | 1    |

| Page Prg 4 Byte                              | $V_{PP}$               | $V_{H}$        | V <sub>IL</sub> | $V_{\text{IH}}$ | V <sub>IL</sub> | TBD  | 6.0 V           | In                     | 05                    | 1    |

| Page Prg 8 Byte                              | $V_{PP}$               | $V_{H}$        | V <sub>IL</sub> | $V_{\text{IH}}$ | V <sub>IL</sub> | TBD  | 6.0 V           | In                     | 06                    | 1    |

| Page Prg 16 Byte                             | $V_{PP}$               | $V_{H}$        | V <sub>IL</sub> | $V_{\text{IH}}$ | V <sub>IL</sub> | TBD  | 6.0 V           | In                     | 07                    | 1    |

### Table 31. Programming and Test Modes

Notes:

1. All test modes are entered by first setting up the corresponding test address and then latching the address by bringing the /OE to V<sub>H</sub> and then to V<sub>IL</sub>, except for the margin read which requires /OE to be kept at V<sub>H</sub>.  $V_{VA}$  = Variable from V<sub>CC</sub> to V<sub>PP</sub>  $V_{PP}$  = 12.5 V ± 0.5 V  $V_{H}$  = 12.5 V ± 0.5 V  $V_{H}$  = 3 V

$V_{IL} = 0 V$ XX = Irrelevant

$I_{PP}$  during programming = 40 mA maximum

$I_{CC}$  during programming, verify, or read = 40 mA maximum.

Table 32 lists the timing of the programming waveform.

#### Table 32. Timing of Programming Waveform

| Parameters | Name                       | Min  | Max | Units |

|------------|----------------------------|------|-----|-------|

| 1          | Address Setup Time         | 2    |     | μs    |

| 2          | Data Setup Time            | 2    |     | μs    |

| 3          | V <sub>PP</sub> Setup Time | 2    |     | μs    |

| 4          | V <sub>CC</sub> Setup Time | 2    |     | μs    |

| 5          | Chip Enable Setup Time     | 2    |     | μs    |

| 6          | Program Pulse Width        | 0.95 |     | μs    |

| 7          | Data Hold Time             | 2    |     | μs    |

| 8          | /OE Setup Time             | 2    |     | μs    |

| 9          | Data Access Time           |      | 200 | ns    |

| 10         | Data Output Float Time     |      | 100 | ns    |

| 11         | Overprogram Pulse Width    | 2.85 |     | ms    |

| 12         | EPM Setup Time             | 2    |     | μs    |

| 13         | /PGM Setup Time            | 2    |     | μs    |

| 14         | Address to /OE Setup Time  | 2    |     | μs    |

| 15         | Option Program Pulse Width | 78   |     | ms    |

Figure 45 shows the EPROM read timing diagram. Figure 46 on page 79 shows the EPROM program and verify timing diagram. Figure 47 on page 80 shows the programming EPROM, RAM protect, and 16K size selection timing diagram.

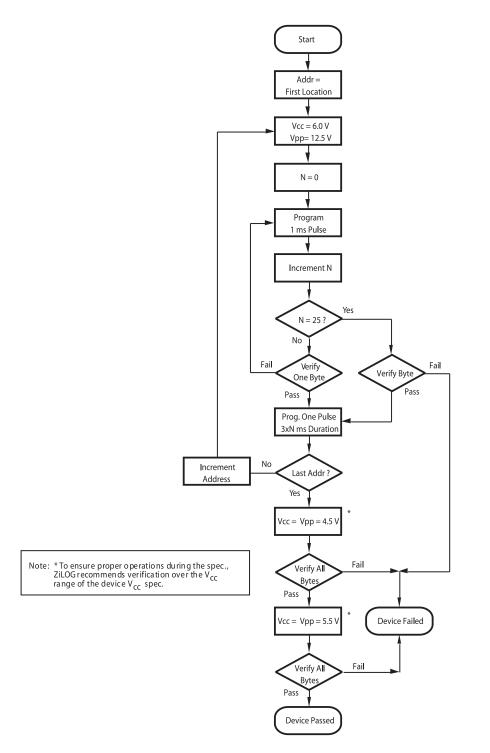

Figure 48. Programming Flowchart

# **Package Information**

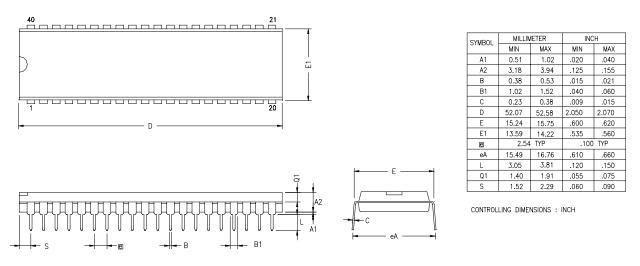

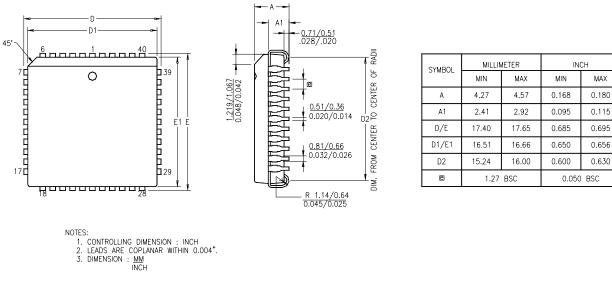

The Z86E72/73 is available in 40-pin DIP (Figure 67), 44-pin LQFP (Figure 68 on page 95), and 44-pin PLCC (Figure 69 on page 96) packages.

Figure 67. 40-Pin DIP Package Diagram

Figure 69. 44-Pin PLCC Package Diagram