Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 11x8b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 28-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f722a-e-so |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

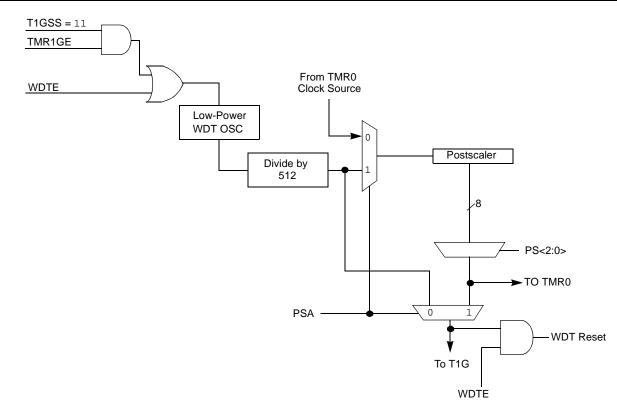

#### 3.4.2 WDT CONTROL

The WDTE bit is located in the Configuration Word Register 1. When set, the WDT runs continuously.

The PSA and PS<2:0> bits of the OPTION register control the WDT period. See **Section 11.0 "Timer0 Module"** for more information.

#### TABLE 3-1: WDT STATUS

| Conditions                                               | WDT                          |

|----------------------------------------------------------|------------------------------|

| WDTE = 0                                                 | Cleared                      |

| CLRWDT Command                                           |                              |

| Exit Sleep + System Clock = T1OSC, EXTRC, INTOSC, EXTCLK |                              |

| Exit Sleep + System Clock = XT, HS, LP                   | Cleared until the end of OST |

#### 4.5.2 PIE1 REGISTER

The PIE1 register contains the interrupt enable bits, as shown in Register 4-2.

**Note:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

| R/W-0                                 | R/W-0        | R/W-0                                                                                                         | R/W-0          | R/W-0           | R/W-0           | R/W-0           | R/W-0  |  |  |  |  |

|---------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------|----------------|-----------------|-----------------|-----------------|--------|--|--|--|--|

| TMR1GIE                               | ADIE         | RCIE                                                                                                          | TXIE           | SSPIE           | CCP1IE          | TMR2IE          | TMR1IE |  |  |  |  |

| bit 7                                 |              |                                                                                                               |                |                 |                 |                 | bit C  |  |  |  |  |

| Legend:                               |              |                                                                                                               |                |                 |                 |                 |        |  |  |  |  |

| •                                     | bit          | W = Writable                                                                                                  | hit            | II – Unimple    | mented bit, rea | d as '0'        |        |  |  |  |  |

| R = Readable bit<br>-n = Value at POR |              | '1' = Bit is set                                                                                              |                | 0' = Bit is cle |                 | x = Bit is unki | nown   |  |  |  |  |

|                                       |              |                                                                                                               |                |                 | carea           |                 |        |  |  |  |  |

| bit 7                                 | TMR1GIE: 7   | Timer1 Gate Inte                                                                                              | rrupt Enable I | bit             |                 |                 |        |  |  |  |  |

|                                       |              | he Timer1 gate                                                                                                | •              |                 | pt              |                 |        |  |  |  |  |

|                                       |              | the Timer1 gate                                                                                               |                |                 |                 |                 |        |  |  |  |  |

| bit 6                                 | ADIE: A/D C  | Converter (ADC)                                                                                               | Interrupt Ena  | ble bit         |                 |                 |        |  |  |  |  |

|                                       |              | the ADC interru                                                                                               | •              |                 |                 |                 |        |  |  |  |  |

|                                       |              | s the ADC interru                                                                                             | •              |                 |                 |                 |        |  |  |  |  |

| bit 5                                 |              | : USART Receive Interrupt Enable bit                                                                          |                |                 |                 |                 |        |  |  |  |  |

|                                       |              | <ul> <li>1 = Enables the USART receive interrupt</li> <li>0 = Disables the USART receive interrupt</li> </ul> |                |                 |                 |                 |        |  |  |  |  |

| bit 4                                 |              |                                                                                                               | •              |                 |                 |                 |        |  |  |  |  |

| DIL 4                                 |              | IE: USART Transmit Interrupt Enable bit<br>= Enables the USART transmit interrupt                             |                |                 |                 |                 |        |  |  |  |  |

|                                       |              | the USART tra                                                                                                 | •              |                 |                 |                 |        |  |  |  |  |

| bit 3                                 |              | chronous Serial                                                                                               |                |                 | bit             |                 |        |  |  |  |  |

|                                       | •            | the SSP interru                                                                                               | . ,            | •               |                 |                 |        |  |  |  |  |

|                                       | 0 = Disables | s the SSP interru                                                                                             | ipt            |                 |                 |                 |        |  |  |  |  |

| bit 2                                 | CCP1IE: CC   | CP1 Interrupt En                                                                                              | able bit       |                 |                 |                 |        |  |  |  |  |

|                                       |              | the CCP1 interr                                                                                               |                |                 |                 |                 |        |  |  |  |  |

|                                       |              | the CCP1 inter                                                                                                | •              |                 |                 |                 |        |  |  |  |  |

| bit 1                                 |              | IR2IE: TMR2 to PR2 Match Interrupt Enable bit                                                                 |                |                 |                 |                 |        |  |  |  |  |

|                                       |              | the Timer2 to P                                                                                               |                |                 |                 |                 |        |  |  |  |  |

| hit O                                 |              | the Timer2 to F                                                                                               |                | •               |                 |                 |        |  |  |  |  |

| bit 0                                 |              | ner1 Overflow Ir                                                                                              |                |                 |                 |                 |        |  |  |  |  |

|                                       |              | the Timer1 over<br>the Timer1 ove                                                                             |                |                 |                 |                 |        |  |  |  |  |

#### REGISTER 4-2: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

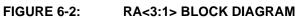

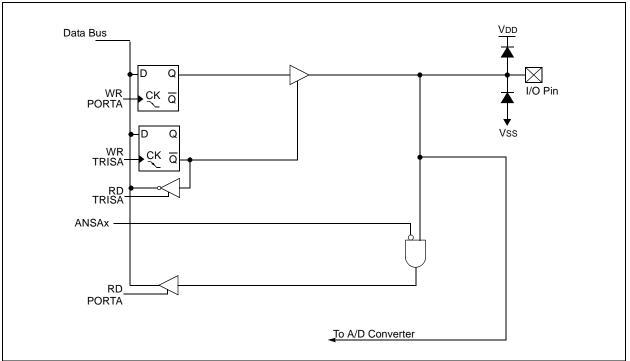

## 6.0 I/O PORTS

There are as many as thirty-five general purpose I/O pins available. Depending on which peripherals are enabled, some or all of the pins may not be available as general purpose I/O. In general, when a peripheral is enabled, the associated pin may not be used as a general purpose I/O pin.

#### 6.1 Alternate Pin Function

The Alternate Pin Function Control (APFCON) register is used to steer specific peripheral input and output functions between different pins. The APFCON register is shown in Register 6-1. For this device family, the following functions can be moved between different pins:

- SS (Slave Select)

- CCP2

#### REGISTER 6-1: APFCON: ALTERNATE PIN FUNCTION CONTROL REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0   |

|-------|-----|-----|-----|-----|-----|-------|---------|

| —     | —   | —   | —   | —   |     | SSSEL | CCP2SEL |

| bit 7 |     |     |     |     |     |       | bit 0   |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 7-2 | Unimplemented: Read as '0'.                                                                                                       |

|---------|-----------------------------------------------------------------------------------------------------------------------------------|

| bit 1   | SSSEL: SS Input Pin Selection bit                                                                                                 |

|         | 0 = <u>SS</u> function is on RA5/AN4/CPS7/SS/VCAP<br>1 = <u>SS</u> function is on RA0/AN0/SS/VCAP                                 |

| bit 0   | <b>CCP2SEL:</b> CCP2 Input/Output Pin Selection bit<br>0 = CCP2 function is on RC1/T1OSI/CCP2<br>1 = CCP2 function is on RB3/CCP2 |

# PIC16(L)F722A/723A

| TABLE 6-4: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTC |

|------------|--------------------------------------------|

|            |                                            |

| Name    | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0   | Register<br>on Page |

|---------|---------|---------|---------|---------|---------|--------|--------|---------|---------------------|

| APFCON  | —       | _       | _       | _       | —       | —      | SSSEL  | CCP2SEL | 42                  |

| CCP1CON | —       | _       | DC1B1   | DC1B0   | CCP1M3  | CCP1M2 | CCP1M1 | CCP1M0  | 115                 |

| CCP2CON | —       | —       | DC2B1   | DC2B0   | CCP2M3  | CCP2M2 | CCP2M1 | CCP2M0  | 115                 |

| PORTC   | RC7     | RC6     | RC5     | RC4     | RC3     | RC2    | RC1    | RC0     | 62                  |

| RCSTA   | SPEN    | RX9     | SREN    | CREN    | ADDEN   | FERR   | OERR   | RX9D    | 134                 |

| SSPCON  | WCOL    | SSPOV   | SSPEN   | CKP     | SSPM3   | SSPM2  | SSPM1  | SSPM0   | 152                 |

| SSPSTAT | SMP     | CKE     | D/A     | Р       | S       | R/W    | UA     | BF      | 153                 |

| T1CON   | TMR1CS1 | TMR1CS0 | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | —      | TMR10N  | 103                 |

| TXSTA   | CSRC    | TX9     | TXEN    | SYNC    | —       | BRGH   | TRMT   | TX9D    | 133                 |

| TRISC   | TRISC7  | TRISC6  | TRISC5  | TRISC4  | TRISC3  | TRISC2 | TRISC1 | TRISC0  | 62                  |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTC.

#### 11.1.3 SOFTWARE PROGRAMMABLE PRESCALER

A single software programmable prescaler is available for use with either Timer0 or the Watchdog Timer (WDT), but not both simultaneously. The prescaler assignment is controlled by the PSA bit of the OPTION register. To assign the prescaler to Timer0, the PSA bit must be cleared to a '0'.

There are eight prescaler options for the Timer0 module ranging from 1:2 to 1:256. The pres ca le values are selectable via the PS<2:0> bits of the OPTION register. In order to have a 1:1 prescaler value for the Timer0 module, the prescaler must be assigned to the WDT module.

The prescaler is not readable or writable. When assigned to the Timer0 module, all instructions writing to the TMR0 register will clear the prescaler.

| Note: | When the prescaler is assigned to WDT, a    |

|-------|---------------------------------------------|

|       | CLRWDT instruction will clear the prescaler |

|       | along with the WDT.                         |

#### 11.1.4 TIMER0 INTERRUPT

Timer0 will generate an interrupt when the TMR0 register overflows from PH to 00h. The T0IF interrupt flag bit of the INTCON register is set every time the TMR0 register overflows, regardless of whether or not the Timer0 interrupt is enabled. The T0IF bit can only be cleared in software. The Timer0 interrupt enable is the T0IE bit of the INTCON register.

| Note: | The Timer0 interrupt cannot wake the    |  |  |  |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|--|--|--|

|       | processor from Sleep since the timer is |  |  |  |  |  |  |  |

|       | frozen during Sleep.                    |  |  |  |  |  |  |  |

#### 11.1.5 8-BIT COUNTER MODE SYNCHRONIZATION

When in 8-Bit Counter mode, the incrementing edge on the T0CKI pin must be synchronized to the instruction clock. Synchronization can be accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the instruction clock. The high and low periods of the external clocking source must meet the timing requirements as shown in **Section 23.0** "**Electrical Specifications**".

| Name    | Bit 7       | Bit 6         | Bit 5        | Bit 4        | Bit 3          | Bit 2     | Bit 1  | Bit 0  | Register<br>on Page |  |

|---------|-------------|---------------|--------------|--------------|----------------|-----------|--------|--------|---------------------|--|

| ANSELB  | —           | —             | ANSB5        | ANSB4        | ANSB3          | ANSB2     | ANSB1  | ANSB0  | 53                  |  |

| CCP1CON | —           | —             | DC1B1        | DC1B0        | CCP1M3         | CCP1M2    | CCP1M1 | CCP1M0 | 115                 |  |

| CCP2CON | —           | —             | DC2B1        | DC2B0        | CCP2M3         | CCP2M2    | CCP2M1 | CCP2M0 | 115                 |  |

| INTCON  | GIE         | PEIE          | T0IE         | INTE         | RBIE           | T0IF      | INTF   | RBIF   | 36                  |  |

| PIE1    | TMR1GIE     | ADIE          | RCIE         | TXIE         | SSPIE          | CCP1IE    | TMR2IE | TMR1IE | 37                  |  |

| PIR1    | TMR1GIF     | ADIF          | RCIF         | TXIF         | SSPIF          | CCP1IF    | TMR2IF | TMR1IF | 39                  |  |

| PORTB   | RB7         | RB6           | RB5          | RB4          | RB3            | RB2       | RB1    | RB0    | 52                  |  |

| TMR1H   | Holding Reg | ister for the | Most Signifi | cant Byte of | the 16-bit T   | MR1 Regis | ter    |        | 99                  |  |

| TMR1L   | Holding Reg | ister for the | Least Signif | icant Byte o | f the 16-bit 7 | MR1 Regis | ster   |        | 99                  |  |

| TRISB   | TRISB7      | TRISB6        | TRISB5       | TRISB4       | TRISB3         | TRISB2    | TRISB1 | TRISB0 | 52                  |  |

| TRISC   | TRISC7      | TRISC6        | TRISC5       | TRISC4       | TRISC3         | TRISC2    | TRISC1 | TRISC0 | 62                  |  |

| T1CON   | TMR1CS1     | TMR1CS0       | T1CKPS1      | T1CKPS0      | T1OSCEN        | T1SYNC    | _      | TMR10N | 103                 |  |

| T1GCON  | TMR1GE      | T1GPOL        | T1GTM        | T1GSPM       | T1GGO/<br>DONE | T1GVAL    | T1GSS1 | T1GSS0 | 104                 |  |

#### TABLE 12-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER1

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

| REGISTER 14-2: CPSCON1: CAPACITIVE SENSING CONTROL REGISTER 1              |     |     |     |      |        |        |        |  |  |  |

|----------------------------------------------------------------------------|-----|-----|-----|------|--------|--------|--------|--|--|--|

| U-0                                                                        | U-0 | U-0 | U-0 | U-0  | R/W-0  | R/W-0  | R/W-0  |  |  |  |

| —                                                                          | —   | —   | —   | _    | CPSCH2 | CPSCH1 | CPSCH0 |  |  |  |

| bit 7                                                                      |     |     |     |      |        |        | bit 0  |  |  |  |

|                                                                            |     |     |     |      |        |        |        |  |  |  |

| Legend:                                                                    |     |     |     |      |        |        |        |  |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'       |     |     |     |      |        |        |        |  |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |     |     |     | nown |        |        |        |  |  |  |

| bit 7-3 | Unimplemented: Read as '0'                         |  |  |  |  |  |  |

|---------|----------------------------------------------------|--|--|--|--|--|--|

| bit 2-0 | CPSCH<2:0>: Capacitive Sensing Channel Select bits |  |  |  |  |  |  |

|         | If CPSON = 0:                                      |  |  |  |  |  |  |

|         | These bits are ignored. No channel is selected.    |  |  |  |  |  |  |

|         | <u>If CPSON = 1</u> :                              |  |  |  |  |  |  |

|         | 000 = channel 0, (CPS0)                            |  |  |  |  |  |  |

|         | 001 = channel 1, (CPS1)                            |  |  |  |  |  |  |

|         | 010 = channel 2, (CPS2)                            |  |  |  |  |  |  |

|         | 011 = channel 3, (CPS3)                            |  |  |  |  |  |  |

|         | 100 = channel 4, (CPS4)                            |  |  |  |  |  |  |

|         | 101 = channel 5, (CPS5)                            |  |  |  |  |  |  |

|         | 110 = channel 6, (CPS6)                            |  |  |  |  |  |  |

|         | 111 = channel 7, (CPS7)                            |  |  |  |  |  |  |

#### TABLE 14-2: SUMMARY OF REGISTERS ASSOCIATED WITH CAPACITIVE SENSING

| Name       | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Register<br>on Page |

|------------|---------|---------|---------|---------|---------|--------|---------|---------|---------------------|

| ANSELA     |         | —       | ANSA5   | ANSA4   | ANSA3   | ANSA2  | ANSA1   | ANSA0   | 44                  |

| ANSELB     | -       | —       | ANSB5   | ANSB4   | ANSB3   | ANSB2  | ANSB1   | ANSB0   | 53                  |

| OPTION_REG | RBPU    | INTEDG  | TOCS    | T0SE    | PSA     | PS2    | PS1     | PS0     | 19                  |

| PIE1       | TMR1GIE | ADIE    | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 37                  |

| PIR1       | TMR1GIF | ADIF    | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 39                  |

| T1CON      | TMR1CS1 | TMR1CS0 | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | —       | TMR10N  | 103                 |

| T2CON      | -       | TOUTPS3 | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | 107                 |

| TRISA      | TRISA7  | TRISA6  | TRISA5  | TRISA4  | TRISA3  | TRISA2 | TRISA1  | TRISA0  | 43                  |

| TRISB      | TRISB7  | TRISB6  | TRISB5  | TRISB4  | TRISB3  | TRISB2 | TRISB1  | TRISB0  | 52                  |

Legend: - = Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the capacitive sensing module.

#### 16.3.1.4 Synchronous Master Reception

Data is received at the RX/DT pin. The RX/DT pin output driver is automatically disabled when the AUSART is configured for synchronous master receive operation.

In Synchronous mode, reception is enabled by setting either the Single Receive Enable bit (SREN of the RCSTA register) or the Continuous Receive Enable bit (CREN of the RCSTA register).

When SREN is set and CREN is clear, only as many clock cycles are generated as there are data bits in a single character. The SREN bit is automatically cleared at the completion of one character. When CREN is set, clocks are continuously generated until CREN is cleared. If CREN is cleared in the middle of a character the CK clock stops immediately and the partial character is discarded. If SREN and CREN are both set, then SREN is cleared at the completion of the first character and CREN takes precedence.

To initiate reception, set either SREN or CREN. Data is sampled at the RX/DT pin on the trailing edge of the TX/CK clock pin and is shifted into the Receive Shift Register (RSR). When a complete character is received into the RSR, the RCIF bit of the PIR1 register is set and the character is automatically transferred to the two character receive FIFO. The Least Significant eight bits of the top character in the receive FIFO are available in RCREG. The RCIF bit remains set as long as there are un-read characters in the receive FIFO.

#### 16.3.1.5 Slave Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a slave receives the clock on the TX/CK line. The TX/ CK pin output driver is automatically disabled when the device is configured for synchronous slave transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One data bit is transferred for each clock cycle. Only as many clock cycles should be received as there are data bits.

#### 16.3.1.6 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before RCREG is read to access the FIFO. When this happens the OERR bit of the RCSTA register is set. Previous data in the FIFO will not be overwritten. The two characters in the FIFO buffer can be read, however, no additional characters will be received until the error is cleared. The OERR bit can only be cleared by clearing the overrun condition. If the overrun error occurred when the SREN bit is set and CREN is clear then the error is cleared by reading RCREG. If the overrun occurred when the CREN bit is set then the error condition is cleared by either clearing the CREN bit of the RCSTA register.

#### 16.3.1.7 Receiving 9-bit Characters

The AUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set, the AUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth, and Most Significant, data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREG.

Address detection in Synchronous modes is not supported, therefore the ADDEN bit of the RCSTA register must be cleared.

## 16.3.1.8 Synchronous Master Reception Setup:

- 1. Initialize the SPBRG register for the appropriate baud rate. Set or clear the BRGH bit, as required, to achieve the desired baud rate.

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Ensure bits CREN and SREN are clear.

- 4. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit reception is desired, set bit RX9.

- 6. Verify address detection is disabled by clearing the ADDEN bit of the RCSTA register.

- 7. Start reception by setting the SREN bit or for continuous reception, set the CREN bit.

- Interrupt flag bit RCIF of the PIR1 register will be set when reception of a character is complete. An interrupt will be generated if the RCIE interrupt enable bit of the PIE1 register was set.

- 9. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 10. Read the 8-bit received data by reading the RCREG register.

- 11. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit, which resets the AUSART.

## 18.0 PROGRAM MEMORY READ

The Flash program memory is readable during normal operation over the full VDD range of the device. To read data from program memory, five Special Function Registers (SFRs) are used:

- PMCON1

- PMDATL

- PMDATH

- PMADRL

- PMADRH

The value written to the PMADRH:PMADRL register pair determines which program memory location is read. The read operation will be initiated by setting the RD bit of the PMCON1 register. The program memory Flash controller takes two instructions to complete the read. As a consequence, after the RD bit has been set, the next two instructions will be ignored. To avoid conflict with program execution, it is recommended that the two instructions following the setting of the RD bit are NOP. When the read completes, the result is placed in the PMDATLH:PMDATL register pair. Refer to Example 18-1 for sample code.

**Note:** Code-protect does not effect the CPU from performing a read operation on the program memory. For more information, refer to **Section 8.2 "Code Protection"**

#### EXAMPLE 18-1: PROGRAM MEMORY READ

BANKSEL PMADRL ; MOVE MS PROG ADDR, W; MOVWF PMADRH ;MS Byte of Program Address to read MOVF LS\_PROG\_ADDR, W; MOVWF PMADRL ;LS Byte of Program Address to read BANKSEL PMCON1 ; BSF PMCON1, RD; Initiate Read Required NOP NOP ;Any instructions here are ignored as program ;memory is read in second cycle after BSF BANKSEL PMDATL ; MOVF PMDATL, W;W = LS Byte of Program Memory Read MOVWF LOWPMBYTE; MOVF PMDATH, W;W = MS Byte of Program Memory Read MOVWF HIGHPMBYTE;

## 21.0 INSTRUCTION SET SUMMARY

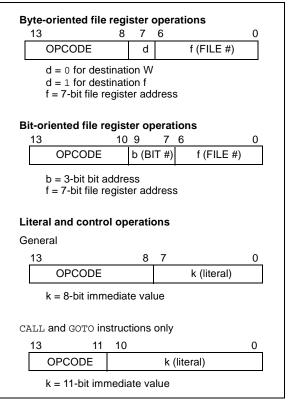

The PIC16(L)F722A/723A instruction set is highly orthogonal and is comprised of three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

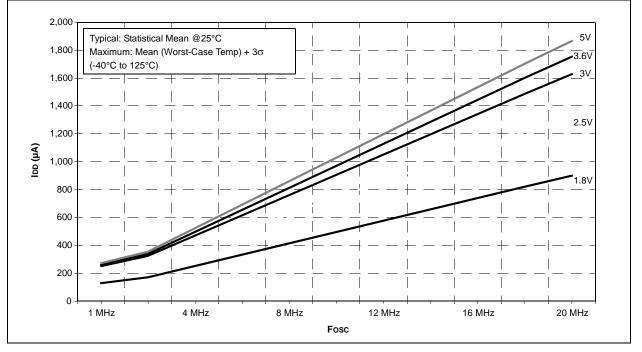

Each PIC16 instruction is a 14-bit word divided into an **opcode**, which specifies the instruction type and one or more **operands**, which further specify the operation of the instruction. The formats for each of the categories is presented in Figure 21-1, while the various opcode fields are summarized in Table 21-1.

Table 21-2 lists the instructions recognized by the MPASM<sup>TM</sup> assembler.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator, which selects the bit affected by the operation, while 'f' represents the address of the file in which the bit is located.

For **literal and control** operations, 'k' represents an 8bit or 11-bit constant, or literal value.

One instruction cycle consists of four oscillator periods; for an oscillator frequency of 4 MHz, this gives a nominal instruction execution time of 1  $\mu$ s. All instructions are executed within a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of an instruction. When this occurs, the execution takes two instruction cycles, with the second cycle executed as a NOP.

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

### 21.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

For example, a CLRF PORTB instruction will read PORTB, clear all the data bits, then write the result back to PORTB. This example would have the unintended consequence of clearing the condition that set the RBIF flag.

#### TABLE 21-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                     |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                            |

| W     | Working register (accumulator)                                                                                                                                                  |

| b     | Bit address within an 8-bit file register                                                                                                                                       |

| k     | Literal field, constant data or label                                                                                                                                           |

| x     | Don't care location (= 0 or 1).<br>The assembler will generate code with $x = 0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; $d = 0$ : store result in W,<br>d = 1: store result in file register f.<br>Default is $d = 1$ .                                                             |

| PC    | Program Counter                                                                                                                                                                 |

| TO    | Time-out bit                                                                                                                                                                    |

| С     | Carry bit                                                                                                                                                                       |

| DC    | Digit carry bit                                                                                                                                                                 |

| Z     | Zero bit                                                                                                                                                                        |

| PD    | Power-down bit                                                                                                                                                                  |

#### FIGURE 21-1: GENERAL FORMAT FOR INSTRUCTIONS

| PIC16LF722A/723A |        |                                                        | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                                                      |                                 |                  |                                                                                                                                                                                                                                                                        |  |  |  |  |

|------------------|--------|--------------------------------------------------------|-------------------------------------------------------|------------------------------------------------------|---------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                  |        |                                                        |                                                       | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                                 |                  |                                                                                                                                                                                                                                                                        |  |  |  |  |

| Param.<br>No.    | Sym.   | Characteristic                                         | Min.                                                  | Тур†                                                 | Max.                            | Units            | Conditions                                                                                                                                                                                                                                                             |  |  |  |  |

| D001             | Vdd    | Supply Voltage                                         |                                                       |                                                      |                                 |                  |                                                                                                                                                                                                                                                                        |  |  |  |  |

|                  |        | PIC16LF722A/723A                                       | 1.8<br>1.8<br>2.3<br>2.5                              |                                                      | 3.6<br>3.6<br>3.6<br>3.6        | V<br>V<br>V<br>V | Fosc $\leq$ 16 MHz: HFINTOSC, EC<br>Fosc $\leq$ 4 MHz<br>Fosc $\leq$ 20 MHz, EC<br>Fosc $\leq$ 20 MHz, HS                                                                                                                                                              |  |  |  |  |

| D001             |        | PIC16F722A/723A                                        | 1.8<br>1.8<br>2.3<br>2.5                              |                                                      | 5.5<br>5.5<br>5.5<br>5.5<br>5.5 | V<br>V<br>V<br>V | Fosc $\leq$ 16 MHz: HFINTOSC, EC<br>Fosc $\leq$ 4 MHz<br>Fosc $\leq$ 20 MHz, EC<br>Fosc $\leq$ 20 MHz, HS                                                                                                                                                              |  |  |  |  |

| D002* Vdr        |        | RAM Data Retention Voltage <sup>(1)</sup>              |                                                       |                                                      |                                 |                  |                                                                                                                                                                                                                                                                        |  |  |  |  |

|                  |        | PIC16LF722A/723A                                       | 1.5                                                   | —                                                    | -                               | V                | Device in Sleep mode                                                                                                                                                                                                                                                   |  |  |  |  |

| D002*            |        | PIC16F722A/723A                                        | 1.7                                                   | _                                                    | _                               | V                | Device in Sleep mode                                                                                                                                                                                                                                                   |  |  |  |  |

|                  | VPOR*  | Power-on Reset Release Voltage                         | —                                                     | 1.6                                                  | -                               | V                |                                                                                                                                                                                                                                                                        |  |  |  |  |

|                  | VPORR* | Power-on Reset Rearm Voltage                           |                                                       |                                                      |                                 |                  |                                                                                                                                                                                                                                                                        |  |  |  |  |

|                  |        | PIC16LF722A/723A                                       |                                                       | 0.8                                                  | -                               | V                | Device in Sleep mode                                                                                                                                                                                                                                                   |  |  |  |  |

|                  |        | PIC16F722A/723A                                        |                                                       | 1.7                                                  | -                               | V                | Device in Sleep mode                                                                                                                                                                                                                                                   |  |  |  |  |

| D003             | Vfvr   | Fixed Voltage Reference Voltage,<br>Initial Accuracy   | -5.5<br>-5.5<br>-5.5                                  | <br> <br>                                            | 5.5<br>5.5<br>5.5               | %<br>%<br>%      | $ \begin{array}{l} {\sf VFVR} = 1.024{\sf V},  {\sf VDD} \geq 2.5{\sf V} \\ {\sf VFVR} = 2.048{\sf V},  {\sf VDD} \geq 2.5{\sf V} \\ {\sf VFVR} = 4.096{\sf V},  {\sf VDD} \geq 4.75{\sf V}; \\ {\sf -40} \leq {\sf TA} \leq 85^{\circ}{\sf C} \end{array} $           |  |  |  |  |

|                  |        |                                                        | -6<br>-6<br>-6                                        |                                                      | 6<br>6<br>6                     | %<br>%<br>%      | $\label{eq:VFVR} \begin{split} &V{\sf FVR} = 1.024{\sf V},  {\sf VDD} \geq 2.5{\sf V} \\ &V{\sf FVR} = 2.048{\sf V},  {\sf VDD} \geq 2.5{\sf V} \\ &V{\sf FVR} = 4.096{\sf V},  {\sf VDD} \geq 4.75{\sf V}; \\ &-40 \leq {\sf TA} \leq 125{\rm ^{\circ}C} \end{split}$ |  |  |  |  |

| D004*            | SVDD   | VDD Rise Rate to ensure internal Power-on Reset signal | 0.05                                                  | —                                                    | —                               | V/ms             | See Section 3.2 "Power-on Reset (POR)" for details.                                                                                                                                                                                                                    |  |  |  |  |

## 23.1 DC Characteristics: PIC16(L)F722A/723A-I/E (Industrial, Extended)

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

#### TABLE 23-7: PIC16F722A/723A A/D CONVERTER (ADC) CHARACTERISTICS:

| Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |                                                   |      |      |      |       |                                                                     |

|----------------------------------------------------------------------------------------------------------------------|------|---------------------------------------------------|------|------|------|-------|---------------------------------------------------------------------|

| Param<br>No.                                                                                                         | Sym. | Characteristic                                    | Min. | Тур† | Max. | Units | Conditions                                                          |

| AD01                                                                                                                 | Nr   | Resolution                                        | —    | _    | 8    | bit   |                                                                     |

| AD02                                                                                                                 | EIL  | Integral Error                                    | —    | _    | ±1.7 | LSb   | VREF = 3.0V                                                         |

| AD03                                                                                                                 | Edl  | Differential Error                                | _    | _    | ±1   | LSb   | No missing codes<br>VREF = 3.0V                                     |

| AD04                                                                                                                 | EOFF | Offset Error                                      | —    | _    | ±2.2 | LSb   | VREF = 3.0V                                                         |

| AD05                                                                                                                 | Egn  | Gain Error                                        | _    | _    | ±1.5 | LSb   | VREF = 3.0V                                                         |

| AD06                                                                                                                 | Vref | Reference Voltage <sup>(3)</sup>                  | 1.8  | _    | Vdd  | V     |                                                                     |

| AD07                                                                                                                 | VAIN | Full-Scale Range                                  | Vss  | _    | VREF | V     |                                                                     |

| AD08                                                                                                                 | ZAIN | Recommended Impedance of<br>Analog Voltage Source | _    | _    | 50   |       | Can go higher if external 0.01µF capacitor is present on input pin. |

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Total Absolute Error includes integral, differential, offset and gain errors.

- 2: The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

- **3:** When ADC is off, it will not consume any current other than leakage current. The power-down current specification includes any such leakage from the ADC module.

#### TABLE 23-8: PIC16F722A/723A A/D CONVERSION REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated)         Operating temperature       -40°C ≤ TA ≤ +125°C |      |                                                                 |            |         |            |          |                                          |

|-----------------------------------------------------------------------------------------------------------------|------|-----------------------------------------------------------------|------------|---------|------------|----------|------------------------------------------|

| Param<br>No.                                                                                                    | Sym. | Characteristic                                                  | Min.       | Тур†    | Max.       | Units    | Conditions                               |

| AD130*                                                                                                          | Tad  | A/D Clock Period<br>A/D Internal RC Oscillator<br>Period        | 1.0<br>1.0 | <br>2.0 | 9.0<br>6.0 | μs<br>μs | Tosc-based<br>ADCS<1:0> = 11 (ADRC mode) |

| AD131                                                                                                           | TCNV | Conversion Time (not including Acquisition Time) <sup>(1)</sup> | _          | 10.5    | —          | Tad      | Set GO/DONE bit to conversion complete   |

| AD132*                                                                                                          | TACQ | Acquisition Time                                                | —          | 1.0     | —          | μs       |                                          |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note** 1: The ADRES register may be read on the following TCY cycle.

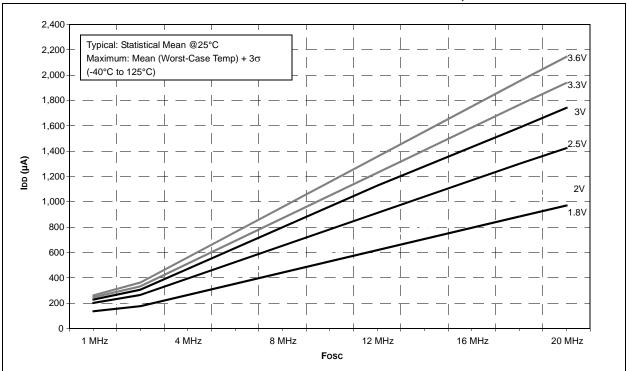

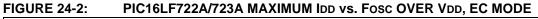

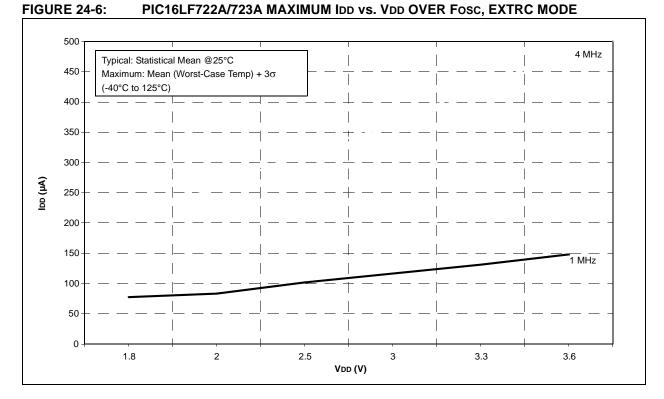

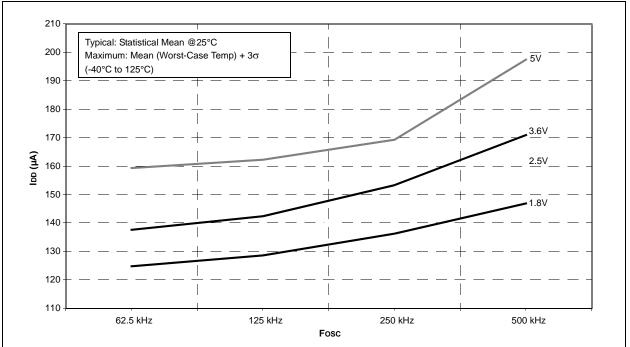

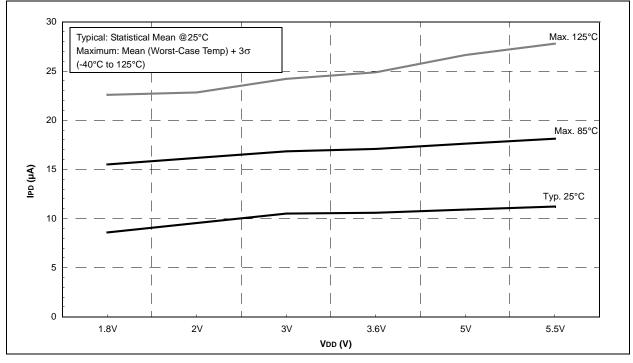

FIGURE 24-18: PIC16LF722A/723A IDD vs. VDD, LP MODE

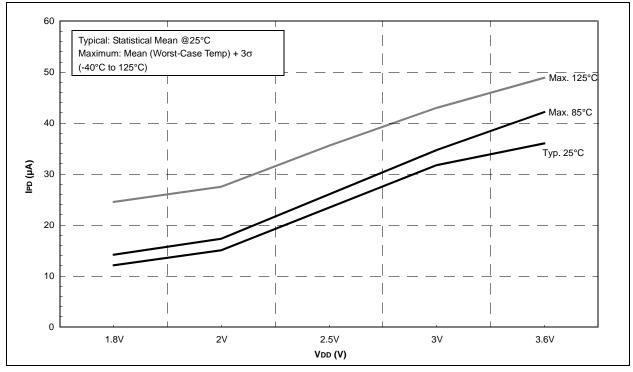

#### FIGURE 24-36: PIC16LF722A/723A CAP SENSE HIGH POWER IPD vs. VDD

## PIC16(L)F722A/723A

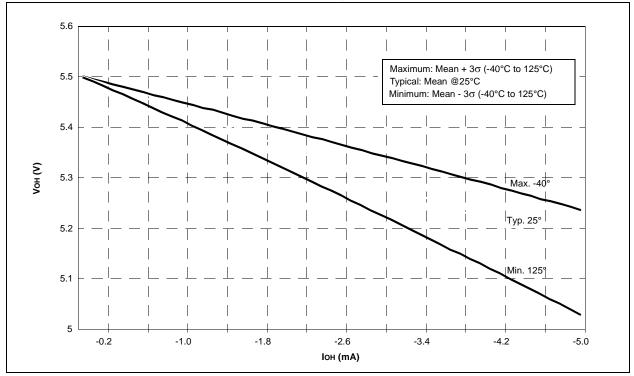

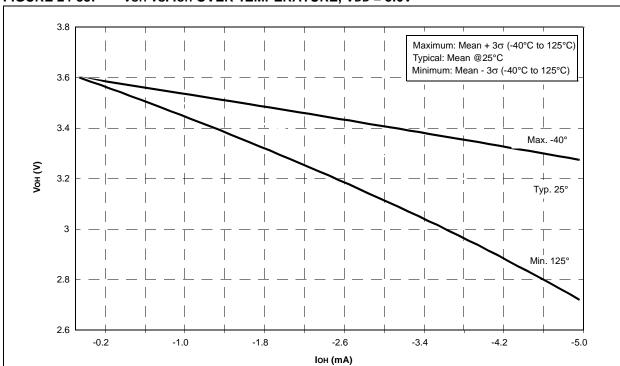

FIGURE 24-53: VOH vs. IOH OVER TEMPERATURE, VDD = 3.6V

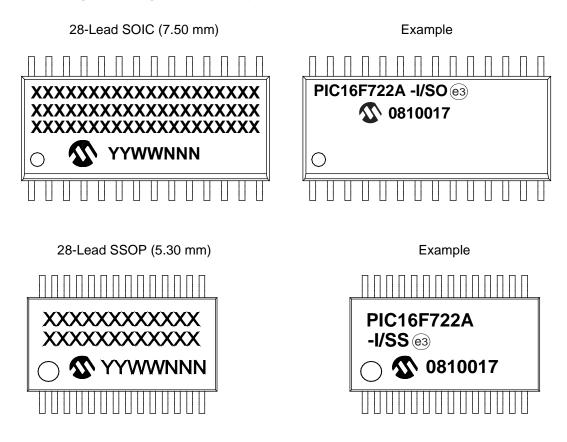

### 25.1 Package Marking Information (Continued)

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC <sup>®</sup> designator ((e3))<br>can be found on the outer packaging for this package. |

|--------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:  | be carrie                                | nt the full Microchip part number cannot be marked on one line, it will<br>d over to the next line, thus limiting the number of available<br>s for customer-specific information.                                                                                                                                                                                                           |

\* Standard PICmicro<sup>®</sup> device marking consists of Microchip part number, year code, week code and traceability code. For PICmicro device marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

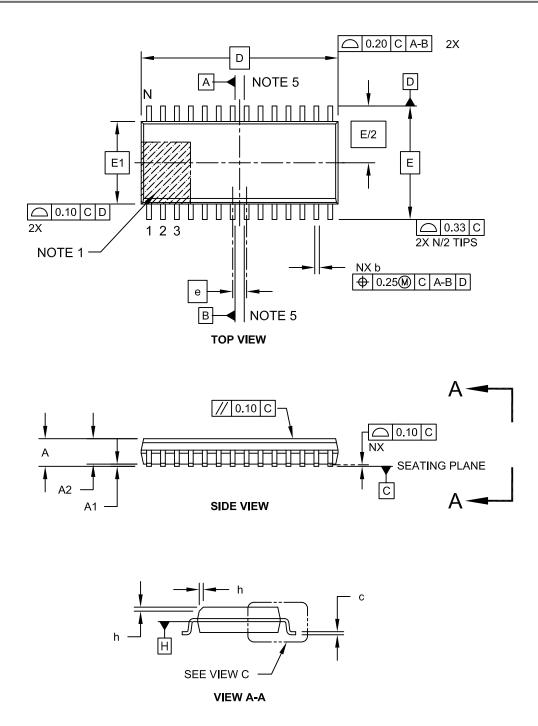

## 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-052C Sheet 1 of 2