Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Data IIa                   |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Details                    |                                                                           |

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 11x8b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 28-SPDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f722a-i-sp |

FIGURE 1-1: PIC16(L)F722A/723A BLOCK DIAGRAM Configuration RA0 13 Data Bus RA1 Program Counter RA2 Flash RA3 Program RA4 Memory 8 Level Stack RA5 RAM RA6 (13-bit) RA7 Program PORTR RAM Addr Bus RB0 RB1 Addr MUX Instruction Reg RB2 RB3 Indirect Direct Addr Addr RB4 RB5 FSR Reg RB6 RB7 STATUS Reg PORTC RC1 RC2 MUX Power-up RC3 RC4 RC5 Oscillator Start-up Timer Instruction RC6 Decode and Control ALU RC7 Power-on Reset OSC1/CLKIN **PORTE** 8 RE3  $\boxtimes$ Timing Generation Watchdog W Reg OSC2/CLKOUT Timer Brown-out Reset LDO<sup>(1)</sup> Internal Regulator Oscillator Block CCP1 CCP1  $\boxtimes$  $\times$  $\boxtimes$  $\times$ MCLR VDD Vss CCP2 CCP2  $\boxtimes$ T10SI 🔀 Timer1 32 kHz T10S0 Oscillator SDI/ SCK/ TX/CK RX/DT SS SDO SDA SCL TOCKI T1G T1CKI X  $\times$  $\times$  $\times$  $\times$  $\bowtie$ Synchronous Timer0 Timer1 Timer2 **AUSART** VREF Serial Port  $\times$ Analog-To-Digital Converter Capacitive Sensing Module X X  $\times$ ANO AN1 AN2 AN3 AN4 AN8 AN9 AN10 AN11 AN12 AN13 CPS0 CPS1 CPS2 CPS3 CPS4 CPS5 CPS6 CPS7 PIC16F722A/723A only. Note 1:

PIC16(L)F723A SPECIAL FUNCTION REGISTERS FIGURE 2-4:

|                   | 7001 | 1 l'                 | امما | 1 - 1 1 1 - 1 (*)    | 1000   | 1                 | File Address |

|-------------------|------|----------------------|------|----------------------|--------|-------------------|--------------|

| Indirect addr.(*) | 00h  | Indirect addr.(*)    | 80h  | Indirect addr.(*)    | 100h   | Indirect addr.(*) | 180h         |

| TMR0              | 01h  | OPTION               | 81h  | TMR0                 | 101h   | OPTION            | 181h         |

| PCL               | 02h  | PCL                  | 82h  | PCL                  | 102h   | PCL               | 182h         |

| STATUS            | 03h  | STATUS               | 83h  | STATUS               | 103h   | STATUS            | 183h         |

| FSR               | 04h  | FSR                  | 84h  | FSR                  | 104h   | FSR               | 184h         |

| PORTA             | 05h  | TRISA                | 85h  |                      | 105h   | ANSELA            | 185h         |

| PORTB             | 06h  | TRISB                | 86h  |                      | 106h   | ANSELB            | 186h         |

| PORTC             | 07h  | TRISC                | 87h  |                      | 107h   |                   | 187h         |

|                   | 08h  |                      | 88h  | CPSCON0              | 108h   |                   | 188h         |

| PORTE             | 09h  | TRISE                | 89h  | CPSCON1              | 109h   |                   | 189h         |

| PCLATH            | 0Ah  | PCLATH               | 8Ah  | PCLATH               | 10Ah   | PCLATH            | 18Ah         |

| INTCON            | 0Bh  | INTCON               | 8Bh  | INTCON               | 10Bh   | INTCON            | 18Bh         |

| PIR1              | 0Ch  | PIE1                 | 8Ch  | PMDATL               | 10Ch   | PMCON1            | 18Ch         |

| PIR2              | 0Dh  | PIE2                 | 8Dh  | PMADRL               | 10Dh   | Reserved          | 18Dh         |

| TMR1L             | 0Eh  | PCON                 | 8Eh  | PMDATH               | 10Eh   | Reserved          | 18Eh         |

| TMR1H             | 0Fh  | T1GCON               | 8Fh  | PMADRH               | 10Fh   | Reserved          | 18Fh         |

| T1CON             | 10h  | OSCCON               | 90h  |                      | 110h   |                   | 190h         |

| TMR2              | 11h  | OSCTUNE              | 91h  |                      | 111h   |                   | 191h         |

| T2CON             | 12h  | PR2                  | 92h  |                      | 112h   |                   | 192h         |

| SSPBUF            | 13h  | SSPADD/SSPMSK        | 93h  |                      | 113h   |                   | 193h         |

| SSPCON            | 14h  | SSPSTAT              | 94h  |                      | 114h   |                   | 194h         |

| CCPR1L            | 15h  | WPUB                 | 95h  |                      | 115h   |                   | 195h         |

| CCPR1H            | 16h  | IOCB                 | 96h  |                      | 116h   |                   | 196h         |

| CCP1CON           | 17h  |                      | 97h  |                      | 117h   |                   | 197h         |

| RCSTA             | 18h  | TXSTA                | 98h  |                      | 118h   |                   | 198h         |

| TXREG             | 19h  | SPBRG                | 99h  |                      | 119h   |                   | 199h         |

| RCREG             | 1Ah  |                      | 9Ah  |                      | 11Ah   |                   | 19Ah         |

| CCPR2L            | 1Bh  |                      | 9Bh  |                      | 11Bh   |                   | 19Bh         |

| CCPR2H            | 1Ch  | APFCON               | 9Ch  |                      | 11Ch   |                   | 19Ch         |

| CCP2CON           | 1Dh  | FVRCON               | 9Dh  |                      | 11Dh   |                   | 19Dh         |

| ADRES             | 1Eh  |                      | 9Eh  |                      | 11Eh   |                   | 19Eh         |

| ADCON0            | 1Fh  | ADCON1               | 9Fh  |                      | 11Fh   |                   | 19Fh         |

|                   | 20h  |                      | A0h  | General Purpose      | 120h   |                   | 1A0h         |

|                   |      | General              |      | Register<br>16 Bytes | 12Fh   |                   |              |

| General           |      | Purpose              |      | . o Zytos            | 130h   |                   |              |

| Purpose           |      | Register<br>80 Bytes |      |                      |        |                   |              |

| Register          |      | OO Dyles             |      |                      | 105    |                   |              |

| 96 Bytes          |      |                      | EFh  |                      | 16Fh   |                   | 1EFh         |

|                   |      | Accesses             | F0h  | Accesses             | 170h   | Accesses          | 1F0h         |

|                   | 751  | 70h-7Fh              | FFh  | 70h-7Fh              | 17Fh   | 70h-7Fh           | 1FFh         |

|                   | 7Fh  |                      | FELL |                      | 171711 |                   | LIFFII       |

**Legend:** = Unimplemented data memory locations, read as '0'.

\* = Not a physical register.

TABLE 3-1: STATUS BITS AND THEIR SIGNIFICANCE

| POR | BOR | ТО | PD | Condition                                               |  |  |  |

|-----|-----|----|----|---------------------------------------------------------|--|--|--|

| 0   | х   | 1  | 1  | Power-on Reset or LDO Reset                             |  |  |  |

| 0   | х   | 0  | х  | egal, TO is set on POR                                  |  |  |  |

| 0   | х   | х  | 0  | egal, PD is set on POR                                  |  |  |  |

| 1   | 0   | 1  | 1  | Brown-out Reset                                         |  |  |  |

| 1   | 1   | 0  | 1  | WDT Reset                                               |  |  |  |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |  |  |  |

| 1   | 1   | u  | u  | MCLR Reset during normal operation                      |  |  |  |

| 1   | 1   | 1  | 0  | MCLR Reset during Sleep or interrupt wake-up from Sleep |  |  |  |

TABLE 3-2: RESET CONDITION FOR SPECIAL REGISTERS<sup>(2)</sup>

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 0000h                 | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 0000h                 | 000u uuuu          | uu               |

| MCLR Reset during Sleep            | 0000h                 | 0001 0uuu          | uu               |

| WDT Reset                          | 0000h                 | 0000 1uuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 0000h                 | 0001 1uuu          | u0               |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | uuu1 0uuu          | uu               |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and Global Enable bit (GIE) is set, the return address is pushed on the stack and PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

<sup>2:</sup> If a Status bit is not implemented, that bit will be read as '0'.

### 6.3.4 PIN DESCRIPTIONS AND DIAGRAMS

Each PORTB pin is multiplexed with other functions. The pins and their combined functions are briefly described here. For specific information about individual functions such as the SSP, I<sup>2</sup>C or interrupts, refer to the appropriate section in this data sheet.

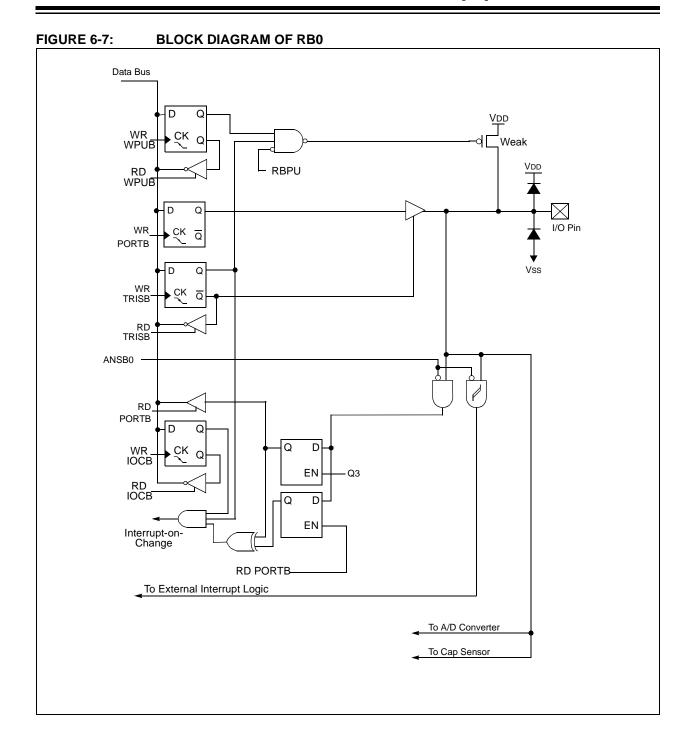

#### 6.3.4.1 RB0/AN12/CPS0/INT

Figure 6-7 shows the diagram for this pin. This pin is configurable to function as one of the following:

- General purpose I/O

- · Analog input for the ADC

- · Capacitive sensing input

- · External edge triggered interrupt

#### 6.3.4.2 RB1/AN10/CPS1

Figure 6-8 shows the diagram for this pin. This pin is configurable to function as one of the following:

- General purpose I/O

- · Analog input for the ADC

- · Capacitive sensing input

#### 6.3.4.3 RB2/AN8/CPS2

Figure 6-8 shows the diagram for this pin. This pin is configurable to function as one of the following:

- General purpose I/O

- · Analog input for the ADC

- · Capacitive sensing input

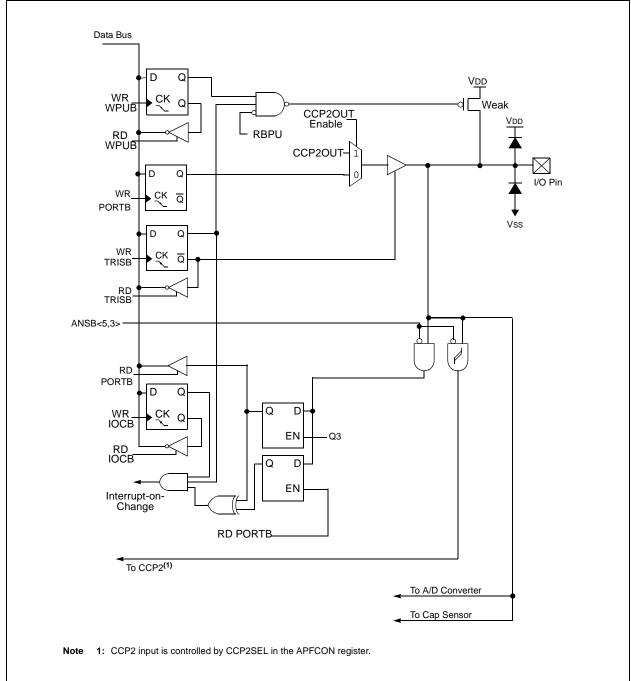

#### 6.3.4.4 RB3/AN9/CPS3/CCP2

Figure 6-9 shows the diagram for this pin. This pin is configurable to function as one of the following:

- General purpose I/O

- · Analog input for the ADC

- Capacitive sensing input

- Capture 2 input, Compare 2 output, and PWM2 output

Note: CCP2 pin location may be selected as RB3 or RC1.

#### 6.3.4.5 RB4/AN11/CPS4

Figure 6-8 shows the diagram for this pin. This pin is configurable to function as one of the following:

- · General purpose I/O

- Analog input for the ADC

- · Capacitive sensing input

#### 6.3.4.6 RB5/AN13/CPS5/T1G

Figure 6-10 shows the diagram for this pin. This pin is configurable to function as one of the following:

- · General purpose I/O

- · Analog input for the ADC

- · Capacitive sensing input

- · Timer1 gate input

#### 6.3.4.7 RB6/ICSPCLK

Figure 6-11 shows the diagram for this pin. This pin is configurable to function as one of the following:

- a general purpose I/O

- · In-Circuit Serial Programming clock

#### 6.3.4.8 RB7/ICSPDAT

Figure 6-12 shows the diagram for this pin. This pin is configurable to function as one of the following:

- · General purpose I/O

- In-Circuit Serial Programming data

FIGURE 6-9: **BLOCK DIAGRAM OF RB3**

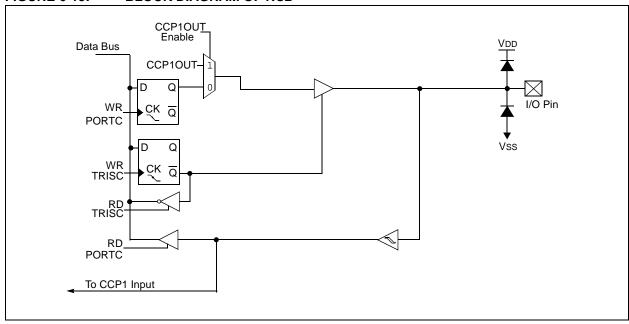

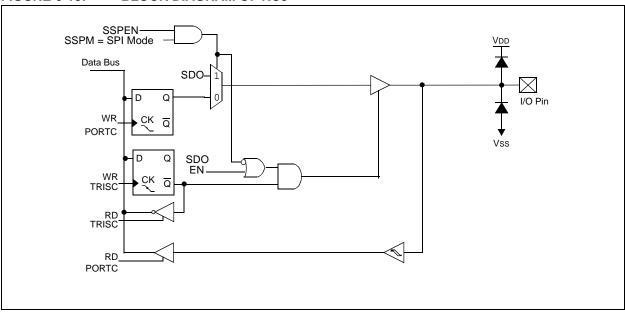

FIGURE 6-15: BLOCK DIAGRAM OF RC2

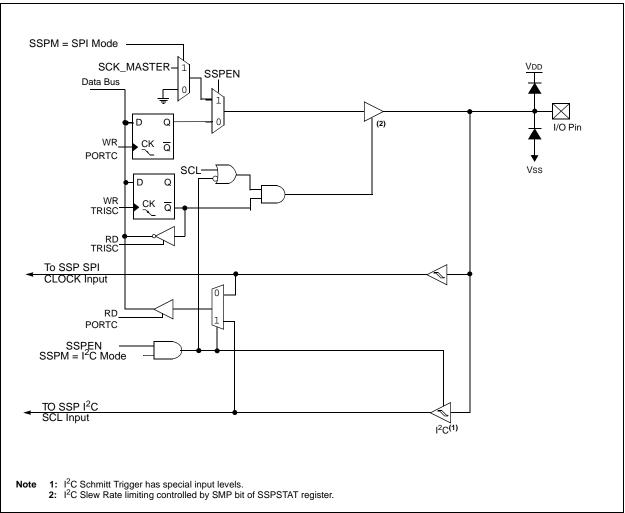

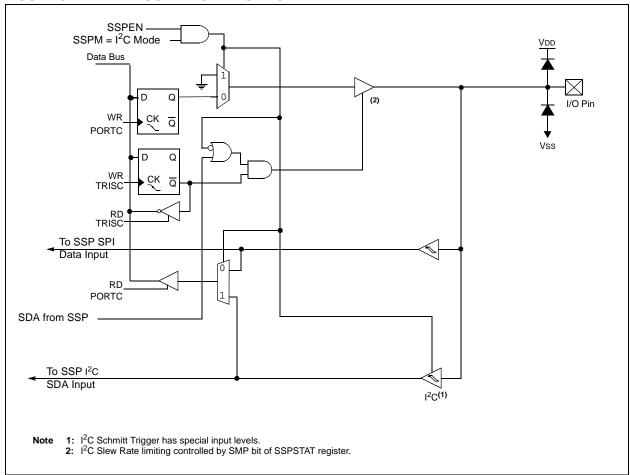

#### FIGURE 6-16: BLOCK DIAGRAM OF RC3

FIGURE 6-17: BLOCK DIAGRAM OF RC4

#### FIGURE 6-18: BLOCK DIAGRAM OF RC5

#### 9.3 A/D Acquisition Requirements

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 9-3. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), refer to Figure 9-3. The maximum recommended impedance for analog sources is  $10~{\rm k}\Omega$ . As the source

impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an A/D acquisition must be done before the conversion can be started. To calculate the minimum acquisition time, Equation 9-1 may be used. This equation assumes that 1/2 LSb error is used (256 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

#### **EQUATION 9-1: ACQUISITION TIME EXAMPLE**

Assumptions: Temperature =  $50^{\circ}$ C and external impedance of  $10k\Omega 5.0V VDD$

$$TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient$$

=  $TAMP + TC + TCOFF$

=  $2\mu s + TC + [(Temperature - 25°C)(0.05\mu s/°C)]$

The value for TC can be approximated with the following equations:

$$V_{APPLIED}\left(1 - \frac{1}{(2^{n+1})-1}\right) = V_{CHOLD}$$

;[1] VCHOLD charged to within 1/2 lsb

$$V_{APPLIED} \left( 1 - e^{\frac{-Tc}{RC}} \right) = V_{CHOLD}$$

;[2] VCHOLD charge response to VAPPLIED

$$V_{APPLIED}\left(1-e^{\frac{-Tc}{RC}}\right) = V_{APPLIED}\left(1-\frac{1}{(2^{n+1})-1}\right)$$

; combining [1] and [2]

*Note:* Where n = number of bits of the ADC.

Solving for TC:

$$TC = -CHOLD(RIC + RSS + RS) \ln(1/511)$$

$$= -10pF(1k\Omega + 7k\Omega + 10k\Omega) \ln(0.001957)$$

$$= 1.12\mu s$$

Therefore:

$$TACQ = 2\mu s + 1.12\mu s + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

= 4.42\mu s

- Note 1: The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- 3: The maximum recommended impedance for analog sources is 10 kΩ. This is required to meet the pin leakage specification.

TABLE 9-2: SUMMARY OF ASSOCIATED ADC REGISTERS

| Name    | Bit 7   | Bit 6  | Bit 5  | Bit 4     | Bit 3       | Bit 2  | Bit 1       | Bit 0  | Register on Page |

|---------|---------|--------|--------|-----------|-------------|--------|-------------|--------|------------------|

| ADCON0  | _       | _      | CHS3   | CHS2      | CHS1        | CHS0   | GO/<br>DONE | ADON   | 85               |

| ADCON1  | _       | ADCS2  | ADCS1  | ADCS0     | _           | _      | ADREF1      | ADREF0 | 86               |

| ANSELA  | _       | _      | ANSA5  | ANSA4     | ANSA3       | ANSA2  | ANSA1       | ANSA0  | 44               |

| ANSELB  | _       | _      | ANSB5  | ANSB4     | ANSB3       | ANSB2  | ANSB1       | ANSB0  | 53               |

| ADRES   |         |        | Α/[    | Result Re | gister Byte |        |             |        | 86               |

| CCP2CON | _       | _      | DC2B1  | DC2B0     | CCP2M3      | CCP2M2 | CCP2M1      | CCP2M0 | 115              |

| FVRCON  | FVRRDY  | FVREN  | _      | _         | _           | _      | ADFVR1      | ADFVR0 | 90               |

| INTCON  | GIE     | PEIE   | TOIE   | INTE      | RBIE        | TOIF   | INTF        | RBIF   | 36               |

| PIE1    | TMR1GIE | ADIE   | RCIE   | TXIE      | SSPIE       | CCP1IE | TMR2IE      | TMR1IE | 37               |

| PIR1    | TMR1GIF | ADIF   | RCIF   | TXIF      | SSPIF       | CCP1IF | TMR2IF      | TMR1IF | 39               |

| TRISA   | TRISA7  | TRISA6 | TRISA5 | TRISA4    | TRISA3      | TRISA2 | TRISA1      | TRISA0 | 43               |

| TRISB   | TRISB7  | TRISB6 | TRISB5 | TRISB4    | TRISB3      | TRISB2 | TRISB1      | TRISB0 | 52               |

**Legend:** x = unknown, u = unchanged, - = unimplemented read as '0', <math>q = value depends on condition. Shaded cells are not used for ADC module.

TABLE 12-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER1

| Name    | Bit 7       | Bit 6         | Bit 5        | Bit 4        | Bit 3          | Bit 2                 | Bit 1  | Bit 0  | Register on Page |

|---------|-------------|---------------|--------------|--------------|----------------|-----------------------|--------|--------|------------------|

| ANSELB  | _           | _             | ANSB5        | ANSB4        | ANSB3          | ANSB2                 | ANSB1  | ANSB0  | 53               |

| CCP1CON | _           | _             | DC1B1        | DC1B0        | CCP1M3         | CCP1M2                | CCP1M1 | CCP1M0 | 115              |

| CCP2CON | _           | _             | DC2B1        | DC2B0        | CCP2M3         | CCP2M2                | CCP2M1 | CCP2M0 | 115              |

| INTCON  | GIE         | PEIE          | T0IE         | INTE         | RBIE           | T0IF                  | INTF   | RBIF   | 36               |

| PIE1    | TMR1GIE     | ADIE          | RCIE         | TXIE         | SSPIE          | CCP1IE                | TMR2IE | TMR1IE | 37               |

| PIR1    | TMR1GIF     | ADIF          | RCIF         | TXIF         | SSPIF          | CCP1IF                | TMR2IF | TMR1IF | 39               |

| PORTB   | RB7         | RB6           | RB5          | RB4          | RB3            | RB2                   | RB1    | RB0    | 52               |

| TMR1H   | Holding Reg | ister for the | Most Signifi | cant Byte of | the 16-bit T   | MR1 Regis             | ter    |        | 99               |

| TMR1L   | Holding Reg | ister for the | Least Signif | icant Byte o | f the 16-bit T | MR1 Regis             | ster   |        | 99               |

| TRISB   | TRISB7      | TRISB6        | TRISB5       | TRISB4       | TRISB3         | TRISB2                | TRISB1 | TRISB0 | 52               |

| TRISC   | TRISC7      | TRISC6        | TRISC5       | TRISC4       | TRISC3         | TRISC2                | TRISC1 | TRISC0 | 62               |

| T1CON   | TMR1CS1     | TMR1CS0       | T1CKPS1      | T1CKPS0      | T10SCEN        | 10SCEN TISYNC — TMR10 |        | TMR10N | 103              |

| T1GCON  | TMR1GE      | T1GPOL        | T1GTM        | T1GSPM       | T1GGO/<br>DONE | T1GVAL                | T1GSS1 | T1GSS0 | 104              |

**Legend:** x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

# 16.0 ADDRESSABLE UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (AUSART)

The Addressable Universal Synchronous Asynchronous Receiver Transmitter (AUSART) module is a serial I/O communications peripheral. It contains all the clock generators, shift registers and data buffers necessary to perform an input or output serial data transfer independent of device program execution. The AUSART, also known as a Serial Communications Interface (SCI), can be configured as a full-duplex asynchronous system or half-duplex synchronous system. Full-Duplex mode is useful for communications with peripheral systems, such as CRT terminals and personal computers. Half-Duplex Synchronous mode is intended for communications with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs or other microcontrollers. These devices typically do not have internal clocks for baud rate generation and require the external clock signal provided by a master synchronous device.

The AUSART module includes the following capabilities:

- · Full-duplex asynchronous transmit and receive

- · Two-character input buffer

- · One-character output buffer

- Programmable 8-bit or 9-bit character length

- · Address detection in 9-bit mode

- Input buffer overrun error detection

- · Received character framing error detection

- · Half-duplex synchronous master

- · Half-duplex synchronous slave

- · Sleep operation

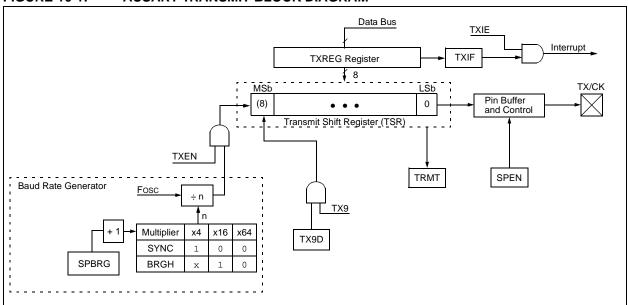

Block diagrams of the AUSART transmitter and receiver are shown in Figure 16-1 and Figure 16-2.

FIGURE 16-1: AUSART TRANSMIT BLOCK DIAGRAM

TABLE 16-2: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

| Name   | Bit 7    | Bit 6       | Bit 5      | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|----------|-------------|------------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE      | PEIE        | TOIE       | INTE   | RBIE   | T0IF   | INTF   | RBIF   | 0000 000x            | 0000 000x                       |

| PIE1   | TMR1GIE  | ADIE        | RCIE       | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| PIR1   | TMR1GIF  | ADIF        | RCIF       | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| RCREG  | AUSART R | eceive Data | a Register |        |        |        |        |        | 0000 0000            | 0000 0000                       |

| RCSTA  | SPEN     | RX9         | SREN       | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 0000 000x            | 0000 000x                       |

| SPBRG  | BRG7     | BRG6        | BRG5       | BRG4   | BRG3   | BRG2   | BRG1   | BRG0   | 0000 0000            | 0000 0000                       |

| TRISC  | TRISC7   | TRISC6      | TRISC5     | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 1111 1111            | 1111 1111                       |

| TXSTA  | CSRC     | TX9         | TXEN       | SYNC   | _      | BRGH   | TRMT   | TX9D   | 0000 -010            | 0000 -010                       |

**Legend:** x = unknown, - = unimplemented read as '0'. Shaded cells are not used for asynchronous reception.

#### REGISTER 17-2: SSPSTAT: SYNC SERIAL PORT STATUS REGISTER (SPI MODE)

| R/W-0       | R/W-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0 |  |

|-------------|-------|-----|-----|-----|-----|-----|-----|--|

| SMP         | CKE   | D/Ā | Р   | S   | R/W | UA  | BF  |  |

| bit 7 bit 0 |       |     |     |     |     |     |     |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 SMP: SPI Data Input Sample Phase bit

SPI Master mode:

1 = Input data sampled at end of data output time0 = Input data sampled at middle of data output time

SPI Slave mode:

SMP must be cleared when SPI is used in Slave mode

bit 6 CKE: SPI Clock Edge Select bit

SPI mode, CKP = 0:

1 = Data stable on rising edge of SCK0 = Data stable on falling edge of SCK

SPI mode, CKP = 1:

1 = Data stable on falling edge of SCK0 = Data stable on rising edge of SCK

bit 5 D/A: Data/Address bit

Used in I<sup>2</sup>C mode only.

bit 4 P: Stop bit

Used in I<sup>2</sup>C mode only.

bit 3 S: Start bit

Used in I<sup>2</sup>C mode only.

bit 2 R/W: Read/Write Information bit

Used in I<sup>2</sup>C mode only.

bit 1 UA: Update Address bit

Used in I<sup>2</sup>C mode only.

bit 0 **BF**: Buffer Full Status bit

1 = Receive complete, SSPBUF is full

0 = Receive not complete, SSPBUF is empty

#### 22.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- · Flexible macro language

- MPLAB X IDE compatibility

#### 22.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel® standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

#### 22.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 22.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire device instruction set

- Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- · Flexible macro language

- MPLAB X IDE compatibility

#### 23.1 DC Characteristics: PIC16(L)F722A/723A-I/E (Industrial, Extended)

| PIC16LI       | F722A/723         | BA                                                     | Standard Operating Conditions (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for extended |                  |                          |             |                                                                                                                              |  |  |

|---------------|-------------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------|--|--|

| PIC16F7       | 722A/723 <i>F</i> | 4                                                      | Standard Operating Conditions (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for extended |                  |                          |             |                                                                                                                              |  |  |

| Param.<br>No. | Sym.              | Characteristic                                         | Min.                                                                                                                                                                                                                               | Тур†             | Max.                     | Units       | Conditions                                                                                                                   |  |  |

| D001          | VDD               | Supply Voltage                                         |                                                                                                                                                                                                                                    |                  |                          |             |                                                                                                                              |  |  |

|               |                   | PIC16LF722A/723A                                       | 1.8<br>1.8<br>2.3<br>2.5                                                                                                                                                                                                           | _<br>_<br>_      | 3.6<br>3.6<br>3.6<br>3.6 | V<br>V<br>V | Fosc ≤ 16 MHz: HFINTOSC, EC<br>Fosc ≤ 4 MHz<br>Fosc ≤ 20 MHz, EC<br>Fosc ≤ 20 MHz, HS                                        |  |  |

| D001          |                   | PIC16F722A/723A                                        | 1.8<br>1.8<br>2.3<br>2.5                                                                                                                                                                                                           | _<br>_<br>_<br>_ | 5.5<br>5.5<br>5.5<br>5.5 | V<br>V<br>V | Fosc $\leq$ 16 MHz: HFINTOSC, EC<br>Fosc $\leq$ 4 MHz<br>Fosc $\leq$ 20 MHz, EC<br>Fosc $\leq$ 20 MHz, HS                    |  |  |

| D002*         | VDR               | RAM Data Retention Voltage <sup>(1)</sup>              |                                                                                                                                                                                                                                    |                  |                          |             | ,                                                                                                                            |  |  |

|               |                   | PIC16LF722A/723A                                       | 1.5                                                                                                                                                                                                                                | _                | _                        | V           | Device in Sleep mode                                                                                                         |  |  |

| D002*         |                   | PIC16F722A/723A                                        | 1.7                                                                                                                                                                                                                                | _                | _                        | V           | Device in Sleep mode                                                                                                         |  |  |

|               | VPOR*             | Power-on Reset Release Voltage                         | _                                                                                                                                                                                                                                  | 1.6              | _                        | V           |                                                                                                                              |  |  |

|               | VPORR*            | Power-on Reset Rearm Voltage                           |                                                                                                                                                                                                                                    |                  |                          |             |                                                                                                                              |  |  |

|               |                   | PIC16LF722A/723A                                       | _                                                                                                                                                                                                                                  | 0.8              | _                        | V           | Device in Sleep mode                                                                                                         |  |  |

|               |                   | PIC16F722A/723A                                        | _                                                                                                                                                                                                                                  | 1.7              | _                        | V           | Device in Sleep mode                                                                                                         |  |  |

| D003          | VFVR              | Fixed Voltage Reference Voltage,<br>Initial Accuracy   | -5.5<br>-5.5<br>-5.5                                                                                                                                                                                                               |                  | 5.5<br>5.5<br>5.5        | %<br>%<br>% | $VFVR = 1.024V, VDD \ge 2.5V \\ VFVR = 2.048V, VDD \ge 2.5V \\ VFVR = 4.096V, VDD \ge 4.75V; \\ -40 \le TA \le 85^{\circ}C$  |  |  |

|               |                   |                                                        | -6<br>-6<br>-6                                                                                                                                                                                                                     | _<br>_<br>_      | 6<br>6<br>6              | %<br>%<br>% | $VFVR = 1.024V, VDD \ge 2.5V \\ VFVR = 2.048V, VDD \ge 2.5V \\ VFVR = 4.096V, VDD \ge 4.75V; \\ -40 \le TA \le 125^{\circ}C$ |  |  |

| D004*         | SVDD              | VDD Rise Rate to ensure internal Power-on Reset signal | 0.05                                                                                                                                                                                                                               | _                | _                        | V/ms        | See Section 3.2 "Power-on Reset (POR)" for details.                                                                          |  |  |

<sup>\*</sup> These parameters are characterized but not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

<sup>†</sup> Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### 23.5 Thermal Considerations

Standard Operating Conditions (unless otherwise stated)

Operating temperature  $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$

| Param<br>No. | Sym.      | Characteristic                         | Тур. | Units | Conditions                                               |

|--------------|-----------|----------------------------------------|------|-------|----------------------------------------------------------|

| TH01         | θЈА       | Thermal Resistance Junction to Ambient | 60.0 | °C/W  | 28-pin SPDIP package                                     |

|              |           |                                        | 69.7 | °C/W  | 28-pin SOIC package                                      |

|              |           |                                        | 71.0 | °C/W  | 28-pin SSOP package                                      |

|              |           |                                        | 52.5 | °C/W  | 28-pin UQFN 4x4mm package                                |

|              |           |                                        | 30.0 | °C/W  | 28-pin QFN 6x6mm package                                 |

| TH02         | θЈС       | Thermal Resistance Junction to Case    | 29.0 | °C/W  | 28-pin SPDIP package                                     |

|              |           |                                        | 18.9 | °C/W  | 28-pin SOIC package                                      |

|              |           |                                        | 24.0 | °C/W  | 28-pin SSOP package                                      |

|              |           |                                        | 16.7 | °C/W  | 28-pin UQFN 4x4mm package                                |

|              |           |                                        | 5.0  | °C/W  | 28-pin QFN 6x6mm package                                 |

| TH03         | ТЈМАХ     | Maximum Junction Temperature           | 150  | °C    |                                                          |

| TH04         | PD        | Power Dissipation                      | _    | W     | PD = PINTERNAL + PI/O                                    |

| TH05         | PINTERNAL | Internal Power Dissipation             | _    | W     | PINTERNAL = IDD x VDD <sup>(1)</sup>                     |

| TH06         | Pı/o      | I/O Power Dissipation                  | _    | W     | $PI/O = \Sigma (IOL * VOL) + \Sigma (IOH * (VDD - VOH))$ |

| TH07         | PDER      | Derated Power                          | _    | W     | PDER = PDMAX (TJ - TA)/θJA <sup>(2)</sup>                |

**Note 1:** IDD is current to run the chip alone without driving any load on the output pins.

<sup>2:</sup> TA = Ambient Temperature

**<sup>3:</sup>** T<sub>J</sub> = Junction Temperature

TABLE 23-3: CLKOUT AND I/O TIMING PARAMETERS

|              | Standard Operating Conditions (unless otherwise stated) Operating Temperature $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ |                                                           |               |      |      |       |                |  |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|---------------|------|------|-------|----------------|--|--|--|

| Param<br>No. | Sym.                                                                                                                                       | Characteristic                                            | Min.          | Тур† | Max. | Units | Conditions     |  |  |  |

| OS11         | TosH2ckL                                                                                                                                   | Fosc↑ to CLKOUT↓ (1)                                      | _             |      | 70   | ns    | VDD = 3.3-5.0V |  |  |  |

| OS12         | TosH2ckH                                                                                                                                   | Fosc↑ to CLKOUT↑ (1)                                      | _             | 1    | 72   | ns    | VDD = 3.3-5.0V |  |  |  |

| OS13         | TckL2ioV                                                                                                                                   | CLKOUT↓ to Port out valid <sup>(1)</sup>                  | _             | 1    | 20   | ns    |                |  |  |  |

| OS14         | TioV2ckH                                                                                                                                   | Port input valid before CLKOUT <sup>(1)</sup>             | Tosc + 200 ns | _    | _    | ns    |                |  |  |  |

| OS15         | TosH2ioV                                                                                                                                   | Fosc↑ (Q1 cycle) to Port out valid                        | _             | 50   | 70*  | ns    | VDD = 3.3-5.0V |  |  |  |

| OS16         | TosH2ioI                                                                                                                                   | Fosc↑ (Q2 cycle) to Port input invalid (I/O in hold time) | 50            | _    | _    | ns    | VDD = 3.3-5.0V |  |  |  |

| OS17         | TioV2osH                                                                                                                                   | Port input valid to Fosc↑ (Q2 cycle) (I/O in setup time)  | 20            | _    | _    | ns    |                |  |  |  |

| OS18         | TioR                                                                                                                                       | Port output rise time <sup>(2)</sup>                      | _             | 40   | 72   | ns    | VDD = 2.0V     |  |  |  |

|              |                                                                                                                                            |                                                           | _             | 15   | 32   |       | VDD = 3.3-5.0V |  |  |  |

| OS19         | TioF                                                                                                                                       | Port output fall time <sup>(2)</sup>                      | _             | 28   | 55   | ns    | VDD = 2.0V     |  |  |  |

|              |                                                                                                                                            |                                                           | _             | 15   | 30   |       | VDD = 3.3-5.0V |  |  |  |

| OS20*        | Tinp                                                                                                                                       | INT pin input high or low time                            | 25            | _    | _    | ns    |                |  |  |  |

| OS21*        | Trbp                                                                                                                                       | PORTB interrupt-on-change new input level time            | Tcy           | _    | _    | ns    |                |  |  |  |

<sup>\*</sup> These parameters are characterized but not tested.

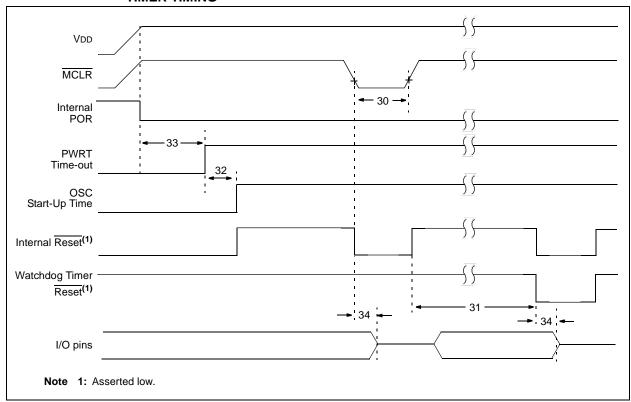

FIGURE 23-8: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

<sup>†</sup> Data in "Typ" column is at 3.0V, 25°C unless otherwise stated.

Note 1: Measurements are taken in RC mode where CLKOUT output is 4 x Tosc.

<sup>2:</sup> Includes OSC2 in CLKOUT mode.

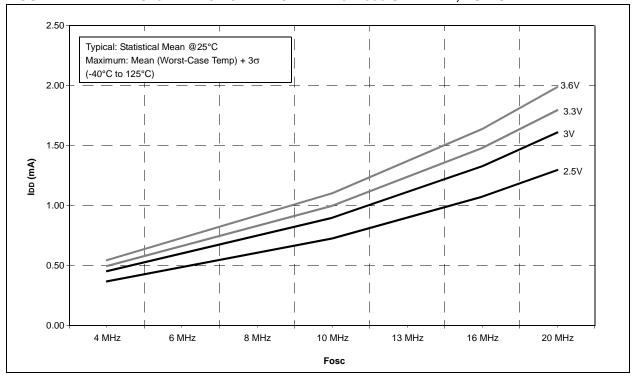

FIGURE 24-12: PIC16LF722A/723A TYPICAL IDD vs. Fosc OVER VDD, HS MODE

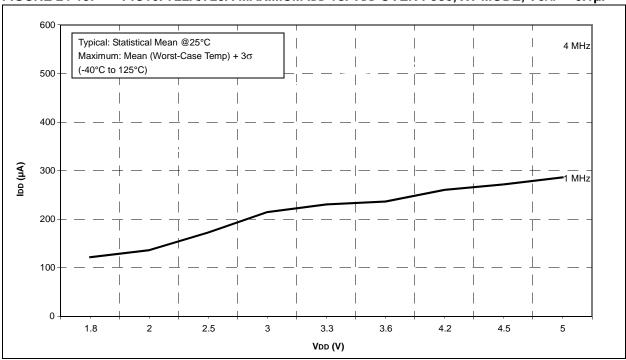

FIGURE 24-13: PIC16F722A/723A MAXIMUM IDD vs. VDD OVER FOSC, XT MODE, VCAP = 0.1µF

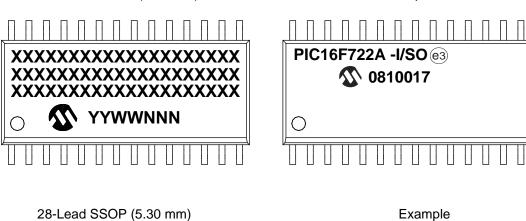

#### 25.1 Package Marking Information (Continued)

28-Lead SOIC (7.50 mm)

Example

PIC16F722A -I/SS @3) **1** 0810017

Legend: XX...X Customer-specific information

Υ Year code (last digit of calendar year) ΥY Year code (last 2 digits of calendar year) WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

(e3) Pb-free JEDEC designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC® designator (@3)

can be found on the outer packaging for this package.

Note: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

Standard PICmicro® device marking consists of Microchip part number, year code, week code and traceability code. For PICmicro device marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.