Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2010                       |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 11x8b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

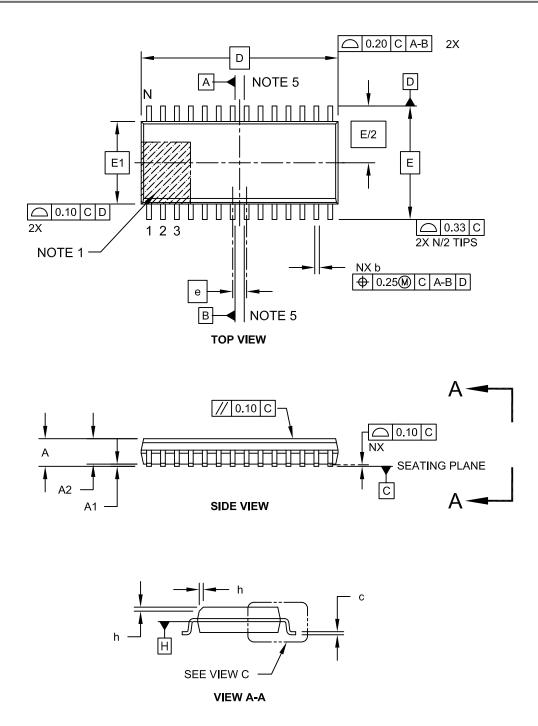

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 28-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f722a-i-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

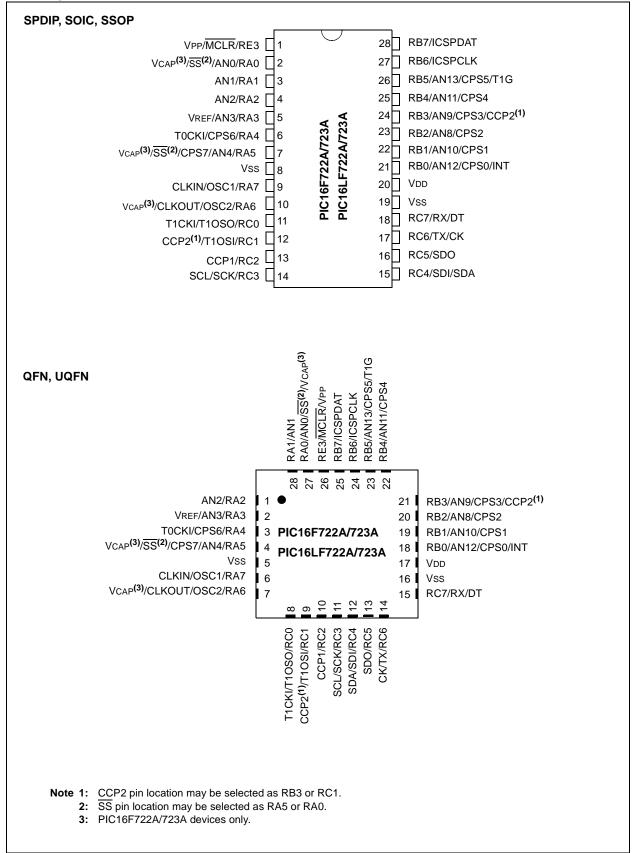

#### Pin Diagrams - 28-PIN SPDIP/SOIC/SSOP/QFN/UQFN (PIC16(L)F722A/723A)

### 1.0 DEVICE OVERVIEW

The PIC16(L)F722A/723A devices are covered by this data sheet. They are available in 28-pin packages. Figure 1-1 shows a block diagram of the PIC16(L)F722A/723A devices. Table 1-1 shows the pinout descriptions.

| Address               | Name    | Bit 7        | Bit 6                                | Bit 5         | Bit 4          | Bit 3         | Bit 2         | Bit 1          | Bit 0     | Value on:<br>POR, BOR | Page   |

|-----------------------|---------|--------------|--------------------------------------|---------------|----------------|---------------|---------------|----------------|-----------|-----------------------|--------|

| Bank 0                |         |              |                                      |               |                |               |               |                |           |                       |        |

| 00h <sup>(2)</sup>    | INDF    | Addressing   | this location                        | uses conter   | nts of FSR to  | address data  | memory (no    | t a physical r | egister)  | xxxx xxxx             | 22,30  |

| 01h                   | TMR0    | Timer0 Mod   | dule Register                        |               |                |               |               |                |           | xxxx xxxx             | 91,30  |

| 02h <sup>(2)</sup>    | PCL     | Program Co   | ounter (PC) L                        | east Signific | cant Byte      |               |               |                |           | 0000 0000             | 21,30  |

| 03h <sup>(2)</sup>    | STATUS  | IRP          | RP1                                  | RP0           | TO             | PD            | Z             | DC             | С         | 0001 1xxx             | 18,30  |

| 04h <sup>(2)</sup>    | FSR     | Indirect Dat | a Memory A                           | ddress Point  | er             |               |               |                |           | XXXX XXXX             | 22,30  |

| 05h                   | PORTA   | RA7          | RA6                                  | RA5           | RA4            | RA3           | RA2           | RA1            | RA0       | xxxx xxxx             | 43,30  |

| 06h                   | PORTB   | RB7          | RB6                                  | RB5           | RB4            | RB3           | RB2           | RB1            | RB0       | xxxx xxxx             | 52,30  |

| 07h                   | PORTC   | RC7          | RC6                                  | RC5           | RC4            | RC3           | RC2           | RC1            | RC0       | xxxx xxxx             | 62,30  |

| 09h                   | PORTE   | _            | —                                    | _             | —              | RE3           | _             | _              | —         | xxxx                  | 69,30  |

| 0Ah <sup>(1, 2)</sup> | PCLATH  | _            | _                                    | _             | Write Buffer   | for the upper | 5 bits of the | Program Co     | unter     | 0 0000                | 21,30  |

| 0Bh <sup>(2)</sup>    | INTCON  | GIE          | PEIE                                 | TOIE          | INTE           | RBIE          | T0IF          | INTF           | RBIF      | 0000 000x             | 36,30  |

| 0Ch                   | PIR1    | TMR1GIF      | ADIF                                 | RCIF          | TXIF           | SSPIF         | CCP1IF        | TMR2IF         | TMR1IF    | 0000 0000             | 39,30  |

| 0Dh                   | PIR2    | _            | _                                    |               | _              | _             | _             | _              | CCP2IF    | 0                     | 40,30  |

| 0Eh                   | TMR1L   | Holding Reg  | gister for the                       | Least Signif  | icant Byte of  | the 16-bit TN | IR1 Register  |                |           | xxxx xxxx             | 99,30  |

| 0Fh                   | TMR1H   | Holding Re   | gister for the                       | Most Signifi  | cant Byte of t | he 16-bit TM  | R1 Register   |                |           | xxxx xxxx             | 99,30  |

| 10h                   | T1CON   | TMR1CS1      | TMR1CS0                              | T1CKPS1       | T1CKPS0        | T1OSCEN       | T1SYNC        | _              | TMR10N    | 0000 00-0             | 103,30 |

| 11h                   | TMR2    | Timer2 Mod   | ule Register                         |               |                |               |               |                |           | 0000 0000             | 106,30 |

| 12h                   | T2CON   | —            | TOUTPS3                              | TOUTPS2       | TOUTPS1        | TOUTPS0       | TMR2ON        | T2CKPS1        | T2CKPS0   | -000 0000             | 107,30 |

| 13h                   | SSPBUF  | Synchronou   | us Serial Port                       | t Receive Bu  | Iffer/Transmit | Register      |               |                |           | xxxx xxxx             | 147,30 |

| 14h                   | SSPCON  | WCOL         | SSPOV                                | SSPEN         | CKP            | SSPM3         | SSPM2         | SSPM1          | SSPM0     | 0000 0000             | 164,30 |

| 15h                   | CCPR1L  | Capture/Co   | mpare/PWM                            | Register (L   | SB)            |               |               |                |           | xxxx xxxx             | 116,30 |

| 16h                   | CCPR1H  | Capture/Co   | mpare/PWM                            | Register (N   | SB)            |               |               |                |           | xxxx xxxx             | 116,30 |

| 17h                   | CCP1CON | _            | _                                    | DC1B1         | DC1B0          | CCP1M3        | CCP1M2        | CCP1M1         | CCP1M0    | 00 0000               | 115,30 |

| 18h                   | RCSTA   | SPEN         | RX9                                  | SREN          | CREN           | ADDEN         | FERR          | OERR           | RX9D      | 0000 000x             | 134,30 |

| 19h                   | TXREG   | USART Tra    | nsmit Data F                         | Register      |                |               |               | •              | •         | 0000 0000             | 133,30 |

| 1Ah                   | RCREG   | USART Red    | ceive Data R                         | egister       |                |               |               |                |           | 0000 0000             | 131,30 |

| 1Bh                   | CCPR2L  | Capture/Co   | Capture/Compare/PWM Register 2 (LSB) |               |                |               |               |                | xxxx xxxx | 116,30                |        |

| 1Ch                   | CCPR2H  | Capture/Co   | mpare/PWM                            | Register 2    | (MSB)          |               |               |                |           | xxxx xxxx             | 116,30 |

| 1Dh                   | CCP2CON | —            | —                                    | DC2B1         | DC2B0          | CCP2M3        | CCP2M2        | CCP2M1         | CCP2M0    | 00 0000               | 115,30 |

| 1Eh                   | ADRES   | A/D Result   | Register                             |               |                |               |               |                | •         | xxxx xxxx             | 86,30  |

| 1Fh                   | ADCON0  | —            | —                                    | CHS3          | CHS2           | CHS1          | CHS0          | GO/DONE        | ADON      | 00 0000               | 85,30  |

| TABLE 2-1: | PIC16(L)F722A/723A SPECIAL FUNCTION REGISTER SUMMARY | ( |

|------------|------------------------------------------------------|---|

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter.

2: These registers can be addressed from any bank.

**3:** Accessible only when SSPM<3:0> = 1001.

4: Accessible only when SSPM<3:0>  $\neq$  1001.

**5:** This bit is always '1' as RE3 is input-only.

### 5.0 LOW DROPOUT (LDO) VOLTAGE REGULATOR

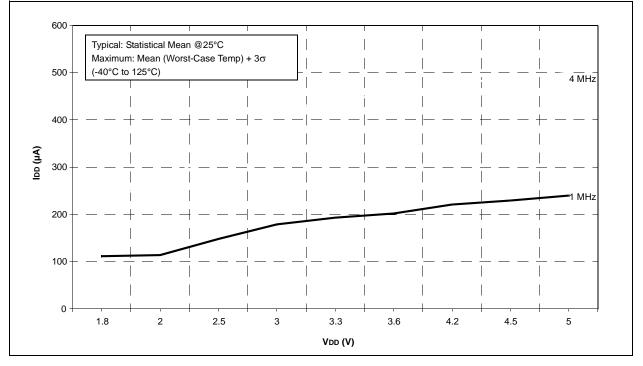

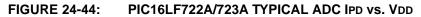

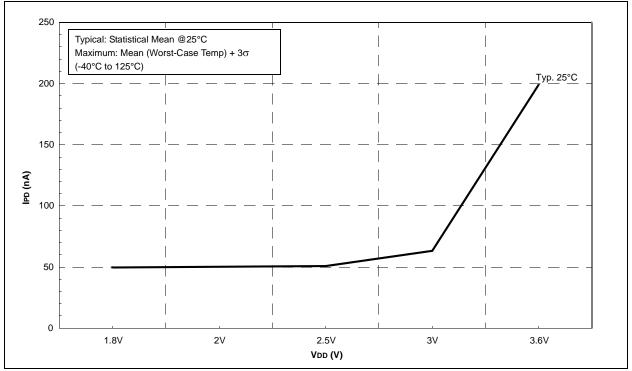

The PIC16F722A/723A devices differ from the PIC16LF722A/723A devices due to an internal Low Dropout (LDO) voltage regulator. The PIC16F722A/723A devices contain an internal LDO, while the PIC16LF722A/723A ones do not.

The lithography of the die allows a maximum operating voltage of 3.6V on the internal digital logic. In order to continue to support 5.0V designs, a LDO voltage regulator is integrated on the die. The LDO voltage regulator allows for the internal digital logic to operate at 3.2V, while I/O's operate at 5.0V (VDD).

The LDO voltage regulator requires an external bypass capacitor for stability. One of three pins, denoted as VCAP, can be configured for the external bypass capacitor. It is recommended that the capacitor be a ceramic cap between 0.1 to  $1.0 \,\mu$ F. The VCAP pin is not intended to supply power to external loads. An external voltage regulator should be used if this functionality is required. In addition, external devices should not supply power to the VCAP pin.

On power-up, the external capacitor will look like a large load on the LDO voltage regulator. To prevent erroneous operation, the device is held in Reset while a constant current source charges the external capacitor. After the cap is fully charged, the device is released from Reset. For more information, refer to **Section 23.0 "Electrical Specifications"**.

See Configuration Word 2 register (Register 8-2) for VCAP enable bits.

#### 6.4 PORTC and TRISC Registers

PORTC is a 8-bit wide, bidirectional port. The corresponding data direction register is TRISC (Register 6-11). Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 6-3 shows how to initialize PORTC.

Reading the PORTC register (Register 6-10) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch.

The TRISC register (Register 6-11) controls the PORTC pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISC register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

#### EXAMPLE 6-3: INITIALIZING PORTC

| BANKSEL PORTC  | ;                          |

|----------------|----------------------------|

| CLRF PORTC     | ;Init PORTC                |

| BANKSEL TRISC  | i                          |

| MOVLW B'000011 | 00' ;Set RC<3:2> as inputs |

| MOVWF TRISC    | ;and set RC<7:4,1:0>       |

|                | ;as outputs                |

|                |                            |

The location of the CCP2 function is controlled by the CCP2SEL bit in the APFCON register (refer to Register 6-1).

#### REGISTER 6-10: PORTC: PORTC REGISTER

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| RC7   | RC6   | RC5   | RC4   | RC3   | RC2   | RC1   | RC0   |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 RC<7:0>: PORTC General Purpose I/O Pin bits

1 = Port pin is > VIH 0 = Port pin is < VIL

#### REGISTER 6-11: TRISC: PORTC TRI-STATE REGISTER

| R/W-1  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| TRISC7 | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-0 TRISC<7:0>: PORTC Tri-State Control bits

1 = PORTC pin configured as an input (tri-stated)

0 = PORTC pin configured as an output

#### 9.1.5 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital conversion. The ADC interrupt flag is the ADIF bit in the PIR1 register. The ADC interrupt enable is the ADIE bit in the PIE1 register. The ADIF bit must be cleared in software.

| Note 1: | The ADIF bit is set at the completion of |

|---------|------------------------------------------|

|         | every conversion, regardless of whether  |

|         | or not the ADC interrupt is enabled.     |

**2:** The ADC operates during Sleep only when the FRC oscillator is selected.

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake-up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake-up from Sleep and resume in-line code execution, the GIE and PEIE bits of the INTCON register must be disabled. If the GIE and PEIE bits of the INTCON register are enabled, execution will switch to the Interrupt Service Routine.

Please refer to **Section 9.1.5** "Interrupts" for more information.

#### 9.2 ADC Operation

#### 9.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/ DONE bit of the ADCON0 register to a '1' will start the Analog-to-Digital conversion.

Note: The GO/DONE bit should not be set in the same instruction that turns on the ADC. Refer to Section 9.2.6 "A/D Conversion Procedure".

#### 9.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- Set the ADIF Interrupt Flag bit

- Update the ADRES register with new conversion result

#### 9.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRES register will be updated with the partially complete Analog-to-Digital conversion sample. Incomplete bits will match the last bit converted.

| Note: | A device Reset forces all registers to their |

|-------|----------------------------------------------|

|       | Reset state. Thus, the ADC module is         |

|       | turned off and any pending conversion is     |

|       | terminated.                                  |

#### 9.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC clock source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

#### 9.2.5 SPECIAL EVENT TRIGGER

The Special Event Trigger of the CCP module allows periodic ADC measurements without software intervention. When this trigger occurs, the GO/DONE bit is set by hardware and the Timer1 counter resets to zero.

Using the Special Event Trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met.

Refer to Section 15.0 "Capture/Compare/PWM (CCP) Module" for more information.

#### 9.3 A/D Acquisition Requirements

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 9-3. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), refer to Figure 9-3. The maximum recommended impedance for analog sources is 10 k $\Omega$ . As the source impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an A/D acquisition must be done before the conversion can be started. To calculate the minimum acquisition time, Equation 9-1 may be used. This equation assumes that 1/2 LSb error is used (256 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

#### EQUATION 9-1: **ACQUISITION TIME EXAMPLE**

Assumptions: Temperature =

$$50^{\circ}C$$

and external impedance of  $10k\Omega 5.0V VDD$

$TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient$

$= TAMP + TC + TCOFF$

$= 2\mu s + TC + [(Temperature - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$

The value for TC can be approximated with the following equations:

value for IC can be approximated with the jollowing equations:

$$V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - 1}\right) = V_{CHOLD} \qquad ;[1] V_{CHOLD} charged to within 1/2 lsb$$

$$V_{APPLIED}\left(1 - e^{\frac{-TC}{RC}}\right) = V_{CHOLD} \qquad ;[2] V_{CHOLD} charge response to V_{APPLIED} V_{APPLIED}\left(1 - e^{\frac{-TC}{RC}}\right) = V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - 1}\right) \qquad ;combining [1] and [2]$$

*Note:* Where n = number of bits of the ADC.

Solving for TC:

$$Tc = -CHOLD(RIC + RSS + RS) ln(1/511)$$

= -10pF(1k\Omega + 7k\Omega + 10k\Omega) ln(0.001957)

= 1.12\mus

Therefore:

$$TACQ = 2\mu s + 1.12\mu s + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

= 4.42\mu s

Note 1: The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- 3: The maximum recommended impedance for analog sources is 10 k $\Omega$ . This is required to meet the pin leakage specification.

#### 14.1 Analog MUX

The capacitive sensing module can monitor up to 8 inputs. The capacitive sensing inputs are defined as CPS<7:0>. To determine if a frequency change has occurred the user must:

- Select the appropriate CPS pin by setting the CPSCH<2:0> bits of the CPSCON1 register

- Set the corresponding ANSEL bit

- Set the corresponding TRIS bit

- Run the software algorithm

Selection of the CPSx pin while the module is enabled will cause the capacitive sensing oscillator to be on the CPSx pin. Failure to set the corresponding ANSEL and TRIS bits can cause the capacitive sensing oscillator to stop, leading to false frequency readings.

#### 14.2 Capacitive Sensing Oscillator

The capacitive sensing oscillator consists of a constant current source and a constant current sink, to produce a triangle waveform. The CPSOUT bit of the CPSCON0 register shows the status of the capacitive sensing oscillator, whether it is a sinking or sourcing current. The oscillator is designed to drive a capacitive load (single PCB pad) and at the same time, be a clock source to either Timer0 or Timer1. The oscillator has three different current settings as defined by CPS-RNG<1:0> of the CPSCON0 register. The different current settings for the oscillator serve two purposes:

- Maximize the number of counts in a timer for a fixed-time base

- Maximize the count differential in the timer during a change in frequency

#### 14.3 Timer Resources

To measure the change in frequency of the capacitive sensing oscillator, a fixed-time base is required. For the period of the fixed-time base, the capacitive sensing oscillator is used to clock either Timer0 or Timer1. The frequency of the capacitive sensing oscillator is equal to the number of counts in the timer divided by the period of the fixed-time base.

#### 14.4 Fixed-Time Base

To measure the frequency of the capacitive sensing oscillator, a fixed-time base is required. Any timer resource or software loop can be used to establish the fixed-time base. It is up to the end user to determine the method in which the fixed-time base is generated.

Note: The fixed-time base can not be generated by the timer resource the capacitive sensing oscillator is clocking.

#### 14.4.1 TIMER0

To select Timer0 as the timer resource for the capacitive sensing module:

- · Set the T0XCS bit of the CPSCON0 register

- · Clear the T0CS bit of the OPTION register

When Timer0 is chosen as the timer resource, the capacitive sensing oscillator will be the clock source for Timer0. Refer to **Section 11.0** "**Timer0 Module**" for additional information.

#### 14.4.2 TIMER1

To select Timer1 as the timer resource for the capacitive sensing module, set the TMR1CS<1:0> of the T1CON register to '11'. When Timer1 is chosen as the timer resource, the capacitive sensing oscillator will be the clock source for Timer1. Because the Timer1 module has a gate control, developing a time base for the frequency measurement can be simplified using either:

- The Timer0 overflow flag

- The Timer2 overflow flag

- The WDT overflow flag

It is recommended that one of these flags, in conjunction with the toggle mode of the Timer1 gate, is used to develop the fixed-time base required by the software portion of the capacitive sensing module. Refer to **Section 12.0 "Timer1 Module with Gate Control**" for additional information.

#### TABLE 14-1: TIMER1 ENABLE FUNCTION

| TMR10N | TMR1GE | Timer1 Operation       |

|--------|--------|------------------------|

| 0      | 0      | Off                    |

| 0      | 1      | Off                    |

| 1      | 0      | On                     |

| 1      | 1      | Count Enabled by input |

#### 14.5 Software Control

The software portion of the capacitive sensing module is required to determine the change in frequency of the capacitive sensing oscillator. This is accomplished by the following:

- Setting a fixed-time base to acquire counts on Timer0 or Timer1

- Establishing the nominal frequency for the capacitive sensing oscillator

- Establishing the reduced frequency for the capacitive sensing oscillator due to an additional capacitive load

- Set the frequency threshold

#### 14.5.1 NOMINAL FREQUENCY (NO CAPACITIVE LOAD)

To determine the nominal frequency of the capacitive sensing oscillator:

- Remove any extra capacitive load on the selected CPSx pin

- At the start of the fixed-time base, clear the timer resource

- At the end of the fixed-time base, save the value in the timer resource

The value of the timer resource is the number of oscillations of the capacitive sensing oscillator for the given time base. The frequency of the capacitive sensing oscillator is equal to the number of counts on in the timer divided by the period of the fixed-time base.

#### 14.5.2 REDUCED FREQUENCY (ADDITIONAL CAPACITIVE LOAD)

The extra capacitive load will cause the frequency of the capacitive sensing oscillator to decrease. To determine the reduced frequency of the capacitive sensing oscillator:

- Add a typical capacitive load on the selected CPSx pin

- Use the same fixed-time base as the nominal frequency measurement

- At the start of the fixed-time base, clear the timer resource

- At the end of the fixed-time base, save the value in the timer resource

The value of the timer resource is the number of oscillations of the capacitive sensing oscillator with an additional capacitive load. The frequency of the capacitive sensing oscillator is equal to the number of counts on in the timer divided by the period of the fixedtime base. This frequency should be less than the value obtained during the nominal frequency measurement.

#### 14.5.3 FREQUENCY THRESHOLD

The frequency threshold should be placed midway between the value of nominal frequency and the reduced frequency of the capacitive sensing oscillator. Refer to Application Note *AN1103, Software Handling for Capacitive Sensing* (DS01103) for more detailed information the software required for capacitive sensing module.

**Note:** For more information on general capacitive sensing refer to Application Notes:

- •AN1101, Introduction to Capacitive Sensing (DS01101)

- •AN1102, Layout and Physical Design Guidelines for Capacitive Sensing (DS01102)

#### 16.1.2 AUSART ASYNCHRONOUS RECEIVER

The Asynchronous mode is typically used in RS-232 systems. The receiver block diagram is shown in Figure 16-2. The data is received on the RX/DT pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at 16 times the baud rate, whereas the serial Receive Shift Register (RSR) operates at the bit rate. When all eight or nine bits of the character have been shifted in, they are immediately transferred to a two character First-In First-Out (FIFO) memory. The FIFO buffering allows reception of two complete characters and the start of a third character before software must start servicing the AUSART receiver. The FIFO and RSR registers are not directly accessible by software. Access to the received data is via the RCREG register.

#### 16.1.2.1 Enabling the Receiver

The AUSART receiver is enabled for asynchronous operation by configuring the following three control bits:

- CREN = 1

- SYNC = 0

- SPEN = 1

All other AUSART control bits are assumed to be in their default state.

Setting the CREN bit of the RCSTA register enables the receiver circuitry of the AUSART. Clearing the SYNC bit of the TXSTA register configures the AUSART for asynchronous operation. Setting the SPEN bit of the RCSTA register enables the AUSART and automatically configures the RX/DT I/O pin as an input.

| Note: | When the SPEN bit is set the TX/CK I/O         |

|-------|------------------------------------------------|

|       | pin is automatically configured as an          |

|       | output, regardless of the state of the         |

|       | corresponding TRIS bit and whether or          |

|       | not the AUSART transmitter is enabled.         |

|       | The PORT latch is disconnected from the        |

|       | output driver so it is not possible to use the |

|       | TX/CK pin as a general purpose output.         |

#### 16.1.2.2 Receiving Data

The receiver data recovery circuit initiates character reception on the falling edge of the first bit. The first bit, also known as the Start bit, is always a zero. The data recovery circuit counts one-half bit time to the center of the Start bit and verifies that the bit is still a zero. If it is not a zero then the data recovery circuit aborts character reception, without generating an error, and resumes looking for the falling edge of the Start bit. If the Start bit zero verification succeeds then the data recovery circuit counts a full bit time to the center of the next bit. The bit is then sampled by a majority detect circuit and the resulting '0' or '1' is shifted into the RSR. This repeats until all data bits have been sampled and shifted into the RSR. One final bit time is measured and the level sampled. This is the Stop bit, which is always a '1'. If the data recovery circuit samples a '0' in the Stop bit position then a framing error is set for this character, otherwise the framing error is cleared for this character. Refer to Section 16.1.2.4 "Receive Framing Error" for more information on framing errors.

Immediately after all data bits and the Stop bit have been received, the character in the RSR is transferred to the AUSART receive FIFO and the RCIF interrupt flag bit of the PIR1 register is set. The top character in the FIFO is transferred out of the FIFO by reading the RCREG register.

| Note: | If the receive FIFO is overrun, no additional<br>characters will be received until the overrun |  |  |  |  |

|-------|------------------------------------------------------------------------------------------------|--|--|--|--|

|       | condition is cleared. Refer to                                                                 |  |  |  |  |

|       | Section 16.1.2.5 "Receive Overrun                                                              |  |  |  |  |

|       | Error" for more information on overrun                                                         |  |  |  |  |

|       | errors.                                                                                        |  |  |  |  |

#### 16.1.2.3 Receive Interrupts

The RCIF interrupt flag bit of the PIR1 register is set whenever the AUSART receiver is enabled and there is an unread character in the receive FIFO. The RCIF interrupt flag bit is read-only, it cannot be set or cleared by software.

RCIF interrupts are enabled by setting all of the following bits:

- RCIE, Receive Interrupt Enable bit of the PIE1

register

- PEIE, Peripheral Interrupt Enable bit of the INTCON register

- GIE, Global Interrupt Enable bit of the INTCON register

The RCIF interrupt flag bit of the PIR1 register will be set when there is an unread character in the FIFO, regardless of the state of interrupt enable bits.

| Name   | Bit 7                        | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2     | Bit 1     | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|------------------------------|--------|--------|--------|--------|-----------|-----------|--------|----------------------|---------------------------------|

| INTCON | GIE                          | PEIE   | TOIE   | INTE   | RBIE   | T0IF      | INTF      | RBIF   | 0000 000x            | 0000 000x                       |

| PIE1   | TMR1GIE                      | ADIE   | RCIE   | TXIE   | SSPIE  | CCP1IE    | TMR2IE    | TMR1IE | 0000 0000            | 0000 0000                       |

| PIR1   | TMR1GIF                      | ADIF   | RCIF   | TXIF   | SSPIF  | CCP1IF    | TMR2IF    | TMR1IF | 0000 0000            | 0000 0000                       |

| RCREG  | AUSART Receive Data Register |        |        |        |        | 0000 0000 | 0000 0000 |        |                      |                                 |

| RCSTA  | SPEN                         | RX9    | SREN   | CREN   | ADDEN  | FERR      | OERR      | RX9D   | 0000 000x            | 0000 000x                       |

| SPBRG  | BRG7                         | BRG6   | BRG5   | BRG4   | BRG3   | BRG2      | BRG1      | BRG0   | 0000 0000            | 0000 0000                       |

| TRISC  | TRISC7                       | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2    | TRISC1    | TRISC0 | 1111 1111            | 1111 1111                       |

| TXSTA  | CSRC                         | TX9    | TXEN   | SYNC   | —      | BRGH      | TRMT      | TX9D   | 0000 -010            | 0000 -010                       |

#### TABLE 16-2: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for asynchronous reception.

| R/W-0             | R/W-0                                                                                         | R-0                                               | R-0                                 | R-0                                | R-0                  | R-0 | R-0                |  |  |

|-------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------------|-------------------------------------|------------------------------------|----------------------|-----|--------------------|--|--|

| SMP               | CKE                                                                                           | D/A                                               | Р                                   | S                                  | R/W                  | UA  | BF                 |  |  |

| bit 7             |                                                                                               | ·                                                 |                                     |                                    |                      | •   | bit                |  |  |

| Legend:           |                                                                                               |                                                   |                                     |                                    |                      |     |                    |  |  |

| R = Readable bit  |                                                                                               | W = Writable                                      | bit                                 | U = Unimplemented bit, read as '0' |                      |     |                    |  |  |

| -n = Value at POR |                                                                                               | '1' = Bit is set                                  |                                     | '0' = Bit is cle                   | '0' = Bit is cleared |     | x = Bit is unknown |  |  |

| bit 7             | <u>SPI Master m</u><br>1 = Input data<br>0 = Input data<br><u>SPI Slave mo</u>                | a sampled at er<br>a sampled at m                 | nd of data ou<br>iddle of data      | output time                        |                      |     |                    |  |  |

| bit 6             | <u>SPI mode, Cł</u><br>1 = Data stab<br>0 = Data stab<br><u>SPI mode, Cł</u><br>1 = Data stab | le on rising ed<br>le on falling ed               | ge of SCK<br>ge of SCK<br>ge of SCK |                                    |                      |     |                    |  |  |

| bit 5             | <b>D/A:</b> Data/Address bit<br>Used in I <sup>2</sup> C mode only.                           |                                                   |                                     |                                    |                      |     |                    |  |  |

| bit 4             | <b>P:</b> Stop bit<br>Used in $I^2C$ mode only.                                               |                                                   |                                     |                                    |                      |     |                    |  |  |

| bit 3             | <b>S:</b> Start bit<br>Used in I <sup>2</sup> C mode only.                                    |                                                   |                                     |                                    |                      |     |                    |  |  |

| bit 2             | <b>R/W:</b> Read/Write Information bit<br>Used in I <sup>2</sup> C mode only.                 |                                                   |                                     |                                    |                      |     |                    |  |  |

| bit 1             | <b>UA:</b> Update Address bit<br>Used in I <sup>2</sup> C mode only.                          |                                                   |                                     |                                    |                      |     |                    |  |  |

| bit 0             |                                                                                               | Il Status bit<br>complete, SSP<br>not complete, S |                                     | npty                               |                      |     |                    |  |  |

#### REGISTER 17-2: SSPSTAT: SYNC SERIAL PORT STATUS REGISTER (SPI MODE)

| SUBWF            | Subtract W from f                                               |                                                                                                                             |  |  |  |

|------------------|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] SU                                                      | JBWF f,d                                                                                                                    |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$ |                                                                                                                             |  |  |  |

| Operation:       | (f) - (W) $\rightarrow$ (destination)                           |                                                                                                                             |  |  |  |

| Status Affected: | C, DC, Z                                                        |                                                                                                                             |  |  |  |

| Description:     | W register f<br>'0', the resu<br>register. If 'd                | s complement method)<br>rom register 'f'. If 'd' is<br>It is stored in the W<br>d' is '1', the result is<br>in register 'f. |  |  |  |

|                  | <b>C</b> = 0                                                    | W > f                                                                                                                       |  |  |  |

|                  | <b>C</b> = 1                                                    | $W \leq f$                                                                                                                  |  |  |  |

$\overline{DC} = 0$

**DC** = 1

W<3:0> > f<3:0> W<3:0>  $\leq$  f<3:0>

| XORLW            | Exclusive OR literal with W                                                                                            |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                               |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                      |  |  |  |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                          |  |  |  |  |

| Status Affected: | Z                                                                                                                      |  |  |  |  |

| Description:     | The contents of the W register<br>are XOR'ed with the 8-bit<br>literal 'k'. The result is placed in<br>the W register. |  |  |  |  |

| SWAPF            | Swap Nibbles in f                                                                                                                                                      |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] SWAPF f,d                                                                                                                                                      |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                            |  |  |  |  |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                                |  |  |  |  |

| Status Affected: | None                                                                                                                                                                   |  |  |  |  |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed in register 'f'. |  |  |  |  |

| XORWF            | Exclusive OR W with f                                                                                                                                                           |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                      |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                     |  |  |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                       |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                               |  |  |  |  |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |  |  |  |  |

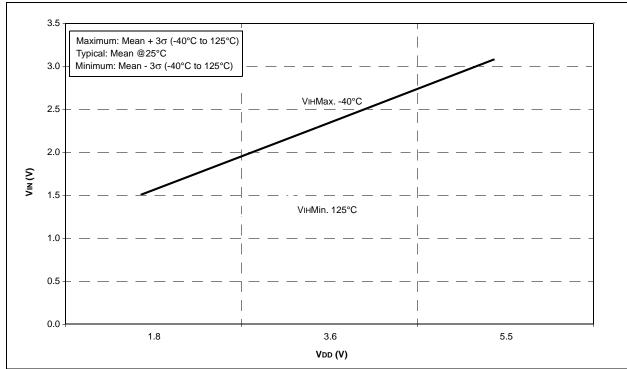

FIGURE 24-50: SCHMITT TRIGGER INPUT THRESHOLD VIN vs. VDD OVER TEMPERATURE

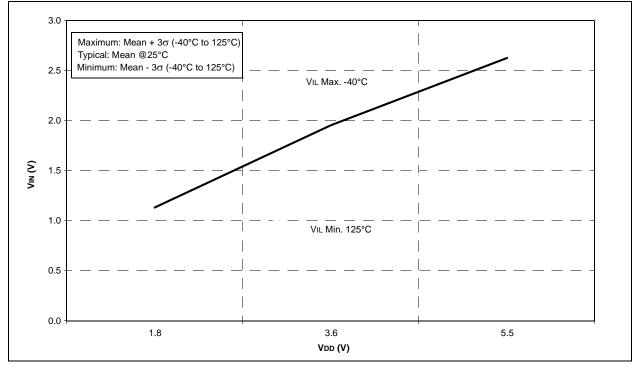

FIGURE 24-51: SCHMITT TRIGGER INPUT THRESHOLD VIN vs. VDD OVER TEMPERATURE

#### 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-052C Sheet 1 of 2

### **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

**Chicago** Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

**Canada - Toronto** Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan Tel: 86-769-8702-9880

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

**Japan - Osaka** Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

**Taiwan - Kaohsiung** Tel: 886-7-213-7828

Taiwan - Taipei Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

Thailand - Bangkok Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf Tel: 49-2129-3766400

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw Tel: 48-22-3325737

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

07/14/15