Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 11x8b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f722at-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.6 Time-out Sequence

On power-up, the time-out sequence is as follows: first, PWRT time out is invoked after POR has expired, then OST is activated after the PWRT time out has expired. The total time out will vary based on oscillator configuration and  $\overrightarrow{PWRTE}$  bit status. For example, in EC mode with  $\overrightarrow{PWRTE}$  bit = 1 ( $\overrightarrow{PWRT}$  disabled), there will be no time-out at all. Figure 3-4, Figure 3-5 and Figure 3-6 depict time-out sequences.

Since the time outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then, bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (see Figure 3-5). This is useful for testing purposes or to synchronize more than one PIC16(L)F722A/723A device operating in parallel.

Table 3-3 shows the Reset conditions for some special registers.

# 3.7 Power Control (PCON) Register

The Power Control (PCON) register has two Status bits to indicate what type of Reset that last occurred.

Bit 0 is  $\overrightarrow{BOR}$  (Brown-out Reset).  $\overrightarrow{BOR}$  is unknown on Power-on Reset. It must then be set by the user and checked on subsequent Resets to see if  $\overrightarrow{BOR} = 0$ , indicating that a brown-out has occurred. The  $\overrightarrow{BOR}$ Status bit is a "don't care" and is not necessarily predictable if the brown-out circuit is disabled (BOREN<1:0> = 00 in the Configuration Word register).

Bit 1 is POR (Power-on Reset). It is a '0' on Power-on Reset and unaffected otherwise. The user must write a '1' to this bit following a Power-on Reset. On a subsequent Reset, if POR is '0', it will indicate that a Power-on Reset has occurred (i.e., VDD may have gone too low).

For more information, see Section 3.5 "Brown-Out Reset (BOR)".

| Oscillator Configuration  | Power-up               |             | Brown-o                | Wake-up from     |             |

|---------------------------|------------------------|-------------|------------------------|------------------|-------------|

| Oscillator Configuration  | <b>PWRTE</b> = 0       | PWRTE = 1   | <b>PWRTE</b> = 0       | <b>PWRTE</b> = 1 | Sleep       |

| XT, HS, LP <sup>(1)</sup> | TPWRT + 1024 •<br>Tosc | 1024 • Tosc | TPWRT + 1024 •<br>Tosc | 1024 • Tosc      | 1024 • Tosc |

| RC, EC, INTOSC            | TPWRT                  |             | TPWRT                  | _                | —           |

### TABLE 3-2: TIME OUT IN VARIOUS SITUATIONS

Note 1: LP mode with T1OSC disabled.

# TABLE 3-3: RESET BITS AND THEIR SIGNIFICANCE

| POR | BOR | то | PD | Condition                          |  |

|-----|-----|----|----|------------------------------------|--|

| 0   | u   | 1  | 1  | Power-on Reset                     |  |

| 1   | 0   | 1  | 1  | Brown-out Reset                    |  |

| u   | u   | 0  | u  | WDT Reset                          |  |

| u   | u   | 0  | 0  | WDT Wake-up                        |  |

| u   | u   | u  | u  | MCLR Reset during normal operation |  |

| u   | u   | 1  | 0  | MCLR Reset during Sleep            |  |

**Legend:** u = unchanged, x = unknown

# 6.2.1 ANSELA REGISTER

The ANSELA register (Register 6-4) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELA bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELA bits has no affect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

# REGISTER 6-4: ANSELA: PORTA ANALOG SELECT REGISTER

'1' = Bit is set

| U-0                               | U-0 | R/W-1 | R/W-1        | R/W-1            | R/W-1    | R/W-1 | R/W-1 |

|-----------------------------------|-----|-------|--------------|------------------|----------|-------|-------|

| —                                 | —   | ANSA5 | ANSA4        | ANSA3            | ANSA2    | ANSA1 | ANSA0 |

| bit 7                             |     |       |              |                  |          |       | bit 0 |

|                                   |     |       |              |                  |          |       |       |

| Legend:                           |     |       |              |                  |          |       |       |

| R = Readable bit W = Writable bit |     |       | U = Unimpler | mented bit, read | l as '0' |       |       |

'0' = Bit is cleared

bit 7-6 Unimplemented: Read as '0'

-n = Value at POR

bit 5-0 **ANSA<5:0>**: Analog Select between Analog or Digital Function on pins RA<5:0>, respectively 0 = Digital I/O. Pin is assigned to port or digital special function. 1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

x = Bit is unknown

# 8.2 Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out using ICSP<sup>TM</sup> for verification purposes.

| Note: | The entire Flash program memory will be   |

|-------|-------------------------------------------|

|       | erased when the code protection is turned |

|       | off. See the "PIC16(L)F72X Memory         |

|       | Programming Specification" (DS41332)      |

|       | for more information.                     |

# 8.3 User ID

Four memory locations (2000h-2003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution, but are readable and writable during Program/Verify mode. Only the Least Significant 7 bits of the ID locations are reported when using MPLAB IDE. See the *"PIC16(L)F72X Memory Programming Specification"* (DS41332) for more information.

| U-0                                                      | R/W-0        | R/W-0                                                                     | R/W-0           | U-0              | U-0             | R/W-0           | R/W-0  |  |  |  |

|----------------------------------------------------------|--------------|---------------------------------------------------------------------------|-----------------|------------------|-----------------|-----------------|--------|--|--|--|

| _                                                        | ADCS2        | ADCS1                                                                     | ADCS0           | _                | _               | ADREF1          | ADREF0 |  |  |  |

| bit 7                                                    |              | ·                                                                         |                 |                  |                 |                 | bit C  |  |  |  |

|                                                          |              |                                                                           |                 |                  |                 |                 |        |  |  |  |

| Legend:                                                  |              |                                                                           |                 |                  |                 |                 |        |  |  |  |

| R = Readal                                               | ble bit      | W = Writable                                                              | bit             | U = Unimpler     | mented bit, rea | d as '0'        |        |  |  |  |

| -n = Value a                                             | at POR       | '1' = Bit is set                                                          |                 | '0' = Bit is cle | ared            | x = Bit is unkr | nown   |  |  |  |

|                                                          |              |                                                                           |                 |                  |                 |                 |        |  |  |  |

| bit 7                                                    | Unimplemen   | ted: Read as '                                                            | 0'              |                  |                 |                 |        |  |  |  |

| bit 6-4 ADCS<2:0>: A/D Conversion Clock Select bits      |              |                                                                           |                 |                  |                 |                 |        |  |  |  |

|                                                          |              | 000 = Fosc/2                                                              |                 |                  |                 |                 |        |  |  |  |

|                                                          |              | 001 = Fosc/8                                                              |                 |                  |                 |                 |        |  |  |  |

|                                                          |              | 010 = Fosc/32                                                             |                 |                  |                 |                 |        |  |  |  |

|                                                          | ·            | 011 = FRC (clock supplied from a dedicated RC oscillator)<br>100 = Fosc/4 |                 |                  |                 |                 |        |  |  |  |

|                                                          | 101 = Fosc/1 | -                                                                         |                 |                  |                 |                 |        |  |  |  |

|                                                          | 110 = Fosc/6 | 64                                                                        |                 |                  |                 |                 |        |  |  |  |

|                                                          | 111 = FRC (C | lock supplied f                                                           | rom a dedicate  | ed RC oscillator | r)              |                 |        |  |  |  |

| bit 3-2                                                  | Unimplemen   | ted: Read as '                                                            | 0'              |                  |                 |                 |        |  |  |  |

| bit 1-0 ADREF<1:0>: Voltage Reference Configuration bits |              |                                                                           |                 |                  |                 |                 |        |  |  |  |

|                                                          | 0x = VREF is | connected to \                                                            | /DD             |                  |                 |                 |        |  |  |  |

|                                                          |              | connected to e                                                            |                 |                  |                 |                 |        |  |  |  |

|                                                          | 11 = VREF is | connected to i                                                            | nternal Fixed V | /oltage Referer  | nce             |                 |        |  |  |  |

# REGISTER 9-2: ADCON1: A/D CONTROL REGISTER 1

### REGISTER 9-3: ADRES: ADC RESULT REGISTER

| R/W-x  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| ADRES7 | ADRES6 | ADRES5 | ADRES4 | ADRES3 | ADRES2 | ADRES1 | ADRES0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 7-0 **ADRES<7:0>**: ADC Result Register bits 8-bit conversion result.

#### 9.3 A/D Acquisition Requirements

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 9-3. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), refer to Figure 9-3. The maximum recommended impedance for analog sources is 10 k $\Omega$ . As the source impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an A/D acquisition must be done before the conversion can be started. To calculate the minimum acquisition time, Equation 9-1 may be used. This equation assumes that 1/2 LSb error is used (256 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

#### EQUATION 9-1: **ACQUISITION TIME EXAMPLE**

Assumptions: Temperature =

$$50^{\circ}C$$

and external impedance of  $10k\Omega 5.0V VDD$

$TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient$

$= TAMP + TC + TCOFF$

$= 2\mu s + TC + [(Temperature - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$

The value for TC can be approximated with the following equations:

value for IC can be approximated with the jollowing equations:

$$V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - 1}\right) = V_{CHOLD} \qquad ;[1] V_{CHOLD} charged to within 1/2 lsb$$

$$V_{APPLIED}\left(1 - e^{\frac{-TC}{RC}}\right) = V_{CHOLD} \qquad ;[2] V_{CHOLD} charge response to V_{APPLIED} V_{APPLIED}\left(1 - e^{\frac{-TC}{RC}}\right) = V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - 1}\right) \qquad ;combining [1] and [2]$$

*Note:* Where n = number of bits of the ADC.

Solving for TC:

$$Tc = -CHOLD(RIC + RSS + RS) ln(1/511)$$

= -10pF(1k\Omega + 7k\Omega + 10k\Omega) ln(0.001957)

= 1.12\mus

Therefore:

$$TACQ = 2\mu s + 1.12\mu s + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

= 4.42\mu s

Note 1: The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- 3: The maximum recommended impedance for analog sources is 10 k $\Omega$ . This is required to meet the pin leakage specification.

# 12.6 Timer1 Gate

Timer1 can be configured to count freely or the count can be enabled and disabled using Timer1 gate circuitry. This is also referred to as Timer1 Gate Count Enable.

Timer1 gate can also be driven by multiple selectable sources.

# 12.6.1 TIMER1 GATE COUNT ENABLE

The Timer1 gate is enabled by setting the TMR1GE bit of the T1GCON register. The polarity of the Timer1 gate is configured using the T1GPOL bit of the T1GCON register.

When Timer1 Gate (T1G) input is active, Timer1 will increment on the rising edge of the Timer1 clock source. When Timer1 gate input is inactive, no incrementing will occur and Timer1 will hold the current count. See Figure 12-4 for timing details.

# TABLE 12-3: TIMER1 GATE ENABLE SELECTIONS

| T1CLK      | T1GPOL | T1G | Timer1 Operation |

|------------|--------|-----|------------------|

| 1          | 0      | 0   | Counts           |

| $\uparrow$ | 0      | 1   | Holds Count      |

| $\uparrow$ | 1      | 0   | Holds Count      |

| $\uparrow$ | 1      | 1   | Counts           |

# 12.6.2 TIMER1 GATE SOURCE SELECTION

The Timer1 gate source can be selected from one of four different sources. Source selection is controlled by the T1GSS bits of the T1GCON register. The polarity for each available source is also selectable. Polarity selection is controlled by the T1GPOL bit of the T1GCON register.

# TABLE 12-4: TIMER1 GATE SOURCES

| T1GSS | Timer1 Gate Source                                                    |

|-------|-----------------------------------------------------------------------|

| 00    | Timer1 Gate Pin                                                       |

| 01    | Overflow of Timer0<br>(TMR0 increments from FFh to 00h)               |

| 10    | Timer2 match PR2<br>(TMR2 increments to match PR2)                    |

| 11    | Count Enabled by WDT Overflow<br>(Watchdog Time-out interval expired) |

# 12.6.2.1 T1G Pin Gate Operation

The T1G pin is one source for Timer1 gate control. It can be used to supply an external source to the Timer1 gate circuitry.

# 12.6.2.2 Timer0 Overflow Gate Operation

When Timer0 increments from FFh to 00h, a low-tohigh pulse will automatically be generated and internally supplied to the Timer1 gate circuitry.

# 12.6.2.3 Timer2 Match Gate Operation

The TMR2 register will increment until it matches the value in the PR2 register. On the very next increment cycle, TMR2 will be reset to 00h. When this Reset occurs, a low-to-high pulse will automatically be generated and internally supplied to the Timer1 gate circuitry.

# 12.6.2.4 Watchdog Overflow Gate Operation

The Watchdog Timer oscillator, prescaler and counter will be automatically turned on when TMR1GE = 1 and T1GSS selects the WDT as a gate source for Timer1 (T1GSS = 11). TMR1ON does not factor into the oscillator, prescaler and counter enable. See Table .

The PSA and PS bits of the OPTION register still control what time-out interval is selected. Changing the prescaler during operation may result in a spurious capture.

Enabling the Watchdog Timer oscillator does not automatically enable a Watchdog Reset or Wake-up from Sleep upon counter overflow.

| Note: | When using the WDT as a gate source for     |

|-------|---------------------------------------------|

|       | 5 5                                         |

|       | Timer1, operations that clear the Watchdog  |

|       | Timer (CLRWDT, SLEEP instructions) will     |

|       | affect the time interval being measured for |

|       | capacitive sensing. This includes waking    |

|       | from Sleep. All other interrupts that might |

|       | wake the device from Sleep should be        |

|       | disabled to prevent them from disturbing    |

|       | the measurement period.                     |

As the gate signal coming from the WDT counter will generate different pulse widths depending on if the WDT is enabled, when the CLRWDT instruction is executed, and so on, Toggle mode must be used. A specific sequence is required to put the device into the correct state to capture the next WDT counter interval.

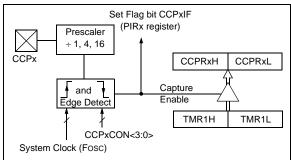

# 15.1 Capture Mode

In Capture mode, CCPRxH:CCPRxL captures the 16-bit value of the TMR1 register when an event occurs on pin CCPx. An event is defined as one of the following and is configured by the CCPxM<3:0> bits of the CCPxCON register:

- Every falling edge

- Every rising edge

- Every 4th rising edge

- Every 16th rising edge

When a capture is made, the Interrupt Request Flag bit CCPxIF of the PIRx register is set. The interrupt flag must be cleared in software. If another capture occurs before the value in the CCPRxH, CCPRxL register pair is read, the old captured value is overwritten by the new captured value (refer to Figure 15-1).

# 15.1.1 CCPx PIN CONFIGURATION

In Capture mode, the CCPx pin should be configured as an input by setting the associated TRIS control bit.

Either RC1 or RB3 can be selected as the CCP2 pin. Refer to **Section 6.1** "Alternate Pin Function" for more information.

**Note:** If the CCPx pin is configured as an output, a write to the port can cause a capture condition.

### FIGURE 15-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

# 15.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode or when Timer1 is clocked at Fosc, the capture operation may not work.

# 15.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit of the PIEx register clear to avoid false interrupts. Additionally, the user should clear the CCPxIF interrupt flag bit of the PIRx register following any change in operating mode.

Note: Clocking Timer1 from the system clock (Fosc) should not be used in Capture mode. In order for Capture mode to recognize the trigger event on the CCPx pin, Timer1 must be clocked from the instruction clock (Fosc/4) or from an external clock source.

# 15.1.4 CCP PRESCALER

There are four prescaler settings specified by the CCPxM<3:0> bits of the CCPxCON register. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another does not clear the prescaler and may generate a false interrupt. To avoid this unexpected operation, turn the module off by clearing the CCPxCON register before changing the prescaler (refer to Example 15-1).

# EXAMPLE 15-1: CHANGING BETWEEN CAPTURE PRESCALERS

| BANKSEL | CCP1CON     | ;Set Bank bits to point |

|---------|-------------|-------------------------|

|         |             | ;to CCP1CON             |

| CLRF    | CCP1CON     | ;Turn CCP module off    |

| MOVLW   | NEW_CAPT_PS | ;Load the W reg with    |

|         |             | ; the new prescaler     |

|         |             | ; move value and CCP ON |

| MOVWF   | CCP1CON     | ;Load CCP1CON with this |

|         |             | ; value                 |

|         |             |                         |

# 15.1.5 CAPTURE DURING SLEEP

Capture mode depends upon the Timer1 module for proper operation. There are two options for driving the Timer1 module in Capture mode. It can be driven by the instruction clock (Fosc/4), or by an external clock source.

If Timer1 is clocked by FOSC/4, then Timer1 will not increment during Sleep. When the device wakes from Sleep, Timer1 will continue from its previous state.

If Timer1 is clocked by an external clock source, then Capture mode will operate as defined in **Section 15.1** "**Capture Mode**".

| Name    | Bit 7                                                                       | Bit 6     | Bit 5        | Bit 4     | Bit 3          | Bit 2  | Bit 1  | Bit 0   | Register<br>on Page |

|---------|-----------------------------------------------------------------------------|-----------|--------------|-----------|----------------|--------|--------|---------|---------------------|

| ANSELB  |                                                                             | -         | ANSB5        | ANSB4     | ANSB3          | ANSB2  | ANSB1  | ANSB0   | 53                  |

| APFCON  | —                                                                           | _         | _            | —         | _              | —      | SSSEL  | CCP2SEL | 42                  |

| CCP1CON | —                                                                           | _         | DC1B1        | DC1B0     | CCP1M3         | CCP1M2 | CCP1M1 | CCP1M0  | 115                 |

| CCP2CON | —                                                                           | _         | DC2B1        | DC2B0     | CCP2M3         | CCP2M2 | CCP2M1 | CCP2M0  | 115                 |

| CCPRxL  | Capture/Compare/PWM Register X Low Byte                                     |           |              |           |                |        |        |         | 116                 |

| CCPRxH  | Capture/Co                                                                  | mpare/PWN | l Register X | High Byte |                |        |        |         | 116                 |

| INTCON  | GIE                                                                         | PEIE      | TOIE         | INTE      | RBIE           | T0IF   | INTF   | RBIF    | 36                  |

| PIE1    | TMR1GIE                                                                     | ADIE      | RCIE         | TXIE      | SSPIE          | CCP1IE | TMR2IE | TMR1IE  | 37                  |

| PIE2    | —                                                                           | _         |              | _         | _              | —      |        | CCP2IE  | 38                  |

| PIR1    | TMR1GIF                                                                     | ADIF      | RCIF         | TXIF      | SSPIF          | CCP1IF | TMR2IF | TMR1IF  | 39                  |

| PIR2    | —                                                                           | _         | _            | _         | _              | —      |        | CCP2IF  | 40                  |

| T1CON   | TMR1CS1                                                                     | TMR1CS0   | T1CKPS1      | T1CKPS0   | T1OSCEN        | T1SYNC |        | TMR10N  | 103                 |

| T1GCON  | TMR1GE                                                                      | T1GPOL    | T1GTM        | T1GSPM    | T1GGO/<br>DONE | T1GVAL | T1GSS1 | T1GSS0  | 104                 |

| TMR1L   | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |           |              |           |                |        |        |         |                     |

| TMR1H   | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register  |           |              |           |                |        |        |         |                     |

| TRISB   | TRISB7                                                                      | TRISB6    | TRISB5       | TRISB4    | TRISB3         | TRISB2 | TRISB1 | TRISB0  | 52                  |

| TRISC   | TRISC7                                                                      | TRISC6    | TRISC5       | TRISC4    | TRISC3         | TRISC2 | TRISC1 | TRISC0  | 62                  |

Legend: - = Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the Capture.

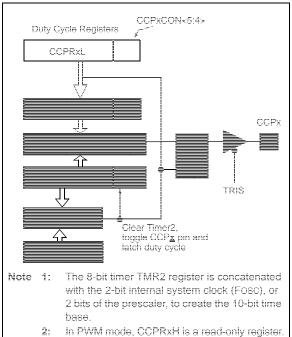

# 15.3 PWM Mode

The PWM mode generates a Pulse-Width Modulated signal on the CCPx pin. The duty cycle, period and resolution are determined by the following registers:

- PR2

- T2CON

- CCPRxL

- CCPxCON

In Pulse-Width Modulation (PWM) mode, the CCP module produces up to a 10-bit resolution PWM output on the CCPx pin.

Figure 15-3 shows a simplified block diagram of PWM operation.

Figure 15-4 shows a typical waveform of the PWM signal.

For a step-by-step procedure on how to set up the CCP module for PWM operation, refer to **Section 15.3.8** "Setup for PWM Operation".

FIGURE 15-3: SIMPLIFIED PWM BLOCK DIAGRAM

The PWM output (Figure 15-4) has a time base (period) and a time that the output stays high (duty cycle).

FIGURE 15-4: CCP PWM OUTPUT

# 15.3.1 CCPX PIN CONFIGURATION

In PWM mode, the CCPx pin is multiplexed with the PORT data latch. The user must configure the CCPx pin as an output by clearing the associated TRIS bit.

Either RC1 or RB3 can be selected as the CCP2 pin. Refer to **Section 6.1** "Alternate Pin Function" for more information.

| Note: | Clearing                               | the | CCPxCON | register | will |  |  |

|-------|----------------------------------------|-----|---------|----------|------|--|--|

|       | relinguish CCPx control of the CCPx pi |     |         |          |      |  |  |

# 16.1.2 AUSART ASYNCHRONOUS RECEIVER

The Asynchronous mode is typically used in RS-232 systems. The receiver block diagram is shown in Figure 16-2. The data is received on the RX/DT pin and drives the data recovery block. The data recovery block is actually a high-speed shifter operating at 16 times the baud rate, whereas the serial Receive Shift Register (RSR) operates at the bit rate. When all eight or nine bits of the character have been shifted in, they are immediately transferred to a two character First-In First-Out (FIFO) memory. The FIFO buffering allows reception of two complete characters and the start of a third character before software must start servicing the AUSART receiver. The FIFO and RSR registers are not directly accessible by software. Access to the received data is via the RCREG register.

# 16.1.2.1 Enabling the Receiver

The AUSART receiver is enabled for asynchronous operation by configuring the following three control bits:

- CREN = 1

- SYNC = 0

- SPEN = 1

All other AUSART control bits are assumed to be in their default state.

Setting the CREN bit of the RCSTA register enables the receiver circuitry of the AUSART. Clearing the SYNC bit of the TXSTA register configures the AUSART for asynchronous operation. Setting the SPEN bit of the RCSTA register enables the AUSART and automatically configures the RX/DT I/O pin as an input.

| Note: | When the SPEN bit is set the TX/CK I/O         |

|-------|------------------------------------------------|

|       | pin is automatically configured as an          |

|       | output, regardless of the state of the         |

|       | corresponding TRIS bit and whether or          |

|       | not the AUSART transmitter is enabled.         |

|       | The PORT latch is disconnected from the        |

|       | output driver so it is not possible to use the |

|       | TX/CK pin as a general purpose output.         |

# 16.1.2.2 Receiving Data

The receiver data recovery circuit initiates character reception on the falling edge of the first bit. The first bit, also known as the Start bit, is always a zero. The data recovery circuit counts one-half bit time to the center of the Start bit and verifies that the bit is still a zero. If it is not a zero then the data recovery circuit aborts character reception, without generating an error, and resumes looking for the falling edge of the Start bit. If the Start bit zero verification succeeds then the data recovery circuit counts a full bit time to the center of the next bit. The bit is then sampled by a majority detect circuit and the resulting '0' or '1' is shifted into the RSR. This repeats until all data bits have been sampled and shifted into the RSR. One final bit time is measured and the level sampled. This is the Stop bit, which is always a '1'. If the data recovery circuit samples a '0' in the Stop bit position then a framing error is set for this character, otherwise the framing error is cleared for this character. Refer to Section 16.1.2.4 "Receive Framing Error" for more information on framing errors.

Immediately after all data bits and the Stop bit have been received, the character in the RSR is transferred to the AUSART receive FIFO and the RCIF interrupt flag bit of the PIR1 register is set. The top character in the FIFO is transferred out of the FIFO by reading the RCREG register.

| Note: | If the receive FIFO is overrun, no additional characters will be received until the overrun |  |  |  |  |  |  |  |

|-------|---------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|       | condition is cleared. Refer to                                                              |  |  |  |  |  |  |  |

|       | Section 16.1.2.5 "Receive Overrun                                                           |  |  |  |  |  |  |  |

|       | Error" for more information on overrun                                                      |  |  |  |  |  |  |  |

|       | errors.                                                                                     |  |  |  |  |  |  |  |

# 16.1.2.3 Receive Interrupts

The RCIF interrupt flag bit of the PIR1 register is set whenever the AUSART receiver is enabled and there is an unread character in the receive FIFO. The RCIF interrupt flag bit is read-only, it cannot be set or cleared by software.

RCIF interrupts are enabled by setting all of the following bits:

- RCIE, Receive Interrupt Enable bit of the PIE1

register

- PEIE, Peripheral Interrupt Enable bit of the INTCON register

- GIE, Global Interrupt Enable bit of the INTCON register

The RCIF interrupt flag bit of the PIR1 register will be set when there is an unread character in the FIFO, regardless of the state of interrupt enable bits.

# 16.3.2 SYNCHRONOUS SLAVE MODE

The following bits are used to configure the AUSART for Synchronous slave operation:

- SYNC = 1

- CSRC = 0

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Clearing the CSRC bit of the TXSTA register configures the device as a slave. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the AUSART.

#### 16.3.2.1 AUSART Synchronous Slave Transmit

The operation of the Synchronous Master and Slave modes are identical (refer to **Section 16.3.1.2 "Synchronous Master Transmission")**, except in the case of the Sleep mode. If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- 1. The first character will immediately transfer to the TSR register and transmit.

- 2. The second word will remain in TXREG register.

- 3. The TXIF bit will not be set.

- After the first character has been shifted out of TSR, the TXREG register will transfer the second character to the TSR and the TXIF bit will now be set.

- If the PEIE and TXIE bits are set, the interrupt will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will call the Interrupt Service Routine.

- 16.3.2.2 Synchronous Slave Transmission Setup:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the CREN and SREN bits.

- If using interrupts, ensure that the GIE and PEIE bits of the INTCON register are set and set the TXIE bit.

- 4. If 9-bit transmission is desired, set the TX9 bit.

- 5. Enable transmission by setting the TXEN bit.

- 6. Verify address detection is disabled by clearing the ADDEN bit of the RCSTA register.

- 7. If 9-bit transmission is selected, insert the Most Significant bit into the TX9D bit.

- 8. Start transmission by writing the Least Significant eight bits to the TXREG register.

| Name   | Bit 7                           | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|---------------------------------|--------|--------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE                             | PEIE   | TOIE   | INTE   | RBIE   | T0IF   | INTF   | RBIF   | 0000 000x            | 0000 000x                       |

| PIE1   | TMR1GIE                         | ADIE   | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| PIR1   | TMR1GIF                         | ADIF   | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| RCSTA  | SPEN                            | RX9    | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 0000 000X            | 0000 000x                       |

| TRISC  | TRISC7                          | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 1111 1111            | 1111 1111                       |

| TXREG  | G AUSART Transmit Data Register |        |        |        |        |        |        |        | 0000 0000            | 0000 0000                       |

| TXSTA  | CSRC                            | TX9    | TXEN   | SYNC   | _      | BRGH   | TRMT   | TX9D   | 0000 -010            | 0000 -010                       |

### TABLE 16-8: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for synchronous slave transmission.

# 17.1.2 SLAVE MODE

For any SPI device acting as a slave, the data is transmitted and received as external clock pulses appear on SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

## 17.1.2.1 Slave Mode Operation

The SSP consists of a transmit/receive shift register (SSPSR) and a buffer register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR until the received data is ready.

The slave has no control as to when data will be clocked in or out of the device. All data that is to be transmitted, to a master or another slave, must be loaded into the SSPBUF register before the first clock pulse is received.

Once eight bits of data have been received:

- · Received byte is moved to the SSPBUF register

- BF bit of the SSPSTAT register is set

- SSPIF bit of the PIR1 register is set

Any write to the SSPBUF register during transmission/ reception of data will be ignored and the Write Collision Detect bit, WCOL of the SSPCON register, will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPBUF register completed successfully.

The user's firmware must read SSPBUF, clearing the BF flag, or the SSPOV bit of the SSPCON register will be set with the reception of the next byte and communication will be disabled.

A SPI module transmits and receives at the same time, occasionally causing dummy data to be transmitted/ received. It is up to the user to determine which data is to be used and what can be discarded.

# 17.1.2.2 Enabling Slave I/O

To enable the serial port, the SSPEN bit of the SSPCON register must be set. If a Slave mode of operation is selected in the SSPM bits of the SSPCON register, the SDI, SDO and SCK pins will be assigned as serial port pins.

For these pins to function as serial port pins, they must have their corresponding data direction bits set or cleared in the associated TRIS register as follows:

- · SDI configured as input

- · SDO configured as output

- · SCK configured as input

Optionally, a fourth pin, Slave Select  $(\overline{SS})$  may be used in Slave mode. Slave Select may be configured to operate on one of the following pins via the SSSEL bit in the APFCON register.

- RA5/AN4/SS

- RA0/AN0/SS

Upon selection of a Slave Select pin, the appropriate bits must be set in the ANSELA and TRISA registers. Slave Select must be set as an input by setting the corresponding bit in TRISA, and digital I/O must be enabled on the SS pin by clearing the corresponding bit of the ANSELA register.

### 17.1.2.3 Slave Mode Setup

When initializing the SSP module to SPI Slave mode, compatibility must be ensured with the master device. This is done by programming the appropriate control bits of the SSPCON and SSPSTAT registers. These control bits allow the following to be specified:

- · SCK as clock input

- Idle state of SCK (CKP bit)

- Data input sample phase (SMP bit)

- Output data on rising/falling edge of SCK (CKE bit)

Figure 17-4 and Figure 17-5 show example waveforms of Slave mode operation.

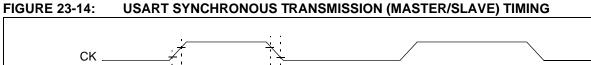

# TABLE 23-9: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |          |                                   |          |      |       |            |  |  |  |

|----------------------------------------------------------------------------------------------------------------------|----------|-----------------------------------|----------|------|-------|------------|--|--|--|

| Param.<br>No.                                                                                                        | Symbol   | Characteristic                    | Min.     | Max. | Units | Conditions |  |  |  |

| US120                                                                                                                | ТскН2ртV | SYNC XMIT (Master and Slave)      | 3.0-5.5V |      | 80    | ns         |  |  |  |

|                                                                                                                      |          | Clock high to data-out valid      | 1.8-5.5V |      | 100   | ns         |  |  |  |

| US121                                                                                                                | TCKRF    | Clock out rise time and fall time | 3.0-5.5V |      | 45    | ns         |  |  |  |

|                                                                                                                      |          | (Master mode)                     | 1.8-5.5V | —    | 50    | ns         |  |  |  |

| US122                                                                                                                | TDTRF    | Data-out rise time and fall time  | 3.0-5.5V | —    | 45    | ns         |  |  |  |

|                                                                                                                      |          |                                   | 1.8-5.5V | —    | 50    | ns         |  |  |  |

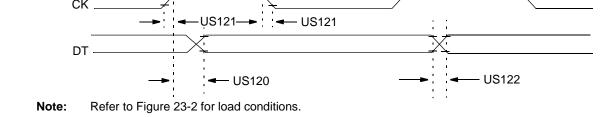

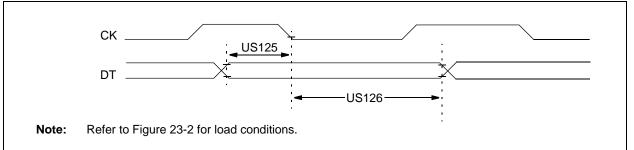

# FIGURE 23-15: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

# TABLE 23-10: USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |          |                                                                                |      |      |       |            |  |  |

|----------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------------|------|------|-------|------------|--|--|

| Param.<br>No.                                                                                                        | Symbol   | Characteristic                                                                 | Min. | Max. | Units | Conditions |  |  |

| US125                                                                                                                | TDTV2CKL | SYNC RCV (Master and Slave)<br>Data-hold before CK $\downarrow$ (DT hold time) | 10   |      | ns    |            |  |  |

| US126                                                                                                                | TCKL2DTL | Data-hold after CK $\downarrow$ (DT hold time)                                 | 15   | _    | ns    |            |  |  |

| Param.<br>No. | Symbol  | Charact               | eristic      | Min.          | Max. | Units | Conditions                                  |

|---------------|---------|-----------------------|--------------|---------------|------|-------|---------------------------------------------|

| SP100*        | Тнідн   | Clock high time       | 100 kHz mode | 4.0           | —    | μS    | Device must operate at a minimum of 1.5 MHz |

|               |         |                       | 400 kHz mode | 0.6           | _    | μS    | Device must operate at a minimum of 10 MHz  |

|               |         |                       | SSP Module   | 1.5Tcy        | —    |       |                                             |

| SP101*        | TLOW    | Clock low time        | 100 kHz mode | 4.7           | -    | μS    | Device must operate at a minimum of 1.5 MHz |

|               |         |                       | 400 kHz mode | 1.3           | -    | μS    | Device must operate at a minimum of 10 MHz  |

|               |         |                       | SSP Module   | 1.5Tcy        | —    |       |                                             |

| SP102*        | TR      | SDA and SCL rise time | 100 kHz mode | —             | 1000 | ns    |                                             |

|               |         |                       | 400 kHz mode | 20 +<br>0.1Св | 300  | ns    | CB is specified to be from 10-400 pF        |

| SP103*        | TF      | SDA and SCL fall      | 100 kHz mode | —             | 250  | ns    |                                             |

|               |         | time                  | 400 kHz mode | 20 +<br>0.1Св | 250  | ns    | CB is specified to be from 10-400 pF        |

| SP106*        | THD:DAT | Data input hold       | 100 kHz mode | 0             | _    | ns    |                                             |

|               |         | time                  | 400 kHz mode | 0             | 0.9  | μs    |                                             |

| SP107*        | TSU:DAT | Data input setup      | 100 kHz mode | 250           | _    | ns    | (Note 2)                                    |

|               |         | time                  | 400 kHz mode | 100           | —    | ns    |                                             |

| SP109*        | ΤΑΑ     | Output valid from     | 100 kHz mode | —             | 3500 | ns    | (Note 1)                                    |

|               |         | clock                 | 400 kHz mode | —             | _    | ns    |                                             |

| SP110*        | TBUF    | Bus free time         | 100 kHz mode | 4.7           | _    | μs    | Time the bus must be free                   |

|               |         |                       | 400 kHz mode | 1.3           | —    | μS    | before a new transmis-<br>sion can start    |

| SP111         | Св      | Bus capacitive loadi  | ing          | _             | 400  | pF    |                                             |

# TABLE 23-13: I<sup>2</sup>C BUS DATA REQUIREMENTS

\* These parameters are characterized but not tested.

**Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of Start or Stop conditions.

**2:** A Fast mode (400 kHz)  $I^2C$  bus device can be used in a Standard mode (100 kHz)  $I^2C$  bus system, but the requirement TsU:DAT  $\ge$  250 ns must then be met. This will automatically be the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the low period of the SCL signal, it must output the next data bit to the SDA line TR max. + TSU:DAT = 1000 + 250 = 1250 ns (according to the Standard mode  $I^2C$  bus specification), before the SCL line is released.

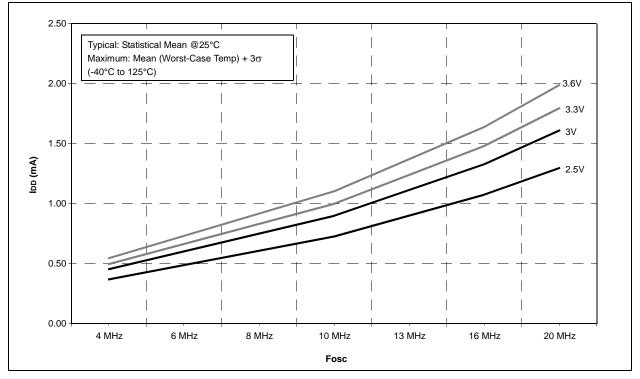

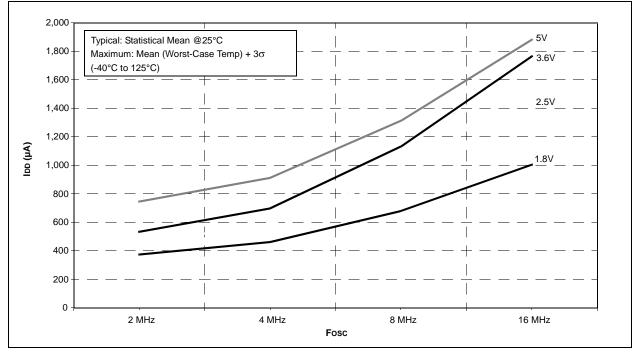

#### FIGURE 24-12: PIC16LF722A/723A TYPICAL IDD vs. Fosc OVER VDD, HS MODE

#### FIGURE 24-20: PIC16LF722A/723A MAXIMUM IDD vs. Fosc OVER VDD, INTOSC MODE

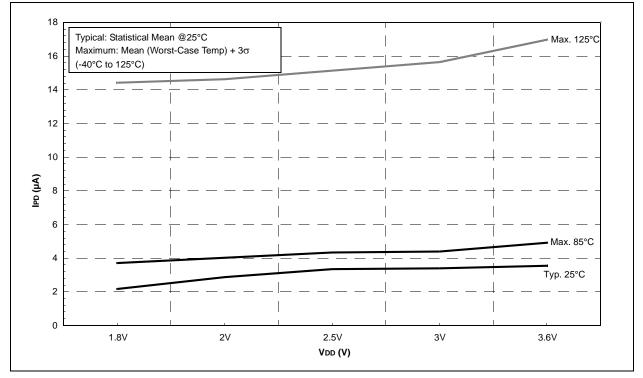

FIGURE 24-21: PIC16F722A/723A MAXIMUM IDD vs. Fosc OVER VDD, INTOSC MODE, VCAP = 0.1µF

# PIC16(L)F722A/723A

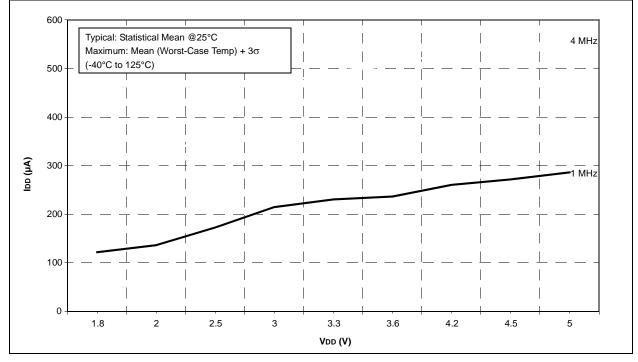

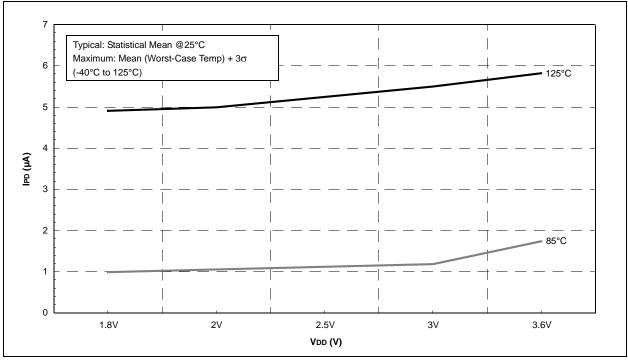

# FIGURE 24-28: PIC16LF722A/723A MAXIMUM BASE IPD vs. VDD

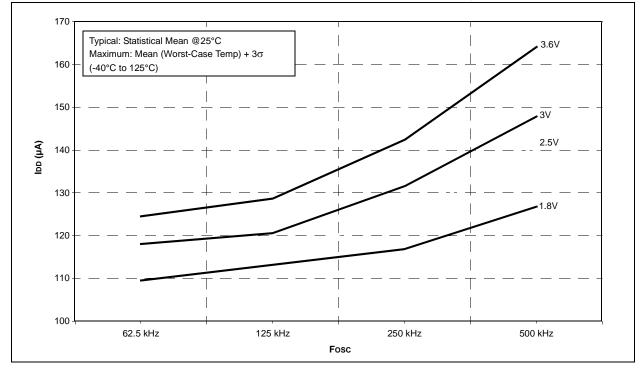

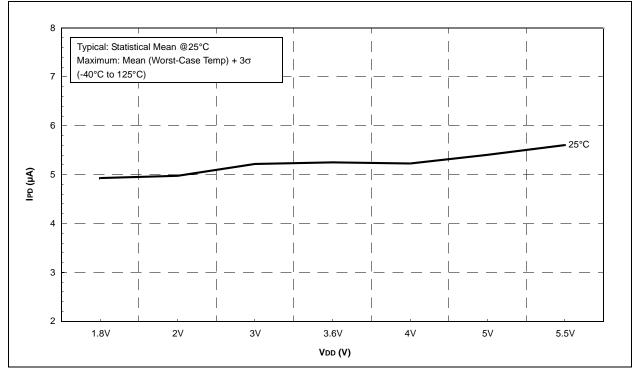

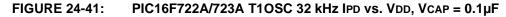

# FIGURE 24-40: PIC16LF722A/723A CAP SENSE LOW POWER IPD vs. VDD

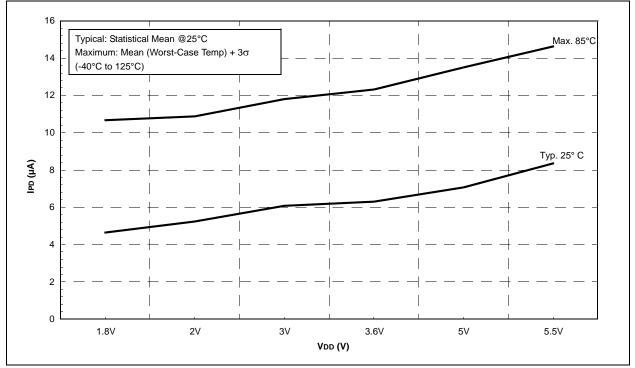

# 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units     |          | MILLIMETERS |      |  |  |

|------------------------|-----------|----------|-------------|------|--|--|

| Dimensio               | on Limits | MIN      | NOM         | MAX  |  |  |

| Number of Pins         | Ν         |          | 28          |      |  |  |

| Pitch                  | е         |          | 0.65 BSC    |      |  |  |

| Overall Height         | Α         | 0.80     | 0.90        | 1.00 |  |  |

| Standoff               | A1        | 0.00     | 0.02        | 0.05 |  |  |

| Contact Thickness      | A3        | 0.20 REF |             |      |  |  |

| Overall Width          | Е         |          | 6.00 BSC    |      |  |  |

| Exposed Pad Width      | E2        | 3.65     | 3.70        | 4.20 |  |  |

| Overall Length         | D         | 6.00 BSC |             |      |  |  |

| Exposed Pad Length     | D2        | 3.65     | 3.70        | 4.20 |  |  |

| Contact Width          | b         | 0.23     | 0.30        | 0.35 |  |  |

| Contact Length         | L         | 0.50     | 0.55        | 0.70 |  |  |

| Contact-to-Exposed Pad | К         | 0.20     | _           | _    |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-105B

# THE MICROCHIP WEBSITE

Microchip provides online support via our website at www.microchip.com. This website is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the website contains the following information:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Micro-chip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip website at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

# **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the website at: http://www.microchip.com/support