Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 11x8b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f722at-i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1.0   | Device Overview                                                              | 7    |

|-------|------------------------------------------------------------------------------|------|

| 2.0   | Memory Organization                                                          | . 11 |

| 3.0   | Resets                                                                       | . 23 |

| 4.0   | Interrupts                                                                   | . 33 |

| 5.0   | Low Dropout (LDO) Voltage Regulator                                          | . 41 |

| 6.0   | I/O Ports                                                                    | . 42 |

| 7.0   | Oscillator Module                                                            | . 71 |

| 8.0   | Device Configuration                                                         | 77   |

| 9.0   | Analog-to-Digital Converter (ADC) Module                                     | . 80 |

| 10.0  | Fixed Voltage Reference                                                      | . 90 |

| 11.0  | Timer0 Module                                                                | . 91 |

| 12.0  | Timer1 Module with Gate Control                                              | 103  |

| 13.0  | Timer2 Module                                                                | 115  |

| 14.0  | Capacitive Sensing Module                                                    | 108  |

| 15.0  | Capture/Compare/PWM (CCP) Module                                             | 114  |

| 16.0  | Addressable Universal Synchronous Asynchronous Receiver Transmitter (AUSART) | 124  |

| 17.0  |                                                                              |      |

| 18.0  | Program Memory Read                                                          | 167  |

| 19.0  | Power-Down Mode (Sleep)                                                      | 170  |

| 20.0  | In-Circuit Serial Programming™ (ICSP™)                                       | 172  |

| 21.0  | Instruction Set Summary                                                      | 173  |

| 22.0  | Development Support                                                          | 182  |

| 23.0  | Electrical Specifications                                                    | 186  |

| 24.0  |                                                                              |      |

| 25.0  | Packaging Information                                                        | 249  |

| Appe  | ndix A: Data Sheet Revision History                                          | 261  |

| Appe  | ndix B: Migrating From Other PIC <sup>®</sup> Devices                        | 261  |

| The I | Nicrochip Website                                                            | 262  |

| Cust  | omer Change Notification Service                                             | 262  |

| Cust  | omer Support                                                                 | 262  |

| Prod  | uct Identification System                                                    | 263  |

| Address                | Name       | Bit 7        | Bit 6         | Bit 5         | Bit 4         | Bit 3         | Bit 2           | Bit 1         | Bit 0    | Value on:<br>POR, BOR | Page   |

|------------------------|------------|--------------|---------------|---------------|---------------|---------------|-----------------|---------------|----------|-----------------------|--------|

| Bank 2                 |            |              |               |               |               |               |                 |               |          |                       |        |

| 100h <sup>(2)</sup>    | INDF       | Addressing   | this location | uses conter   | nts of FSR to | address data  | a memory (not   | a physical r  | egister) | xxxx xxxx             | 22,30  |

| 101h                   | TMR0       | Timer0 Mod   | lule Register |               |               |               |                 |               |          | xxxx xxxx             | 91,30  |

| 102h <sup>(2)</sup>    | PCL        | Program Co   | ounter's (PC) | Least Signi   | ificant Byte  |               |                 |               |          | 0000 0000             | 21,30  |

| 103h <sup>(2)</sup>    | STATUS     | IRP          | RP1           | RP0           | TO            | PD            | Z               | DC            | С        | 0001 1xxx             | 18,30  |

| 104h <sup>(2)</sup>    | FSR        | Indirect Dat | a Memory A    | ddress Point  | ter           | •             | •               |               |          | xxxx xxxx             | 22,30  |

| 105h                   | —          | Unimpleme    | nted          |               |               |               |                 |               |          | _                     | _      |

| 106h                   | —          | Unimpleme    | nted          |               |               |               |                 |               |          | _                     | _      |

| 107h                   | —          | Unimpleme    | nted          |               |               |               |                 |               |          | _                     | _      |

| 108h                   | CPSCON0    | CPSON        | _             | _             | _             | CPSRNG1       | CPSRNG0         | CPSOUT        | TOXCS    | 0 0000                | 112,31 |

| 109h                   | CPSCON1    | _            | _             | _             | _             | _             | CPSCH2          | CPSCH1        | CPSCH0   | 0000                  | 113,31 |

| 10Ah <sup>(1, 2)</sup> | PCLATH     | —            | —             | —             | Write Buffer  | for the upper | r 5 bits of the | Program Cou   | unter    | 0 0000                | 21,30  |

| 10Bh <sup>(2)</sup>    | INTCON     | GIE          | PEIE          | TOIE          | INTE          | RBIE          | T0IF            | INTF          | RBIF     | 0000 000x             | 36,30  |

| 10Ch                   | PMDATL     | Program Me   | emory Read    | Data Regist   | er Low Byte   |               |                 |               |          | xxxx xxxx             | 167,31 |

| 10Dh                   | PMADRL     | Program Me   | emory Read    | Address Re    | gister Low By | /te           |                 |               |          | xxxx xxxx             | 167,31 |

| 10Eh                   | PMDATH     | _            | _             | Program M     | emory Read    | Data Registe  | r High Byte     |               |          | xx xxxx               | 167,31 |

| 10Fh                   | PMADRH     | _            | _             | _             | Program Me    | mory Read A   | Address Regis   | ter High Byte | e        | x xxxx                | 167,31 |

| Bank 3                 |            | •            |               | •             | •             |               |                 |               |          | •                     |        |

| 180h <sup>(2)</sup>    | INDF       | Addressing   | this location | uses conter   | nts of FSR to | address data  | a memory (not   | a physical r  | egister) | xxxx xxxx             | 22,30  |

| 181h                   | OPTION_REG | RBPU         | INTEDG        | TOCS          | TOSE          | PSA           | PS2             | PS1           | PS0      | 1111 1111             | 19,30  |

| 182h <sup>(2)</sup>    | PCL        | Program Co   | ounter (PC) L | east Signific | cant Byte     | •             | •               |               |          | 0000 0000             | 21,30  |

| 183h <sup>(2)</sup>    | STATUS     | IRP          | RP1           | RP0           | TO            | PD            | Z               | DC            | С        | 0001 1xxx             | 18,30  |

| 184h <sup>(2)</sup>    | FSR        | Indirect Dat | a Memory A    | ddress Point  | ter           |               |                 |               |          | xxxx xxxx             | 22,30  |

| 185h                   | ANSELA     | —            | _             | ANSA5         | ANSA4         | ANSA3         | ANSA2           | ANSA1         | ANSA0    | 11 1111               | 44,31  |

| 186h                   | ANSELB     | —            | _             | ANSB5         | ANSB4         | ANSB3         | ANSB2           | ANSB1         | ANSB0    | 11 1111               | 53,31  |

| 187h                   | —          | Unimpleme    | nted          |               |               |               |                 |               |          | —                     | _      |

| 18Ah <sup>(1, 2)</sup> | PCLATH     | _            | _             | _             | Write Buffer  | for the upper | r 5 bits of the | Program Cou   | unter    | 0 0000                | 21,30  |

| 18Bh <sup>(2)</sup>    | INTCON     | GIE          | PEIE          | TOIE          | INTE          | RBIE          | T0IF            | INTF          | RBIF     | 0000 000x             | 36,30  |

| 18Ch                   | PMCON1     | Reserved     | —             | —             | —             | _             | —               | —             | RD       | 10                    | 168,31 |

| 18Dh                   | —          | Unimpleme    | nted          |               |               |               |                 |               |          | —                     | _      |

| 18Eh                   | _          | Unimpleme    | nted          |               |               |               |                 |               |          | —                     | —      |

| 18Fh                   | —          | Unimpleme    | nted          |               |               |               |                 |               |          | _                     | —      |

## TABLE 2-1: PIC16(L)F722A/723A SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

**Legend:** x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter.

2: These registers can be addressed from any bank.

**3:** Accessible only when SSPM<3:0 > = 1001.

4: Accessible only when SSPM<3:0>  $\neq$  1001.

5: This bit is always '1' as RE3 is input-only.

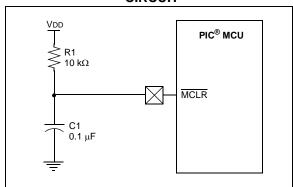

## 3.1 MCLR

The PIC16(L)F722A/723A has a noise filter in the  $\overline{\text{MCLR}}$  Reset path. The filter will detect and ignore small pulses.

It should be noted that a Reset does not drive the MCLR pin low.

Voltages applied to the pin that exceed its specification can result in both MCLR Resets and excessive current beyond the device specification during the ESD event. For this reason, Microchip recommends that the MCLR pin no longer be tied directly to VDD. The use of an RC network, as shown in Figure 3-2, is suggested.

An internal  $\overline{\text{MCLR}}$  option is enabled by clearing the MCLRE bit in the Configuration Word register. When MCLRE = 0, the Reset signal to the chip is generated internally. When the MCLRE = 1, the RE3/MCLR pin becomes an external Reset input. In this mode, the RE3/MCLR pin has a weak pull up to VDD. In-Circuit Serial Programming is not affected by selecting the internal  $\overline{\text{MCLR}}$  option.

#### FIGURE 3-2: RECOMMENDED MCLR CIRCUIT

## 3.2 Power-on Reset (POR)

The on-chip POR circuit holds the chip in Reset until VDD has reached a high enough level for proper operation. A maximum rise time for VDD is required. See **Section 23.0 "Electrical Specifications"** for details. If the BOR is enabled, the maximum rise time specification does not apply. The BOR circuitry will keep the device in Reset until VDD reaches VBOR (see **Section 3.5** "**Brown-Out Reset (BOR)**").

When the device starts normal operation (exits the Reset condition), device operating parameters (i.e., voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

For additional information, refer to Application Note *AN607, Power-up Trouble Shooting* (DS00607).

## 3.3 Power-up Timer (PWRT)

The Power-up Timer provides a fixed 64 ms (nominal) time-out on power-up only, from POR or Brown-out Reset. The Power-up Timer operates from the WDT oscillator. For more information, see **Section 7.3** "Internal Clock Modes". The chip is kept in Reset as long as PWRT is active. The PWRT delay allows the VDD to rise to an acceptable level. A Configuration bit, PWRTE, can disable (if set) or enable (if cleared or programmed) the Power-up Timer. The Power-up Timer should be enabled when Brown-out Reset is enabled, although it is not required.

The Power-up Timer delay will vary from chip-to-chip and vary due to:

- VDD variation

- Temperature variation

- · Process variation

See DC parameters for details (Section 23.0 "Electrical Specifications").

Note: The Power-up Timer is enabled by the PWRTE bit in the Configuration Word.

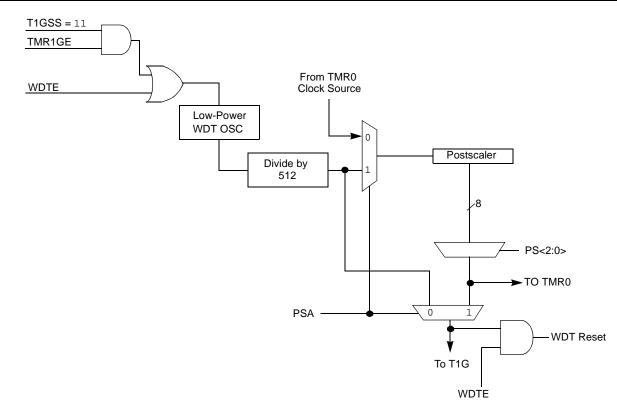

## 3.4 Watchdog Timer (WDT)

The WDT has the following features:

- Shares an 8-bit prescaler with Timer0

- Time-out period is from 17 ms to 2.2 seconds, nominal

- Enabled by a Configuration bit

WDT is cleared under certain conditions described in Table 3-1.

### 3.4.1 WDT OSCILLATOR

The WDT derives its time base from 31 kHz internal oscillator.

Note: When the Oscillator Start-up Timer (OST) is invoked, the WDT is held in Reset, because the WDT Ripple Counter is used by the OST to perform the oscillator delay count. When the OST count has expired, the WDT will begin counting (if enabled).

### 3.4.2 WDT CONTROL

The WDTE bit is located in the Configuration Word Register 1. When set, the WDT runs continuously.

The PSA and PS<2:0> bits of the OPTION register control the WDT period. See **Section 11.0 "Timer0 Module"** for more information.

#### TABLE 3-1: WDT STATUS

| Conditions                                               | WDT                          |

|----------------------------------------------------------|------------------------------|

| WDTE = 0                                                 | Cleared                      |

| CLRWDT Command                                           |                              |

| Exit Sleep + System Clock = T1OSC, EXTRC, INTOSC, EXTCLK |                              |

| Exit Sleep + System Clock = XT, HS, LP                   | Cleared until the end of OST |

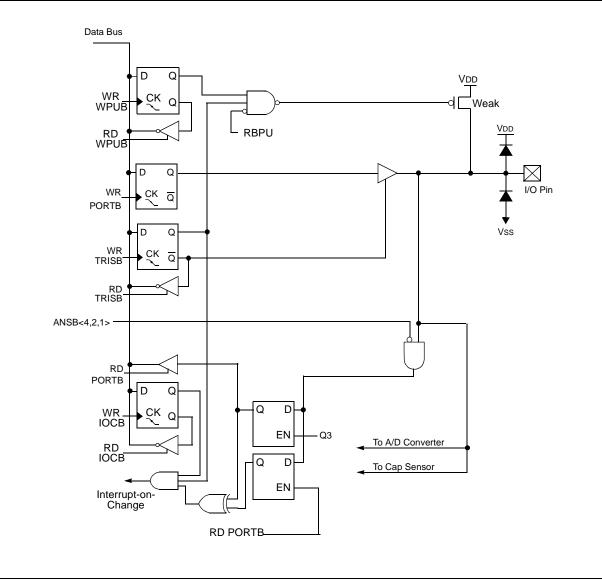

### 6.2.1 ANSELA REGISTER

The ANSELA register (Register 6-4) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELA bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELA bits has no affect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

### REGISTER 6-4: ANSELA: PORTA ANALOG SELECT REGISTER

'1' = Bit is set

| U-0                               | U-0 | R/W-1 | R/W-1 | R/W-1        | R/W-1            | R/W-1    | R/W-1 |

|-----------------------------------|-----|-------|-------|--------------|------------------|----------|-------|

| —                                 | —   | ANSA5 | ANSA4 | ANSA3        | ANSA2            | ANSA1    | ANSA0 |

| bit 7                             |     |       |       |              |                  |          | bit 0 |

|                                   |     |       |       |              |                  |          |       |

| Legend:                           |     |       |       |              |                  |          |       |

| R = Readable bit W = Writable bit |     |       | bit   | U = Unimpler | mented bit, read | l as '0' |       |

'0' = Bit is cleared

bit 7-6 Unimplemented: Read as '0'

-n = Value at POR

bit 5-0 **ANSA<5:0>**: Analog Select between Analog or Digital Function on pins RA<5:0>, respectively 0 = Digital I/O. Pin is assigned to port or digital special function. 1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

x = Bit is unknown

| R/W-x                          | R/W-x | R/W-x        | R/W-x | R/W-x        | R/W-x            | R/W-x  | R/W-x |

|--------------------------------|-------|--------------|-------|--------------|------------------|--------|-------|

| RB7                            | RB6   | RB5          | RB4   | RB3          | RB2              | RB1    | RB0   |

| bit 7                          |       |              |       |              |                  |        | bit 0 |

|                                |       |              |       |              |                  |        |       |

|                                |       |              |       |              |                  |        |       |

| Legend:                        |       |              |       |              |                  |        |       |

| <b>Legend:</b><br>R = Readable | bit   | W = Writable | bit   | U = Unimplen | nented bit, read | as '0' |       |

### REGISTER 6-5: PORTB: PORTB REGISTER

bit 7-0 RB<7:0>: PORTB I/O Pin bits

1 = Port pin is > VIH

0 = Port pin is < VIL

#### REGISTER 6-6: TRISB: PORTB TRI-STATE REGISTER

| R/W-1  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 7-0

**—**

TRISB<7:0>: PORTB Tri-State Control bits

1 = PORTB pin configured as an input (tri-stated)

0 = PORTB pin configured as an output

#### REGISTER 6-7: WPUB: WEAK PULL-UP PORTB REGISTER

| R/W-1 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| WPUB7 | WPUB6 | WPUB5 | WPUB4 | WPUB3 | WPUB2 | WPUB1 | WPUB0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 **WPUB<7:0>**: Weak Pull-up Register bits

1 = Pull up enabled

0 = Pull up disabled

**Note 1:** Global RBPU bit of the OPTION register must be cleared for individual pull ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is in configured as an output.

## 7.2 Clock Source Modes

Clock source modes can be classified as external or internal.

- Internal clock source (INTOSC) is contained within the oscillator module and derived from a 500 kHz high precision oscillator. The oscillator module has eight selectable output frequencies, with a maximum internal frequency of 16 MHz.

- External clock modes rely on external circuitry for the clock source. Examples are: oscillator modules (EC mode), quartz crystal resonators or ceramic resonators (LP, XT and HS modes) and Resistor-Capacitor (RC) mode circuits.

The system clock can be selected between external or internal clock sources via the FOSC bits of the Configuration Word 1.

## 7.3 Internal Clock Modes

The oscillator module has eight output frequencies derived from a 500 kHz high precision oscillator. The IRCF bits of the OSCCON register select the postscaler applied to the clock source dividing the frequency by 1, 2, 4 or 8. Setting the PLLEN bit of the Configuration Word 1 locks the internal clock source to 16 MHz before the postscaler is selected by the IRCF bits. The PLLEN bit must be set or cleared at the time of programming; therefore, only the upper or low four clock source frequencies are selectable in software.

## 7.3.1 INTOSC AND INTOSCIO MODES

The INTOSC and INTOSCIO modes configure the internal oscillators as the system clock source when the device is programmed using the oscillator selection or the FOSC<2:0> bits in the CONFIG1 register. See **Section 8.0** "**Device Configuration**" for more information.

In INTOSC mode, OSC1/CLKIN is available for general purpose I/O. OSC2/CLKOUT outputs the selected internal oscillator frequency divided by 4. The CLKOUT signal may be used to provide a clock for external circuitry, synchronization, calibration, test or other application requirements.

In INTOSCIO mode, OSC1/CLKIN and OSC2/ CLKOUT are available for general purpose I/O.

## 7.3.2 FREQUENCY SELECT BITS (IRCF)

The output of the 500 kHz INTOSC and 16 MHz INTOSC, with Phase-Locked Loop enabled, connect to a postscaler and multiplexer (see Figure 7-1). The Internal Oscillator Frequency Select bits (IRCF) of the OSCCON register select the frequency output of the internal oscillator. Depending upon the PLLEN bit, one of four frequencies of two frequency sets can be selected via software:

If PLLEN = 1, frequency selection is as follows:

- 16 MHz

- 8 MHz (Default after Reset)

- 4 MHz

- 2 MHz

- If PLLEN = 0, frequency selection is as follows:

- 500 kHz

- 250 kHz (Default after Reset)

- 125 kHz

- 62.5 kHz

- Note: Following any Reset, the IRCF<1:0> bits of the OSCCON register are set to '10' and the frequency selection is set to 8 MHz or 250 kHz. The user can modify the IRCF bits to select a different frequency.

There is no start-up delay before a new frequency selected in the IRCF bits takes effect. This is because the old and new frequencies are derived from INTOSC via the postscaler and multiplexer.

Start-up delay specifications are located in Table 23-2 in Section 23.0 "Electrical Specifications".

## 7.5 Oscillator Tuning

The INTOSC is factory-calibrated but can be adjusted in software by writing to the OSCTUNE register (Register 7-2).

The default value of the OSCTUNE register is '0'. The value is a 6-bit two's complement number.

When the OSCTUNE register is modified, the INTOSC frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred.

#### REGISTER 7-2: OSCTUNE: OSCILLATOR TUNING REGISTER

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     |     | TUN5  | TUN4  | TUN3  | TUN2  | TUN1  | TUN0  |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 7-6 Unimplemented: Read as '0'

bit 5-0

### REGISTER 8-1: CONFIG1: CONFIGURATION WORD REGISTER 1 (CONTINUED)

bit 2-0

FOSC<2:0>: Oscillator Selection bits

111 = RC oscillator: CLKOUT function on RA6/OSC2/CLKOUT pin, RC on RA7/OSC1/CLKIN

110 = RCIO oscillator: I/O function on RA6/OSC2/CLKOUT pin, RC on RA7/OSC1/CLKIN

101 = INTOSC oscillator: CLKOUT function on RA6/OSC2/CLKOUT pin, I/O function on RA7/OSC1/CLKIN

- 100 = INTOSCIO oscillator: I/O function on RA6/OSC2/CLKOUT pin, I/O function on RA7/OSC1/CLKIN

- 011 = EC: I/O function on RA6/OSC2/CLKOUT pin, CLKIN on RA7/OSC1/CLKIN

- 010 = HS oscillator: High-speed crystal/resonator on RA6/OSC2/CLKOUT and RA7/OSC1/CLKIN

- 001 = XT oscillator: Crystal/resonator on RA6/OSC2/CLKOUT and RA7/OSC1/CLKIN

- 000 = LP oscillator: Low-power crystal on RA6/OSC2/CLKOUT and RA7/OSC1/CLKIN

**Note 1:** Enabling Brown-out Reset does not automatically enable Power-up Timer.

- 2: The entire program memory will be erased when the code protection is turned off.

- 3: When MCLR is asserted in INTOSC or RC mode, the internal clock oscillator is disabled.

- 4: MPLAB<sup>®</sup> X IDE masks unimplemented Configuration bits to '0'.

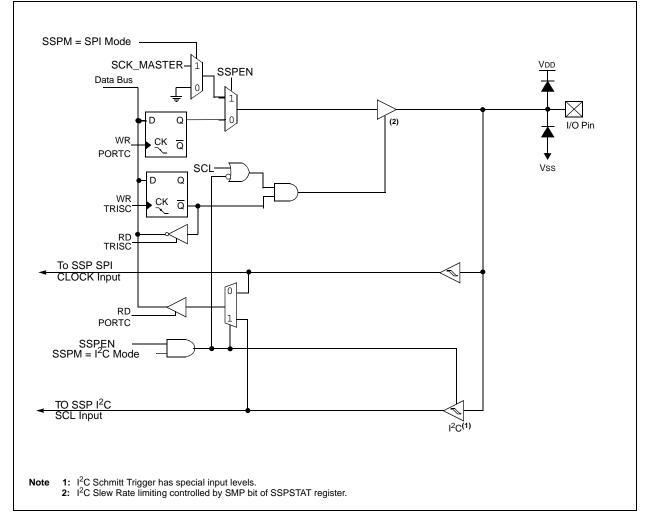

#### REGISTER 8-2: CONFIG2: CONFIGURATION WORD REGISTER 2

| Legend:           | P = Programmable bit |                                    |                    |  |  |  |

|-------------------|----------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 13-6 Unimplemented: Read as '1'

| bit 5-4 | VCAPEN<1:0>: Voltage Regulator Capacitor Enable bits<br>For the PIC16LF722A/723A: |

|---------|-----------------------------------------------------------------------------------|

|         | These bits are ignored. All VCAP pin functions are disabled.                      |

|         | For the PIC16F722A/723A:                                                          |

|         | 00 = VCAP functionality is enabled on RA0                                         |

|         | 01 = VCAP functionality is enabled on RA5                                         |

|         | 10 = VCAP functionality is enabled on RA6                                         |

|         | 11 = All VCAP functions are disabled (not recommended)                            |

| bit 3-0 | Unimplemented: Read as '1'                                                        |

Note 1: MPLAB<sup>®</sup> X IDE masks unimplemented Configuration bits to '0'.

## 9.3 A/D Acquisition Requirements

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 9-3. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), refer to Figure 9-3. The maximum recommended impedance for analog sources is 10 k $\Omega$ . As the source

impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an A/D acquisition must be done before the conversion can be started. To calculate the minimum acquisition time, Equation 9-1 may be used. This equation assumes that 1/2 LSb error is used (256 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

## EQUATION 9-1: ACQUISITION TIME EXAMPLE

Assumptions: Temperature =

$$50^{\circ}C$$

and external impedance of  $10k\Omega 5.0V VDD$

$TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient$

$= TAMP + TC + TCOFF$

$= 2\mu s + TC + [(Temperature - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$

The value for TC can be approximated with the following equations:

*The value for TC can be approximated with the following equations:*

$$V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - 1}\right) = V_{CHOLD} ; [1] V_{CHOLD} charged to within 1/2 lsb$$

$$V_{APPLIED}\left(1 - e^{\frac{-TC}{RC}}\right) = V_{CHOLD} ; [2] V_{CHOLD} charge response to V_{APPLIED} V_{APPLIED}\left(1 - e^{\frac{-TC}{RC}}\right) = V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - 1}\right) ; combining [1] and [2]$$

*Note:* Where n = number of bits of the ADC.

Solving for TC:

$$Tc = -CHOLD(RIC + RSS + RS) \ln(1/511)$$

=  $-10pF(1k\Omega + 7k\Omega + 10k\Omega) \ln(0.001957)$

=  $1.12\mu s$

Therefore:

$$TACQ = 2\mu s + 1.12\mu s + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

= 4.42\mu s

**Note 1:** The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is  $10 \text{ k}\Omega$ . This is required to meet the pin leakage specification.

| Name    | Bit 7       | a 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2 |              | Bit 1        | Bit 0          | Register<br>on Page |        |        |     |  |  |

|---------|-------------|---------------------------------------------------------------------------|--------------|--------------|----------------|---------------------|--------|--------|-----|--|--|

| ANSELB  | —           | —                                                                         | ANSB5        | ANSB4        | ANSB3          | ANSB2               | ANSB1  | ANSB0  | 53  |  |  |

| CCP1CON | —           | _                                                                         | DC1B1        | DC1B0        | CCP1M3         | CCP1M2              | CCP1M1 | CCP1M0 | 115 |  |  |

| CCP2CON | —           | —                                                                         | DC2B1        | DC2B0        | CCP2M3         | CCP2M2              | CCP2M1 | CCP2M0 | 115 |  |  |

| INTCON  | GIE         | PEIE                                                                      | T0IE         | INTE         | RBIE           | T0IF                | INTF   | RBIF   | 36  |  |  |

| PIE1    | TMR1GIE     | ADIE                                                                      | RCIE         | TXIE         | SSPIE          | CCP1IE              | TMR2IE | TMR1IE | 37  |  |  |

| PIR1    | TMR1GIF     | ADIF                                                                      | RCIF         | TXIF         | SSPIF          | CCP1IF              | TMR2IF | TMR1IF | 39  |  |  |

| PORTB   | RB7         | RB6                                                                       | RB5          | RB4          | RB3            | RB2                 | RB1    | RB0    | 52  |  |  |

| TMR1H   | Holding Reg | ister for the                                                             | Most Signifi | cant Byte of | the 16-bit T   | MR1 Regis           | ter    |        | 99  |  |  |

| TMR1L   | Holding Reg | ister for the                                                             | Least Signif | icant Byte o | f the 16-bit 7 | MR1 Regis           | ster   |        | 99  |  |  |

| TRISB   | TRISB7      | TRISB6                                                                    | TRISB5       | TRISB4       | TRISB3         | TRISB2              | TRISB1 | TRISB0 | 52  |  |  |

| TRISC   | TRISC7      | TRISC6                                                                    | TRISC5       | TRISC4       | TRISC3         | TRISC2              | TRISC1 | TRISC0 | 62  |  |  |

| T1CON   | TMR1CS1     | TMR1CS0                                                                   | T1CKPS1      | T1CKPS0      | T1OSCEN        | T1SYNC              | _      | TMR10N | 103 |  |  |

| T1GCON  | TMR1GE      | T1GPOL                                                                    | T1GTM        | T1GSPM       | T1GGO/<br>DONE | T1GVAL              | T1GSS1 | T1GSS0 | 104 |  |  |

#### TABLE 12-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER1

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

|        |                  |            |                             | _                |            | <b>SYNC</b> = 0,            | BRGH = 1       | 1          |                             |                |            |                             |

|--------|------------------|------------|-----------------------------|------------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Fosc = 8.000 MHz |            | Fos                         | Fosc = 4.000 MHz |            | Fosc = 3.6864 MHz           |                |            | Fosc = 1.000 MHz            |                |            |                             |

| RATE   | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | —                |            | —                           | _                | _          | _                           |                | _          | _                           | 300            | 0.16       | 207                         |

| 1200   | —                | —          | —                           | 1202             | 0.16       | 207                         | 1200           | 0.00       | 191                         | 1202           | 0.16       | 51                          |

| 2400   | 2404             | 0.16       | 207                         | 2404             | 0.16       | 103                         | 2400           | 0.00       | 95                          | 2404           | 0.16       | 25                          |

| 9600   | 9615             | 0.16       | 51                          | 9615             | 0.16       | 25                          | 9600           | 0.00       | 23                          | _              | _          | _                           |

| 10417  | 10417            | 0.00       | 47                          | 10417            | 0.00       | 23                          | 10473          | 0.53       | 21                          | 10417          | 0.00       | 5                           |

| 19.2k  | 19231            | 0.16       | 25                          | 19.23k           | 0.16       | 12                          | 19.2k          | 0.00       | 11                          | —              | _          | _                           |

| 57.6k  | 55556            | -3.55      | 8                           | —                | _          | _                           | 57.60k         | 0.00       | 3                           | —              | _          | _                           |

| 115.2k | _                | —          | _                           | _                | —          | —                           | 115.2k         | 0.00       | 1                           | _              | —          | _                           |

#### TABLE 16-5: BAUD RATES FOR ASYNCHRONOUS MODES

| FIGURE 16-8:            | SYNCHRONOUS RECEPTION (MASTER MODE, SREN)                                          |     |

|-------------------------|------------------------------------------------------------------------------------|-----|

| RX/DT<br>pin            | bit 0 bit 1 bit 2 bit 3 bit 4 bit 5 bit 6 bit 7                                    |     |

| TX/CK pin               |                                                                                    |     |

| Write to<br>bit SREN    |                                                                                    |     |

| SREN bit                | l                                                                                  |     |

| CREN bit <u>'</u> 0'    |                                                                                    | ʻ0' |

| RCIF bit<br>(Interrupt) |                                                                                    |     |

| Read<br>RCREG           |                                                                                    |     |

| Note: Timing d          | iagram demonstrates Synchronous Master mode with bit SREN = 1 and bit BRGH = $0$ . |     |

| Name   | Bit 7    | Bit 6       | Bit 5      | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|----------|-------------|------------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE      | PEIE        | TOIE       | INTE   | RBIE   | T0IF   | INTF   | RBIF   | 0000 000x            | 0000 000x                       |

| PIE1   | TMR1GIE  | ADIE        | RCIE       | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| PIR1   | TMR1GIF  | ADIF        | RCIF       | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| RCREG  | AUSART R | eceive Data | a Register |        |        |        |        |        | 0000 0000            | 0000 0000                       |

| RCSTA  | SPEN     | RX9         | SREN       | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 0000 000x            | 0000 000x                       |

| TRISC  | TRISC7   | TRISC6      | TRISC5     | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 1111 1111            | 1111 1111                       |

| TXSTA  | CSRC     | TX9         | TXEN       | SYNC   | —      | BRGH   | TRMT   | TX9D   | 0000 -010            | 0000 -010                       |

#### TABLE 16-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for synchronous master reception.

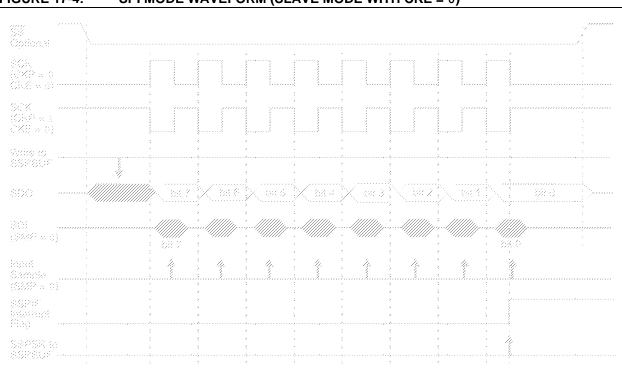

#### FIGURE 17-4: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 0)

#### SS SCK (CKP = 0 $\dot{C}KE = 1)$ SCK (CKP = 1 CKE = 1) Write to SSPBUF bit 6 bit 5 bit 4 bit 2 bit 1 bit 0 SDO bit '7 bit 3 ï SDI (SMP = 0)I bit 0 bit 7 Input Sample (SMP = 0)SSPIF Interrupt Flag SSPSR to SSPBUF 1 . i . . . .

### FIGURE 17-5: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

| SUBWF            | Subtract W from f                                                                                                                                                                         |              |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--|--|--|--|--|

| Syntax:          | [label] SU                                                                                                                                                                                | JBWF f,d     |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                        |              |  |  |  |  |  |

| Operation:       | (f) - (W) $\rightarrow$ (                                                                                                                                                                 | destination) |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                                  |              |  |  |  |  |  |

| Description:     | Subtract (2's complement method<br>W register from register 'f'. If 'd' is<br>'0', the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f. |              |  |  |  |  |  |

|                  | <b>C</b> = 0                                                                                                                                                                              | W > f        |  |  |  |  |  |

|                  | <b>C</b> = 1                                                                                                                                                                              | $W \leq f$   |  |  |  |  |  |

$\overline{DC} = 0$

**DC** = 1

W<3:0> > f<3:0> W<3:0>  $\leq$  f<3:0>

| XORLW            | Exclusive OR literal with W                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                               |

| Operands:        | $0 \leq k \leq 255$                                                                                                    |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                          |

| Status Affected: | Z                                                                                                                      |

| Description:     | The contents of the W register<br>are XOR'ed with the 8-bit<br>literal 'k'. The result is placed in<br>the W register. |

| SWAPF            | Swap Nibbles in f                                                                                                                                                      |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SWAPF f,d                                                                                                                                                      |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                            |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                                |

| Status Affected: | None                                                                                                                                                                   |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed in register 'f'. |

| XORWF            | Exclusive OR W with f                                                                                                                                                           |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                      |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                     |  |  |  |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                       |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                               |  |  |  |  |  |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |  |  |  |  |  |

| PIC16LF       | 722A/723  | A                                                         | $ \begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq T A \leq +85^\circ C \mbox{ for industrial} \\ -40^\circ C \leq T A \leq +125^\circ C \mbox{ for extended} \end{array} $ |                                                                                                                                                                                         |                          |                  |                                                                                                                                                                                                                                                              |  |  |

|---------------|-----------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PIC16F7       | 722A/723A | <b>N</b>                                                  |                                                                                                                                                                                                                                                               | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |                          |                  |                                                                                                                                                                                                                                                              |  |  |

| Param.<br>No. | Sym.      | Characteristic                                            | Min.                                                                                                                                                                                                                                                          | Тур†                                                                                                                                                                                    | Max.                     | Units            | Conditions                                                                                                                                                                                                                                                   |  |  |

| D001          | Vdd       | Supply Voltage                                            |                                                                                                                                                                                                                                                               |                                                                                                                                                                                         |                          |                  |                                                                                                                                                                                                                                                              |  |  |

|               |           | PIC16LF722A/723A                                          | 1.8<br>1.8<br>2.3<br>2.5                                                                                                                                                                                                                                      |                                                                                                                                                                                         | 3.6<br>3.6<br>3.6<br>3.6 | V<br>V<br>V<br>V | Fosc $\leq$ 16 MHz: HFINTOSC, EC<br>Fosc $\leq$ 4 MHz<br>Fosc $\leq$ 20 MHz, EC<br>Fosc $\leq$ 20 MHz, HS                                                                                                                                                    |  |  |

| D001          |           | PIC16F722A/723A                                           | 1.8<br>1.8<br>2.3<br>2.5                                                                                                                                                                                                                                      |                                                                                                                                                                                         | 5.5<br>5.5<br>5.5<br>5.5 | V<br>V<br>V<br>V | Fosc $\leq$ 16 MHz: HFINTOSC, EC<br>Fosc $\leq$ 4 MHz<br>Fosc $\leq$ 20 MHz, EC<br>Fosc $\leq$ 20 MHz, HS                                                                                                                                                    |  |  |

| D002*         | Vdr       | RAM Data Retention Voltage <sup>(1)</sup>                 |                                                                                                                                                                                                                                                               |                                                                                                                                                                                         |                          |                  |                                                                                                                                                                                                                                                              |  |  |

|               |           | PIC16LF722A/723A                                          | 1.5                                                                                                                                                                                                                                                           |                                                                                                                                                                                         | —                        | V                | Device in Sleep mode                                                                                                                                                                                                                                         |  |  |

| D002*         |           | PIC16F722A/723A                                           | 1.7                                                                                                                                                                                                                                                           | —                                                                                                                                                                                       | _                        | V                | Device in Sleep mode                                                                                                                                                                                                                                         |  |  |

|               | VPOR*     | Power-on Reset Release Voltage                            |                                                                                                                                                                                                                                                               | 1.6                                                                                                                                                                                     | _                        | V                |                                                                                                                                                                                                                                                              |  |  |

|               | VPORR*    | Power-on Reset Rearm Voltage                              |                                                                                                                                                                                                                                                               |                                                                                                                                                                                         |                          |                  |                                                                                                                                                                                                                                                              |  |  |

|               |           | PIC16LF722A/723A                                          |                                                                                                                                                                                                                                                               | 0.8                                                                                                                                                                                     | —                        | V                | Device in Sleep mode                                                                                                                                                                                                                                         |  |  |

|               |           | PIC16F722A/723A                                           | _                                                                                                                                                                                                                                                             | 1.7                                                                                                                                                                                     |                          | V                | Device in Sleep mode                                                                                                                                                                                                                                         |  |  |

| D003          | Vfvr      | Fixed Voltage Reference Voltage,<br>Initial Accuracy      | -5.5<br>-5.5<br>-5.5                                                                                                                                                                                                                                          | <br> <br>                                                                                                                                                                               | 5.5<br>5.5<br>5.5        | %<br>%<br>%      | $ \begin{array}{l} {\sf VFVR} = 1.024{\sf V},  {\sf VDD} \geq 2.5{\sf V} \\ {\sf VFVR} = 2.048{\sf V},  {\sf VDD} \geq 2.5{\sf V} \\ {\sf VFVR} = 4.096{\sf V},  {\sf VDD} \geq 4.75{\sf V}; \\ {\sf -40} \leq {\sf TA} \leq 85^{\circ}{\sf C} \end{array} $ |  |  |

|               |           |                                                           | -6<br>-6<br>-6                                                                                                                                                                                                                                                |                                                                                                                                                                                         | 6<br>6<br>6              | %<br>%<br>%      | $\label{eq:VFVR} \begin{split} &V{\sf FVR} = 1.024V, \ V{\sf DD} \geq 2.5V \\ &V{\sf FVR} = 2.048V, \ V{\sf DD} \geq 2.5V \\ &V{\sf FVR} = 4.096V, \ V{\sf DD} \geq 4.75V; \\ &-40 \leq {\sf TA} \leq 125^{\circ}{\sf C} \end{split}$                        |  |  |

| D004*         | SVDD      | VDD Rise Rate to ensure internal<br>Power-on Reset signal | 0.05                                                                                                                                                                                                                                                          |                                                                                                                                                                                         | —                        | V/ms             | See Section 3.2 "Power-on Reset (POR)" for details.                                                                                                                                                                                                          |  |  |

## 23.1 DC Characteristics: PIC16(L)F722A/723A-I/E (Industrial, Extended)

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

| Param.<br>No.                | Symbol  | Charact              | haracteristic |               | Max. | Units | Conditions                                  |  |

|------------------------------|---------|----------------------|---------------|---------------|------|-------|---------------------------------------------|--|

| SP100* THIGH Clock high time |         | Clock high time      | 100 kHz mode  | 4.0           | —    | μS    | Device must operate at a minimum of 1.5 MHz |  |

|                              |         |                      | 400 kHz mode  | 0.6           | _    | μS    | Device must operate at a minimum of 10 MHz  |  |

|                              |         |                      | SSP Module    | 1.5Tcy        | —    |       |                                             |  |

| SP101*                       | TLOW    | Clock low time       | 100 kHz mode  | 4.7           | -    | μS    | Device must operate at a minimum of 1.5 MHz |  |

|                              |         |                      | 400 kHz mode  | 1.3           | -    | μS    | Device must operate at a minimum of 10 MHz  |  |

|                              |         |                      | SSP Module    | 1.5Tcy        | —    |       |                                             |  |

| SP102*                       | TR      | SDA and SCL rise     | 100 kHz mode  | —             | 1000 | ns    |                                             |  |

| time                         |         | time                 | 400 kHz mode  | 20 +<br>0.1Св | 300  | ns    | CB is specified to be from 10-400 pF        |  |

| SP103*                       | TF      | SDA and SCL fall     | 100 kHz mode  | —             | 250  | ns    |                                             |  |

|                              |         | time                 | 400 kHz mode  | 20 +<br>0.1Св | 250  | ns    | CB is specified to be from 10-400 pF        |  |

| SP106*                       | THD:DAT | Data input hold      | 100 kHz mode  | 0             | _    | ns    |                                             |  |

|                              |         | time                 | 400 kHz mode  | 0             | 0.9  | μs    |                                             |  |

| SP107*                       | TSU:DAT | Data input setup     | 100 kHz mode  | 250           | _    | ns    | (Note 2)                                    |  |

|                              |         | time                 | 400 kHz mode  | 100           | —    | ns    |                                             |  |

| SP109*                       | ΤΑΑ     | Output valid from    | 100 kHz mode  | —             | 3500 | ns    | (Note 1)                                    |  |

|                              |         | clock                | 400 kHz mode  | —             | _    | ns    |                                             |  |

| SP110*                       | TBUF    | Bus free time        | 100 kHz mode  | 4.7           | _    | μs    | Time the bus must be free                   |  |

|                              |         |                      | 400 kHz mode  | 1.3           | —    | μS    | before a new transmis-<br>sion can start    |  |

| SP111                        | Св      | Bus capacitive loadi | ing           | _             | 400  | pF    |                                             |  |

## TABLE 23-13: I<sup>2</sup>C BUS DATA REQUIREMENTS

\* These parameters are characterized but not tested.

**Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of Start or Stop conditions.

**2:** A Fast mode (400 kHz)  $I^2C$  bus device can be used in a Standard mode (100 kHz)  $I^2C$  bus system, but the requirement TsU:DAT  $\ge$  250 ns must then be met. This will automatically be the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the low period of the SCL signal, it must output the next data bit to the SDA line TR max. + TSU:DAT = 1000 + 250 = 1250 ns (according to the Standard mode  $I^2C$  bus specification), before the SCL line is released.