Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | · · · · · · · · · · · · · · · · · · ·                                      |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 11x8b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f722at-i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address               | Name    | Bit 7                                                                                          | Bit 6                                | Bit 5         | Bit 4          | Bit 3         | Bit 2         | Bit 1      | Bit 0   | Value on:<br>POR, BOR | Page   |

|-----------------------|---------|------------------------------------------------------------------------------------------------|--------------------------------------|---------------|----------------|---------------|---------------|------------|---------|-----------------------|--------|

| Bank 0                |         |                                                                                                |                                      |               |                |               |               |            |         |                       |        |

| 00h <sup>(2)</sup>    | INDF    | Addressing this location uses contents of FSR to address data memory (not a physical register) |                                      |               |                |               |               |            |         |                       | 22,30  |

| 01h                   | TMR0    | Timer0 Mod                                                                                     | lule Register                        |               |                |               |               |            |         | xxxx xxxx             | 91,30  |

| 02h <sup>(2)</sup>    | PCL     | Program Co                                                                                     | ounter (PC) L                        | east Signific | cant Byte      |               |               |            |         | 0000 0000             | 21,30  |

| 03h <sup>(2)</sup>    | STATUS  | IRP                                                                                            | RP1                                  | RP0           | TO             | PD            | Z             | DC         | С       | 0001 1xxx             | 18,30  |

| 04h <sup>(2)</sup>    | FSR     | Indirect Dat                                                                                   | a Memory A                           | ddress Point  | er             |               |               |            |         | XXXX XXXX             | 22,30  |

| 05h                   | PORTA   | RA7                                                                                            | RA6                                  | RA5           | RA4            | RA3           | RA2           | RA1        | RA0     | xxxx xxxx             | 43,30  |

| 06h                   | PORTB   | RB7                                                                                            | RB6                                  | RB5           | RB4            | RB3           | RB2           | RB1        | RB0     | xxxx xxxx             | 52,30  |

| 07h                   | PORTC   | RC7                                                                                            | RC6                                  | RC5           | RC4            | RC3           | RC2           | RC1        | RC0     | xxxx xxxx             | 62,30  |

| 09h                   | PORTE   | _                                                                                              | —                                    | _             | —              | RE3           | _             | _          | _       | xxxx                  | 69,30  |

| 0Ah <sup>(1, 2)</sup> | PCLATH  | _                                                                                              | _                                    | _             | Write Buffer   | for the upper | 5 bits of the | Program Co | unter   | 0 0000                | 21,30  |

| 0Bh <sup>(2)</sup>    | INTCON  | GIE                                                                                            | PEIE                                 | TOIE          | INTE           | RBIE          | T0IF          | INTF       | RBIF    | 0000 000x             | 36,30  |

| 0Ch                   | PIR1    | TMR1GIF                                                                                        | ADIF                                 | RCIF          | TXIF           | SSPIF         | CCP1IF        | TMR2IF     | TMR1IF  | 0000 0000             | 39,30  |

| 0Dh                   | PIR2    | _                                                                                              | _                                    |               | _              | _             | _             | _          | CCP2IF  | 0                     | 40,30  |

| 0Eh                   | TMR1L   | Holding Reg                                                                                    | gister for the                       | Least Signif  | icant Byte of  | the 16-bit TN | IR1 Register  |            |         | xxxx xxxx             | 99,30  |

| 0Fh                   | TMR1H   | Holding Re                                                                                     | gister for the                       | Most Signifi  | cant Byte of t | he 16-bit TM  | R1 Register   |            |         | xxxx xxxx             | 99,30  |

| 10h                   | T1CON   | TMR1CS1                                                                                        | TMR1CS0                              | T1CKPS1       | T1CKPS0        | T1OSCEN       | T1SYNC        | _          | TMR10N  | 0000 00-0             | 103,30 |

| 11h                   | TMR2    | Timer2 Mod                                                                                     | ule Register                         |               |                |               |               |            |         | 0000 0000             | 106,30 |

| 12h                   | T2CON   | —                                                                                              | TOUTPS3                              | TOUTPS2       | TOUTPS1        | TOUTPS0       | TMR2ON        | T2CKPS1    | T2CKPS0 | -000 0000             | 107,30 |

| 13h                   | SSPBUF  | Synchronou                                                                                     | us Serial Port                       | t Receive Bu  | Iffer/Transmit | Register      |               |            |         | xxxx xxxx             | 147,30 |

| 14h                   | SSPCON  | WCOL                                                                                           | SSPOV                                | SSPEN         | CKP            | SSPM3         | SSPM2         | SSPM1      | SSPM0   | 0000 0000             | 164,30 |

| 15h                   | CCPR1L  | Capture/Co                                                                                     | mpare/PWM                            | Register (L   | SB)            |               |               |            |         | xxxx xxxx             | 116,30 |

| 16h                   | CCPR1H  | Capture/Co                                                                                     | mpare/PWM                            | Register (N   | SB)            |               |               |            |         | xxxx xxxx             | 116,30 |

| 17h                   | CCP1CON | _                                                                                              | _                                    | DC1B1         | DC1B0          | CCP1M3        | CCP1M2        | CCP1M1     | CCP1M0  | 00 0000               | 115,30 |

| 18h                   | RCSTA   | SPEN                                                                                           | RX9                                  | SREN          | CREN           | ADDEN         | FERR          | OERR       | RX9D    | 0000 000x             | 134,30 |

| 19h                   | TXREG   | USART Tra                                                                                      | nsmit Data F                         | Register      |                |               |               | •          | •       | 0000 0000             | 133,30 |

| 1Ah                   | RCREG   | USART Red                                                                                      | ceive Data R                         | egister       |                |               |               |            |         | 0000 0000             | 131,30 |

| 1Bh                   | CCPR2L  | Capture/Compare/PWM Register 2 (LSB)                                                           |                                      |               |                |               |               |            |         | xxxx xxxx             | 116,30 |

| 1Ch                   | CCPR2H  | Capture/Co                                                                                     | Capture/Compare/PWM Register 2 (MSB) |               |                |               |               |            |         |                       | 116,30 |

| 1Dh                   | CCP2CON | —                                                                                              | —                                    | DC2B1         | DC2B0          | CCP2M3        | CCP2M2        | CCP2M1     | CCP2M0  | 00 0000               | 115,30 |

| 1Eh                   | ADRES   | A/D Result                                                                                     | Register                             |               |                |               |               |            | •       | xxxx xxxx             | 86,30  |

| 1Fh                   | ADCON0  | —                                                                                              | —                                    | CHS3          | CHS2           | CHS1          | CHS0          | GO/DONE    | ADON    | 00 0000               | 85,30  |

| TABLE 2-1: | PIC16(L)F722A/723A SPECIAL FUNCTION REGISTER SUMMARY | ( |

|------------|------------------------------------------------------|---|

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter.

2: These registers can be addressed from any bank.

**3:** Accessible only when SSPM<3:0> = 1001.

4: Accessible only when SSPM<3:0>  $\neq$  1001.

**5:** This bit is always '1' as RE3 is input-only.

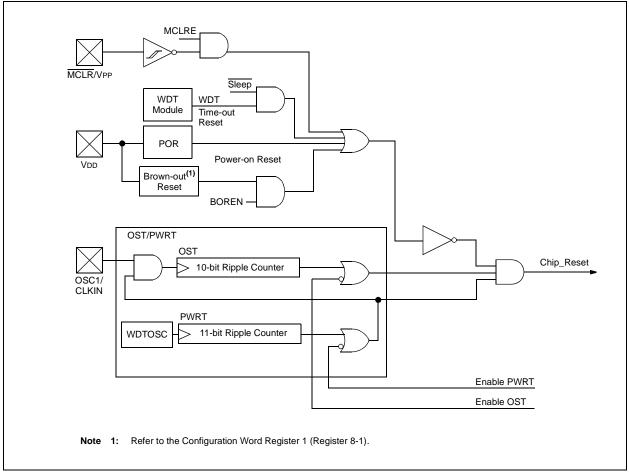

# 3.0 RESETS

The PIC16(L)F722A/723A differentiates between various kinds of Reset:

- a) Power-on Reset (POR)

- b) WDT Reset during normal operation

- c) WDT Reset during Sleep

- d) MCLR Reset during normal operation

- e) MCLR Reset during Sleep

- f) Brown-out Reset (BOR)

Some registers are not affected in any Reset condition; their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on:

- Power-on Reset (POR)

- MCLR Reset

- MCLR Reset during Sleep

- WDT Reset

- Brown-out Reset (BOR)

Most registers are not affected by a WDT wake-up since this is viewed as the resumption of normal operation. TO and PD bits are set or cleared differently in different Reset situations, as indicated in Table 3-3. These bits are used in software to determine the nature of the Reset.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 3-1.

The MCLR Reset path has a noise filter to detect and ignore small pulses. See **Section 23.0** "**Electrical Specifications**" for pulse width specifications.

## FIGURE 3-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

# 4.1 Operation

Interrupts are disabled upon any device Reset. They are enabled by setting the following bits:

- GIE bit of the INTCON register

- Interrupt Enable bit(s) for the specific interrupt event(s)

- PEIE bit of the INTCON register (if the Interrupt Enable bit of the interrupt event is contained in the PIE1 and PIE2 registers)

The INTCON, PIR1 and PIR2 registers record individual interrupts via interrupt flag bits. Interrupt flag bits will be set, regardless of the status of the GIE, PEIE and individual interrupt enable bits.

The following events happen when an interrupt event occurs while the GIE bit is set:

- · Current prefetched instruction is flushed

- · GIE bit is cleared

- Current Program Counter (PC) is pushed onto the stack

- · PC is loaded with the interrupt vector 0004h

The ISR determines the source of the interrupt by polling the interrupt flag bits. The interrupt flag bits must be cleared before exiting the ISR to avoid repeated

interrupts. Because the GIE bit is cleared, any interrupt that occurs while executing the ISR will be recorded through its interrupt flag, but will not cause the processor to redirect to the interrupt vector.

The RETFIE instruction exits the ISR by popping the previous address from the stack and setting the GIE bit.

For additional information on a specific interrupt's operation, refer to its peripheral chapter.

- Note 1: Individual interrupt flag bits are set, regardless of the state of any other enable bits.

- 2: All interrupts will be ignored while the GIE bit is cleared. Any interrupt occurring while the GIE bit is clear will be serviced when the GIE bit is set again.

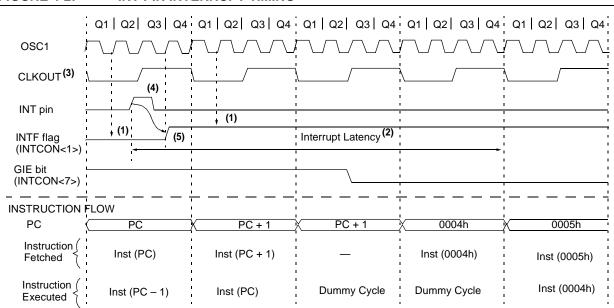

# 4.2 Interrupt Latency

Interrupt latency is defined as the time from when the interrupt event occurs to the time code execution at the interrupt vector begins. The latency for synchronous interrupts is three instruction cycles. For asynchronous interrupts, the latency is three to four instruction cycles, depending on when the interrupt occurs. See Figure 4-2 for timing details.

Note 1: INTF flag is sampled here (every Q1).

- 2: Asynchronous interrupt latency = 3-4 TCY. Synchronous latency = 3 TCY, where TCY = instruction cycle time. Latency is the same whether Inst (PC) is a single cycle or a 2-cycle instruction.

- 3: CLKOUT is available only in INTOSC and RC Oscillator modes.

- 4: For minimum width of INT pulse, refer to AC specifications in Section 23.0 "Electrical Specifications".

- 5: INTF is enabled to be set any time during the Q4-Q1 cycles.

# 4.5.1 INTCON REGISTER

The INTCON register is a readable and writable register, which contains the various enable and flag bits for TMR0 register overflow, PORTB change and external RB0/INT/SEG0 pin interrupts.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

# REGISTER 4-1: INTCON: INTERRUPT CONTROL REGISTER

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0               | R/W-0               | R/W-0 | R/W-x |

|-------|-------|-------|-------|---------------------|---------------------|-------|-------|

| GIE   | PEIE  | TOIE  | INTE  | RBIE <sup>(1)</sup> | T0IF <sup>(2)</sup> | INTF  | RBIF  |

| bit 7 |       |       |       |                     |                     |       | bit 0 |

|       |       |       |       |                     |                     |       |       |

| Legend:           |                  |                                                     |                    |  |  |

|-------------------|------------------|-----------------------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Writable bit U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                                | x = Bit is unknown |  |  |

| bit 7        | GIE: Global Interrupt Enable bit                                                                                            |

|--------------|-----------------------------------------------------------------------------------------------------------------------------|

|              | 1 = Enables all unmasked interrupts                                                                                         |

|              | 0 = Disables all interrupts                                                                                                 |

| bit 6        | PEIE: Peripheral Interrupt Enable bit                                                                                       |

|              | 1 = Enables all unmasked peripheral interrupts<br>0 = Disables all peripheral interrupts                                    |

| L:1. F       |                                                                                                                             |

| bit 5        | <b>TolE:</b> Timer0 Overflow Interrupt Enable bit<br>1 = Enables the Timer0 interrupt                                       |

|              | 0 = Disables the Timer0 interrupt                                                                                           |

| bit 4        | INTE: RB0/INT External Interrupt Enable bit                                                                                 |

|              | 1 = Enables the RB0/INT external interrupt                                                                                  |

|              | 0 = Disables the RB0/INT external interrupt                                                                                 |

| bit 3        | RBIE: PORTB Change Interrupt Enable bit <sup>(1)</sup>                                                                      |

|              | 1 = Enables the PORTB change interrupt                                                                                      |

|              | 0 = Disables the PORTB change interrupt                                                                                     |

| bit 2        | <b>T0IF:</b> Timer0 Overflow Interrupt Flag bit <sup>(2)</sup>                                                              |

|              | 1 = TMR0 register has overflowed (must be cleared in software)                                                              |

|              | 0 = TMR0 register did not overflow                                                                                          |

| bit 1        | INTF: RB0/INT External Interrupt Flag bit<br>1 = The RB0/INT external interrupt occurred (must be cleared in software)      |

|              | 0 = The RBO/INT external interrupt did not occur                                                                            |

| bit 0        | <b>RBIF:</b> PORTB Change Interrupt Flag bit                                                                                |

| bit 0        | <ul> <li>1 = When at least one of the PORTB general purpose I/O pins changed state (must be cleared in software)</li> </ul> |

|              | 0 = None of the PORTB general purpose I/O pins have changed state                                                           |

| <b>N</b> 4 4 |                                                                                                                             |

| Note 1:      | The appropriate bits in the IOCB register must also be set.                                                                 |

- **Note 1:** The appropriate bits in the IOCB register must also be set.

- 2: T0IF bit is set when Timer0 rolls over. Timer0 is unchanged on Reset and should be initialized before clearing T0IF bit.

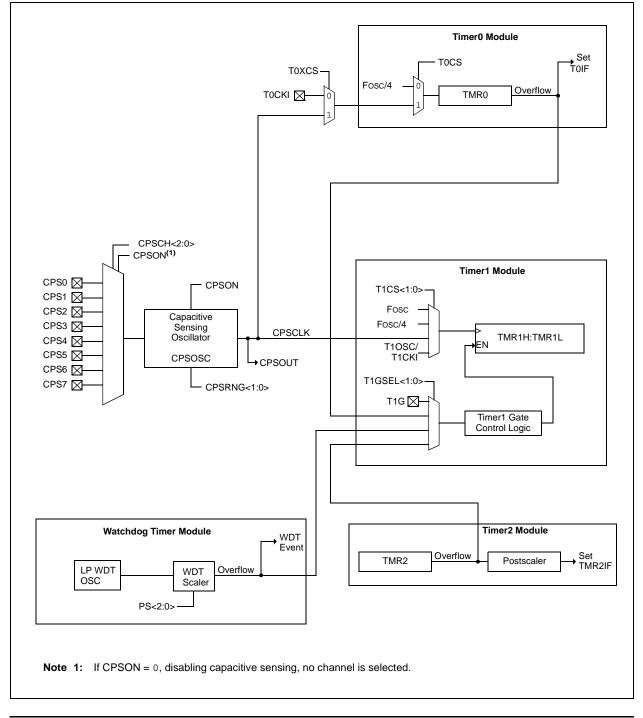

# 14.0 CAPACITIVE SENSING MODULE

The capacitive sensing module allows for an interaction with an end user without a mechanical interface. In a typical application, the capacitive sensing module is attached to a pad on a printed circuit board (PCB), which is electrically isolated from the end user. When the end user places their finger over the PCB pad, a capacitive load is added, causing a frequency shift in the capacitive sensing module. The capacitive sensing module requires software and at least one timer resource to determine the change in frequency. Key features of this module include:

- · Analog MUX for monitoring multiple inputs

- · Capacitive sensing oscillator

- Multiple timer resources

- Software control

- · Operation during Sleep

### FIGURE 14-1: CAPACITIVE SENSING BLOCK DIAGRAM

# 14.6 Operation During Sleep

The capacitive sensing oscillator will continue to run as long as the module is enabled, independent of the part being in Sleep. In order for the software to determine if a frequency change has occurred, the part must be awake. However, the part does not have to be awake when the timer resource is acquiring counts. One way to acquire the Timer1 counts while in Sleep is to have Timer1 gated with the overflow of the Watchdog Timer. This can be accomplished using the following steps:

- 1. Configure the Watchdog Time-out overflow as the Timer1's gate source T1GSS<1:0> = 11.

- 2. Set Timer1 gate to toggle mode by setting the T1GTM bit of the T1GCON register.

- 3. Set the TMR1GE bit of the T1GCON register.

- 4. Set TMR1ON bit of the T1CON register.

- 5. Enable capacitive sensing module with the appropriate current settings and pin selection.

- 6. Clear Timer1.

- 7. Put the part to Sleep.

- 8. On the first WDT overflow, the capacitive sensing oscillator will begin to increment Timer1. Then put the part to Sleep.

- 9. On the second WDT overflow Timer1 will stop incrementing. Then run the software routine to determine if a frequency change has occurred.

Refer to Section 12.0 "Timer1 Module with Gate Control" for additional information.

- Note 1: When using the WDT to set the interval on Timer1, any other source that wakes the part up early will cause the WDT overflow to be delayed, affecting the value captured by Timer1.

- 2: Timer0 does not operate when in Sleep, and therefore cannot be used for capacitive sense measurements in Sleep.

| REGISTER 14-2: CPSCON1: CAPACITIVE SENSING CONTROL REGISTER 1        |     |     |     |                 |        |        |        |  |  |

|----------------------------------------------------------------------|-----|-----|-----|-----------------|--------|--------|--------|--|--|

| U-0                                                                  | U-0 | U-0 | U-0 | U-0             | R/W-0  | R/W-0  | R/W-0  |  |  |

| —                                                                    | —   | —   | —   | _               | CPSCH2 | CPSCH1 | CPSCH0 |  |  |

| bit 7                                                                |     |     |     |                 |        |        | bit 0  |  |  |

|                                                                      |     |     |     |                 |        |        |        |  |  |

| Legend:                                                              |     |     |     |                 |        |        |        |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |     |     |     |                 |        |        |        |  |  |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x =          |     |     |     | x = Bit is unkr | nown   |        |        |  |  |

| bit 7-3 | Unimplemented: Read as '0'                         |  |  |  |  |  |  |

|---------|----------------------------------------------------|--|--|--|--|--|--|

| bit 2-0 | CPSCH<2:0>: Capacitive Sensing Channel Select bits |  |  |  |  |  |  |

|         | If CPSON = 0:                                      |  |  |  |  |  |  |

|         | These bits are ignored. No channel is selected.    |  |  |  |  |  |  |

|         | <u>If CPSON = 1</u> :                              |  |  |  |  |  |  |

|         | 000 = channel 0, (CPS0)                            |  |  |  |  |  |  |

|         | 001 = channel 1, (CPS1)                            |  |  |  |  |  |  |

|         | 010 = channel 2, (CPS2)                            |  |  |  |  |  |  |

|         | 011 = channel 3, (CPS3)                            |  |  |  |  |  |  |

|         | 100 = channel 4, (CPS4)                            |  |  |  |  |  |  |

|         | 101 = channel 5, (CPS5)                            |  |  |  |  |  |  |

|         | 110 = channel 6, (CPS6)                            |  |  |  |  |  |  |

|         | 111 = channel 7, (CPS7)                            |  |  |  |  |  |  |

## TABLE 14-2: SUMMARY OF REGISTERS ASSOCIATED WITH CAPACITIVE SENSING

| Name       | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Register<br>on Page |

|------------|---------|---------|---------|---------|---------|--------|---------|---------|---------------------|

| ANSELA     |         | —       | ANSA5   | ANSA4   | ANSA3   | ANSA2  | ANSA1   | ANSA0   | 44                  |

| ANSELB     | -       | —       | ANSB5   | ANSB4   | ANSB3   | ANSB2  | ANSB1   | ANSB0   | 53                  |

| OPTION_REG | RBPU    | INTEDG  | TOCS    | T0SE    | PSA     | PS2    | PS1     | PS0     | 19                  |

| PIE1       | TMR1GIE | ADIE    | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 37                  |

| PIR1       | TMR1GIF | ADIF    | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 39                  |

| T1CON      | TMR1CS1 | TMR1CS0 | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | —       | TMR10N  | 103                 |

| T2CON      | -       | TOUTPS3 | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | 107                 |

| TRISA      | TRISA7  | TRISA6  | TRISA5  | TRISA4  | TRISA3  | TRISA2 | TRISA1  | TRISA0  | 43                  |

| TRISB      | TRISB7  | TRISB6  | TRISB5  | TRISB4  | TRISB3  | TRISB2 | TRISB1  | TRISB0  | 52                  |

Legend: - = Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the capacitive sensing module.

| Name   | Bit 7    | Bit 6       | Bit 5      | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|----------|-------------|------------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE      | PEIE        | TOIE       | INTE   | RBIE   | T0IF   | INTF   | RBIF   | 0000 000x            | 0000 000x                       |

| PIE1   | TMR1GIE  | ADIE        | RCIE       | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| PIR1   | TMR1GIF  | ADIF        | RCIF       | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| RCREG  | AUSART R | eceive Data | a Register |        |        |        |        |        | 0000 0000            | 0000 0000                       |

| RCSTA  | SPEN     | RX9         | SREN       | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 0000 000x            | 0000 000x                       |

| SPBRG  | BRG7     | BRG6        | BRG5       | BRG4   | BRG3   | BRG2   | BRG1   | BRG0   | 0000 0000            | 0000 0000                       |

| TRISC  | TRISC7   | TRISC6      | TRISC5     | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 1111 1111            | 1111 1111                       |

| TXSTA  | CSRC     | TX9         | TXEN       | SYNC   | —      | BRGH   | TRMT   | TX9D   | 0000 -010            | 0000 -010                       |

# TABLE 16-2: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for asynchronous reception.

# 16.3.1.4 Synchronous Master Reception

Data is received at the RX/DT pin. The RX/DT pin output driver is automatically disabled when the AUSART is configured for synchronous master receive operation.

In Synchronous mode, reception is enabled by setting either the Single Receive Enable bit (SREN of the RCSTA register) or the Continuous Receive Enable bit (CREN of the RCSTA register).

When SREN is set and CREN is clear, only as many clock cycles are generated as there are data bits in a single character. The SREN bit is automatically cleared at the completion of one character. When CREN is set, clocks are continuously generated until CREN is cleared. If CREN is cleared in the middle of a character the CK clock stops immediately and the partial character is discarded. If SREN and CREN are both set, then SREN is cleared at the completion of the first character and CREN takes precedence.

To initiate reception, set either SREN or CREN. Data is sampled at the RX/DT pin on the trailing edge of the TX/CK clock pin and is shifted into the Receive Shift Register (RSR). When a complete character is received into the RSR, the RCIF bit of the PIR1 register is set and the character is automatically transferred to the two character receive FIFO. The Least Significant eight bits of the top character in the receive FIFO are available in RCREG. The RCIF bit remains set as long as there are un-read characters in the receive FIFO.

## 16.3.1.5 Slave Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a slave receives the clock on the TX/CK line. The TX/ CK pin output driver is automatically disabled when the device is configured for synchronous slave transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One data bit is transferred for each clock cycle. Only as many clock cycles should be received as there are data bits.

# 16.3.1.6 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before RCREG is read to access the FIFO. When this happens the OERR bit of the RCSTA register is set. Previous data in the FIFO will not be overwritten. The two characters in the FIFO buffer can be read, however, no additional characters will be received until the error is cleared. The OERR bit can only be cleared by clearing the overrun condition. If the overrun error occurred when the SREN bit is set and CREN is clear then the error is cleared by reading RCREG. If the overrun occurred when the CREN bit is set then the error condition is cleared by either clearing the CREN bit of the RCSTA register.

## 16.3.1.7 Receiving 9-bit Characters

The AUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set, the AUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth, and Most Significant, data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREG.

Address detection in Synchronous modes is not supported, therefore the ADDEN bit of the RCSTA register must be cleared.

# 16.3.1.8 Synchronous Master Reception Setup:

- 1. Initialize the SPBRG register for the appropriate baud rate. Set or clear the BRGH bit, as required, to achieve the desired baud rate.

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Ensure bits CREN and SREN are clear.

- 4. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit reception is desired, set bit RX9.

- 6. Verify address detection is disabled by clearing the ADDEN bit of the RCSTA register.

- 7. Start reception by setting the SREN bit or for continuous reception, set the CREN bit.

- Interrupt flag bit RCIF of the PIR1 register will be set when reception of a character is complete. An interrupt will be generated if the RCIE interrupt enable bit of the PIE1 register was set.

- 9. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 10. Read the 8-bit received data by reading the RCREG register.

- 11. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit, which resets the AUSART.

# 17.1.2 SLAVE MODE

For any SPI device acting as a slave, the data is transmitted and received as external clock pulses appear on SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

## 17.1.2.1 Slave Mode Operation

The SSP consists of a transmit/receive shift register (SSPSR) and a buffer register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR until the received data is ready.

The slave has no control as to when data will be clocked in or out of the device. All data that is to be transmitted, to a master or another slave, must be loaded into the SSPBUF register before the first clock pulse is received.

Once eight bits of data have been received:

- · Received byte is moved to the SSPBUF register

- BF bit of the SSPSTAT register is set

- SSPIF bit of the PIR1 register is set

Any write to the SSPBUF register during transmission/ reception of data will be ignored and the Write Collision Detect bit, WCOL of the SSPCON register, will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPBUF register completed successfully.

The user's firmware must read SSPBUF, clearing the BF flag, or the SSPOV bit of the SSPCON register will be set with the reception of the next byte and communication will be disabled.

A SPI module transmits and receives at the same time, occasionally causing dummy data to be transmitted/ received. It is up to the user to determine which data is to be used and what can be discarded.

## 17.1.2.2 Enabling Slave I/O

To enable the serial port, the SSPEN bit of the SSPCON register must be set. If a Slave mode of operation is selected in the SSPM bits of the SSPCON register, the SDI, SDO and SCK pins will be assigned as serial port pins.

For these pins to function as serial port pins, they must have their corresponding data direction bits set or cleared in the associated TRIS register as follows:

- · SDI configured as input

- · SDO configured as output

- · SCK configured as input

Optionally, a fourth pin, Slave Select  $(\overline{SS})$  may be used in Slave mode. Slave Select may be configured to operate on one of the following pins via the SSSEL bit in the APFCON register.

- RA5/AN4/SS

- RA0/AN0/SS

Upon selection of a Slave Select pin, the appropriate bits must be set in the ANSELA and TRISA registers. Slave Select must be set as an input by setting the corresponding bit in TRISA, and digital I/O must be enabled on the SS pin by clearing the corresponding bit of the ANSELA register.

## 17.1.2.3 Slave Mode Setup

When initializing the SSP module to SPI Slave mode, compatibility must be ensured with the master device. This is done by programming the appropriate control bits of the SSPCON and SSPSTAT registers. These control bits allow the following to be specified:

- SCK as clock input

- Idle state of SCK (CKP bit)

- Data input sample phase (SMP bit)

- Output data on rising/falling edge of SCK (CKE bit)

Figure 17-4 and Figure 17-5 show example waveforms of Slave mode operation.

#### START AND STOP CONDITIONS 17.2.2

During times of no data transfer (Idle time), both the clock line (SCL) and the data line (SDA) are pulled high through external pull-up resistors. The Start and Stop conditions determine the start and stop of data transmission. The Start condition is defined as a high-to-low transition of the SDA line while SCL is high. The Stop condition is defined as a low-to-high transition of the SDA line while SCL is high.

Figure 17-9 shows the Start and Stop conditions. A master device generates these conditions for starting and terminating data transfer. Due to the definition of the Start and Stop conditions, when data is being transmitted, the SDA line can only change state when the SCL line is low.

#### ACKNOWLEDGE 17.2.3

After the valid reception of an address or data byte, the hardware automatically will generate the Acknowledge (ACK) pulse and load the SSPBUF register with the received value currently in the SSPSR register. There are certain conditions that will cause the SSP module not to generate this ACK pulse. They include any or all of the following:

- The Buffer Full bit, BF of the SSPSTAT register, was set before the transfer was received.

- The SSP Overflow bit. SSPOV of the SSPCON register, was set before the transfer was received.

- The SSP module is being operated in Firmware Master mode.

In such a case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF of the PIR1 register is set. Table 17-2 shows the results of when a data transfer byte is received, given the status of bits BF and SSPOV. Flag bit BF is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

# ٦ SDA SCL S Р Change of Change of Data Allowed Data Allowed Start Stop Condition Condition

| Status Bits as Data<br>Transfer is Received |       | $SSPSR \to SSPBUF$ | Generate ACK<br>Pulse | Set bit SSPIF<br>(SSP Interrupt occurs |  |  |

|---------------------------------------------|-------|--------------------|-----------------------|----------------------------------------|--|--|

| BF                                          | SSPOV |                    | Puise                 | if enabled)                            |  |  |

| 0                                           | 0     | Yes                | Yes                   | Yes                                    |  |  |

| 1                                           | 0     | No                 | No                    | Yes                                    |  |  |

| 1                                           | 1     | No                 | No                    | Yes                                    |  |  |

| 0                                           | 1     | No                 | No                    | Yes                                    |  |  |

Note 1: Shaded cells show the conditions where the user software did not properly clear the overflow condition.

#### **FIGURE 17-9:** START AND STOP CONDITIONS

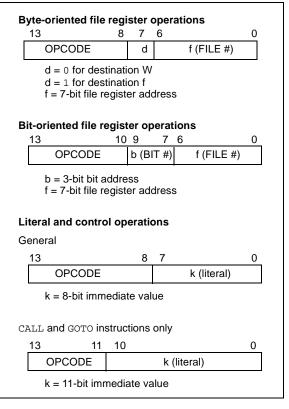

# 21.0 INSTRUCTION SET SUMMARY

The PIC16(L)F722A/723A instruction set is highly orthogonal and is comprised of three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

Each PIC16 instruction is a 14-bit word divided into an **opcode**, which specifies the instruction type and one or more **operands**, which further specify the operation of the instruction. The formats for each of the categories is presented in Figure 21-1, while the various opcode fields are summarized in Table 21-1.

Table 21-2 lists the instructions recognized by the MPASM<sup>TM</sup> assembler.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator, which selects the bit affected by the operation, while 'f' represents the address of the file in which the bit is located.

For **literal and control** operations, 'k' represents an 8bit or 11-bit constant, or literal value.

One instruction cycle consists of four oscillator periods; for an oscillator frequency of 4 MHz, this gives a nominal instruction execution time of 1  $\mu$ s. All instructions are executed within a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of an instruction. When this occurs, the execution takes two instruction cycles, with the second cycle executed as a NOP.

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

# 21.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

For example, a CLRF PORTB instruction will read PORTB, clear all the data bits, then write the result back to PORTB. This example would have the unintended consequence of clearing the condition that set the RBIF flag.

## TABLE 21-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                     |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                            |

| W     | Working register (accumulator)                                                                                                                                                  |

| b     | Bit address within an 8-bit file register                                                                                                                                       |

| k     | Literal field, constant data or label                                                                                                                                           |

| x     | Don't care location (= 0 or 1).<br>The assembler will generate code with $x = 0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; $d = 0$ : store result in W,<br>d = 1: store result in file register f.<br>Default is $d = 1$ .                                                             |

| PC    | Program Counter                                                                                                                                                                 |

| TO    | Time-out bit                                                                                                                                                                    |

| С     | Carry bit                                                                                                                                                                       |

| DC    | Digit carry bit                                                                                                                                                                 |

| Z     | Zero bit                                                                                                                                                                        |

| PD    | Power-down bit                                                                                                                                                                  |

## FIGURE 21-1: GENERAL FORMAT FOR INSTRUCTIONS

© 2010-2016 Microchip Technology Inc.

| RLF              | Rotate                                                                                                                                                                                                               | Left f thi                 | roug  | h Carry | y    |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------|---------|------|--|--|--|--|

| Syntax:          | [ label ]                                                                                                                                                                                                            | RLF                        | f,d   |         |      |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                   |                            |       |         |      |  |  |  |  |

| Operation:       | See de                                                                                                                                                                                                               | scription                  | belov | N       |      |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                                    |                            |       |         |      |  |  |  |  |

| Description:     | The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry flag. If 'd' is '0', the<br>result is placed in the W register.<br>If 'd' is '1', the result is stored<br>back in register 'f'. |                            |       |         |      |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                    |                            |       |         |      |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                    |                            |       |         |      |  |  |  |  |

| Example:         | RLF                                                                                                                                                                                                                  | REG1,                      | 0     |         |      |  |  |  |  |

|                  | Before Instruction                                                                                                                                                                                                   |                            |       |         |      |  |  |  |  |

|                  |                                                                                                                                                                                                                      | REG1                       | =     | 1110    | 0110 |  |  |  |  |

|                  | Aftor In                                                                                                                                                                                                             | C = 0<br>After Instruction |       |         |      |  |  |  |  |

|                  | Alter In                                                                                                                                                                                                             | REG1                       | =     | 1110    | 0110 |  |  |  |  |

|                  |                                                                                                                                                                                                                      | W                          | =     | 1100    | 1100 |  |  |  |  |

|                  |                                                                                                                                                                                                                      |                            |       |         |      |  |  |  |  |

| SLEEP            | Enter Sleep mode                                                                                                                                                                                                       |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SLEEP                                                                                                                                                                                                          |

| Operands:        | None                                                                                                                                                                                                                   |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow \underline{WDT} \text{ prescaler}, \\ 1 \rightarrow \overline{\underline{TO}}, \\ 0 \rightarrow \overline{PD} \end{array}$                                     |

| Status Affected: | TO, PD                                                                                                                                                                                                                 |

| Description:     | The power-down Status bit, $\overline{PD}$ is cleared. Time-out Status bit, $\overline{TO}$ is set. Watchdog Timer and its prescaler are cleared.<br>The processor is put into Sleep mode with the oscillator stopped. |

| RRF              | Rotate Right f through Carry                                                                                                                                                                                          |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                              |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                           |

| Operation:       | See description below                                                                                                                                                                                                 |

| Status Affected: | С                                                                                                                                                                                                                     |

| Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry flag. If 'd' is '0', the<br>result is placed in the W register.<br>If 'd' is '1', the result is placed<br>back in register 'f'. |

|                  | C Register f                                                                                                                                                                                                          |

| SUBLW            | Subtract W from literal    |                                                                                  |  |  |  |  |  |

|------------------|----------------------------|----------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] SUBLW k   |                                                                                  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$        |                                                                                  |  |  |  |  |  |

| Operation:       | $k \text{ - } (W) \to (V)$ | V)                                                                               |  |  |  |  |  |

| Status Affected: | C, DC, Z                   |                                                                                  |  |  |  |  |  |

| Description:     | complemen                  | ster is subtracted (2's<br>t method) from the 8-bit<br>e result is placed in the |  |  |  |  |  |

|                  | <b>C</b> = 0               | W > k                                                                            |  |  |  |  |  |

|                  | <b>C</b> = 1               | $W \leq k$                                                                       |  |  |  |  |  |

DC = 0

**DC** = 1

W<3:0> > k<3:0>

$W < 3:0 > \le k < 3:0 >$

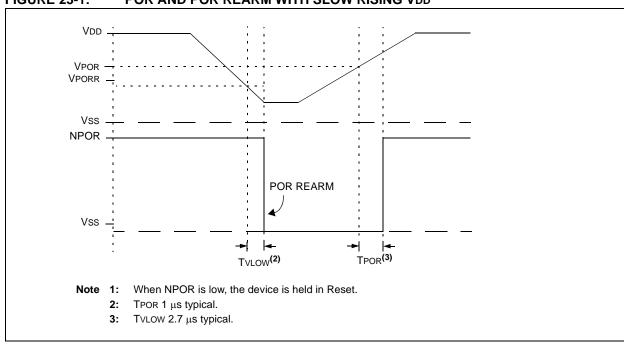

## FIGURE 23-1: POR AND POR REARM WITH SLOW RISING VDD

# 23.3 DC Characteristics: PIC16(L)F722A/723A-I/E (Power-Down)

| PIC16LF722A/723A |                         |          |      |                                                      |                |       |     |                                    |  |  |  |

|------------------|-------------------------|----------|------|------------------------------------------------------|----------------|-------|-----|------------------------------------|--|--|--|

| PIC16F722A/723A  |                         |          |      | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                |       |     | C for industrial                   |  |  |  |

| Param<br>No.     | Device Characteristics  | Min.     | Тур† | Max.<br>+85°C                                        | Max.<br>+125°C | Units |     | Conditions                         |  |  |  |

|                  | Power-down Base Current | (Ipp)(2) |      |                                                      |                |       | VDD | Note                               |  |  |  |

| D020             | Fower-down base current | (IPD)( / | 0.02 | 0.7                                                  | 3.9            | μA    | 1.8 | WDT, BOR, FVR, and T1OSC           |  |  |  |

| D020             |                         |          | 0.02 | 1.0                                                  | 4.3            | μΑ    | 3.0 | disabled, all Peripherals Inactive |  |  |  |

| D020             |                         |          | 4.3  | 10.2                                                 | 4.3            | μΑ    | 1.8 | WDT, BOR, FVR, and T1OSC           |  |  |  |

| 2020             |                         |          | 5    | 10.2                                                 | 18             | μΑ    | 3.0 | disabled, all Peripherals Inactive |  |  |  |

|                  |                         |          | 5.5  | 11.8                                                 | 21             | μΑ    | 5.0 | -                                  |  |  |  |

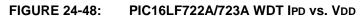

| D021             |                         | _        | 0.5  | 1.7                                                  | 4.1            | μΑ    | 1.8 | LPWDT Current (Note 1)             |  |  |  |

|                  |                         | _        | 0.8  | 2.5                                                  | 4.8            | μA    | 3.0 |                                    |  |  |  |

| D021             |                         |          | 6    | 13.5                                                 | 16.4           | μA    | 1.8 | LPWDT Current (Note 1)             |  |  |  |

|                  |                         | _        | 6.5  | 14.5                                                 | 16.8           | μA    | 3.0 |                                    |  |  |  |

|                  |                         | _        | 7.5  | 16                                                   | 18.7           | μA    | 5.0 |                                    |  |  |  |

| D021A            |                         | —        | 8.5  | 14                                                   | 19             | μA    | 1.8 | FVR current (Note 1. Note 3)       |  |  |  |

|                  |                         | _        | 8.5  | 14                                                   | 20             | μA    | 3.0 |                                    |  |  |  |

| D021A            |                         | —        | 23   | 44                                                   | 48             | μA    | 1.8 | FVR current (Note 1, Note 3,       |  |  |  |

|                  |                         | _        | 25   | 45                                                   | 55             | μA    | 3.0 | Note 5)                            |  |  |  |

|                  |                         | _        | 26   | 60                                                   | 70             | μA    | 5.0 |                                    |  |  |  |

| D022             |                         | _        | —    | _                                                    | _              | μΑ    | 1.8 | BOR Current (Note 1, Note 3)       |  |  |  |

|                  |                         | —        | 7.5  | 12                                                   | 22             | μΑ    | 3.0 |                                    |  |  |  |

| D022             |                         | _        | —    |                                                      | —              | μA    | 1.8 | BOR Current (Note 1, Note 3,       |  |  |  |

|                  |                         |          | 23   | 42                                                   | 49             | μΑ    | 3.0 | Note 5)                            |  |  |  |

|                  |                         | —        | 25   | 46                                                   | 50             | μΑ    | 5.0 |                                    |  |  |  |

| D026             |                         | _        | 0.6  | 2                                                    | —              | μΑ    | 1.8 | T1OSC Current (Note 1)             |  |  |  |

|                  |                         | _        | 1.8  | 3.0                                                  |                | μΑ    | 3.0 |                                    |  |  |  |

| D026             |                         |          | 4.5  | 11.1                                                 |                | μΑ    | 1.8 | T1OSC Current (Note 1)             |  |  |  |

|                  |                         |          | 6    | 12.5                                                 | —              | μΑ    | 3.0 | -                                  |  |  |  |

|                  | —                       |          | 7    | 13.5                                                 |                | μA    | 5.0 |                                    |  |  |  |

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral ∆ current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD.

3: Fixed Voltage Reference is automatically enabled whenever the BOR is enabled.

4: A/D oscillator source is FRC.

5: 0.1 μF capacitor on VCAP (RA0).

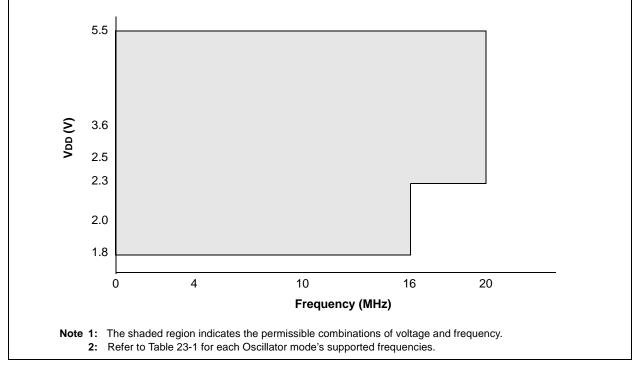

# 23.7 AC Characteristics: PIC16F722A/723A-I/E

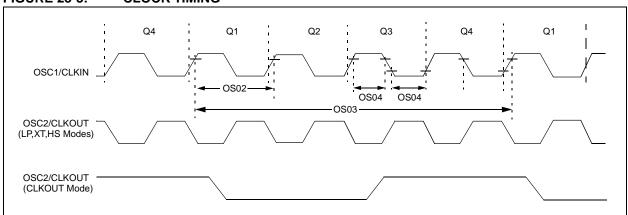

## FIGURE 23-3: CLOCK TIMING

| Param.<br>No. | Symbol | Characteristic |        | Min. | Тур† | Max. | Units | Conditions |

|---------------|--------|----------------|--------|------|------|------|-------|------------|

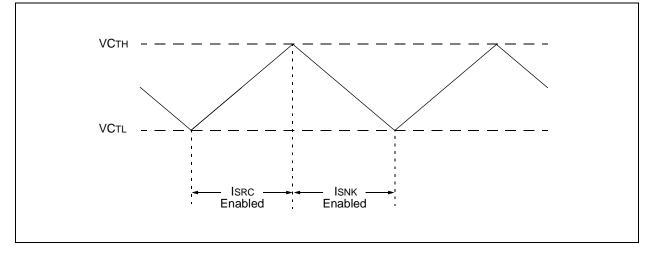

| CS01          | ISRC   | Current Source | High   | —    | -5.8 | -6   | μΑ    |            |

|               |        |                | Medium | —    | -1.1 | -3.2 | μA    | -40, -85°C |

|               |        |                | Low    | —    | -0.2 | -0.9 | μA    |            |

| CS02          | ISNK   | Current Sink   | High   | —    | 6.6  | 6    | μA    |            |

|               |        |                | Medium | —    | 1.3  | 3.2  | μA    | -40, -85°C |

|               |        |                | Low    | —    | 0.24 | 0.9  | μA    |            |

| CS03          | VCHYST | Cap Hysteresis | High   | -    | 525  | —    | mV    |            |

|               |        |                | Medium | _    | 375  |      | mV    | VCTH-VCTL  |

|               |        |                | Low    | _    | 280  |      | mV    |            |

# TABLE 23-14: CAP SENSE OSCILLATOR SPECIFICATIONS

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

FIGURE 23-22: CAP SENSE OSCILLATOR

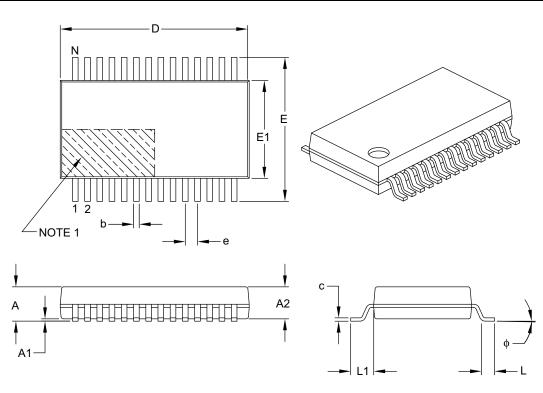

# 28-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

|                          | Units     | MILLIMETERS |          |       |  |

|--------------------------|-----------|-------------|----------|-------|--|

| Dimensio                 | on Limits | MIN         | NOM      | MAX   |  |

| Number of Pins           | Ν         | 28          |          |       |  |

| Pitch                    | е         |             | 0.65 BSC |       |  |

| Overall Height           | Α         | -           | -        | 2.00  |  |

| Molded Package Thickness | A2        | 1.65        | 1.75     | 1.85  |  |

| Standoff                 | A1        | 0.05        | -        | -     |  |

| Overall Width            | Е         | 7.40        | 7.80     | 8.20  |  |

| Molded Package Width     | E1        | 5.00        | 5.30     | 5.60  |  |

| Overall Length           | D         | 9.90        | 10.20    | 10.50 |  |

| Foot Length              | L         | 0.55        | 0.75     | 0.95  |  |

| Footprint                | 1.25 REF  |             |          |       |  |

| Lead Thickness           | С         | 0.09        | -        | 0.25  |  |

| Foot Angle               | ф         | 0°          | 4°       | 8°    |  |

| Lead Width               | b         | 0.22        | -        | 0.38  |  |

### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-073B

NOTES: