Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

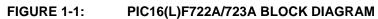

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 192 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 11x8b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-QFN (6x6)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f723a-e-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address                | Name            | Bit 7                                                                                          | Bit 6                                      | Bit 5        | Bit 4         | Bit 3         | Bit 2           | Bit 1        | Bit 0     | Value on:<br>POR, BOR | Page   |

|------------------------|-----------------|------------------------------------------------------------------------------------------------|--------------------------------------------|--------------|---------------|---------------|-----------------|--------------|-----------|-----------------------|--------|

| Bank 2                 |                 |                                                                                                |                                            |              |               |               |                 |              |           |                       |        |

| 100h <sup>(2)</sup>    | INDF            | Addressing                                                                                     | this location                              | uses conter  | nts of FSR to | address data  | a memory (not   | a physical r | egister)  | xxxx xxxx             | 22,30  |

| 101h                   | TMR0            | Timer0 Mod                                                                                     | lule Register                              |              |               |               |                 |              |           | xxxx xxxx             | 91,30  |

| 102h <sup>(2)</sup>    | PCL             | Program Co                                                                                     | ounter's (PC)                              | Least Signi  | ificant Byte  |               |                 |              |           | 0000 0000             | 21,30  |

| 103h <sup>(2)</sup>    | STATUS          | IRP                                                                                            | RP1                                        | RP0          | TO            | PD            | Z               | DC           | С         | 0001 1xxx             | 18,30  |

| 104h <sup>(2)</sup>    | FSR             | Indirect Dat                                                                                   | a Memory A                                 | ddress Point | ter           | •             | •               |              |           | xxxx xxxx             | 22,30  |

| 105h                   | —               | Unimpleme                                                                                      | nted                                       |              |               |               |                 |              |           | _                     | _      |

| 106h                   | —               | Unimpleme                                                                                      | nted                                       |              |               |               |                 |              |           | _                     | _      |

| 107h                   | —               | Unimpleme                                                                                      | nted                                       |              |               |               |                 |              |           | _                     | _      |

| 108h                   | CPSCON0         | CPSON                                                                                          | _                                          | _            | _             | CPSRNG1       | CPSRNG0         | CPSOUT       | TOXCS     | 0 0000                | 112,31 |

| 109h                   | CPSCON1         | _                                                                                              | _                                          | _            | _             | _             | CPSCH2          | CPSCH1       | CPSCH0    | 0000                  | 113,31 |

| 10Ah <sup>(1, 2)</sup> | PCLATH          | —                                                                                              | —                                          | —            | Write Buffer  | for the upper | r 5 bits of the | Program Cou  | unter     | 0 0000                | 21,30  |

| 10Bh <sup>(2)</sup>    | INTCON          | GIE                                                                                            | PEIE                                       | TOIE         | INTE          | RBIE          | T0IF            | INTF         | RBIF      | 0000 000x             | 36,30  |

| 10Ch                   | PMDATL          | Program Me                                                                                     | Program Memory Read Data Register Low Byte |              |               |               |                 |              |           | xxxx xxxx             | 167,31 |

| 10Dh                   | PMADRL          | Program Memory Read Address Register Low Byte                                                  |                                            |              |               |               | xxxx xxxx       | 167,31       |           |                       |        |

| 10Eh                   | PMDATH          | — Program Memory Read Data Register High Byte                                                  |                                            |              |               |               | xx xxxx         | 167,31       |           |                       |        |

| 10Fh                   | PMADRH          | — — Program Memory Read Address Register High Byte                                             |                                            |              |               |               | e               | x xxxx       | 167,31    |                       |        |

| Bank 3                 |                 |                                                                                                |                                            |              |               |               |                 |              |           |                       |        |

| 180h <sup>(2)</sup>    | INDF            | Addressing this location uses contents of FSR to address data memory (not a physical register) |                                            |              |               |               | xxxx xxxx       | 22,30        |           |                       |        |

| 181h                   | OPTION_REG      | RBPU                                                                                           | INTEDG                                     | TOCS         | TOSE          | PSA           | PS2             | PS1          | PS0       | 1111 1111             | 19,30  |

| 182h <sup>(2)</sup>    | PCL             | Program Counter (PC) Least Significant Byte                                                    |                                            |              |               |               | 0000 0000       | 21,30        |           |                       |        |

| 183h <sup>(2)</sup>    | STATUS          | IRP                                                                                            | RP1                                        | RP0          | TO            | PD            | Z               | DC           | С         | 0001 1xxx             | 18,30  |

| 184h <sup>(2)</sup>    | FSR             | Indirect Dat                                                                                   | Indirect Data Memory Address Pointer       |              |               |               |                 |              | xxxx xxxx | 22,30                 |        |

| 185h                   | ANSELA          | _                                                                                              | _                                          | ANSA5        | ANSA4         | ANSA3         | ANSA2           | ANSA1        | ANSA0     | 11 1111               | 44,31  |

| 186h                   | ANSELB          | —                                                                                              | _                                          | ANSB5        | ANSB4         | ANSB3         | ANSB2           | ANSB1        | ANSB0     | 11 1111               | 53,31  |

| 187h                   | —               | Unimpleme                                                                                      | nted                                       |              |               |               |                 |              |           | —                     | _      |

| 18Ah <sup>(1, 2)</sup> | PCLATH          | _                                                                                              | _                                          | _            | Write Buffer  | for the upper | r 5 bits of the | Program Cou  | unter     | 0 0000                | 21,30  |

| 18Bh <sup>(2)</sup>    | INTCON          | GIE                                                                                            | PEIE                                       | TOIE         | INTE          | RBIE          | T0IF            | INTF         | RBIF      | 0000 000x             | 36,30  |

| 18Ch                   | PMCON1          | Reserved                                                                                       | —                                          | —            | —             | —             | —               | —            | RD        | 10                    | 168,31 |

| 18Dh                   | —               | Unimplemented                                                                                  |                                            |              |               |               | —               | _            |           |                       |        |

| 18Eh                   | _               | Unimplemented                                                                                  |                                            |              |               |               | —               | —            |           |                       |        |

| 18Fh                   | — Unimplemented |                                                                                                |                                            |              |               |               |                 | _            | —         |                       |        |

#### TABLE 2-1: PIC16(L)F722A/723A SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

**Legend:** x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter.

2: These registers can be addressed from any bank.

**3:** Accessible only when SSPM<3:0 > = 1001.

4: Accessible only when SSPM<3:0>  $\neq$  1001.

5: This bit is always '1' as RE3 is input-only.

| POR | BOR | то | PD | Condition                                               |

|-----|-----|----|----|---------------------------------------------------------|

| 0   | x   | 1  | 1  | Power-on Reset or LDO Reset                             |

| 0   | x   | 0  | x  | Illegal, TO is set on POR                               |

| 0   | x   | x  | 0  | Illegal, PD is set on POR                               |

| 1   | 0   | 1  | 1  | Brown-out Reset                                         |

| 1   | 1   | 0  | 1  | WDT Reset                                               |

| 1   | 1   | 0  | 0  | WDT Wake-up                                             |

| 1   | 1   | u  | u  | MCLR Reset during normal operation                      |

| 1   | 1   | 1  | 0  | MCLR Reset during Sleep or interrupt wake-up from Sleep |

#### TABLE 3-1: STATUS BITS AND THEIR SIGNIFICANCE

#### TABLE 3-2: RESET CONDITION FOR SPECIAL REGISTERS<sup>(2)</sup>

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 0000h                 | 0001 1xxx          | 0x               |

| MCLR Reset during normal operation | 0000h                 | 000u uuuu          | uu               |

| MCLR Reset during Sleep            | 0000h                 | 0001 Ouuu          | uu               |

| WDT Reset                          | 0000h                 | 0000 luuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 0000h                 | 0001 luuu          | u0               |

| Interrupt Wake-up from Sleep       | PC + 1 <sup>(1)</sup> | uuul Ouuu          | uu               |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and Global Enable bit (GIE) is set, the return address is pushed on the stack and PC is loaded with the interrupt vector (0004h) after execution of PC + 1.

**2:** If a Status bit is not implemented, that bit will be read as '0'.

#### 4.3 Interrupts During Sleep

Some interrupts can be used to wake from Sleep. To wake from Sleep, the peripheral must be able to operate without the system clock. The interrupt source must have the appropriate interrupt enable bit(s) set prior to entering Sleep.

On waking from Sleep, if the GIE bit is also set, the processor will branch to the interrupt vector. Otherwise, the processor will continue executing instructions after the SLEEP instruction. The instruction directly after the SLEEP instruction will always be executed before branching to the ISR. Refer to **Section 19.0 "Power-Down Mode (Sleep)"** for more details.

#### 4.4 INT Pin

The external interrupt, INT pin, causes an asynchronous, edge-triggered interrupt. The INTEDG bit of the OPTION register determines on which edge the interrupt will occur. When the INTEDG bit is set, the rising edge will cause the interrupt. When the INTEDG bit is clear, the falling edge will cause the interrupt. The INTF bit of the INTCON register will be set when a valid edge appears on the INT pin. If the GIE and INTE bits are also set, the processor will redirect program execution to the interrupt vector. This interrupt is disabled by clearing the INTE bit of the INTCON register.

#### 4.5 Context Saving

When an interrupt occurs, only the return PC value is saved to the stack. If the ISR modifies or uses an instruction that modifies key registers, their values must be saved at the beginning of the ISR and restored when the ISR completes. This prevents instructions following the ISR from using invalid data. Examples of key registers include the W, STATUS, FSR and PCLATH registers.

| Note: | The microcontroller does not normally    |

|-------|------------------------------------------|

|       | require saving the PCLATH register.      |

|       | However, if computed GOTO's are used,    |

|       | the PCLATH register must be saved at the |

|       | beginning of the ISR and restored when   |

|       | the ISR is complete to ensure correct    |

|       | program flow.                            |

The code shown in Example 4-1 can be used to do the following.

- · Save the W register

- Save the STATUS register

- Save the PCLATH register

- Execute the ISR program

- Restore the PCLATH register

- Restore the STATUS register

- · Restore the W register

Since most instructions modify the W register, it must be saved immediately upon entering the ISR. The SWAPF instruction is used when saving and restoring the W and STATUS registers because it will not affect any bits in the STATUS register. It is useful to place  $W_{TEMP}$  in shared memory because the ISR cannot predict which bank will be selected when the interrupt occurs.

The processor will branch to the interrupt vector by loading the PC with 0004h. The PCLATH register will remain unchanged. This requires the ISR to ensure that the PCLATH register is set properly before using an instruction that causes PCLATH to be loaded into the PC. See **Section 2.3 "PCL and PCLATH"** for details on PC operation.

EXAMPLE 4-1: SAVING W, STATUS AND PCLATH REGISTERS IN RAM

| —                      | ;Copy W to W_TEMP register<br>;Swap status to be saved into W<br>;Swaps are used because they do not affect the status bits |  |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|

| BANKSELSTATUS_TEMP     | ;Select regardless of current bank                                                                                          |  |

| MOVWF STATUS_TEMP      | ;Copy status to bank zero STATUS_TEMP register                                                                              |  |

| MOVF PCLATH,W          | ;Copy PCLATH to W register                                                                                                  |  |

| MOVWF PCLATH_TEMP<br>: | ;Copy W register to PCLATH_TEMP                                                                                             |  |

| :(ISR)<br>:            | ;Insert user code here                                                                                                      |  |

| BANKSELSTATUS_TEMP     | ;Select regardless of current bank                                                                                          |  |

| MOVF PCLATH_TEMP,W     | ;                                                                                                                           |  |

| MOVWF PCLATH           | ;Restore PCLATH                                                                                                             |  |

| SWAPFSTATUS_TEMP,W     | ;Swap STATUS_TEMP register into W                                                                                           |  |

|                        | ;(sets bank to original state)                                                                                              |  |

| MOVWFSTATUS            | ;Move W into STATUS register                                                                                                |  |

| SWAPFW_TEMP,F          | ;Swap W_TEMP                                                                                                                |  |

| SWAPFW_TEMP,W          | ;Swap W_TEMP into W                                                                                                         |  |

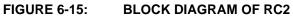

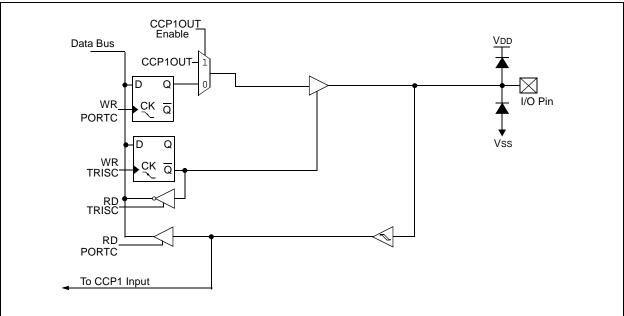

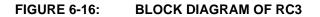

## 6.2.2 PIN DESCRIPTIONS AND DIAGRAMS

Each PORTA pin is multiplexed with other functions. The pins and their combined functions are briefly described here. For specific information about individual functions such as the A/D Converter (ADC), refer to the appropriate section in this data sheet.

#### 6.2.2.1 RA0/AN0/SS/VCAP

Figure 6-1 shows the diagram for this pin. This pin is configurable to function as one of the following:

- General purpose I/O

- Analog input for the ADC

- Slave select input for the SSP(1)

- Voltage regulator capacitor pin (PIC16F722A/ 723A only)

## Note 1: SS pin location may be selected as RA5 or RA0.

#### 6.2.2.2 RA1/AN1

Figure 6-2 shows the diagram for this pin. This pin is configurable to function as one of the following:

- General purpose I/O

- Analog input for the ADC

#### 6.2.2.3 RA2/AN2

Figure 6-2 shows the diagram for this pin. This pin is configurable to function as one of the following:

- General purpose I/O

- Analog input for the ADC

#### 6.2.2.4 RA3/AN3/VREF

Figure 6-2 shows the diagram for this pin. This pin is configurable to function as one of the following:

- General purpose I/O

- · Analog input for the ADC

- Voltage reference input for the ADC

#### 6.2.2.5 RA4/CPS6/T0CKI

Figure 6-3 shows the diagram for this pin. This pin is configurable to function as one of the following:

- General purpose I/O

- Capacitive sensing input

- Clock input for Timer0

The Timer0 clock input function works independently of any TRIS register setting. Effectively, if TRISA4 = 0, the PORTA4 register bit will output to the pad and clock Timer0 at the same time.

#### 6.2.2.6 RA5/AN4/CPS7/SS/VCAP

Figure 6-4 shows the diagram for this pin. This pin is configurable to function as one of the following:

- General purpose I/O

- Analog input for the ADC

- · Capacitive sensing input

- Slave select input for the SSP<sup>(1)</sup>

- Voltage regulator capacitor pin (PIC16F722A/ 723A only)

**Note 1:** SS pin location may be selected as RA5 or RA0.

#### 6.2.2.7 RA6/OSC2/CLKOUT/VCAP

Figure 6-5 shows the diagram for this pin. This pin is configurable to function as one of the following:

- General purpose I/O

- Crystal/resonator connection

- Clock output

- Voltage regulator capacitor pin (PIC16F722A/ 723A only)

#### 6.2.2.8 RA7/OSC1/CLKIN

Figure 6-6 shows the diagram for this pin. This pin is configurable to function as one of the following:

- General purpose I/O

- Crystal/resonator connection

- Clock input

#### 8.2 Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out using ICSP<sup>TM</sup> for verification purposes.

| Note: | The entire Flash program memory will be   |  |  |  |

|-------|-------------------------------------------|--|--|--|

|       | erased when the code protection is turned |  |  |  |

|       | off. See the "PIC16(L)F72X Memory         |  |  |  |

|       | Programming Specification" (DS41332)      |  |  |  |

|       | for more information.                     |  |  |  |

#### 8.3 User ID

Four memory locations (2000h-2003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution, but are readable and writable during Program/Verify mode. Only the Least Significant 7 bits of the ID locations are reported when using MPLAB IDE. See the *"PIC16(L)F72X Memory Programming Specification"* (DS41332) for more information.

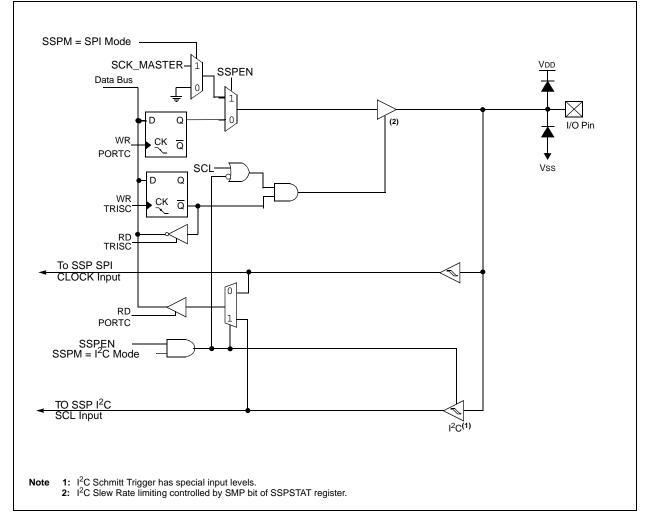

#### 15.2 Compare Mode

In Compare mode, the 16-bit CCPRx register value is constantly compared against the TMR1 register pair value. When a match occurs, the CCPx module may:

- Toggle the CCPx output

- Set the CCPx output

- · Clear the CCPx output

- Generate a Special Event Trigger

- Generate a Software Interrupt

The action on the pin is based on the value of the CCPxM<3:0> control bits of the CCPxCON register.

All Compare modes can generate an interrupt.

#### FIGURE 15-2: COMPARE MODE OPERATION BLOCK DIAGRAM

- Special Event Trigger will:

- Clear TMR1H and TMR1L registers.

- NOT set interrupt flag bit TMR1IF of the PIR1 register.

Set the GO/DONE bit to start the ADC conversion

(CCP2 only).

#### 15.2.1 CCPx PIN CONFIGURATION

The user must configure the CCPx pin as an output by clearing the associated TRIS bit.

Either RC1 or RB3 can be selected as the CCP2 pin. Refer to **Section 6.1** "Alternate Pin Function" for more information.

Note: Clearing the CCPxCON register will force the CCPx compare output latch to the default low level. This is not the PORT I/O data latch.

#### 15.2.2 TIMER1 MODE SELECTION

In Compare mode, Timer1 must be running in either Timer mode or Synchronized Counter mode. The compare operation may not work in Asynchronous Counter mode.

| Note: | Clocking Timer1 from the system clock  |

|-------|----------------------------------------|

|       | (Fosc) should not be used in Compare   |

|       | mode. For the Compare operation of the |

|       | TMR1 register to the CCPRx register to |

|       | occur, Timer1 must be clocked from the |

|       | instruction clock (Fosc/4) or from an  |

|       | external clock source.                 |

#### 15.2.3 SOFTWARE INTERRUPT MODE

When Software Interrupt mode is chosen (CCPxM<3:0> = 1010), the CCPxIF bit in the PIRx register is set and the CCPx module does not assert control of the CCPx pin (refer to the CCPxCON register).

#### 15.2.4 SPECIAL EVENT TRIGGER

When Special Event Trigger mode is chosen (CCPxM<3:0> = 1011), the CCPx module does the following:

- Resets Timer1

- Starts an ADC conversion if ADC is enabled (CCP2 only)

The CCPx module does not assert control of the CCPx pin in this mode (refer to the CCPxCON register).

The Special Event Trigger output of the CCP occurs immediately upon a match between the TMR1H, TMR1L register pair and the CCPRxH, CCPRxL register pair. The TMR1H, TMR1L register pair is not reset until the next rising edge of the Timer1 clock. This allows the CCPRxH, CCPRxL register pair to effectively provide a 16-bit programmable period register for Timer1.

- Note 1: The Special Event Trigger from the CCP module does not set interrupt flag bit TMR1IF of the PIR1 register.

- 2: Removing the match condition by changing the contents of the CCPRxH and CCPRxL register pair, between the clock edge that generates the Special Event Trigger and the clock edge that generates the Timer1 Reset, will preclude the Reset from occurring.

#### 15.2.5 COMPARE DURING SLEEP

The Compare mode is dependent upon the system clock (Fosc) for proper operation. Since Fosc is shut down during Sleep mode, the Compare mode will not function properly during Sleep.

#### 16.1.1.4 TSR Status

The TRMT bit of the TXSTA register indicates the status of the TSR register. This is a read-only bit. The TRMT bit is set when the TSR register is empty and is cleared when a character is transferred to the TSR register from the TXREG. The TRMT bit remains clear until all bits have been shifted out of the TSR register. No interrupt logic is tied to this bit, so the user has to poll this bit to determine the TSR status.

| Note: | The TSR register is not mapped in data      |

|-------|---------------------------------------------|

|       | memory, so it is not available to the user. |

#### 16.1.1.5 Transmitting 9-Bit Characters

The AUSART supports 9-bit character transmissions. When the TX9 bit of the TXSTA register is set, the AUSART will shift nine bits out for each character transmitted. The TX9D bit of the TXSTA register is the ninth, and Most Significant, data bit. When transmitting 9-bit data, the TX9D data bit must be written before writing the eight Least Significant bits into the TXREG. All nine bits of data will be transferred to the TSR shift register immediately after the TXREG is written.

A special 9-bit Address mode is available for use with multiple receivers. Refer to **Section 16.1.2.7** "**Address Detection**" for more information on the Address mode.

#### 16.1.1.6 Asynchronous Transmission Setup:

- Initialize the SPBRG register and the BRGH bit to achieve the desired baud rate (Refer to Section 16.2 "AUSART Baud Rate Generator (BRG)").

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If 9-bit transmission is desired, set the TX9 control bit. A set ninth data bit will indicate that the eight Least Significant data bits are an address when the receiver is set for address detection.

- Enable the transmission by setting the TXEN control bit. This will cause the TXIF interrupt bit to be set.

- If interrupts are desired, set the TXIE interrupt enable bit of the PIE1 register. An interrupt will occur immediately provided that the GIE and PEIE bits of the INTCON register are also set.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded into the TX9D data bit.

- 7. Load 8-bit data into the TXREG register. This will start the transmission.

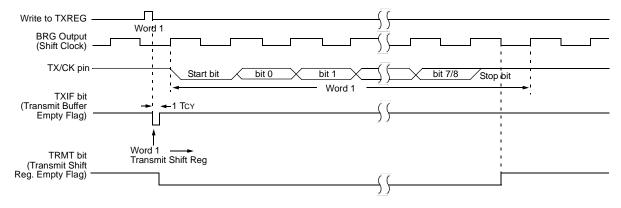

### FIGURE 16-3: ASYNCHRONOUS TRANSMISSION

#### 16.3.1.4 Synchronous Master Reception

Data is received at the RX/DT pin. The RX/DT pin output driver is automatically disabled when the AUSART is configured for synchronous master receive operation.

In Synchronous mode, reception is enabled by setting either the Single Receive Enable bit (SREN of the RCSTA register) or the Continuous Receive Enable bit (CREN of the RCSTA register).

When SREN is set and CREN is clear, only as many clock cycles are generated as there are data bits in a single character. The SREN bit is automatically cleared at the completion of one character. When CREN is set, clocks are continuously generated until CREN is cleared. If CREN is cleared in the middle of a character the CK clock stops immediately and the partial character is discarded. If SREN and CREN are both set, then SREN is cleared at the completion of the first character and CREN takes precedence.

To initiate reception, set either SREN or CREN. Data is sampled at the RX/DT pin on the trailing edge of the TX/CK clock pin and is shifted into the Receive Shift Register (RSR). When a complete character is received into the RSR, the RCIF bit of the PIR1 register is set and the character is automatically transferred to the two character receive FIFO. The Least Significant eight bits of the top character in the receive FIFO are available in RCREG. The RCIF bit remains set as long as there are un-read characters in the receive FIFO.

#### 16.3.1.5 Slave Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a slave receives the clock on the TX/CK line. The TX/ CK pin output driver is automatically disabled when the device is configured for synchronous slave transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One data bit is transferred for each clock cycle. Only as many clock cycles should be received as there are data bits.

#### 16.3.1.6 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before RCREG is read to access the FIFO. When this happens the OERR bit of the RCSTA register is set. Previous data in the FIFO will not be overwritten. The two characters in the FIFO buffer can be read, however, no additional characters will be received until the error is cleared. The OERR bit can only be cleared by clearing the overrun condition. If the overrun error occurred when the SREN bit is set and CREN is clear then the error is cleared by reading RCREG. If the overrun occurred when the CREN bit is set then the error condition is cleared by either clearing the CREN bit of the RCSTA register.

#### 16.3.1.7 Receiving 9-bit Characters

The AUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set, the AUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth, and Most Significant, data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREG.

Address detection in Synchronous modes is not supported, therefore the ADDEN bit of the RCSTA register must be cleared.

### 16.3.1.8 Synchronous Master Reception Setup:

- 1. Initialize the SPBRG register for the appropriate baud rate. Set or clear the BRGH bit, as required, to achieve the desired baud rate.

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Ensure bits CREN and SREN are clear.

- 4. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit reception is desired, set bit RX9.

- 6. Verify address detection is disabled by clearing the ADDEN bit of the RCSTA register.

- 7. Start reception by setting the SREN bit or for continuous reception, set the CREN bit.

- Interrupt flag bit RCIF of the PIR1 register will be set when reception of a character is complete. An interrupt will be generated if the RCIE interrupt enable bit of the PIE1 register was set.

- 9. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 10. Read the 8-bit received data by reading the RCREG register.

- 11. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit, which resets the AUSART.

#### 17.1.2 SLAVE MODE

For any SPI device acting as a slave, the data is transmitted and received as external clock pulses appear on SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

#### 17.1.2.1 Slave Mode Operation

The SSP consists of a transmit/receive shift register (SSPSR) and a buffer register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR until the received data is ready.

The slave has no control as to when data will be clocked in or out of the device. All data that is to be transmitted, to a master or another slave, must be loaded into the SSPBUF register before the first clock pulse is received.

Once eight bits of data have been received:

- · Received byte is moved to the SSPBUF register

- BF bit of the SSPSTAT register is set

- SSPIF bit of the PIR1 register is set

Any write to the SSPBUF register during transmission/ reception of data will be ignored and the Write Collision Detect bit, WCOL of the SSPCON register, will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPBUF register completed successfully.

The user's firmware must read SSPBUF, clearing the BF flag, or the SSPOV bit of the SSPCON register will be set with the reception of the next byte and communication will be disabled.

A SPI module transmits and receives at the same time, occasionally causing dummy data to be transmitted/ received. It is up to the user to determine which data is to be used and what can be discarded.

#### 17.1.2.2 Enabling Slave I/O

To enable the serial port, the SSPEN bit of the SSPCON register must be set. If a Slave mode of operation is selected in the SSPM bits of the SSPCON register, the SDI, SDO and SCK pins will be assigned as serial port pins.

For these pins to function as serial port pins, they must have their corresponding data direction bits set or cleared in the associated TRIS register as follows:

- · SDI configured as input

- · SDO configured as output

- · SCK configured as input

Optionally, a fourth pin, Slave Select  $(\overline{SS})$  may be used in Slave mode. Slave Select may be configured to operate on one of the following pins via the SSSEL bit in the APFCON register.

- RA5/AN4/SS

- RA0/AN0/SS

Upon selection of a Slave Select pin, the appropriate bits must be set in the ANSELA and TRISA registers. Slave Select must be set as an input by setting the corresponding bit in TRISA, and digital I/O must be enabled on the SS pin by clearing the corresponding bit of the ANSELA register.

#### 17.1.2.3 Slave Mode Setup

When initializing the SSP module to SPI Slave mode, compatibility must be ensured with the master device. This is done by programming the appropriate control bits of the SSPCON and SSPSTAT registers. These control bits allow the following to be specified:

- SCK as clock input

- Idle state of SCK (CKP bit)

- Data input sample phase (SMP bit)

- Output data on rising/falling edge of SCK (CKE bit)

Figure 17-4 and Figure 17-5 show example waveforms of Slave mode operation.

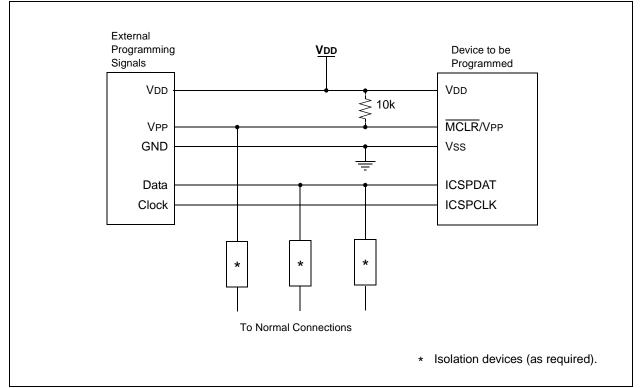

#### 20.0 IN-CIRCUIT SERIAL PROGRAMMING<sup>™</sup> (ICSP<sup>™</sup>)

ICSP<sup>™</sup> programming allows customers to manufacture circuit boards with unprogrammed devices. Programming can be done after the assembly process allowing the device to be programmed with the most recent firmware or a custom firmware. Five pins are needed for ICSP<sup>™</sup> programming:

- ICSPCLK

- ICSPDAT

- MCLR/VPP

- VDD

- Vss

The device is placed into Program/Verify mode by holding the ICSPCLK and ICSPDAT pins low then raising the voltage on MCLR/VPP from 0v to VPP. In Program/Verify mode the Program Memory, User IDs and the Configuration Words are programmed through serial communications. The ICSPDAT pin is a bidirectional I/O used for transferring the serial data and the ISCPCLK pin is the clock input. For more information on ICSP<sup>TM</sup> refer to the "PIC16(L)F72X Memory Programming Specification" (DS41332).

**Note:** The ICD 2 produces a VPP voltage greater than the maximum VPP specification of the PIC16(L)F722A/723A. When using this programmer, an external circuit, such as the AC164112 MPLAB ICD 2 VPP voltage limiter, is required to keep the VPP voltage within the device specifications.

#### FIGURE 20-1: TYPICAL CONNECTION FOR ICSP™ PROGRAMMING

| ADDLW            | Add literal and W                                                                                                      |

|------------------|------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDLW k                                                                                                        |

| Operands:        | $0 \leq k \leq 255$                                                                                                    |

| Operation:       | $(W) + k \to (W)$                                                                                                      |

| Status Affected: | C, DC, Z                                                                                                               |

| Description:     | The contents of the W register<br>are added to the 8-bit literal 'k'<br>and the result is placed in the<br>W register. |

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [label]BCF f,b                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| ADDWF            | Add W and f                                                                                                                                                            |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                      |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                        |  |  |  |  |  |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                  |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                               |  |  |  |  |  |

| Description:     | Add the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |  |  |  |  |  |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| ANDLW            | AND literal with W                                                                                                   |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                             |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                    |  |  |  |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                      |  |  |  |

| Status Affected: | Z                                                                                                                    |  |  |  |

| Description:     | The contents of W register are<br>AND'ed with the 8-bit literal 'k'.<br>The result is placed in the W reg-<br>ister. |  |  |  |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                                     |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BTFSC f,b                                                                                                                                                                                                    |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                           |

| Operation:       | skip if (f <b>) = <math>0</math></b>                                                                                                                                                                                          |

| Status Affected: | None                                                                                                                                                                                                                          |

| Description:     | If bit 'b' in register 'f' is '1', the next<br>instruction is executed.<br>If bit 'b', in register 'f', is '0', the<br>next instruction is discarded, and<br>a NOP is executed instead, making<br>this a 2-cycle instruction. |

| ANDWF            | AND W with f                                                                                                                                                    |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] ANDWF f,d                                                                                                                                               |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                 |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                       |  |  |  |

| Status Affected: | Z                                                                                                                                                               |  |  |  |

| Description:     | AND the W register with register<br>'f'. If 'd' is '0', the result is stored in<br>the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |  |  |  |

| RETFIE           | Return from Interrupt                                                                                                                                                                                              | RET         |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Syntax:          | [ label ] RETFIE                                                                                                                                                                                                   | Synt        |

| Operands:        | None                                                                                                                                                                                                               | Oper        |

| Operation:       | $TOS \rightarrow PC, \\ 1 \rightarrow GIE$                                                                                                                                                                         | Ope         |

| Status Affected: | None                                                                                                                                                                                                               | Statu       |

| Description:     | Return from Interrupt. Stack is<br>POPed and Top-of-Stack (TOS) is<br>loaded in the PC. Interrupts are<br>enabled by setting Global<br>Interrupt Enable bit, GIE<br>(INTCON<7>). This is a 2-cycle<br>instruction. | Desc        |

| Words:           | 1                                                                                                                                                                                                                  | Cycl        |

| Cycles:          | 2                                                                                                                                                                                                                  | <u>Exar</u> |

| Example:         | RETFIE                                                                                                                                                                                                             |             |

|                  | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                                                                             | TABI        |

| RETLW            | Return with literal in W                                                                                                                                                                                                        |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                                                                        |  |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                                                                                                                               |  |  |  |  |  |  |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow PC$                                                                                                                                                                                    |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                            |  |  |  |  |  |  |

| Description:     | The W register is loaded with the<br>8-bit literal 'k'. The program<br>counter is loaded from the top of<br>the stack (the return address).<br>This is a 2-cycle instruction.                                                   |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                               |  |  |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                                               |  |  |  |  |  |  |

| Example:         | CALL TABLE;W contains table                                                                                                                                                                                                     |  |  |  |  |  |  |

| TABLE            | <pre>;offset value<br/>;W now has table value<br/>ADDWF PC ;W = offset<br/>RETLW k1 ;Begin table<br/>RETLW k2 ;<br/>RETLW kn ; End of table<br/>Before Instruction<br/>W = 0x07<br/>After Instruction<br/>W = value of k8</pre> |  |  |  |  |  |  |

| RETURN           | Return from Subroutine                                                                                                                                                                                                          |  |  |  |  |  |  |

| Syntax:          | [label] RETURN                                                                                                                                                                                                                  |  |  |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                                            |  |  |  |  |  |  |

| Operation:       | $TOS \rightarrow PC$                                                                                                                                                                                                            |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                            |  |  |  |  |  |  |

| Description:     | Return from subroutine. The stack<br>is POPed and the top of the stack<br>(TOS) is loaded into the program<br>counter. This is a 2-cycle instruc-<br>tion.                                                                      |  |  |  |  |  |  |

#### 23.4 DC Characteristics: PIC16(L)F722A/723A-I/E (Continued)

| DC CHARACTERISTICS |        |                                                  | Standard Operating Conditions (unless otherwise stated)         Operating temperature -40°C $\leq$ TA $\leq$ +85°C for industrial         -40°C $\leq$ TA $\leq$ +125°C for extended |      |      |       |                                                                         |

|--------------------|--------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|-------------------------------------------------------------------------|

| Param<br>No.       | Sym.   | Characteristic                                   | Min.                                                                                                                                                                                 | Тур† | Max. | Units | Conditions                                                              |

| D130               | Eр     | Cell Endurance                                   | 100                                                                                                                                                                                  | 1k   | —    | E/W   | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$    |

| D131               |        | VDD for Read                                     | Vmin                                                                                                                                                                                 | —    | —    | V     |                                                                         |

|                    |        | Voltage on MCLR/VPP during<br>Erase/Program      | 8.0                                                                                                                                                                                  | _    | 9.0  | V     | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$    |

|                    |        | VDD for Bulk Erase                               | 2.7                                                                                                                                                                                  | 3    | —    | V     | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$    |

| D132               | VPEW   | VDD for Write or Row Erase                       | 2.7                                                                                                                                                                                  | -    | —    | V     | VMIN = Minimum operating voltage<br>VMAX = Maximum operating<br>voltage |

|                    | IPPPGM | Current on MCLR/VPP during<br>Erase/Write        | _                                                                                                                                                                                    | _    | 5.0  | mA    | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$    |

|                    | IDDPGM | Current on VDD during Erase/<br>Write            | _                                                                                                                                                                                    |      | 5.0  | mA    | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$    |

| D133               | TPEW   | Erase/Write cycle time                           | -                                                                                                                                                                                    |      | 2.8  | ms    | Temperature during programming: $10^{\circ}C \le TA \le 40^{\circ}C$    |

| D134               | TRETD  | Characteristic Retention                         | 40                                                                                                                                                                                   | -    | —    | Year  | Provided no other specifications<br>are violated                        |

|                    |        | VCAP Capacitor Charging                          |                                                                                                                                                                                      |      |      |       |                                                                         |

| D135               |        | Charging current                                 |                                                                                                                                                                                      | 200  |      | μΑ    |                                                                         |

| D135A              |        | Source/sink capability when<br>charging complete | _                                                                                                                                                                                    | 0.0  | —    | mA    |                                                                         |

Legend: TBD = To Be Determined

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

2: Negative current is defined as current sourced by the pin.

**3:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

4: Including OSC2 in CLKOUT mode.

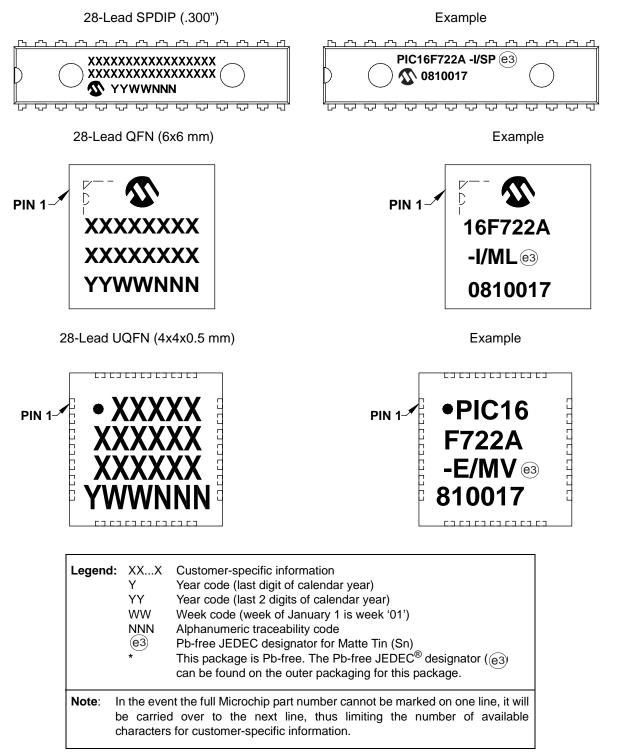

#### 25.0 PACKAGING INFORMATION

#### 25.1 Package Marking Information

\* Standard PICmicro<sup>®</sup> device marking consists of Microchip part number, year code, week code and traceability code. For PICmicro device marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

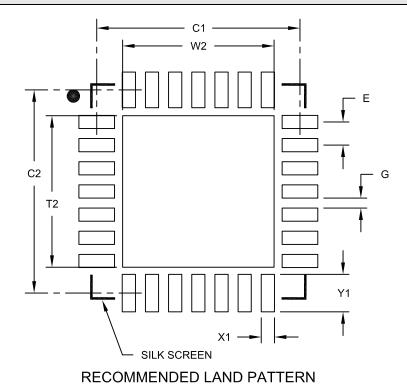

## 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS |      |          |      |

|----------------------------|-------------|------|----------|------|

| Dimension Limits           |             | MIN  | NOM      | MAX  |

| Contact Pitch              | E           |      | 0.65 BSC |      |

| Optional Center Pad Width  | W2          |      |          | 4.25 |

| Optional Center Pad Length | T2          |      |          | 4.25 |

| Contact Pad Spacing        | C1          |      | 5.70     |      |

| Contact Pad Spacing        | C2          |      | 5.70     |      |

| Contact Pad Width (X28)    | X1          |      |          | 0.37 |

| Contact Pad Length (X28)   | Y1          |      |          | 1.00 |

| Distance Between Pads      | G           | 0.20 |          |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2105A

### **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

**Chicago** Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110

**Canada - Toronto** Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan Tel: 86-769-8702-9880

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

**Japan - Osaka** Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

**Taiwan - Kaohsiung** Tel: 886-7-213-7828

Taiwan - Taipei Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

Thailand - Bangkok Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf Tel: 49-2129-3766400

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice Tel: 39-049-7625286

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw Tel: 48-22-3325737

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

07/14/15