Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I²C, SPI, UART/USART                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 192 x 8                                                                   |

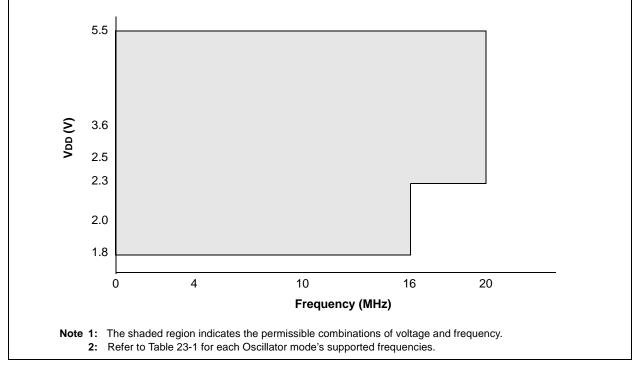

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 11x8b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

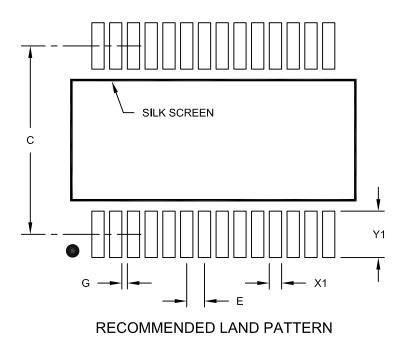

| Package / Case             | 28-UFQFN Exposed Pad                                                      |

| Supplier Device Package    | 28-UQFN (4x4)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f723a-e-mv |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS3000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

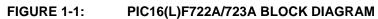

# PIC16(L)F722A/723A

# PIC16(L)F722A/723A

| Address               | Name                  | Bit 7         | Bit 6         | Bit 5                     | Bit 4         | Bit 3                 | Bit 2           | Bit 1          | Bit 0    | Value on:<br>POR, BOR | Page   |

|-----------------------|-----------------------|---------------|---------------|---------------------------|---------------|-----------------------|-----------------|----------------|----------|-----------------------|--------|

| Bank 1                |                       |               |               |                           |               |                       |                 |                |          |                       |        |

| 80h <sup>(2)</sup>    | INDF                  | Addressing    | this location | uses conter               | nts of FSR to | address data          | a memory (no    | t a physical r | egister) | xxxx xxxx             | 22,30  |

| 81h                   | OPTION_REG            | RBPU          | INTEDG        | TOCS                      | TOSE          | PSA                   | PS2             | PS1            | PS0      | 1111 1111             | 19,30  |

| 82h <sup>(2)</sup>    | PCL                   | Program Co    | ounter (PC) L | east Signifie             | cant Byte     |                       |                 |                |          | 0000 0000             | 21,30  |

| 83h <sup>(2)</sup>    | STATUS                | IRP           | RP1           | RP0                       | TO            | PD                    | Z               | DC             | С        | 0001 1xxx             | 18,30  |

| 84h <sup>(2)</sup>    | FSR                   | Indirect Data | a Memory A    | ddress Point              | ter           |                       |                 |                |          | xxxx xxxx             | 22,30  |

| 85h                   | TRISA                 | TRISA7        | TRISA6        | TRISA5                    | TRISA4        | TRISA3                | TRISA2          | TRISA1         | TRISA0   | 1111 1111             | 43,30  |

| 86h                   | TRISB                 | TRISB7        | TRISB6        | TRISB5                    | TRISB4        | TRISB3                | TRISB2          | TRISB1         | TRISB0   | 1111 1111             | 52,30  |

| 87h                   | TRISC                 | TRISC7        | TRISC6        | TRISC5                    | TRISC4        | TRISC3                | TRISC2          | TRISC1         | TRISC0   | 1111 1111             | 62,30  |

| 89h                   | TRISE                 | _             |               |                           | _             | TRISE3 <sup>(5)</sup> | _               | _              | _        | 1111                  | 69,30  |

| 8Ah <sup>(1, 2)</sup> | PCLATH                | _             |               |                           | Write Buffer  | for the upper         | r 5 bits of the | Program Co     | unter    | 0 0000                | 21,30  |

| 8Bh <sup>(2)</sup>    | INTCON                | GIE           | PEIE          | TOIE                      | INTE          | RBIE                  | T0IF            | INTF           | RBIF     | x000 000x             | 36,30  |

| 8Ch                   | PIE1                  | TMR1GIE       | ADIE          | RCIE                      | TXIE          | SSPIE                 | CCP1IE          | TMR2IE         | TMR1IE   | 0000 0000             | 37,31  |

| 8Dh                   | PIE2                  | —             | -             | -                         | —             | —                     | _               | —              | CCP2IE   | 0                     | 38,31  |

| 8Eh                   | PCON                  | _             |               |                           | _             | _                     | _               | POR            | BOR      | dd                    | 20,31  |

| 8Fh                   | T1GCON                | TMR1GE        | T1GPOL        | T1GTM                     | T1GSPM        | T1GGO<br>DONE         | T1GVAL          | T1GSS1         | T1GSS0   | 0000 0x00             | 104,31 |

| 90h                   | OSCCON                | —             | -             | IRCF1                     | IRCF0         | ICSL                  | ICSS            | —              | _        | 10 qq                 | 73,31  |

| 91h                   | OSCTUNE               | —             |               | TUN5                      | TUN4          | TUN3                  | TUN2            | TUN1           | TUN0     | 00 0000               | 74,31  |

| 92h                   | PR2                   | Timer2 Peri   | od Register   |                           |               |                       |                 |                |          | 1111 1111             | 106,31 |

| 93h                   | SSPADD(4)             | Synchronou    | s Serial Port | t (I <sup>2</sup> C mode) | Address Reg   | ister                 |                 |                |          | 0000 0000             | 155,31 |

| 93h                   | SSPMSK <sup>(3)</sup> | Synchronou    | s Serial Port | t (I <sup>2</sup> C mode) | Address Mas   | k Register            |                 |                |          | 1111 1111             | 166,31 |

| 94h                   | SSPSTAT               | SMP           | CKE           | D/A                       | Р             | S                     | R/W             | UA             | BF       | 0000 0000             | 153,31 |

| 95h                   | WPUB                  | WPUB7         | WPUB6         | WPUB5                     | WPUB4         | WPUB3                 | WPUB2           | WPUB1          | WPUB0    | 1111 1111             | 52,31  |

| 96h                   | IOCB                  | IOCB7         | IOCB6         | IOCB5                     | IOCB4         | IOCB3                 | IOCB2           | IOCB1          | IOCB0    | 0000 0000             | 53,31  |

| 97h                   |                       | Unimpleme     | nted          |                           |               |                       |                 |                |          | _                     |        |

| 98h                   | TXSTA                 | CSRC          | TX9           | TXEN                      | SYNC          | _                     | BRGH            | TRMT           | TX9D     | 0000 -010             | 133,31 |

| 99h                   | SPBRG                 | BRG7          | BRG6          | BRG5                      | BRG4          | BRG3                  | BRG2            | BRG1           | BRG0     | 0000 0000             | 135,31 |

| 9Ah                   | _                     | Unimpleme     | nted          |                           |               |                       |                 |                |          | —                     | —      |

| 9Bh                   | —                     | Unimpleme     | nted          |                           |               |                       |                 |                |          | _                     | _      |

| 9Ch                   | APFCON                | _             | _             | _                         | _             | —                     | _               | SSSEL          | CCP2SEL  | 00                    | 42,31  |

| 9Dh                   | FVRCON                | FVRRDY        | FVREN         | —                         | _             | _                     | _               | ADFVR1         | ADFVR0   | q000                  | 90,31  |

| 9Eh                   | —                     | Unimpleme     | nted          |                           |               |                       |                 |                |          | _                     | —      |

| 9Fh                   | ADCON1                | _             | ADCS2         | ADCS1                     | ADCS0         | _                     | _               | ADREF1         | ADREF0   | 000000                | 86,31  |

#### TABLE 2-1:PIC16(L)F722A/723A SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.

Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter.

**2:** These registers can be addressed from any bank.

3: Accessible only when SSPM<3:0> = 1001.

4: Accessible only when SSPM<3:0>  $\neq$  1001.

5: This bit is always '1' as RE3 is input-only.

#### 2.2.2.2 **OPTION** register

The OPTION register, shown in Register 2-2, is a readable and writable register, which contains various control bits to configure:

- Timer0/WDT prescaler

- External RB0/INT interrupt

- Timer0

- Weak pull ups on PORTB

Note: To achieve a 1:1 prescaler assignment for Timer0, assign the prescaler to the WDT by setting PSA bit of the OPTION register to '1'. Refer to Section 12.3 "Timer1 Prescaler".

bit 0

| <b>REGISTER 2-</b> | 2: OPTIO | N_REG: OP | FION REGIS | TER   |       |       |       |

|--------------------|----------|-----------|------------|-------|-------|-------|-------|

| R/W-1              | R/W-1    | R/W-1     | R/W-1      | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

| RBPU               | INTEDG   | TOCS      | TOSE       | PSA   | PS2   | PS1   | PS0   |

| bit 7              |          |           |            |       |       |       | bit   |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7   | RBPU: PORTB Pull-up Enable bit                                                                                     |

|---------|--------------------------------------------------------------------------------------------------------------------|

|         | 1 = PORTB pull ups are disabled                                                                                    |

|         | 0 = PORTB pull ups are enabled by individual bits in the WPUB register                                             |

| bit 6   | INTEDG: Interrupt Edge Select bit                                                                                  |

|         | <ul><li>1 = Interrupt on rising edge of RB0/INT pin</li><li>0 = Interrupt on falling edge of RB0/INT pin</li></ul> |

| bit 5   | TOCS: Timer0 Clock Source Select bit                                                                               |

|         | <ul><li>1 = Transition on RA4/T0CKI pin</li><li>0 = Internal instruction cycle clock (Fosc/4)</li></ul>            |

| bit 4   | T0SE: Timer0 Source Edge Select bit                                                                                |

|         | 1 = Increment on high-to-low transition on RA4/T0CKI pin                                                           |

|         | 0 = Increment on low-to-high transition on RA4/T0CKI pin                                                           |

| bit 3   | PSA: Prescaler Assignment bit                                                                                      |

|         | 1 = Prescaler is assigned to the WDT                                                                               |

|         | 0 = Prescaler is assigned to the Timer0 module                                                                     |

| bit 2-0 | PS<2:0>: Prescaler Rate Select bits                                                                                |

|         | Bit Value Timer0 Rate WDT Rate                                                                                     |

|         | 000 1:2 1:1                                                                                                        |

|         |                                                                                                                    |

|         | 010   1:8   1:4<br>011   1:16   1:8                                                                                |

|         |                                                                                                                    |

|         | 101 1:64 1:32                                                                                                      |

|         | 110 1:128 1:64                                                                                                     |

|         | 111 <b>1:256 1:128</b>                                                                                             |

# 6.2 PORTA and the TRISA Registers

PORTA is a 8-bit wide, bidirectional port. The corresponding data direction register is TRISA (Register 6-3). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). Example 6-1 shows how to initialize PORTA.

Reading the PORTA register (Register 6-2) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch.

The TRISA register (Register 6-3) controls the PORTA pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the

**REGISTER 6-2:** PORTA: PORTA REGISTER R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x RA6 RA5 RA2 RA7 RA4 RA3 RA1 RA0 bit 7 bit 0

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 RA<7:0>: PORTA I/O Pin bit

1 = Port pin is > VIH 0 = Port pin is < VIL

# REGISTER 6-3: TRISA: PORTA TRI-STATE REGISTER

| R/W-1  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 7-0 TRISA<7:0>: PORTA Tri-State Control bit

1 = PORTA pin configured as an input (tri-stated)

0 = PORTA pin configured as an output

TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

| Note: | The ANSELA register must be initialized     |

|-------|---------------------------------------------|

|       | to configure an analog channel as a digital |

|       | input. Pins configured as analog inputs     |

|       | will read '0'.                              |

| BANKSEL PORTA ;<br>CLRF PORTA ;Init PORTA<br>BANKSEL ANSELA ;<br>CLRF ANSELA ;digital I/O<br>BANKSEL TRISA ;<br>MOVLW 0Ch ;Set RA<3:2> as inputs<br>MOVWF TRISA ;and set RA<7:4,1:0> | EXAMPLE 6-1:                                                              | INITIALIZING PORTA                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------|

| , as outputs                                                                                                                                                                         | CLRF PORTA<br>BANKSEL ANSELA<br>CLRF ANSELA<br>BANKSEL TRISA<br>MOVLW OCh | ;Init PORTA<br>;<br>;digital I/O<br>;<br>;Set RA<3:2> as inputs |

# 9.1.5 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital conversion. The ADC interrupt flag is the ADIF bit in the PIR1 register. The ADC interrupt enable is the ADIE bit in the PIE1 register. The ADIF bit must be cleared in software.

| Note 1: | The ADIF bit is set at the completion of |

|---------|------------------------------------------|

|         | every conversion, regardless of whether  |

|         | or not the ADC interrupt is enabled.     |

**2:** The ADC operates during Sleep only when the FRC oscillator is selected.

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake-up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake-up from Sleep and resume in-line code execution, the GIE and PEIE bits of the INTCON register must be disabled. If the GIE and PEIE bits of the INTCON register are enabled, execution will switch to the Interrupt Service Routine.

Please refer to **Section 9.1.5** "Interrupts" for more information.

# 9.2 ADC Operation

# 9.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/ DONE bit of the ADCON0 register to a '1' will start the Analog-to-Digital conversion.

Note: The GO/DONE bit should not be set in the same instruction that turns on the ADC. Refer to Section 9.2.6 "A/D Conversion Procedure".

# 9.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- Set the ADIF Interrupt Flag bit

- Update the ADRES register with new conversion result

# 9.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRES register will be updated with the partially complete Analog-to-Digital conversion sample. Incomplete bits will match the last bit converted.

| Note: | A device Reset forces all registers to their |

|-------|----------------------------------------------|

|       | Reset state. Thus, the ADC module is         |

|       | turned off and any pending conversion is     |

|       | terminated.                                  |

# 9.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC clock source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

# 9.2.5 SPECIAL EVENT TRIGGER

The Special Event Trigger of the CCP module allows periodic ADC measurements without software intervention. When this trigger occurs, the GO/DONE bit is set by hardware and the Timer1 counter resets to zero.

Using the Special Event Trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met.

Refer to Section 15.0 "Capture/Compare/PWM (CCP) Module" for more information.

# 12.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The T1CKPS bits of the T1CON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

# 12.4 Timer1 Oscillator

A dedicated low-power 32.768 kHz oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). This internal circuit is to be used in conjunction with an external 32.768 kHz crystal.

The oscillator circuit is enabled by setting the T1OSCEN bit of the T1CON register. The oscillator will continue to run during Sleep.

| Note: | The oscillator requires a start-up and   |

|-------|------------------------------------------|

|       | stabilization time before use. Thus,     |

|       | T1OSCEN should be set and a suitable     |

|       | delay observed prior to enabling Timer1. |

# 12.5 Timer1 Operation in Asynchronous Counter Mode

If control bit T1SYNC of the T1CON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 12.5.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

**Note:** When switching from synchronous to asynchronous operation, it is possible to skip an increment. When switching from asynchronous to synchronous operation, it is possible to produce an additional increment.

#### 12.5.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TMR1L register pair.

# 12.11 Timer1 Control Register

The Timer1 Control register (T1CON), shown in Register 12-1, is used to control Timer1 and select the various features of the Timer1 module.

## REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | U-0 | R/W-0  |

|---------|---------|---------|---------|---------|--------|-----|--------|

| TMR1CS1 | TMR1CS0 | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | _   | TMR10N |

| bit 7   |         |         |         |         |        |     | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7-6        | TMR1CS<1:0>: Timer1 Clock Source Select bits                                                                                                                                                                                                                                                                                     |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | <ul> <li>11 = Timer1 clock source is Capacitive Sensing Oscillator (CAPOSC)</li> <li>10 = Timer1 clock source is pin or oscillator:</li> </ul>                                                                                                                                                                                   |

|                | $\frac{\text{If } T10SCEN = 0}{T10SCEN = 0}$                                                                                                                                                                                                                                                                                     |

|                | External clock from T1CKI pin (on the rising edge)<br>If T1OSCEN = 1:                                                                                                                                                                                                                                                            |

|                | Crystal oscillator on T1OSI/T1OSO pins                                                                                                                                                                                                                                                                                           |

|                | 01 = Timer1 clock source is system clock (Fosc)<br>00 = Timer1 clock source is instruction clock (Fosc/4)                                                                                                                                                                                                                        |

| bit 5-4        | <b>T1CKPS&lt;1:0&gt;:</b> Timer1 Input Clock Prescale Select bits                                                                                                                                                                                                                                                                |

| bit 0 4        | 11 = 1.8 Prescale value                                                                                                                                                                                                                                                                                                          |

|                | 10 = 1:4 Prescale value                                                                                                                                                                                                                                                                                                          |

|                | 01 = 1:2 Prescale value<br>00 = 1:1 Prescale value                                                                                                                                                                                                                                                                               |

| bit 3          | <b>TIOSCEN:</b> LP Oscillator Enable Control bit                                                                                                                                                                                                                                                                                 |

| bit 5          | 1 = Dedicated Timer1 oscillator circuit enabled                                                                                                                                                                                                                                                                                  |

|                | 0 = Dedicated Timer1 oscillator circuit disabled                                                                                                                                                                                                                                                                                 |

| bit 2          | <b>T1SYNC:</b> Timer1 External Clock Input Synchronization Control bit                                                                                                                                                                                                                                                           |

|                | TISTIC. Timer External Clock input Synchronization Control bit                                                                                                                                                                                                                                                                   |

|                | <u>TMR1CS&lt;1:0&gt; = <math>1X</math></u>                                                                                                                                                                                                                                                                                       |

|                | $\frac{\text{TMR1CS}<1:0> = 1x}{1 = \text{Do not synchronize external clock input}}$                                                                                                                                                                                                                                             |

|                | $\underline{TMR1CS} = \underline{1X}$                                                                                                                                                                                                                                                                                            |

|                | $\frac{\text{TMR1CS} < 1:0> = 1x}{1 = \text{Do not synchronize external clock input}}$<br>0 = Synchronize external clock input with system clock (Fosc)<br>$\frac{\text{TMR1CS} < 1:0> = 0x}{10}$                                                                                                                                |

|                | $\frac{\text{TMR1CS}<1:0> = 1x}{1 = \text{ Do not synchronize external clock input}}$ $0 = \text{Synchronize external clock input with system clock (Fosc)}$ $\frac{\text{TMR1CS}<1:0> = 0x}{\text{This bit is ignored. Timer1 uses the internal clock when TMR1CS}<1:0> = 1x.$                                                  |

| bit 1          | $\frac{\text{TMR1CS} < 1:0 > = 1x}{1 = \text{Do not synchronize external clock input}}$ $0 = \text{Synchronize external clock input with system clock (Fosc)}$ $\frac{\text{TMR1CS} < 1:0 > = 0x}{\text{This bit is ignored. Timer1 uses the internal clock when TMR1CS} < 1:0 > = 1x.$ Unimplemented: Read as '0'               |

| bit 1<br>bit 0 | $\frac{\text{TMR1CS}<1:0> = 1x}{1 = \text{ Do not synchronize external clock input}}$ $0 = \text{Synchronize external clock input with system clock (Fosc)}$ $\frac{\text{TMR1CS}<1:0> = 0x}{\text{This bit is ignored. Timer1 uses the internal clock when TMR1CS}<1:0> = 1x.$ Unimplemented: Read as '0' TMR1ON: Timer1 On bit |

|                | $\frac{\text{TMR1CS} < 1:0 > = 1x}{1 = \text{Do not synchronize external clock input}}$ $0 = \text{Synchronize external clock input with system clock (Fosc)}$ $\frac{\text{TMR1CS} < 1:0 > = 0x}{\text{This bit is ignored. Timer1 uses the internal clock when TMR1CS} < 1:0 > = 1x.$ Unimplemented: Read as '0'               |

| Name    | Bit 7       | Bit 6         | Bit 5        | Bit 4        | Bit 3          | Bit 2     | Bit 1  | Bit 0  | Register<br>on Page |  |

|---------|-------------|---------------|--------------|--------------|----------------|-----------|--------|--------|---------------------|--|

| ANSELB  | —           | —             | ANSB5        | ANSB4        | ANSB3          | ANSB2     | ANSB1  | ANSB0  | 53                  |  |

| CCP1CON | —           | _             | DC1B1        | DC1B0        | CCP1M3         | CCP1M2    | CCP1M1 | CCP1M0 | 115                 |  |

| CCP2CON | —           | —             | DC2B1        | DC2B0        | CCP2M3         | CCP2M2    | CCP2M1 | CCP2M0 | 115                 |  |

| INTCON  | GIE         | PEIE          | T0IE         | INTE         | RBIE           | T0IF      | INTF   | RBIF   | 36                  |  |

| PIE1    | TMR1GIE     | ADIE          | RCIE         | TXIE         | SSPIE          | CCP1IE    | TMR2IE | TMR1IE | 37                  |  |

| PIR1    | TMR1GIF     | ADIF          | RCIF         | TXIF         | SSPIF          | CCP1IF    | TMR2IF | TMR1IF | 39                  |  |

| PORTB   | RB7         | RB6           | RB5          | RB4          | RB3            | RB2       | RB1    | RB0    | 52                  |  |

| TMR1H   | Holding Reg | ister for the | Most Signifi | cant Byte of | the 16-bit T   | MR1 Regis | ter    |        | 99                  |  |

| TMR1L   | Holding Reg | ister for the | Least Signif | icant Byte o | f the 16-bit 7 | MR1 Regis | ster   |        | 99                  |  |

| TRISB   | TRISB7      | TRISB6        | TRISB5       | TRISB4       | TRISB3         | TRISB2    | TRISB1 | TRISB0 | 52                  |  |

| TRISC   | TRISC7      | TRISC6        | TRISC5       | TRISC4       | TRISC3         | TRISC2    | TRISC1 | TRISC0 | 62                  |  |

| T1CON   | TMR1CS1     | TMR1CS0       | T1CKPS1      | T1CKPS0      | T1OSCEN        | T1SYNC    | _      | TMR10N | 103                 |  |

| T1GCON  | TMR1GE      | T1GPOL        | T1GTM        | T1GSPM       | T1GGO/<br>DONE | T1GVAL    | T1GSS1 | T1GSS0 | 104                 |  |

#### TABLE 12-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER1

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

|        |                  | SYNC = 0, BRGH = 1 |                             |                  |            |                             |                   |            |                             |                  |            |                             |

|--------|------------------|--------------------|-----------------------------|------------------|------------|-----------------------------|-------------------|------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fosc = 8.000 MHz |                    |                             | Fosc = 4.000 MHz |            |                             | Fosc = 3.6864 MHz |            |                             | Fosc = 1.000 MHz |            |                             |

| RATE   | Actual<br>Rate   | %<br>Error         | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | —                |                    | —                           | _                | _          | _                           |                   | _          | _                           | 300              | 0.16       | 207                         |

| 1200   | —                | —                  | —                           | 1202             | 0.16       | 207                         | 1200              | 0.00       | 191                         | 1202             | 0.16       | 51                          |

| 2400   | 2404             | 0.16               | 207                         | 2404             | 0.16       | 103                         | 2400              | 0.00       | 95                          | 2404             | 0.16       | 25                          |

| 9600   | 9615             | 0.16               | 51                          | 9615             | 0.16       | 25                          | 9600              | 0.00       | 23                          | _                | _          | _                           |

| 10417  | 10417            | 0.00               | 47                          | 10417            | 0.00       | 23                          | 10473             | 0.53       | 21                          | 10417            | 0.00       | 5                           |

| 19.2k  | 19231            | 0.16               | 25                          | 19.23k           | 0.16       | 12                          | 19.2k             | 0.00       | 11                          | —                | _          | _                           |

| 57.6k  | 55556            | -3.55              | 8                           | —                | _          | _                           | 57.60k            | 0.00       | 3                           | —                | _          | _                           |

| 115.2k | _                | _                  | _                           | _                | —          | —                           | 115.2k            | 0.00       | 1                           | _                | —          | _                           |

#### TABLE 16-5: BAUD RATES FOR ASYNCHRONOUS MODES

| R/W-0      | R/W-0                                            | R/W-0                                                                                                                        | R/W-0                                                          | R/W-0                                    | R/W-0            | R/W-0                         | R/W-0                          |

|------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------|------------------|-------------------------------|--------------------------------|

| WCOL       | SSPOV                                            | SSPEN                                                                                                                        | CKP                                                            | SSPM3                                    | SSPM2            | SSPM1                         | SSPM0                          |

| bit 7      | ·                                                | ·                                                                                                                            |                                                                | •                                        | •                | •                             | bit (                          |

|            |                                                  |                                                                                                                              |                                                                |                                          |                  |                               |                                |

| Legend:    |                                                  |                                                                                                                              |                                                                |                                          |                  |                               |                                |

| R = Reada  |                                                  | W = Writable                                                                                                                 |                                                                | -                                        | mented bit, rea  |                               |                                |

| -n = Value | at POR                                           | '1' = Bit is set                                                                                                             |                                                                | '0' = Bit is cle                         | eared            | x = Bit is unk                | nown                           |

| bit 7      | WCOL: W                                          | rite Collision Dete                                                                                                          | ct bit                                                         |                                          |                  |                               |                                |

|            | 1 = The S<br>softwa                              | SPBUF register is<br>are)                                                                                                    | s written while                                                | e it is still transr                     | mitting the prev | ious word (mus                | t be cleared i                 |

|            | 0 = No co                                        | Ilision                                                                                                                      |                                                                |                                          |                  |                               |                                |

| bit 6      | <b>SSPOV</b> : R                                 | eceive Overflow I                                                                                                            | ndicator bit                                                   |                                          |                  |                               |                                |

|            | overfle<br>the S<br>overfle                      | v byte is received<br>ow, the data in SS<br>SPBUF, even if<br>ow bit is not set s<br>SUF register.<br>erflow                 | PSR is lost. (                                                 | Overflow can or<br>ting data, to a       | nly occur in Sla | ve mode. The uverflow. In Mas | user must rea<br>ster mode, th |

| bit 5      | SSPEN: S                                         | ynchronous Seria                                                                                                             | l Port Enable                                                  | bit                                      |                  |                               |                                |

|            |                                                  | es serial port and es serial port and                                                                                        |                                                                |                                          |                  | rt pins <sup>(1)</sup>        |                                |

| bit 4      | CKP: Cloc                                        | k Polarity Select I                                                                                                          | oit                                                            |                                          |                  |                               |                                |

|            |                                                  | ate for clock is a h<br>ate for clock is a le                                                                                | 0                                                              |                                          |                  |                               |                                |

| bit 3-0    | SSPM<3:0                                         | <b>)&gt;</b> : Synchronous \$                                                                                                | Serial Port Mo                                                 | ode Select bits                          |                  |                               |                                |

|            | 0001 = SF<br>0010 = SF<br>0011 = SF<br>0100 = SF | PI Master mode, c<br>PI Master mode, c<br>PI Master mode, c<br>PI Master mode, c<br>PI Slave mode, clo<br>PI Slave mode, clo | lock = Fosc/1<br>lock = Fosc/6<br>lock = TMR2<br>ock = SCK pir | 16<br>64<br>output/2<br>n. SS pin contro |                  |                               | 1/O pip                        |

| Note 1:    |                                                  | these pins must b                                                                                                            | •                                                              | •                                        |                  |                               | " O pii.                       |

# REGISTER 17-1: SSPCON: SYNC SERIAL PORT CONTROL REGISTER (SPI MODE)

Note 1: When enabled, these pins must be properly configured as input or output.

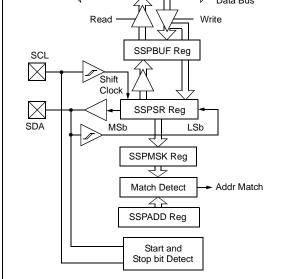

# 17.2 I<sup>2</sup>C Mode

The SSP module, in  $I^2C$  mode, implements all slave functions, except general call support. It provides interrupts on Start and Stop bits in hardware to facilitate firmware implementations of the master functions. The SSP module implements the  $I^2C$  Standard mode specifications:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- Start and Stop bit interrupts enabled to support firmware Master mode

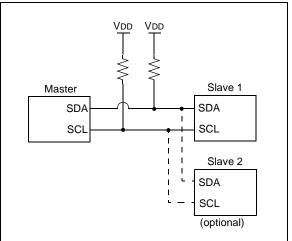

- Address masking

Two pins are used for data transfer; the SCL pin (clock line) and the SDA pin (data line). The user must configure the two pin's data direction bits as inputs in the appropriate TRIS register. Upon enabling  $I^2C$  mode, the  $I^2C$  slew rate limiters in the I/O pads are controlled by the SMP bit of SSPSTAT register. The SSP module functions are enabled by setting the SSPEN bit of SSPCON register.

Data is sampled on the rising edge and shifted out on the falling edge of the clock. This ensures that the SDA signal is valid during the SCL high time. The SCL clock input must have minimum high and low times for proper operation. Refer to **Section 23.0** "**Electrical Specifications**".

# FIGURE 17-7: I<sup>2</sup>C MODE BLOCK DIAGRAM

# FIGURE 17-8: TYPICAL I<sup>2</sup>C

# CONNECTIONS

The SSP module has six registers for  $\mathsf{I}^2\mathsf{C}$  operation. They are:

- SSP Control (SSPCON) register

- SSP Status (SSPSTAT) register

- Serial Receive/Transmit Buffer (SSPBUF) register

- SSP Shift Register (SSPSR), not directly accessible

- SSP Address (SSPADD) register

- SSP Address Mask (SSPMSK) register

# 17.2.1 HARDWARE SETUP

Selection of  $I^2C$  mode, with the SSPEN bit of the SSPCON register set, forces the SCL and SDA pins to be open drain, provided these pins are programmed as inputs by setting the appropriate TRISC bits. The SSP module will override the input state with the output data, when required, such as for Acknowledge and slave-transmitter sequences.

**Note:** Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the I<sup>2</sup>C module.

# 23.2 DC Characteristics: PIC16(L)F722A/723A-I/E (Industrial, Extended)

| PIC16LF        | 722A/723A                              |          | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                        |       |                                                                                                                               |                                                                                 |  |  |  |

|----------------|----------------------------------------|----------|------------------------------------------------------|------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|--|--|--|

| PIC16F7        | 22A/723A                               |          |                                                      | d Operati<br>g tempera | ature | itions (unless otherwise stated)<br>-40°C $\leq$ TA $\leq$ +85°C for industrial<br>-40°C $\leq$ TA $\leq$ +125°C for extended |                                                                                 |  |  |  |

| Param          | Device                                 | Min.     | Typt                                                 | Max.                   | Units |                                                                                                                               | Conditions                                                                      |  |  |  |

| No.            | Characteristics                        | IVIIII.  | Тур†                                                 | IVIAX.                 | Units | VDD                                                                                                                           | Note                                                                            |  |  |  |

|                | Supply Current (IDD) <sup>(1, 2)</sup> |          |                                                      |                        |       |                                                                                                                               |                                                                                 |  |  |  |

| D009           | LDO Regulator                          | -        | 350                                                  | _                      | μΑ    | —                                                                                                                             | HS, EC OR INTOSC/INTOSCIO (8-16 MHz)<br>Clock modes with all VCAP pins disabled |  |  |  |

|                |                                        |          | 50                                                   | —                      | μΑ    | _                                                                                                                             | All VCAP pins disabled                                                          |  |  |  |

|                |                                        | —        | 30                                                   | —                      | μA    | —                                                                                                                             | VCAP enabled on RA0, RA5 or RA6                                                 |  |  |  |

|                |                                        | _        | 5                                                    | _                      | μΑ    | —                                                                                                                             | LP Clock mode and Sleep (requires FVR and BOR to be disabled)                   |  |  |  |

| D010           |                                        | _        | 7.0                                                  | 12                     | μΑ    | 1.8                                                                                                                           | Fosc = 32 kHz                                                                   |  |  |  |

|                |                                        | —        | 9.0                                                  | 14                     | μΑ    | 3.0                                                                                                                           | LP Oscillator mode (Note 4),<br>-40°C $\leq$ TA $\leq$ +85°C                    |  |  |  |

| D010           |                                        |          | 11                                                   | 20                     | μΑ    | 1.8                                                                                                                           | Fosc = 32 kHz                                                                   |  |  |  |

|                |                                        | —        | 14                                                   | 22                     | μΑ    | 3.0                                                                                                                           | LP Oscillator mode (Note 4),<br>-40°C $\leq$ TA $\leq$ +85°C                    |  |  |  |

|                |                                        | —        | 15                                                   | 24                     | μΑ    | 5.0                                                                                                                           | $-40$ C $\leq$ 1A $\leq$ +63 C                                                  |  |  |  |

| D011           |                                        |          | 7.0                                                  | 12                     | μΑ    | 1.8                                                                                                                           | Fosc = 32 kHz                                                                   |  |  |  |

|                |                                        | _        | 9.0                                                  | 18                     | μΑ    | 3.0                                                                                                                           | LP Oscillator mode<br>-40°C $\leq$ TA $\leq$ +125°C                             |  |  |  |

| D011           |                                        |          | 11                                                   | 21                     | μΑ    | 1.8                                                                                                                           | Fosc = 32 kHz                                                                   |  |  |  |

|                |                                        | _        | 14                                                   | 25                     | μΑ    | 3.0                                                                                                                           | LP Oscillator mode (Note 4)<br>-40°C $\leq$ TA $\leq$ +125°C                    |  |  |  |

|                |                                        | —        | 15                                                   | 27                     | μΑ    | 5.0                                                                                                                           | -40 C \sec 1A \sec +125 C                                                       |  |  |  |

| D011           |                                        |          | 110                                                  | 150                    | μΑ    | 1.8                                                                                                                           | Fosc = 1 MHz                                                                    |  |  |  |

|                |                                        |          | 150                                                  | 215                    | μΑ    | 3.0                                                                                                                           | XT Oscillator mode                                                              |  |  |  |

| D011           |                                        |          | 120                                                  | 175                    | μΑ    | 1.8                                                                                                                           | Fosc = 1 MHz                                                                    |  |  |  |

|                |                                        |          | 180                                                  | 250                    | μΑ    | 3.0                                                                                                                           | XT Oscillator mode (Note 5)                                                     |  |  |  |

| <b>B</b> 4 4 5 |                                        |          | 240                                                  | 300                    | μA    | 5.0                                                                                                                           |                                                                                 |  |  |  |

| D012           |                                        |          | 230                                                  | 300                    | μΑ    | 1.8                                                                                                                           | Fosc = 4 MHz<br>XT Oscillator mode                                              |  |  |  |

| Data           |                                        | -        | 400                                                  | 600                    | μΑ    | 3.0                                                                                                                           |                                                                                 |  |  |  |

| D012           |                                        |          | 250                                                  | 350                    | μΑ    | 1.8                                                                                                                           | Fosc = 4 MHz<br>XT Oscillator mode (Note 5)                                     |  |  |  |

|                |                                        |          | 420                                                  | 650                    | μΑ    | 3.0                                                                                                                           | -                                                                               |  |  |  |

| D012           |                                        |          | 500                                                  | 750                    | μΑ    | 5.0                                                                                                                           |                                                                                 |  |  |  |

| D013           |                                        | <u> </u> | 125<br>230                                           | 180<br>270             | μΑ    | 1.8<br>3.0                                                                                                                    | Fosc = 1 MHz<br>EC Oscillator mode                                              |  |  |  |

| D012           |                                        |          |                                                      |                        | μΑ    |                                                                                                                               |                                                                                 |  |  |  |

| D013           |                                        |          | 150                                                  | 205                    | μΑ    | 1.8                                                                                                                           | Fosc = 1 MHz<br>EC Oscillator mode (Note 5)                                     |  |  |  |

|                |                                        |          | 225                                                  | 320                    | μΑ    | 3.0                                                                                                                           | -                                                                               |  |  |  |

|                | The test conditions for                |          | 250                                                  | 410                    | μΑ    | 5.0                                                                                                                           |                                                                                 |  |  |  |

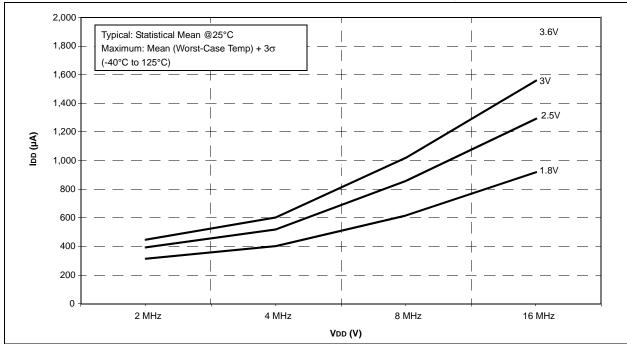

**Note 1:** The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

3: For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in k $\Omega$ .

4: FVR and BOR are disabled.

5: 0.1  $\mu$ F capacitor on VCAP (RA0).

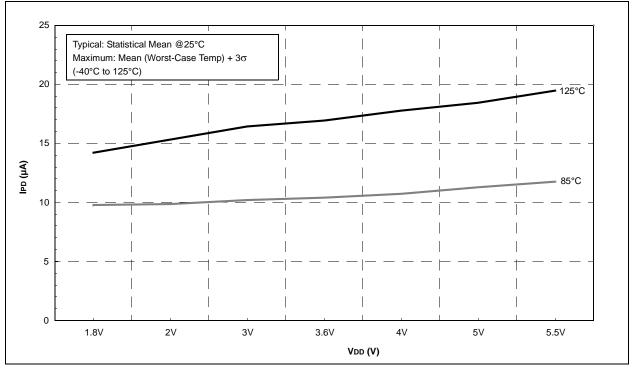

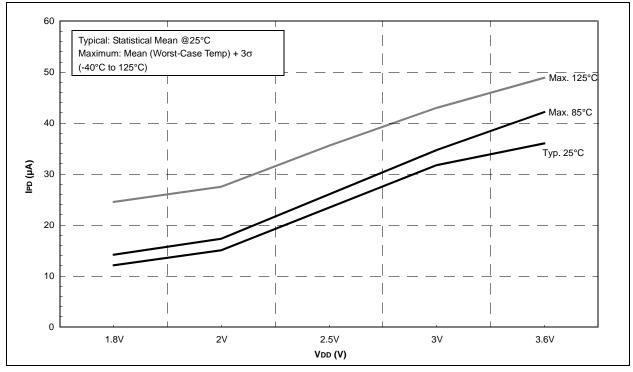

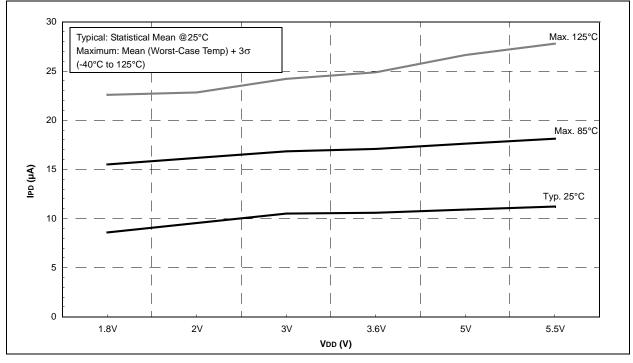

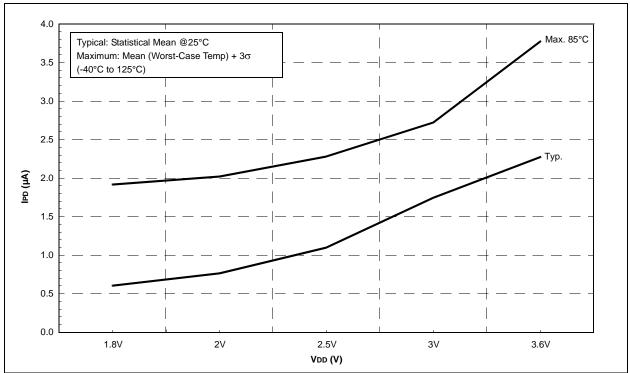

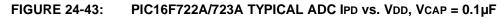

# 23.3 DC Characteristics: PIC16(L)F722A/723A-I/E (Power-Down) (Continued)

| PIC16LF7        | 22A/723A                |                      |                                                  | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |        |                                                                                                                                |     |                                  |  |  |  |

|-----------------|-------------------------|----------------------|--------------------------------------------------|------------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------------|--|--|--|

| PIC16F722A/723A |                         |                      | Standard Operating Cone<br>Operating temperature |                                                      |        | ditions (unless otherwise stated)<br>-40°C $\leq$ TA $\leq$ +85°C for industrial<br>-40°C $\leq$ TA $\leq$ +125°C for extended |     |                                  |  |  |  |

| Param           | Device Characteristics  | Min.                 | Тур†                                             | Max.                                                 | Max.   | Units                                                                                                                          |     | Conditions                       |  |  |  |

| No.             |                         |                      |                                                  | +85°C                                                | +125°C |                                                                                                                                | VDD | Note                             |  |  |  |

|                 | Power-down Base Current | (IPD) <sup>(2)</sup> |                                                  | -                                                    |        |                                                                                                                                | -   |                                  |  |  |  |

| D027            |                         |                      | 0.06                                             | 0.7                                                  | 5.0    | μA                                                                                                                             | 1.8 | A/D Current (Note 1, Note 4), no |  |  |  |

|                 |                         | —                    | 0.08                                             | 1.0                                                  | 5.5    | μΑ                                                                                                                             | 3.0 | conversion in progress           |  |  |  |

| D027            |                         |                      | 6                                                | 10.7                                                 | 18     | μΑ                                                                                                                             | 1.8 | A/D Current (Note 1, Note 4), no |  |  |  |

|                 |                         |                      | 7                                                | 10.6                                                 | 20     | μΑ                                                                                                                             | 3.0 | conversion in progress           |  |  |  |

|                 |                         | —                    | 7.2                                              | 11.9                                                 | 22     | μΑ                                                                                                                             | 5.0 |                                  |  |  |  |

| D027A           |                         |                      | 250                                              | 400                                                  | —      | μΑ                                                                                                                             | 1.8 | A/D Current (Note 1, Note 4),    |  |  |  |

|                 |                         | —                    | 250                                              | 400                                                  | —      | μΑ                                                                                                                             | 3.0 | conversion in progress           |  |  |  |

| D027A           |                         |                      | 280                                              | 430                                                  | —      | μΑ                                                                                                                             | 1.8 | A/D Current (Note 1, Note 4,     |  |  |  |

|                 |                         |                      | 280                                              | 430                                                  | —      | μΑ                                                                                                                             | 3.0 | Note 5), conversion in progress  |  |  |  |

|                 |                         | —                    | 280                                              | 430                                                  | —      | μΑ                                                                                                                             | 5.0 |                                  |  |  |  |

| D028            |                         | —                    | 2.2                                              | 3.2                                                  | 14.4   | μA                                                                                                                             | 1.8 | Cap Sense Low Power              |  |  |  |

|                 |                         | —                    | 3.3                                              | 4.4                                                  | 15.6   | μA                                                                                                                             | 3.0 | Oscillator mode                  |  |  |  |

| D028            |                         | _                    | 6.5                                              | 13                                                   | 21     | μΑ                                                                                                                             | 1.8 | Cap Sense Low Power              |  |  |  |

|                 |                         | —                    | 8                                                | 14                                                   | 23     | μΑ                                                                                                                             | 3.0 | Oscillator mode                  |  |  |  |

|                 |                         | —                    | 8                                                | 14                                                   | 25     | μΑ                                                                                                                             | 5.0 |                                  |  |  |  |

| D028A           |                         |                      | 4.2                                              | 6                                                    | 17     | μA                                                                                                                             | 1.8 | Cap Sense Medium Power           |  |  |  |

|                 |                         | —                    | 6                                                | 7                                                    | 18     | μA                                                                                                                             | 3.0 | Oscillator mode                  |  |  |  |

| D028A           |                         |                      | 8.5                                              | 15.5                                                 | 23     | μA                                                                                                                             | 1.8 | Cap Sense Medium Power           |  |  |  |

|                 |                         | _                    | 11                                               | 17                                                   | 24     | μΑ                                                                                                                             | 3.0 | Oscillator mode                  |  |  |  |

|                 |                         | _                    | 11                                               | 18                                                   | 27     | μA                                                                                                                             | 5.0 |                                  |  |  |  |

| D028B           |                         | _                    | 12                                               | 14                                                   | 25     | μA                                                                                                                             | 1.8 | Cap Sense High Power             |  |  |  |

|                 |                         |                      | 32                                               | 35                                                   | 44     | μA                                                                                                                             | 3.0 | Oscillator mode                  |  |  |  |

| D028B           |                         | _                    | 16                                               | 20                                                   | 31     | μA                                                                                                                             | 1.8 | Cap Sense High Power             |  |  |  |

|                 |                         | _                    | 36                                               | 41                                                   | 50     | μA                                                                                                                             | 3.0 | Oscillator mode                  |  |  |  |

|                 |                         |                      | 42                                               | 49                                                   | 58     | μΑ                                                                                                                             | 5.0 | ]                                |  |  |  |

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral △ current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.