Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 192 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 11x8b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-UFQFN Exposed Pad                                                      |

| Supplier Device Package    | 28-UQFN (4x4)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f723a-i-mv |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16(L)F722A/723A

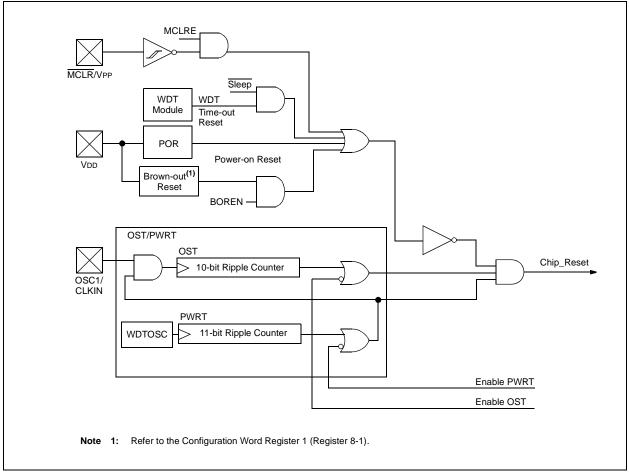

# 3.0 RESETS

The PIC16(L)F722A/723A differentiates between various kinds of Reset:

- a) Power-on Reset (POR)

- b) WDT Reset during normal operation

- c) WDT Reset during Sleep

- d) MCLR Reset during normal operation

- e) MCLR Reset during Sleep

- f) Brown-out Reset (BOR)

Some registers are not affected in any Reset condition; their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on:

- Power-on Reset (POR)

- MCLR Reset

- MCLR Reset during Sleep

- WDT Reset

- Brown-out Reset (BOR)

Most registers are not affected by a WDT wake-up since this is viewed as the resumption of normal operation. TO and PD bits are set or cleared differently in different Reset situations, as indicated in Table 3-3. These bits are used in software to determine the nature of the Reset.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 3-1.

The MCLR Reset path has a noise filter to detect and ignore small pulses. See **Section 23.0** "**Electrical Specifications**" for pulse width specifications.

#### FIGURE 3-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

#### 4.5.2 PIE1 REGISTER

The PIE1 register contains the interrupt enable bits, as shown in Register 4-2.

**Note:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

| R/W-0         | R/W-0                                                     | R/W-0                                                             | R/W-0          | R/W-0           | R/W-0           | R/W-0           | R/W-0  |

|---------------|-----------------------------------------------------------|-------------------------------------------------------------------|----------------|-----------------|-----------------|-----------------|--------|

| TMR1GIE       | ADIE                                                      | RCIE                                                              | TXIE           | SSPIE           | CCP1IE          | TMR2IE          | TMR1IE |

| bit 7         |                                                           |                                                                   |                |                 |                 |                 | bit C  |

| Legend:       |                                                           |                                                                   |                |                 |                 |                 |        |

| R = Readable  | bit                                                       | W = Writable                                                      | hit            | II – Unimple    | mented bit, rea | d as '0'        |        |

| -n = Value at |                                                           | '1' = Bit is set                                                  |                | 0' = Bit is cle |                 | x = Bit is unki | nown   |

|               |                                                           |                                                                   |                |                 | carea           |                 |        |

| bit 7         | TMR1GIE: 7                                                | Timer1 Gate Inte                                                  | rrupt Enable I | bit             |                 |                 |        |

|               |                                                           | he Timer1 gate                                                    | •              |                 | pt              |                 |        |

|               |                                                           | the Timer1 gate                                                   |                |                 |                 |                 |        |

| bit 6         | ADIE: A/D C                                               | Converter (ADC)                                                   | Interrupt Ena  | ble bit         |                 |                 |        |

|               |                                                           | the ADC interru                                                   | •              |                 |                 |                 |        |

|               |                                                           | s the ADC interru                                                 | •              |                 |                 |                 |        |

| bit 5         |                                                           | RT Receive Inter                                                  | •              | bit             |                 |                 |        |

|               |                                                           | es the USART receive interrupt<br>les the USART receive interrupt |                |                 |                 |                 |        |

| bit 4         |                                                           | RT Transmit Inter                                                 | •              |                 |                 |                 |        |

| DIL 4         |                                                           | the USART trans                                                   | •              |                 |                 |                 |        |

|               |                                                           | the USART tra                                                     |                |                 |                 |                 |        |

| bit 3         | SSPIE: Synchronous Serial Port (SSP) Interrupt Enable bit |                                                                   |                |                 |                 |                 |        |

| •             |                                                           | s the SSP interrupt                                               |                |                 |                 |                 |        |

|               | 0 = Disables                                              | s the SSP interru                                                 | ipt            |                 |                 |                 |        |

| bit 2         | CCP1IE: CC                                                | CP1 Interrupt En                                                  | able bit       |                 |                 |                 |        |

|               |                                                           | bles the CCP1 interrupt                                           |                |                 |                 |                 |        |

|               |                                                           | the CCP1 inter                                                    | •              |                 |                 |                 |        |

| bit 1         |                                                           | IR2 to PR2 Mate                                                   | •              |                 |                 |                 |        |

|               |                                                           | the Timer2 to P                                                   |                |                 |                 |                 |        |

| hit O         |                                                           | the Timer2 to F                                                   |                | •               |                 |                 |        |

| bit 0         |                                                           | ner1 Overflow Ir                                                  |                |                 |                 |                 |        |

|               |                                                           | the Timer1 over<br>the Timer1 ove                                 |                |                 |                 |                 |        |

#### REGISTER 4-2: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

# 6.5 **PORTE and TRISE Registers**

PORTE<sup>(1)</sup> is an 1-bit wide, input-only port. RE3 is inputonly and its TRIS bit will always read as '1'.

Reading the PORTE register (Register 6-12) reads the status of the pins. RE3 reads '0' when MCLRE = 1.

#### REGISTER 6-12: PORTE: PORTE REGISTER

| U-0   | U-0 | U-0 | U-0 | R-x | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| —     | —   | —   | _   | RE3 | —   | —   | —     |

| bit 7 |     |     |     |     |     |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-4 | Unimplemented: Read as '0'             |

|---------|----------------------------------------|

| bit 3   | RE3: PORTE I/O Pin bits <sup>(1)</sup> |

|         | 1 = Port pin is > VIH                  |

|         | 0 = Port pin is < VIL                  |

| bit 2-0 | Unimplemented: Read as '0'             |

#### **REGISTER 6-13:** TRISE: PORTE TRI-STATE REGISTER

| U-0   | U-0 | U-0 | U-0 | R-1    | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|--------|-----|-----|-------|

| _     | —   | —   | —   | TRISE3 | —   | —   | —     |

| bit 7 |     |     |     | •      |     |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-4 | Unimplemented: Read as '0'                     |

|---------|------------------------------------------------|

| bit 3   | TRISE3: RE3 Port Tri-state Control bit         |

|         | This bit is always '1' as RE3 is an input-only |

| bit 2-0 | Unimplemented: Read as '0'                     |

#### TABLE 6-5: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

| Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3                 | Bit 2 | Bit 1 | Bit 0 | Register on<br>Page |

|-------|-------|-------|-------|-------|-----------------------|-------|-------|-------|---------------------|

| PORTE | —     |       |       |       | RE3                   |       |       |       | 69                  |

| TRISE | _     |       |       |       | TRISE3 <sup>(1)</sup> |       | _     |       | 69                  |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTE

**Note 1:** This bit is always '1' as RE3 is input-only.

# 7.4 Oscillator Control

The Oscillator Control (OSCCON) register (Figure 7-1) displays the status and allows frequency selection of the internal oscillator (INTOSC) system clock. The OSCCON register contains the following bits:

- Frequency selection bits (IRCF)

- Status Locked bits (ICSL)

- Status Stable bits (ICSS)

#### REGISTER 7-1: OSCCON: OSCILLATOR CONTROL REGISTER

| U-0     | U-0 | R/W-1 | R/W-0 | R-q  | R-q  | U-0 | U-0   |

|---------|-----|-------|-------|------|------|-----|-------|

|         | —   | IRCF1 | IRCF0 | ICSL | ICSS |     | _     |

| bit 7   |     |       |       |      |      |     | bit 0 |

|         |     |       |       |      |      |     |       |

| Legend: |     |       |       |      |      |     |       |

| R = Readable bit       | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |

|------------------------|------------------|-----------------------|------------------------------------|--|--|

| -n = Value at POR      | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |

| q = Value depends on c | ondition         |                       |                                    |  |  |

| bit 7-6 | Unimplemented: Read as '0'                                                               |

|---------|------------------------------------------------------------------------------------------|

| bit 5-4 | IRCF<1:0>: Internal Oscillator Frequency Select bits                                     |

|         | <u>When PLLEN = 1 (16 MHz INTOSC)</u>                                                    |

|         | 11 <b>= 16 MHz</b>                                                                       |

|         | 10 = 8 MHz (POR value)                                                                   |

|         | 01 = 4  MHz                                                                              |

|         | 00 = 2 MHz                                                                               |

|         | $\frac{\text{When PLLEN} = 0 (500 \text{ kHz INTOSC})}{11 - 500 \text{ kHz}}$            |

|         | 11 = 500 kHz                                                                             |

|         | 10 = 250 kHz (POR value)<br>01 = 125 kHz                                                 |

|         | 01 = 125  kHz<br>00 = 62.5  kHz                                                          |

| h it 0  |                                                                                          |

| bit 3   | ICSL: Internal Clock Oscillator Status Locked bit (2% Stable)                            |

|         | 1 = 16 MHz/500 kHz Internal Oscillator (HFIOSC) is in lock                               |

|         | 0 = 16 MHz/500 kHz Internal Oscillator (HFIOSC) has not yet locked                       |

| bit 2   | ICSS: Internal Clock Oscillator Status Stable bit (0.5% Stable)                          |

|         | 1 = 16 MHz/500 kHz Internal Oscillator (HFIOSC) has stabilized to its maximum accuracy   |

|         | 0 = 16 MHz/500 kHz Internal Oscillator (HFIOSC) has not yet reached its maximum accuracy |

| bit 1-0 | Unimplemented: Read as '0'                                                               |

|         |                                                                                          |

# 7.5 Oscillator Tuning

The INTOSC is factory-calibrated but can be adjusted in software by writing to the OSCTUNE register (Register 7-2).

The default value of the OSCTUNE register is '0'. The value is a 6-bit two's complement number.

When the OSCTUNE register is modified, the INTOSC frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred.

#### REGISTER 7-2: OSCTUNE: OSCILLATOR TUNING REGISTER

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     |     | TUN5  | TUN4  | TUN3  | TUN2  | TUN1  | TUN0  |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 7-6 Unimplemented: Read as '0'

bit 5-0

# 8.2 Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out using ICSP<sup>TM</sup> for verification purposes.

| Note: | The entire Flash program memory will be   |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|

|       | erased when the code protection is turned |  |  |  |  |  |  |  |

|       | off. See the "PIC16(L)F72X Memory         |  |  |  |  |  |  |  |

|       | Programming Specification" (DS41332)      |  |  |  |  |  |  |  |

|       | for more information.                     |  |  |  |  |  |  |  |

# 8.3 User ID

Four memory locations (2000h-2003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution, but are readable and writable during Program/Verify mode. Only the Least Significant 7 bits of the ID locations are reported when using MPLAB IDE. See the *"PIC16(L)F72X Memory Programming Specification"* (DS41332) for more information.

# 12.1 Timer1 Operation

The Timer1 module is a 16-bit incrementing counter which is accessed through the TMR1H:TMR1L register pair. Writes to TMR1H or TMR1L directly update the counter.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

Timer1 is enabled by configuring the TMR1ON and TMR1GE bits in the T1CON and T1GCON registers, respectively. Table 12-1 displays the Timer1 enable selections.

TABLE 12-1: TIMER1 ENABLE SELECTIONS

| TMR10N | TMR1GE | Timer1<br>Operation |

|--------|--------|---------------------|

| 0      | 0      | Off                 |

| 0      | 1      | Off                 |

| 1      | 0      | Always On           |

| 1      | 1      | Count Enabled       |

# 12.2 Clock Source Selection

The TMR1CS<1:0> and T1OSCEN bits of the T1CON register are used to select the clock source for Timer1. Table 12-2 displays the clock source selections.

#### 12.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected the TMR1H:TMR1L register pair will increment on multiples of FISC as determined by the Timer1 prescaler.

### 12.2.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1 module may work as a timer or a counter.

When enabled to count, Timer1 is increment ed on the rising edge of the external clock input T1CKI or the capacitive sensing oscillator signal. Either of these external clock sources can be synchronized to the microcontroller system clock or they can run asynchronously.

When used as a timer with a clock oscillator, an external 32.768 kHz crystal can be used in conjunction with the dedicated internal oscillator circuit.

| Note: | In Counter mode, a falling edge must be<br>registered by the counter prior to the first<br>incrementing rising edge after any one or |

|-------|--------------------------------------------------------------------------------------------------------------------------------------|

|       | more of the following conditions:                                                                                                    |

|       | •Timer1 enabled after POP                                                                                                            |

•Timer1 enabled after POR

•Write to TMR1H or TMR1L

- •Timer1 is disabled

- •Timer1 is disabled (TMR1ON = 0) when T1CKI is high then Timer1 is enabled (TMR1ON= 1) when T1CKI is low.

| TMR1CS1 | TMR1CS0 | T10SCEN | Clock Source                           |  |

|---------|---------|---------|----------------------------------------|--|

| 0       | 1       | x       | System Clock (FOSC)                    |  |

| 0       | 0       | x       | Instruction Clock (Fosc/4)             |  |

| 1       | 1       | x       | Capacitive Sensing Oscillator          |  |

| 1       | 0       | 0       | External Clocking on T1CKI Pin         |  |

| 1       | 0       | 1       | Oscillator Circuit on T1OSI/T1OSO Pins |  |

#### TABLE 12-2: CLOCK SOURCE SELECTIONS

#### 12.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The T1CKPS bits of the T1CON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

# 12.4 Timer1 Oscillator

A dedicated low-power 32.768 kHz oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). This internal circuit is to be used in conjunction with an external 32.768 kHz crystal.

The oscillator circuit is enabled by setting the T1OSCEN bit of the T1CON register. The oscillator will continue to run during Sleep.

| Note: | The oscillator requires a start-up and   |

|-------|------------------------------------------|

|       | stabilization time before use. Thus,     |

|       | T1OSCEN should be set and a suitable     |

|       | delay observed prior to enabling Timer1. |

# 12.5 Timer1 Operation in Asynchronous Counter Mode

If control bit T1SYNC of the T1CON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 12.5.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

**Note:** When switching from synchronous to asynchronous operation, it is possible to skip an increment. When switching from asynchronous to synchronous operation, it is possible to produce an additional increment.

#### 12.5.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TMR1L register pair.

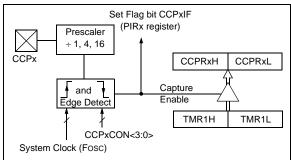

## 15.1 Capture Mode

In Capture mode, CCPRxH:CCPRxL captures the 16-bit value of the TMR1 register when an event occurs on pin CCPx. An event is defined as one of the following and is configured by the CCPxM<3:0> bits of the CCPxCON register:

- Every falling edge

- Every rising edge

- Every 4th rising edge

- Every 16th rising edge

When a capture is made, the Interrupt Request Flag bit CCPxIF of the PIRx register is set. The interrupt flag must be cleared in software. If another capture occurs before the value in the CCPRxH, CCPRxL register pair is read, the old captured value is overwritten by the new captured value (refer to Figure 15-1).

#### 15.1.1 CCPx PIN CONFIGURATION

In Capture mode, the CCPx pin should be configured as an input by setting the associated TRIS control bit.

Either RC1 or RB3 can be selected as the CCP2 pin. Refer to **Section 6.1** "Alternate Pin Function" for more information.

**Note:** If the CCPx pin is configured as an output, a write to the port can cause a capture condition.

#### FIGURE 15-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 15.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode or when Timer1 is clocked at Fosc, the capture operation may not work.

### 15.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit of the PIEx register clear to avoid false interrupts. Additionally, the user should clear the CCPxIF interrupt flag bit of the PIRx register following any change in operating mode.

Note: Clocking Timer1 from the system clock (Fosc) should not be used in Capture mode. In order for Capture mode to recognize the trigger event on the CCPx pin, Timer1 must be clocked from the instruction clock (Fosc/4) or from an external clock source.

#### 15.1.4 CCP PRESCALER

There are four prescaler settings specified by the CCPxM<3:0> bits of the CCPxCON register. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another does not clear the prescaler and may generate a false interrupt. To avoid this unexpected operation, turn the module off by clearing the CCPxCON register before changing the prescaler (refer to Example 15-1).

#### EXAMPLE 15-1: CHANGING BETWEEN CAPTURE PRESCALERS

| BANKSEL | CCP1CON     | ;Set Bank bits to point |

|---------|-------------|-------------------------|

|         |             | ;to CCP1CON             |

| CLRF    | CCP1CON     | ;Turn CCP module off    |

| MOVLW   | NEW_CAPT_PS | ;Load the W reg with    |

|         |             | ; the new prescaler     |

|         |             | ; move value and CCP ON |

| MOVWF   | CCP1CON     | ;Load CCP1CON with this |

|         |             | ; value                 |

|         |             |                         |

#### 15.1.5 CAPTURE DURING SLEEP

Capture mode depends upon the Timer1 module for proper operation. There are two options for driving the Timer1 module in Capture mode. It can be driven by the instruction clock (Fosc/4), or by an external clock source.

If Timer1 is clocked by FOSC/4, then Timer1 will not increment during Sleep. When the device wakes from Sleep, Timer1 will continue from its previous state.

If Timer1 is clocked by an external clock source, then Capture mode will operate as defined in **Section 15.1** "**Capture Mode**".

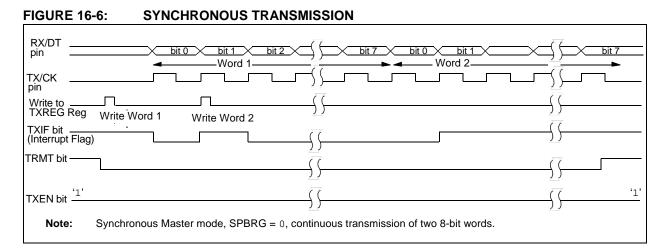

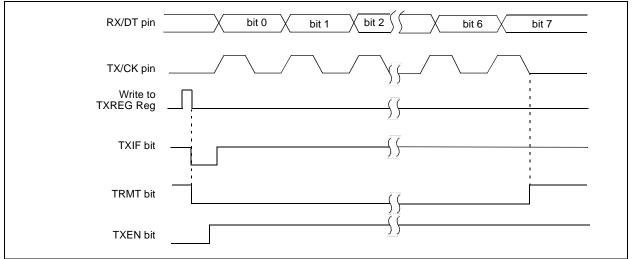

#### FIGURE 16-7: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

#### TABLE 16-6: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Name   | Bit 7    | Bit 6       | Bit 5      | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|----------|-------------|------------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE      | PEIE        | TOIE       | INTE   | RBIE   | T0IF   | INTF   | RBIF   | 0000 000x            | 0000 000x                       |

| PIE1   | TMR1GIE  | ADIE        | RCIE       | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| PIR1   | TMR1GIF  | ADIF        | RCIF       | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| RCSTA  | SPEN     | RX9         | SREN       | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 0000 000x            | 0000 000x                       |

| SPBRG  | BRG7     | BRG6        | BRG5       | BRG4   | BRG3   | BRG2   | BRG1   | BRG0   | 0000 0000            | 0000 0000                       |

| TRISC  | TRISC7   | TRISC6      | TRISC5     | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 1111 1111            | 1111 1111                       |

| TXREG  | AUSART T | ransmit Dat | a Register |        |        |        |        |        | 0000 0000            | 0000 0000                       |

| TXSTA  | CSRC     | TX9         | TXEN       | SYNC   | _      | BRGH   | TRMT   | TX9D   | 0000 -010            | 0000 -010                       |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for synchronous master transmission.

#### START AND STOP CONDITIONS 17.2.2

During times of no data transfer (Idle time), both the clock line (SCL) and the data line (SDA) are pulled high through external pull-up resistors. The Start and Stop conditions determine the start and stop of data transmission. The Start condition is defined as a high-to-low transition of the SDA line while SCL is high. The Stop condition is defined as a low-to-high transition of the SDA line while SCL is high.

Figure 17-9 shows the Start and Stop conditions. A master device generates these conditions for starting and terminating data transfer. Due to the definition of the Start and Stop conditions, when data is being transmitted, the SDA line can only change state when the SCL line is low.

#### ACKNOWLEDGE 17.2.3

After the valid reception of an address or data byte, the hardware automatically will generate the Acknowledge (ACK) pulse and load the SSPBUF register with the received value currently in the SSPSR register. There are certain conditions that will cause the SSP module not to generate this ACK pulse. They include any or all of the following:

- The Buffer Full bit, BF of the SSPSTAT register, was set before the transfer was received.

- The SSP Overflow bit. SSPOV of the SSPCON register, was set before the transfer was received.

- The SSP module is being operated in Firmware Master mode.

In such a case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF of the PIR1 register is set. Table 17-2 shows the results of when a data transfer byte is received, given the status of bits BF and SSPOV. Flag bit BF is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

# ٦ SDA SCL S Р Change of Change of Data Allowed Data Allowed Start Stop Condition Condition

|    | its as Data<br>s Received | $SSPSR \to SSPBUF$ | Generate ACK<br>Pulse | Set bit SSPIF<br>(SSP Interrupt occurs |  |  |

|----|---------------------------|--------------------|-----------------------|----------------------------------------|--|--|

| BF | SSPOV                     |                    | Puise                 | if enabled)                            |  |  |

| 0  | 0                         | Yes                | Yes                   | Yes                                    |  |  |

| 1  | 0                         | No                 | No                    | Yes                                    |  |  |

| 1  | 1                         | No                 | No                    | Yes                                    |  |  |

| 0  | 1                         | No                 | No                    | Yes                                    |  |  |

Note 1: Shaded cells show the conditions where the user software did not properly clear the overflow condition.

#### **FIGURE 17-9:** START AND STOP CONDITIONS

## 22.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

# 22.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

# PIC16(L)F722A/723A

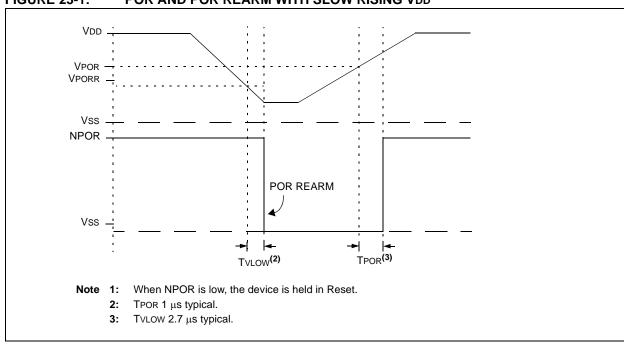

#### FIGURE 23-1: POR AND POR REARM WITH SLOW RISING VDD

### 23.2 DC Characteristics: PIC16(L)F722A/723A-I/E (Industrial, Extended) (Continued)

| PIC16LF722A/723A |                                     |     | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |         |                                   |                                                                               |                             |  |

|------------------|-------------------------------------|-----|------------------------------------------------------|---------|-----------------------------------|-------------------------------------------------------------------------------|-----------------------------|--|

| PIC16F722A/723A  |                                     |     | <b>l Operati</b><br>g tempera                        | ature - | $40^{\circ}\text{C} \le \text{T}$ | less otherwise stated)<br>A ≤ +85°C for industrial<br>A ≤ +125°C for extended |                             |  |

| Param            | Min                                 |     | Тур†                                                 | Max.    | Units                             |                                                                               | Conditions                  |  |

| No.              | Characteristics                     |     |                                                      |         |                                   | VDD                                                                           | Note                        |  |

|                  | Supply Current (IDD) <sup>(1,</sup> | 2)  |                                                      |         |                                   |                                                                               |                             |  |

| D014             |                                     | —   | 290                                                  | 330     | μA                                | 1.8                                                                           | Fosc = 4 MHz                |  |

|                  | —                                   | 460 | 500                                                  | μA      | 3.0                               | EC Oscillator mode                                                            |                             |  |

| D014             |                                     |     | 300                                                  | 430     | μA                                | 1.8                                                                           | Fosc = 4 MHz                |  |

|                  |                                     |     | 450                                                  | 655     | μA                                | 3.0                                                                           | EC Oscillator mode (Note 5) |  |

|                  |                                     | —   | 500                                                  | 730     | μΑ                                | 5.0                                                                           |                             |  |

| D015             |                                     | _   | 100                                                  | 130     | μA                                | 1.8                                                                           | Fosc = 500 kHz              |  |

|                  |                                     | —   | 120                                                  | 150     | μA                                | 3.0                                                                           | MFINTOSC mode               |  |

| D015             |                                     | _   | 115                                                  | 195     | μΑ                                | 1.8                                                                           | Fosc = 500 kHz              |  |

|                  |                                     | —   | 135                                                  | 200     | μA                                | 3.0                                                                           | MFINTOSC mode (Note 5)      |  |

|                  |                                     | —   | 150                                                  | 220     | μA                                | 5.0                                                                           |                             |  |

| D016             |                                     | _   | 650                                                  | 800     | μΑ                                | 1.8                                                                           | Fosc = 8 MHz                |  |

|                  |                                     | —   | 1000                                                 | 1200    | μΑ                                | 3.0                                                                           | HFINTOSC mode               |  |

| D016             |                                     | _   | 625                                                  | 850     | μA                                | 1.8                                                                           | Fosc = 8 MHz                |  |

|                  |                                     | —   | 1000                                                 | 1200    | μΑ                                | 3.0                                                                           | HFINTOSC mode (Note 5)      |  |

|                  |                                     | —   | 1100                                                 | 1500    | μΑ                                | 5.0                                                                           |                             |  |

| D017             |                                     | —   | 1.0                                                  | 1.2     | mA                                | 1.8                                                                           | Fosc = 16 MHz               |  |

|                  |                                     | _   | 1.5                                                  | 1.85    | mA                                | 3.0                                                                           | HFINTOSC mode               |  |

| D017             |                                     |     | 1                                                    | 1.2     | mA                                | 1.8                                                                           | Fosc = 16 MHz               |  |

|                  |                                     | _   | 1.5                                                  | 1.7     | mA                                | 3.0                                                                           | HFINTOSC mode (Note 5)      |  |

|                  |                                     | —   | 1.7                                                  | 2.1     | mA                                | 5.0                                                                           |                             |  |

| D018             |                                     | _   | 210                                                  | 240     | μA                                | 1.8                                                                           | Fosc = 4 MHz                |  |

|                  |                                     |     | 340                                                  | 380     | μΑ                                | 3.0                                                                           | EXTRC mode (Note 3, Note 5) |  |

| D018             |                                     | _   | 225                                                  | 320     | μA                                | 1.8                                                                           | Fosc = 4 MHz                |  |

|                  |                                     | _   | 360                                                  | 445     | μΑ                                | 3.0                                                                           | EXTRC mode (Note 3, Note 5) |  |

|                  |                                     | —   | 410                                                  | 650     | μΑ                                | 5.0                                                                           |                             |  |

| D019             |                                     |     | 1.6                                                  | 1.9     | mA                                | 3.0                                                                           | Fosc = 20 MHz               |  |

|                  |                                     | —   | 2.0                                                  | 2.8     | mA                                | 3.6                                                                           | HS Oscillator mode          |  |

| D019             |                                     |     | 1.6                                                  | 2       | mA                                | 3.0                                                                           | Fosc = 20 MHz               |  |

|                  |                                     |     | 1.9                                                  | 3.2     | mA                                | 5.0                                                                           | HS Oscillator mode (Note 5) |  |

**Note 1:** The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

**3:** For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in kΩ.

4: FVR and BOR are disabled.

5: 0.1 μF capacitor on VCAP (RA0).

# 23.3 DC Characteristics: PIC16(L)F722A/723A-I/E (Power-Down) (Continued)

| PIC16LF7        |                         |                      |      |                                |                |                                                                                                                                |            |                                  |  |  |

|-----------------|-------------------------|----------------------|------|--------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------|------------|----------------------------------|--|--|

| PIC16F722A/723A |                         |                      |      | r <b>d Operat</b><br>ng temper |                | ditions (unless otherwise stated)<br>-40°C $\leq$ TA $\leq$ +85°C for industrial<br>-40°C $\leq$ TA $\leq$ +125°C for extended |            |                                  |  |  |

| Param<br>No.    | Device Characteristics  | Min.                 | Тур† | Max.<br>+85°C                  | Max.<br>+125°C | Units                                                                                                                          | Conditions |                                  |  |  |

|                 |                         |                      |      |                                |                |                                                                                                                                | VDD        | Note                             |  |  |

|                 | Power-down Base Current | (IPD) <sup>(2)</sup> | r    | n                              | 1              |                                                                                                                                | n          | T                                |  |  |

| D027            |                         |                      | 0.06 | 0.7                            | 5.0            | μA                                                                                                                             | 1.8        | A/D Current (Note 1, Note 4), no |  |  |

|                 |                         | _                    | 0.08 | 1.0                            | 5.5            | μA                                                                                                                             | 3.0        | conversion in progress           |  |  |

| D027            |                         |                      | 6    | 10.7                           | 18             | μA                                                                                                                             | 1.8        | A/D Current (Note 1, Note 4), n  |  |  |

|                 |                         |                      | 7    | 10.6                           | 20             | μΑ                                                                                                                             | 3.0        | conversion in progress           |  |  |

|                 |                         | —                    | 7.2  | 11.9                           | 22             | μA                                                                                                                             | 5.0        |                                  |  |  |

| D027A           |                         | —                    | 250  | 400                            | —              | μA                                                                                                                             | 1.8        | A/D Current (Note 1, Note 4),    |  |  |

|                 |                         | —                    | 250  | 400                            | —              | μA                                                                                                                             | 3.0        | conversion in progress           |  |  |

| D027A           |                         |                      | 280  | 430                            | —              | μΑ                                                                                                                             | 1.8        | A/D Current (Note 1, Note 4,     |  |  |

|                 |                         |                      | 280  | 430                            | —              | μΑ                                                                                                                             | 3.0        | Note 5), conversion in progress  |  |  |

|                 |                         | —                    | 280  | 430                            | —              | μΑ                                                                                                                             | ιA 5.0     |                                  |  |  |

| D028            |                         |                      | 2.2  | 3.2                            | 14.4           | μΑ                                                                                                                             | 1.8        | Cap Sense Low Power              |  |  |

|                 |                         | —                    | 3.3  | 4.4                            | 15.6           | μA                                                                                                                             | 3.0        | Oscillator mode                  |  |  |

| D028            |                         | —                    | 6.5  | 13                             | 21             | μΑ                                                                                                                             | 1.8        | Cap Sense Low Power              |  |  |

|                 |                         | —                    | 8    | 14                             | 23             | μΑ                                                                                                                             | 3.0        | Oscillator mode                  |  |  |

|                 |                         | —                    | 8    | 14                             | 25             | μΑ                                                                                                                             | 5.0        |                                  |  |  |

| D028A           |                         |                      | 4.2  | 6                              | 17             | μA                                                                                                                             | 1.8        | Cap Sense Medium Power           |  |  |

|                 |                         | —                    | 6    | 7                              | 18             | μA                                                                                                                             | 3.0        | Oscillator mode                  |  |  |

| D028A           |                         | _                    | 8.5  | 15.5                           | 23             | μA                                                                                                                             | 1.8        | Cap Sense Medium Power           |  |  |

|                 |                         | _                    | 11   | 17                             | 24             | μΑ                                                                                                                             | 3.0        | Oscillator mode                  |  |  |

|                 |                         | _                    | 11   | 18                             | 27             | μA                                                                                                                             | 5.0        |                                  |  |  |

| D028B           |                         | _                    | 12   | 14                             | 25             | μA                                                                                                                             | 1.8        | Cap Sense High Power             |  |  |

|                 |                         | _                    | 32   | 35                             | 44             | μA                                                                                                                             | 3.0        | Oscillator mode                  |  |  |

| D028B           |                         | _                    | 16   | 20                             | 31             | μΑ                                                                                                                             | 1.8        | Cap Sense High Power             |  |  |

|                 |                         | _                    | 36   | 41                             | 50             | μΑ                                                                                                                             | 3.0        | Oscillator mode                  |  |  |

|                 |                         |                      | 42   | 49                             | 58             | μA                                                                                                                             | 5.0        | 1                                |  |  |

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral △ current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD.

3: Fixed Voltage Reference is automatically enabled whenever the BOR is enabled.

4: A/D oscillator source is FRC.

5: 0.1  $\mu$ F capacitor on VCAP (RA0).

### TABLE 23-7: PIC16F722A/723A A/D CONVERTER (ADC) CHARACTERISTICS:

| Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |                                                   |      |      |      |       |                                                                     |

|--------------------------------------------------------------------------------------------------------------------------|------|---------------------------------------------------|------|------|------|-------|---------------------------------------------------------------------|

| Param<br>No.                                                                                                             | Sym. | Characteristic                                    | Min. | Тур† | Max. | Units | Conditions                                                          |

| AD01                                                                                                                     | Nr   | Resolution                                        | —    |      | 8    | bit   |                                                                     |

| AD02                                                                                                                     | EIL  | Integral Error                                    | —    |      | ±1.7 | LSb   | VREF = 3.0V                                                         |

| AD03                                                                                                                     | Edl  | Differential Error                                | _    | —    | ±1   | LSb   | No missing codes<br>VREF = 3.0V                                     |

| AD04                                                                                                                     | EOFF | Offset Error                                      | —    | —    | ±2.2 | LSb   | VREF = 3.0V                                                         |

| AD05                                                                                                                     | Egn  | Gain Error                                        | _    | _    | ±1.5 | LSb   | VREF = 3.0V                                                         |

| AD06                                                                                                                     | Vref | Reference Voltage <sup>(3)</sup>                  | 1.8  | _    | Vdd  | V     |                                                                     |

| AD07                                                                                                                     | VAIN | Full-Scale Range                                  | Vss  | —    | VREF | V     |                                                                     |

| AD08                                                                                                                     | ZAIN | Recommended Impedance of<br>Analog Voltage Source | _    | —    | 50   |       | Can go higher if external 0.01µF capacitor is present on input pin. |

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Total Absolute Error includes integral, differential, offset and gain errors.

- 2: The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

- **3:** When ADC is off, it will not consume any current other than leakage current. The power-down current specification includes any such leakage from the ADC module.

#### TABLE 23-8: PIC16F722A/723A A/D CONVERSION REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |                                                                 |            |         |            |          |                                          |

|----------------------------------------------------------------------------------------------------------------------|------|-----------------------------------------------------------------|------------|---------|------------|----------|------------------------------------------|

| Param<br>No.                                                                                                         | Sym. | Characteristic                                                  | Min.       | Тур†    | Max.       | Units    | Conditions                               |

| AD130*                                                                                                               | Tad  | A/D Clock Period<br>A/D Internal RC Oscillator<br>Period        | 1.0<br>1.0 | <br>2.0 | 9.0<br>6.0 | μs<br>μs | Tosc-based<br>ADCS<1:0> = 11 (ADRC mode) |

| AD131                                                                                                                | TCNV | Conversion Time (not including Acquisition Time) <sup>(1)</sup> | _          | 10.5    | —          | Tad      | Set GO/DONE bit to conversion complete   |

| AD132*                                                                                                               | TACQ | Acquisition Time                                                | —          | 1.0     | —          | μs       |                                          |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note** 1: The ADRES register may be read on the following TCY cycle.

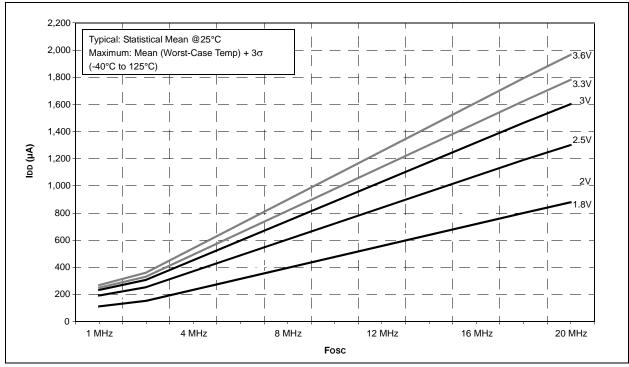

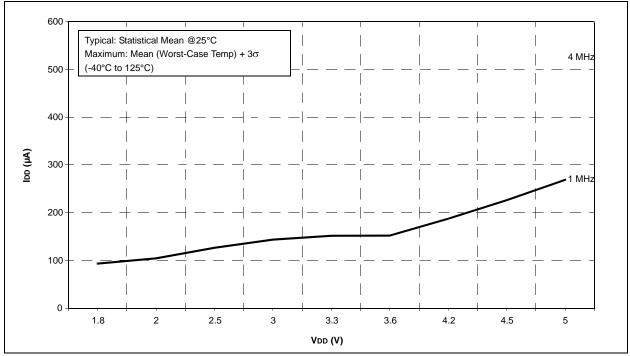

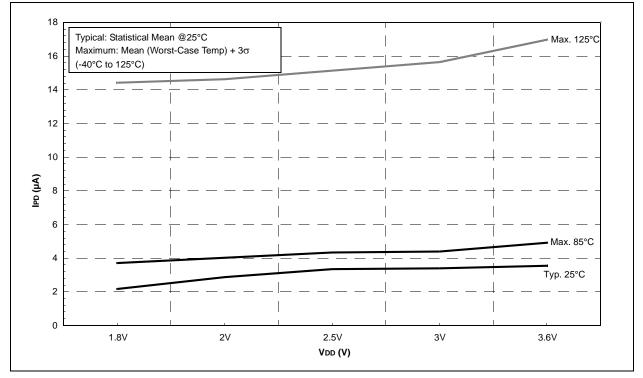

#### FIGURE 24-4: PIC16LF722A/723A TYPICAL IDD vs. Fosc OVER VDD, EC MODE

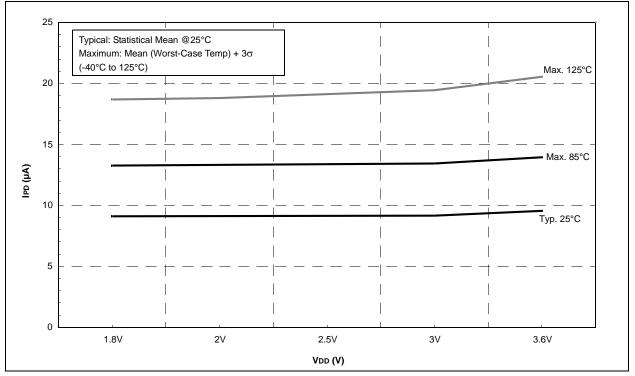

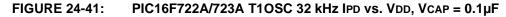

#### FIGURE 24-40: PIC16LF722A/723A CAP SENSE LOW POWER IPD vs. VDD

# THE MICROCHIP WEBSITE

Microchip provides online support via our website at www.microchip.com. This website is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the website contains the following information:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Micro-chip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip website at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

# **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the website at: http://www.microchip.com/support