Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 192 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 11x8b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 28-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f723a-i-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16(L)F722A/723A

| Address               | Name                  | Bit 7         | Bit 6         | Bit 5                     | Bit 4         | Bit 3                 | Bit 2           | Bit 1          | Bit 0    | Value on:<br>POR, BOR | Page   |

|-----------------------|-----------------------|---------------|---------------|---------------------------|---------------|-----------------------|-----------------|----------------|----------|-----------------------|--------|

| Bank 1                |                       |               |               |                           |               |                       |                 |                |          |                       |        |

| 80h <sup>(2)</sup>    | INDF                  | Addressing    | this location | uses conter               | nts of FSR to | address data          | a memory (no    | t a physical r | egister) | xxxx xxxx             | 22,30  |

| 81h                   | OPTION_REG            | RBPU          | INTEDG        | TOCS                      | TOSE          | PSA                   | PS2             | PS1            | PS0      | 1111 1111             | 19,30  |

| 82h <sup>(2)</sup>    | PCL                   | Program Co    | ounter (PC) L | east Signifie             | cant Byte     |                       |                 |                |          | 0000 0000             | 21,30  |

| 83h <sup>(2)</sup>    | STATUS                | IRP           | RP1           | RP0                       | TO            | PD                    | Z               | DC             | С        | 0001 1xxx             | 18,30  |

| 84h <sup>(2)</sup>    | FSR                   | Indirect Data | a Memory A    | ddress Point              | ter           |                       |                 |                |          | xxxx xxxx             | 22,30  |

| 85h                   | TRISA                 | TRISA7        | TRISA6        | TRISA5                    | TRISA4        | TRISA3                | TRISA2          | TRISA1         | TRISA0   | 1111 1111             | 43,30  |

| 86h                   | TRISB                 | TRISB7        | TRISB6        | TRISB5                    | TRISB4        | TRISB3                | TRISB2          | TRISB1         | TRISB0   | 1111 1111             | 52,30  |

| 87h                   | TRISC                 | TRISC7        | TRISC6        | TRISC5                    | TRISC4        | TRISC3                | TRISC2          | TRISC1         | TRISC0   | 1111 1111             | 62,30  |

| 89h                   | TRISE                 | _             |               |                           | _             | TRISE3 <sup>(5)</sup> | _               | _              | _        | 1111                  | 69,30  |

| 8Ah <sup>(1, 2)</sup> | PCLATH                | _             |               |                           | Write Buffer  | for the upper         | r 5 bits of the | Program Co     | unter    | 0 0000                | 21,30  |

| 8Bh <sup>(2)</sup>    | INTCON                | GIE           | PEIE          | TOIE                      | INTE          | RBIE                  | T0IF            | INTF           | RBIF     | x000 000x             | 36,30  |

| 8Ch                   | PIE1                  | TMR1GIE       | ADIE          | RCIE                      | TXIE          | SSPIE                 | CCP1IE          | TMR2IE         | TMR1IE   | 0000 0000             | 37,31  |

| 8Dh                   | PIE2                  | —             | -             | -                         | —             | —                     | _               | —              | CCP2IE   | 0                     | 38,31  |

| 8Eh                   | PCON                  | _             |               |                           | _             | _                     | _               | POR            | BOR      | dd                    | 20,31  |

| 8Fh                   | T1GCON                | TMR1GE        | T1GPOL        | T1GTM                     | T1GSPM        | T1GGO<br>DONE         | T1GVAL          | T1GSS1         | T1GSS0   | 0000 0x00             | 104,31 |

| 90h                   | OSCCON                | —             | -             | IRCF1                     | IRCF0         | ICSL                  | ICSS            | —              | _        | 10 qq                 | 73,31  |

| 91h                   | OSCTUNE               | —             |               | TUN5                      | TUN4          | TUN3                  | TUN2            | TUN1           | TUN0     | 00 0000               | 74,31  |

| 92h                   | PR2                   | Timer2 Peri   | od Register   |                           |               |                       |                 |                |          | 1111 1111             | 106,31 |

| 93h                   | SSPADD(4)             | Synchronou    | s Serial Port | t (I <sup>2</sup> C mode) | Address Reg   | ister                 |                 |                |          | 0000 0000             | 155,31 |

| 93h                   | SSPMSK <sup>(3)</sup> | Synchronou    | s Serial Port | t (I <sup>2</sup> C mode) | Address Mas   | k Register            |                 |                |          | 1111 1111             | 166,31 |

| 94h                   | SSPSTAT               | SMP           | CKE           | D/A                       | Р             | S                     | R/W             | UA             | BF       | 0000 0000             | 153,31 |

| 95h                   | WPUB                  | WPUB7         | WPUB6         | WPUB5                     | WPUB4         | WPUB3                 | WPUB2           | WPUB1          | WPUB0    | 1111 1111             | 52,31  |

| 96h                   | IOCB                  | IOCB7         | IOCB6         | IOCB5                     | IOCB4         | IOCB3                 | IOCB2           | IOCB1          | IOCB0    | 0000 0000             | 53,31  |

| 97h                   |                       | Unimpleme     | nted          |                           |               |                       |                 |                |          | _                     |        |

| 98h                   | TXSTA                 | CSRC          | TX9           | TXEN                      | SYNC          | _                     | BRGH            | TRMT           | TX9D     | 0000 -010             | 133,31 |

| 99h                   | SPBRG                 | BRG7          | BRG6          | BRG5                      | BRG4          | BRG3                  | BRG2            | BRG1           | BRG0     | 0000 0000             | 135,31 |

| 9Ah                   | _                     | Unimpleme     | nted          |                           |               |                       |                 |                |          | —                     | —      |

| 9Bh                   | —                     | Unimplemented |               |                           |               |                       |                 |                |          | _                     | _      |

| 9Ch                   | APFCON                | _             | _             | _                         | _             | —                     | _               | SSSEL          | CCP2SEL  | 00                    | 42,31  |

| 9Dh                   | FVRCON                | FVRRDY        | FVREN         | —                         | _             | _                     | _               | ADFVR1         | ADFVR0   | q000                  | 90,31  |

| 9Eh                   | —                     | Unimpleme     | nted          |                           |               |                       |                 |                |          | _                     | —      |

| 9Fh                   | ADCON1                | _             | ADCS2         | ADCS1                     | ADCS0         | _                     | _               | ADREF1         | ADREF0   | 000000                | 86,31  |

#### TABLE 2-1:PIC16(L)F722A/723A SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.

Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter.

**2:** These registers can be addressed from any bank.

3: Accessible only when SSPM<3:0> = 1001.

4: Accessible only when SSPM<3:0>  $\neq$  1001.

5: This bit is always '1' as RE3 is input-only.

# PIC16(L)F722A/723A

| TABLE 6-4: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTC |

|------------|--------------------------------------------|

|            |                                            |

| Name    | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0   | Register<br>on Page |

|---------|---------|---------|---------|---------|---------|--------|--------|---------|---------------------|

| APFCON  | —       | _       | _       | _       | —       | —      | SSSEL  | CCP2SEL | 42                  |

| CCP1CON | —       | _       | DC1B1   | DC1B0   | CCP1M3  | CCP1M2 | CCP1M1 | CCP1M0  | 115                 |

| CCP2CON | —       | —       | DC2B1   | DC2B0   | CCP2M3  | CCP2M2 | CCP2M1 | CCP2M0  | 115                 |

| PORTC   | RC7     | RC6     | RC5     | RC4     | RC3     | RC2    | RC1    | RC0     | 62                  |

| RCSTA   | SPEN    | RX9     | SREN    | CREN    | ADDEN   | FERR   | OERR   | RX9D    | 134                 |

| SSPCON  | WCOL    | SSPOV   | SSPEN   | CKP     | SSPM3   | SSPM2  | SSPM1  | SSPM0   | 152                 |

| SSPSTAT | SMP     | CKE     | D/Ā     | Р       | S       | R/W    | UA     | BF      | 153                 |

| T1CON   | TMR1CS1 | TMR1CS0 | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | —      | TMR10N  | 103                 |

| TXSTA   | CSRC    | TX9     | TXEN    | SYNC    | —       | BRGH   | TRMT   | TX9D    | 133                 |

| TRISC   | TRISC7  | TRISC6  | TRISC5  | TRISC4  | TRISC3  | TRISC2 | TRISC1 | TRISC0  | 62                  |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTC.

# 8.0 DEVICE CONFIGURATION

Device configuration consists of Configuration Word 1 and Configuration Word 2 registers, code protection and device ID.

## 8.1 Configuration Words

There are several Configuration Word bits that allow different oscillator and memory protection options. These are implemented as Configuration Word 1 register at 2007h and Configuration Word 2 register at 2008h. These registers are only accessible during programming.

#### REGISTER 8-1: CONFIG1: CONFIGURATION WORD REGISTER 1

|                    |                                                                            | R/P-1                                                                                                                             | R/P-1                                      | U-1 <sup>(4)</sup>                    | R/P-1              | R/P-1            | R/P-1  |

|--------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|---------------------------------------|--------------------|------------------|--------|

|                    |                                                                            | DEBUG                                                                                                                             | PLLEN                                      | —                                     | BORV               | BOREN1           | BOREN0 |

|                    |                                                                            | bit 13                                                                                                                            | 1                                          |                                       |                    |                  | bit    |

|                    |                                                                            |                                                                                                                                   |                                            |                                       |                    |                  |        |

| U-1 <sup>(4)</sup> | R/P-1                                                                      | R/P-1                                                                                                                             | R/P-1                                      | R/P-1                                 | R/P-1              | R/P-1            | R/P-1  |

| —                  | CP                                                                         | MCLRE                                                                                                                             | PWRTE                                      | WDTE                                  | FOSC2              | FOSC1            | FOSC0  |

| oit 7              |                                                                            |                                                                                                                                   |                                            |                                       |                    |                  | bit    |

|                    |                                                                            |                                                                                                                                   |                                            |                                       |                    |                  |        |

| Legend:            |                                                                            | P = Programma                                                                                                                     | able bit                                   |                                       |                    |                  |        |

| R = Readable       | bit                                                                        | W = Writable bi                                                                                                                   | t                                          | U = Unimplem                          | ented bit, read as | s 'O'            |        |

| -n = Value at F    | POR                                                                        | '1' = Bit is set                                                                                                                  |                                            | '0' = Bit is clea                     | ired               | x = Bit is unkno | own    |

| oit 13<br>oit 12   | 1 = In-circuit o<br>0 = In-circuit o<br><b>PLLEN:</b> INTC<br>0 = INTOSC f | ircuit Debugger M<br>debugger disabled<br>debugger enabled<br>DSC PLL Enable b<br>requency is 500 k<br>requency is 16 Mł          | , RB6/ICSPCLI<br>, RB6/ICSPCLI<br>it<br>Hz |                                       | 0                  |                  |        |

| bit 11             |                                                                            | ted: Read as '1'                                                                                                                  | (- )                                       |                                       |                    |                  |        |

| bit 10             | 0 = Brown-ou                                                               | n-out Reset Voltag<br>t Reset Voltage (V<br>t Reset Voltage (V                                                                    | BOR) set to 2.5                            |                                       |                    |                  |        |

| bit 9-8            | BOREN<1:0><br>0x = BOR dis                                                 | Brown-out Rese<br>abled (preconditio<br>abled during opera                                                                        | t Selection bits                           | 1)                                    |                    |                  |        |

| oit 7              | Unimplemen                                                                 | ted: Read as '1'                                                                                                                  |                                            |                                       |                    |                  |        |

| bit 6              | CP: Code Pro                                                               | otection bit <sup>(2)</sup>                                                                                                       |                                            |                                       |                    |                  |        |

|                    |                                                                            | memory code prot                                                                                                                  |                                            |                                       |                    |                  |        |

| bit 5              | MCLRE: RE3<br>1 = RE3/MCL                                                  | memory code prot<br>$\sqrt{MCLR}$ Pin Functi<br>$\overline{R}$ pin function is $\overline{R}$<br>$\overline{R}$ pin function is d | on Select bit <sup>(3)</sup><br>ICLR       |                                       | d to VDD           |                  |        |

| bit 4              |                                                                            | ver-up Timer Enab<br>sabled                                                                                                       | •                                          |                                       |                    |                  |        |

| bit 3              | WDTE: Watch<br>1 = WDT enal<br>0 = WDT disa                                |                                                                                                                                   | e bit                                      |                                       |                    |                  |        |

| 2: TI<br>3: W      | he entire program<br>/hen MCLR is ass                                      | t Reset does not a<br>memory will be el<br>erted in INTOSC o<br>sks unimplemente                                                  | rased when the<br>or RC mode, the          | code protection<br>e internal clock c | is turned off.     | ed.              |        |

4: MPLAB<sup>®</sup> X IDE masks unimplemented Configuration bits to '0'.

# 9.1 ADC Configuration

When configuring and using the ADC the following functions must be considered:

- Port configuration

- Channel selection

- ADC voltage reference selection

- ADC conversion clock source

- Interrupt control

- Results formatting

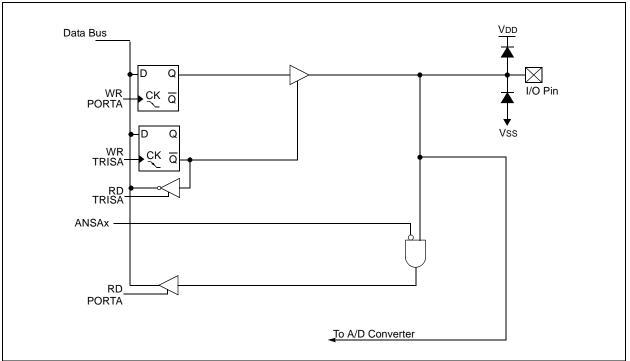

### 9.1.1 PORT CONFIGURATION

The ADC can be used to convert both analog and digital signals. When converting analog signals, the I/O pin should be configured for analog by setting the associated TRIS and ANSEL bits. Refer to **Section 6.0 "I/O Ports"** for more information.

| Note: | Analog voltages on any pin that is defined |

|-------|--------------------------------------------|

|       | as a digital input may cause the input     |

|       | buffer to conduct excess current.          |

#### 9.1.2 CHANNEL SELECTION

The CHS bits of the ADCON0 register determine which channel is connected to the sample and hold circuit.

When changing channels, a delay is required before starting the next conversion. Refer to **Section 9.2 "ADC Operation"** for more information.

# 9.1.3 ADC VOLTAGE REFERENCE

The ADREF bits of the ADCON1 register provides control of the positive voltage reference. The positive voltage reference can be either VDD, an external voltage source or the internal Fixed Voltage Reference. The negative voltage reference is always connected to the ground reference. See **Section 10.0** "**Fixed Voltage Reference**" for more details.

### 9.1.4 CONVERSION CLOCK

The source of the conversion clock is software selectable via the ADCS bits of the ADCON1 register. There are seven possible clock options:

- Fosc/2

- Fosc/4

- Fosc/8

- Fosc/16

- Fosc/32

- Fosc/64

- FRC (dedicated internal oscillator)

The time to complete one bit conversion is defined as TAD. One full 8-bit conversion requires 10 TAD periods as shown in Figure 9-2.

For correct conversion, the appropriate TAD specification must be met. Refer to the A/D conversion requirements in **Section 23.0 "Electrical Specifications"** for more information. Table 9-1 gives examples of appropriate ADC clock selections.

Note: Unless using the FRC, any changes in the system clock frequency will change the ADC clock frequency, which may adversely affect the ADC result.

### 12.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The T1CKPS bits of the T1CON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

# 12.4 Timer1 Oscillator

A dedicated low-power 32.768 kHz oscillator circuit is built-in between pins T1OSI (input) and T1OSO (amplifier output). This internal circuit is to be used in conjunction with an external 32.768 kHz crystal.

The oscillator circuit is enabled by setting the T1OSCEN bit of the T1CON register. The oscillator will continue to run during Sleep.

| Note: | The oscillator requires a start-up and   |

|-------|------------------------------------------|

|       | stabilization time before use. Thus,     |

|       | T1OSCEN should be set and a suitable     |

|       | delay observed prior to enabling Timer1. |

# 12.5 Timer1 Operation in Asynchronous Counter Mode

If control bit T1SYNC of the T1CON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 12.5.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

**Note:** When switching from synchronous to asynchronous operation, it is possible to skip an increment. When switching from asynchronous to synchronous operation, it is possible to produce an additional increment.

#### 12.5.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TMR1L register pair.

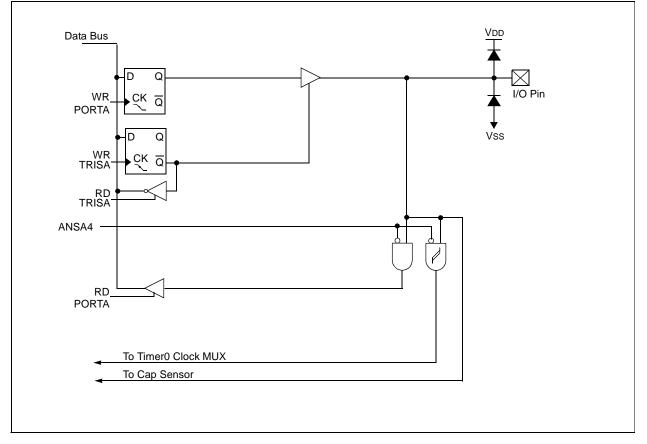

## 14.5 Software Control

The software portion of the capacitive sensing module is required to determine the change in frequency of the capacitive sensing oscillator. This is accomplished by the following:

- Setting a fixed-time base to acquire counts on Timer0 or Timer1

- Establishing the nominal frequency for the capacitive sensing oscillator

- Establishing the reduced frequency for the capacitive sensing oscillator due to an additional capacitive load

- Set the frequency threshold

#### 14.5.1 NOMINAL FREQUENCY (NO CAPACITIVE LOAD)

To determine the nominal frequency of the capacitive sensing oscillator:

- Remove any extra capacitive load on the selected CPSx pin

- At the start of the fixed-time base, clear the timer resource

- At the end of the fixed-time base, save the value in the timer resource

The value of the timer resource is the number of oscillations of the capacitive sensing oscillator for the given time base. The frequency of the capacitive sensing oscillator is equal to the number of counts on in the timer divided by the period of the fixed-time base.

### 14.5.2 REDUCED FREQUENCY (ADDITIONAL CAPACITIVE LOAD)

The extra capacitive load will cause the frequency of the capacitive sensing oscillator to decrease. To determine the reduced frequency of the capacitive sensing oscillator:

- Add a typical capacitive load on the selected CPSx pin

- Use the same fixed-time base as the nominal frequency measurement

- At the start of the fixed-time base, clear the timer resource

- At the end of the fixed-time base, save the value in the timer resource

The value of the timer resource is the number of oscillations of the capacitive sensing oscillator with an additional capacitive load. The frequency of the capacitive sensing oscillator is equal to the number of counts on in the timer divided by the period of the fixedtime base. This frequency should be less than the value obtained during the nominal frequency measurement.

### 14.5.3 FREQUENCY THRESHOLD

The frequency threshold should be placed midway between the value of nominal frequency and the reduced frequency of the capacitive sensing oscillator. Refer to Application Note *AN1103, Software Handling for Capacitive Sensing* (DS01103) for more detailed information the software required for capacitive sensing module.

**Note:** For more information on general capacitive sensing refer to Application Notes:

- •AN1101, Introduction to Capacitive Sensing (DS01101)

- •AN1102, Layout and Physical Design Guidelines for Capacitive Sensing (DS01102)

| Name   | Bit 7    | Bit 6       | Bit 5      | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|----------|-------------|------------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE      | PEIE        | TOIE       | INTE   | RBIE   | T0IF   | INTF   | RBIF   | 0000 000x            | 0000 000x                       |

| PIE1   | TMR1GIE  | ADIE        | RCIE       | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| PIR1   | TMR1GIF  | ADIF        | RCIF       | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| RCREG  | AUSART R | eceive Data | a Register |        |        |        |        |        | 0000 0000            | 0000 0000                       |

| RCSTA  | SPEN     | RX9         | SREN       | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 0000 000x            | 0000 000x                       |

| SPBRG  | BRG7     | BRG6        | BRG5       | BRG4   | BRG3   | BRG2   | BRG1   | BRG0   | 0000 0000            | 0000 0000                       |

| TRISC  | TRISC7   | TRISC6      | TRISC5     | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 1111 1111            | 1111 1111                       |

| TXSTA  | CSRC     | TX9         | TXEN       | SYNC   | —      | BRGH   | TRMT   | TX9D   | 0000 -010            | 0000 -010                       |

### TABLE 16-2: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for asynchronous reception.

|        |                |            |                             |                   |            | <b>SYNC</b> = 0,            | , BRGH = 0     |            |                             |                |                    |                             |  |

|--------|----------------|------------|-----------------------------|-------------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|--------------------|-----------------------------|--|

| BAUD   | Fosc           | ; = 20.00  | 0 MHz                       | Fosc = 18.432 MHz |            |                             | Fosc           | = 16.000   | 00 MHz                      | Fosc           | Fosc = 11.0592 MHz |                             |  |

| RATE   | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error         | SPBRG<br>value<br>(decimal) |  |

| 300    |                | _          | _                           |                   | _          | _                           | —              | —          | —                           |                | _                  | _                           |  |

| 1200   | 1221           | 1.73       | 255                         | 1200              | 0.00       | 239                         | 1201           | 0.08       | 207                         | 1200           | 0.00               | 143                         |  |

| 2400   | 2404           | 0.16       | 129                         | 2400              | 0.00       | 119                         | 2403           | 0.16       | 103                         | 2400           | 0.00               | 71                          |  |

| 9600   | 9470           | -1.36      | 32                          | 9600              | 0.00       | 29                          | 9615           | 0.16       | 25                          | 9600           | 0.00               | 17                          |  |

| 10417  | 10417          | 0.00       | 29                          | 10286             | -1.26      | 27                          | 10416          | -0.01      | 23                          | 10165          | -2.42              | 16                          |  |

| 19.2k  | 19.53k         | 1.73       | 15                          | 19.20k            | 0.00       | 14                          | 19.23k         | 0.16       | 12                          | 19.20k         | 0.00               | 8                           |  |

| 57.6k  | —              | —          | _                           | 57.60k            | 0.00       | 7                           | —              | —          | _                           | 57.60k         | 0.00               | 2                           |  |

| 115.2k | —              | _          | —                           | _                 | _          | —                           | _              | —          | —                           | —              | —                  | —                           |  |

#### TABLE 16-5: BAUD RATES FOR ASYNCHRONOUS MODES

|        | <b>SYNC</b> = 0, <b>BRGH</b> = 0 |            |                             |                  |            |                             |                |            |                             |                |                  |                             |  |

|--------|----------------------------------|------------|-----------------------------|------------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------------|-----------------------------|--|

| BAUD   | Fosc = 8.000 MHz                 |            |                             | Fosc = 4.000 MHz |            |                             | Fosc           | = 3.686    | 4 MHz                       | Fos            | Fosc = 1.000 MHz |                             |  |

| RATE   | Actual<br>Rate                   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error       | SPBRG<br>value<br>(decimal) |  |

| 300    | _                                | _          | _                           | 300              | 0.16       | 207                         | 300            | 0.00       | 191                         | 300            | 0.16             | 51                          |  |

| 1200   | 1202                             | 0.16       | 103                         | 1202             | 0.16       | 51                          | 1200           | 0.00       | 47                          | 1202           | 0.16             | 12                          |  |

| 2400   | 2404                             | 0.16       | 51                          | 2404             | 0.16       | 25                          | 2400           | 0.00       | 23                          | —              | _                | _                           |  |

| 9600   | 9615                             | 0.16       | 12                          | —                | _          | _                           | 9600           | 0.00       | 5                           | —              | _                | _                           |  |

| 10417  | 10417                            | 0.00       | 11                          | 10417            | 0.00       | 5                           | —              | _          | _                           | —              | _                | _                           |  |

| 19.2k  | —                                | _          | _                           | —                | _          | _                           | 19.20k         | 0.00       | 2                           | —              | _                | _                           |  |

| 57.6k  | —                                | _          | —                           | —                | —          | —                           | 57.60k         | 0.00       | 0                           | —              | _                | —                           |  |

| 115.2k |                                  | —          | —                           |                  | —          | —                           |                | _          | —                           |                | —                | —                           |  |

|        |                |                   |                             |                |                   | SYNC = 0,                   | BRGH = 2       | BRGH = 1   |                             |                |                    |                             |  |  |

|--------|----------------|-------------------|-----------------------------|----------------|-------------------|-----------------------------|----------------|------------|-----------------------------|----------------|--------------------|-----------------------------|--|--|

| BAUD   | Fosc           | Fosc = 20.000 MHz |                             |                | Fosc = 18.432 MHz |                             |                | = 16.000   | 00 MHz                      | Fosc           | Fosc = 11.0592 MHz |                             |  |  |

| RATE   | Actual<br>Rate | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error         | SPBRG<br>value<br>(decimal) |  |  |

| 300    | —              |                   | _                           |                |                   | _                           | _              | —          | —                           | —              | —                  | _                           |  |  |

| 1200   | —              | —                 | —                           | —              | —                 | —                           | —              | —          | —                           | —              | —                  | —                           |  |  |

| 2400   | —              | _                 | _                           | _              | _                 | _                           | _              | _          | —                           | —              | —                  | _                           |  |  |

| 9600   | 9615           | 0.16              | 129                         | 9600           | 0.00              | 119                         | 9615           | 0.16       | 103                         | 9600           | 0.00               | 71                          |  |  |

| 10417  | 10417          | 0.00              | 119                         | 10378          | -0.37             | 110                         | 10417          | 0.00       | 95                          | 10473          | 0.53               | 65                          |  |  |

| 19.2k  | 19.23k         | 0.16              | 64                          | 19.20k         | 0.00              | 59                          | 19.23k         | 0.16       | 51                          | 19.20k         | 0.00               | 35                          |  |  |

| 57.6k  | 56.82k         | -1.36             | 21                          | 57.60k         | 0.00              | 19                          | 58.8k          | 2.12       | 16                          | 57.60k         | 0.00               | 11                          |  |  |

| 115.2k | 113.64k        | -1.36             | 10                          | 115.2k         | 0.00              | 9                           | —              | _          | _                           | 115.2k         | 0.00               | 5                           |  |  |

### 16.3 AUSART Synchronous Mode

Synchronous serial communications are typically used in systems with a single master and one or more slaves. The master device contains the necessary circuitry for baud rate generation and supplies the clock for all devices in the system. Slave devices can take advantage of the master clock by eliminating the internal clock generation circuitry.

There are two signal lines in Synchronous mode: a bidirectional data line and a clock line. Slaves use the external clock supplied by the master to shift the serial data into and out of their respective receive and transmit shift registers. Since the data line is bidirectional, synchronous operation is half-duplex only. Half-duplex refers to the fact that master and slave devices can receive and transmit data but not both simultaneously. The AUSART can operate as either a master or slave device.

Start and Stop bits are not used in synchronous transmissions.

#### 16.3.1 SYNCHRONOUS MASTER MODE

The following bits are used to configure the AUSART for Synchronous Master operation:

- SYNC = 1

- CSRC = 1

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Setting the CSRC bit of the TXSTA register configures the device as a master. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the AUSART.

#### 16.3.1.1 Master Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a master transmits the clock on the TX/ CK line. The TX/CK pin output driver is automatically enabled when the AUSART is configured for synchronous transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One clock cycle is generated for each data bit. Only as many clock cycles are generated as there are data bits.

#### 16.3.1.2 Synchronous Master Transmission

Data is transferred out of the device on the RX/DT pin. The RX/DT and TX/CK pin output drivers are automatically enabled when the AUSART is configured for synchronous master transmit operation.

A transmission is initiated by writing a character to the TXREG register. If the TSR still contains all or part of a previous character, the new character data is held in the TXREG until the last bit of the previous character has been transmitted. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXREG is immediately transferred to the TSR. The transmission of the character commences immediately following the transfer of the data to the TSR from the TXREG.

Each data bit changes on the leading edge of the master clock and remains valid until the subsequent leading clock edge.

Note: The TSR register is not mapped in data memory, so it is not available to the user.

16.3.1.3 Synchronous Master Transmission Setup:

- Initialize the SPBRG register and the BRGH bit to achieve the desired baud rate (refer to Section 16.2 "AUSART Baud Rate Generator (BRG)").

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Disable Receive mode by clearing bits SREN and CREN.

- 4. Enable Transmit mode by setting the TXEN bit.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. If interrupts are desired, set the TXIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded in the TX9D bit.

- 8. Start transmission by loading data to the TXREG register.

# 16.3.2.3 AUSART Synchronous Slave Reception

The operation of the Synchronous Master and Slave modes is identical (Section 16.3.1.4 "Synchronous Master Reception"), with the following exceptions:

- Sleep

- CREN bit is always set, therefore the receiver is never Idle

- SREN bit, which is a "don't care" in Slave mode

A character may be received while in Sleep mode by setting the CREN bit prior to entering Sleep. Once the word is received, the RSR register will transfer the data to the RCREG register. If the RCIE interrupt enable bit of the PIE1 register is set, the interrupt generated will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will branch to the interrupt vector.

- 16.3.2.4 Synchronous Slave Reception Setup:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 3. If 9-bit reception is desired, set the RX9 bit.

- 4. Verify address detection is disabled by clearing the ADDEN bit of the RCSTA register.

- 5. Set the CREN bit to enable reception.

- The RCIF bit of the PIR1 register will be set when reception is complete. An interrupt will be generated if the RCIE bit of the PIE1 register was set.

- 7. If 9-bit mode is enabled, retrieve the Most Significant bit from the RX9D bit of the RCSTA register.

- 8. Retrieve the eight Least Significant bits from the receive FIFO by reading the RCREG register.

- 9. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register.

| Name   | Bit 7    | Bit 6       | Bit 5      | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|----------|-------------|------------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE      | PEIE        | TOIE       | INTE   | RBIE   | T0IF   | INTF   | RBIF   | 0000 000x            | 0000 000x                       |

| PIE1   | TMR1GIE  | ADIE        | RCIE       | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| PIR1   | TMR1GIF  | ADIF        | RCIF       | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| RCREG  | AUSART R | eceive Data | a Register |        |        |        |        |        | 0000 0000            | 0000 0000                       |

| RCSTA  | SPEN     | RX9         | SREN       | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 0000 000X            | 0000 000x                       |

| TRISC  | TRISC7   | TRISC6      | TRISC5     | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 1111 1111            | 1111 1111                       |

| TXSTA  | CSRC     | TX9         | TXEN       | SYNC   | —      | BRGH   | TRMT   | TX9D   | 0000 -010            | 0000 -010                       |

#### TABLE 16-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for synchronous slave reception.

# 18.0 PROGRAM MEMORY READ

The Flash program memory is readable during normal operation over the full VDD range of the device. To read data from program memory, five Special Function Registers (SFRs) are used:

- PMCON1

- PMDATL

- PMDATH

- PMADRL

- PMADRH

The value written to the PMADRH:PMADRL register pair determines which program memory location is read. The read operation will be initiated by setting the RD bit of the PMCON1 register. The program memory Flash controller takes two instructions to complete the read. As a consequence, after the RD bit has been set, the next two instructions will be ignored. To avoid conflict with program execution, it is recommended that the two instructions following the setting of the RD bit are NOP. When the read completes, the result is placed in the PMDATLH:PMDATL register pair. Refer to Example 18-1 for sample code.

**Note:** Code-protect does not effect the CPU from performing a read operation on the program memory. For more information, refer to **Section 8.2 "Code Protection"**

### EXAMPLE 18-1: PROGRAM MEMORY READ

BANKSEL PMADRL ; MOVE MS PROG ADDR, W; MOVWF PMADRH ;MS Byte of Program Address to read MOVF LS\_PROG\_ADDR, W; MOVWF PMADRL ;LS Byte of Program Address to read BANKSEL PMCON1 ; BSF PMCON1, RD; Initiate Read Required NOP NOP ;Any instructions here are ignored as program ;memory is read in second cycle after BSF BANKSEL PMDATL ; MOVF PMDATL, W;W = LS Byte of Program Memory Read MOVWF LOWPMBYTE; MOVF PMDATH, W;W = MS Byte of Program Memory Read MOVWF HIGHPMBYTE;

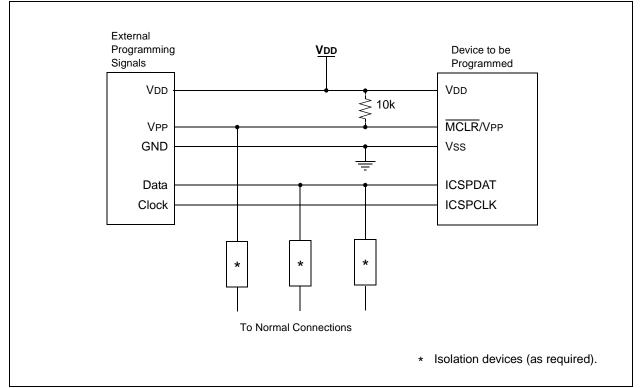

# 20.0 IN-CIRCUIT SERIAL PROGRAMMING<sup>™</sup> (ICSP<sup>™</sup>)

ICSP<sup>™</sup> programming allows customers to manufacture circuit boards with unprogrammed devices. Programming can be done after the assembly process allowing the device to be programmed with the most recent firmware or a custom firmware. Five pins are needed for ICSP<sup>™</sup> programming:

- ICSPCLK

- ICSPDAT

- MCLR/VPP

- VDD

- Vss

The device is placed into Program/Verify mode by holding the ICSPCLK and ICSPDAT pins low then raising the voltage on MCLR/VPP from 0v to VPP. In Program/Verify mode the Program Memory, User IDs and the Configuration Words are programmed through serial communications. The ICSPDAT pin is a bidirectional I/O used for transferring the serial data and the ISCPCLK pin is the clock input. For more information on ICSP<sup>TM</sup> refer to the "PIC16(L)F72X Memory Programming Specification" (DS41332).

**Note:** The ICD 2 produces a VPP voltage greater than the maximum VPP specification of the PIC16(L)F722A/723A. When using this programmer, an external circuit, such as the AC164112 MPLAB ICD 2 VPP voltage limiter, is required to keep the VPP voltage within the device specifications.

### FIGURE 20-1: TYPICAL CONNECTION FOR ICSP™ PROGRAMMING

## 22.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

### 22.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline

assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

## 22.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 22.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

# 23.0 ELECTRICAL SPECIFICATIONS

# Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                                                                                                                                                                                                    | 40°C to +125°C                      |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--|--|--|

| Storage temperature                                                                                                                                                                                                               | 65°C to +150°C                      |  |  |  |

| Voltage on VDD with respect to Vss, PIC16F722A/723A                                                                                                                                                                               | 0.3V to +6.5V                       |  |  |  |

| Voltage on VCAP pin with respect to Vss, PIC16F722A/723A                                                                                                                                                                          | 0.3V to +4.0V                       |  |  |  |

| Voltage on VDD with respect to Vss, PIC16LF722A/723A                                                                                                                                                                              | 0.3V to +4.0V                       |  |  |  |

| Voltage on MCLR with respect to Vss                                                                                                                                                                                               | 0.3V to +9.0V                       |  |  |  |

| Voltage on all other pins with respect to Vss                                                                                                                                                                                     | 0.3V to (VDD + 0.3V)                |  |  |  |

| Total power dissipation <sup>(1)</sup>                                                                                                                                                                                            | 800 mW                              |  |  |  |

| Maximum current out of Vss pin                                                                                                                                                                                                    | 95 mA                               |  |  |  |

| Maximum current into VDD pin                                                                                                                                                                                                      | 70 mA                               |  |  |  |

| Clamp current, IK (VPIN < 0 or VPIN > VDD)                                                                                                                                                                                        | ± 20 mA                             |  |  |  |

| Maximum output current sunk by any I/O pin                                                                                                                                                                                        | 25 mA                               |  |  |  |

| Maximum output current sourced by any I/O pin                                                                                                                                                                                     | 25 mA                               |  |  |  |

| Maximum current sunk by all ports (2), -40°C $\leq$ TA $\leq$ +85°C for industrial                                                                                                                                                | 200 mA                              |  |  |  |

| Maximum current sunk by all ports <sup>(2)</sup> , -40°C $\leq$ TA $\leq$ +125°C for extended                                                                                                                                     | 90 mA                               |  |  |  |

| Maximum current sourced by all ports <sup>(2)</sup> , $40^{\circ}C \le TA \le +85^{\circ}C$ for industrial                                                                                                                        | 140 mA                              |  |  |  |

| Maximum current sourced by all ports <sup>(2)</sup> , -40°C $\leq$ TA $\leq$ +125°C for extended                                                                                                                                  | 65 mA                               |  |  |  |

| <b>Note 1:</b> Power dissipation is calculated as follows: PDIS = VDD x {IDD $-\Sigma$ IOH} + $\Sigma$ {(VDD $-\Sigma$                                                                                                            | VOH) x IOH} + $\Sigma$ (VOI x IOL). |  |  |  |

| † NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those |                                     |  |  |  |

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure above maximum rating conditions for extended periods may affect device reliability.

# 23.5 Thermal Considerations

| Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |           |                                        |      |       |                                                          |  |  |

|--------------------------------------------------------------------------------------------------------------------------|-----------|----------------------------------------|------|-------|----------------------------------------------------------|--|--|

| Param<br>No.                                                                                                             | Sym.      | Characteristic                         | Тур. | Units | Conditions                                               |  |  |

| TH01                                                                                                                     | θJA       | Thermal Resistance Junction to Ambient | 60.0 | °C/W  | 28-pin SPDIP package                                     |  |  |

|                                                                                                                          |           |                                        | 69.7 | °C/W  | 28-pin SOIC package                                      |  |  |

|                                                                                                                          |           |                                        | 71.0 | °C/W  | 28-pin SSOP package                                      |  |  |

|                                                                                                                          |           |                                        | 52.5 | °C/W  | 28-pin UQFN 4x4mm package                                |  |  |

|                                                                                                                          |           |                                        | 30.0 | °C/W  | 28-pin QFN 6x6mm package                                 |  |  |

| TH02                                                                                                                     | θJC       | Thermal Resistance Junction to Case    | 29.0 | °C/W  | 28-pin SPDIP package                                     |  |  |

|                                                                                                                          |           |                                        | 18.9 | °C/W  | 28-pin SOIC package                                      |  |  |

|                                                                                                                          |           |                                        | 24.0 | °C/W  | 28-pin SSOP package                                      |  |  |

|                                                                                                                          |           |                                        | 16.7 | °C/W  | 28-pin UQFN 4x4mm package                                |  |  |

|                                                                                                                          |           |                                        | 5.0  | °C/W  | 28-pin QFN 6x6mm package                                 |  |  |

| TH03                                                                                                                     | Тјмах     | Maximum Junction Temperature           | 150  | °C    |                                                          |  |  |

| TH04                                                                                                                     | PD        | Power Dissipation                      | _    | W     | PD = PINTERNAL + PI/O                                    |  |  |

| TH05                                                                                                                     | PINTERNAL | Internal Power Dissipation             | —    | W     | PINTERNAL = IDD x VDD <sup>(1)</sup>                     |  |  |

| TH06                                                                                                                     | Pi/o      | I/O Power Dissipation                  | —    | W     | $PI/O = \Sigma (IOL * VOL) + \Sigma (IOH * (VDD - VOH))$ |  |  |

| TH07                                                                                                                     | Pder      | Derated Power                          | _    | W     | Pder = PDmax (Tj - Ta)/θja <sup>(2)</sup>                |  |  |

Note 1: IDD is current to run the chip alone without driving any load on the output pins.

2: TA = Ambient Temperature

**3:** T<sub>J</sub> = Junction Temperature

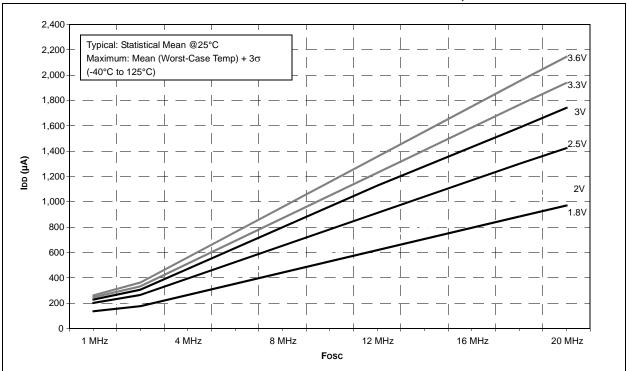

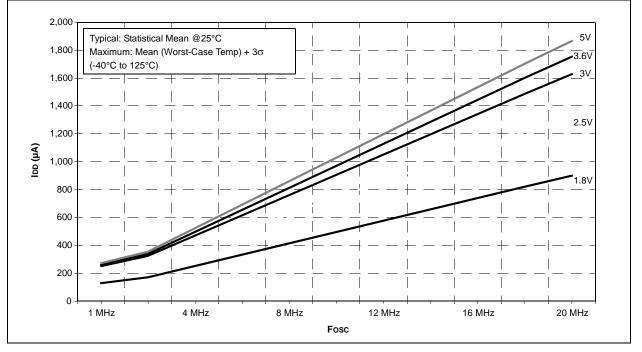

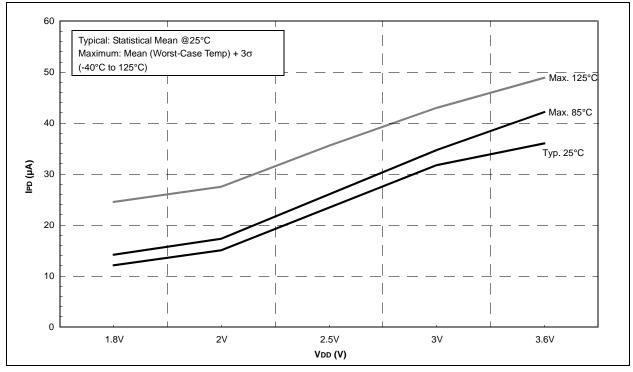

FIGURE 24-34: PIC16LF722A/723A BOR IPD vs. VDD

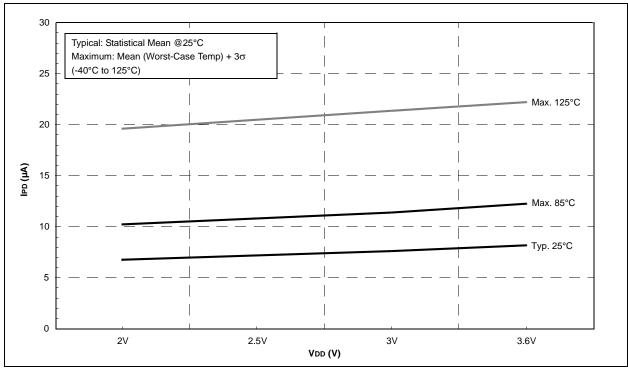

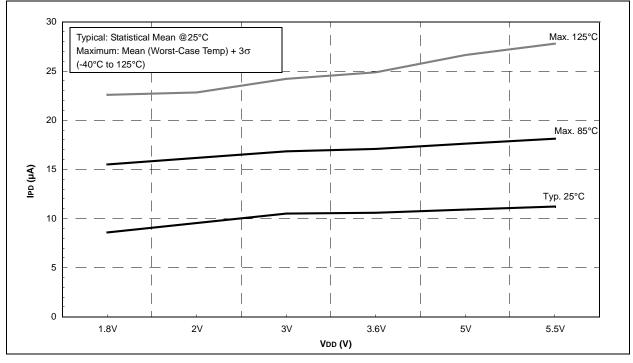

#### FIGURE 24-36: PIC16LF722A/723A CAP SENSE HIGH POWER IPD vs. VDD

# PIC16(L)F722A/723A