Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I²C, SPI, UART/USART                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 192 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 11x8b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f723at-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.2 Data Memory Organization

The data memory is partitioned into multiple banks which contain the General Purpose Registers (GPRs) and the Special Function Registers (SFRs). Bits RP0 and RP1 are bank select bits.

#### <u>RP1</u> <u>RP0</u>

| 0 | 0 | $\rightarrow$ | Bank 0 is selected |

|---|---|---------------|--------------------|

| 0 | 1 | $\rightarrow$ | Bank 1 is selected |

| 1 | 0 | $\rightarrow$ | Bank 2 is selected |

| 1 | 1 | $\rightarrow$ | Bank 3 is selected |

|   |   |               |                    |

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are reserved for the Special Function Registers. Above the Special Function Registers are the General Purpose Registers, implemented as static RAM. All implemented banks contain Special Function Registers. Some frequently used Special Function Registers from one bank are mirrored in another bank for code reduction and quicker access.

#### 2.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as 128 x 8 bits in the PIC16(L)F722A and 192 x 8 bits in the PIC16(L)F723A. Each register is accessed either directly or indirectly through the File Select Register (FSR), (Refer to Section 2.5 "Indirect Addressing, INDF and FSR Registers").

#### 2.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral functions for controlling the desired operation of the device (refer to Table 2-1). These registers are static RAM.

The Special Function Registers can be classified into two sets: core and peripheral. The Special Function Registers associated with the "core" are described in this section. Those related to the operation of the peripheral features are described in the section of that peripheral feature.

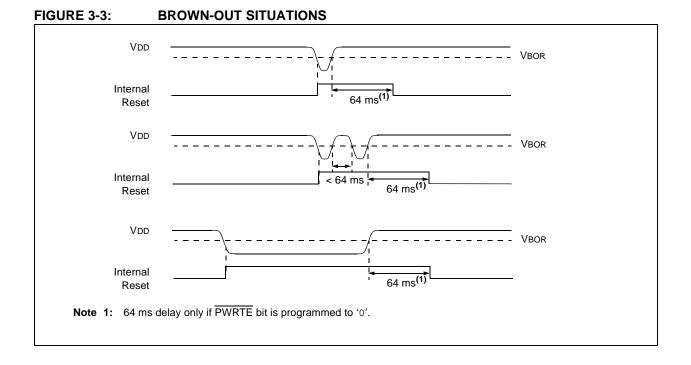

#### 3.5 Brown-Out Reset (BOR)

Brown-out Reset is enabled by programming the BOREN<1:0> bits in the Configuration register. The brown-out trip point is selectable from two trip points via the BORV bit in the Configuration register.

Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

Two bits are used to enable the BOR. When BOREN = 11, the BOR is always enabled. When BOREN = 10, the BOR is enabled, but disabled during Sleep. When BOREN = 0X, the BOR is disabled.

If VDD falls below VBOR for greater than parameter (TBOR) (see **Section 23.0** "**Electrical Specifica-tions**"), the brown-out situation will reset the device. This will occur regardless of VDD slew rate. A Reset is not ensured to occur if VDD falls below VBOR for more than parameter (TBOR).

If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be re-initialized. Once VDD rises above VBOR, the Power-up Timer will execute a 64 ms Reset.

Note: When erasing Flash program memory, the BOR is forced to enabled at the minimum BOR setting to ensure that any code protection circuitry is operating properly.

#### 4.1 Operation

Interrupts are disabled upon any device Reset. They are enabled by setting the following bits:

- GIE bit of the INTCON register

- Interrupt Enable bit(s) for the specific interrupt event(s)

- PEIE bit of the INTCON register (if the Interrupt Enable bit of the interrupt event is contained in the PIE1 and PIE2 registers)

The INTCON, PIR1 and PIR2 registers record individual interrupts via interrupt flag bits. Interrupt flag bits will be set, regardless of the status of the GIE, PEIE and individual interrupt enable bits.

The following events happen when an interrupt event occurs while the GIE bit is set:

- · Current prefetched instruction is flushed

- · GIE bit is cleared

- Current Program Counter (PC) is pushed onto the stack

- · PC is loaded with the interrupt vector 0004h

The ISR determines the source of the interrupt by polling the interrupt flag bits. The interrupt flag bits must be cleared before exiting the ISR to avoid repeated

interrupts. Because the GIE bit is cleared, any interrupt that occurs while executing the ISR will be recorded through its interrupt flag, but will not cause the processor to redirect to the interrupt vector.

The RETFIE instruction exits the ISR by popping the previous address from the stack and setting the GIE bit.

For additional information on a specific interrupt's operation, refer to its peripheral chapter.

- Note 1: Individual interrupt flag bits are set, regardless of the state of any other enable bits.

- 2: All interrupts will be ignored while the GIE bit is cleared. Any interrupt occurring while the GIE bit is clear will be serviced when the GIE bit is set again.

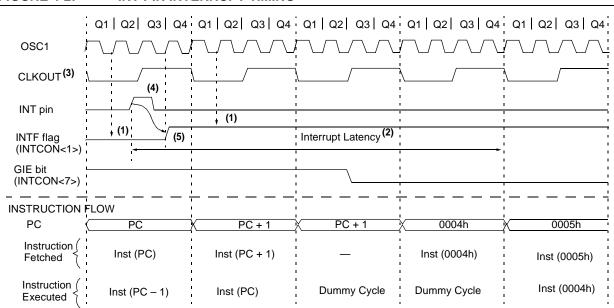

#### 4.2 Interrupt Latency

Interrupt latency is defined as the time from when the interrupt event occurs to the time code execution at the interrupt vector begins. The latency for synchronous interrupts is three instruction cycles. For asynchronous interrupts, the latency is three to four instruction cycles, depending on when the interrupt occurs. See Figure 4-2 for timing details.

Note 1: INTF flag is sampled here (every Q1).

- 2: Asynchronous interrupt latency = 3-4 TCY. Synchronous latency = 3 TCY, where TCY = instruction cycle time. Latency is the same whether Inst (PC) is a single cycle or a 2-cycle instruction.

- 3: CLKOUT is available only in INTOSC and RC Oscillator modes.

- 4: For minimum width of INT pulse, refer to AC specifications in Section 23.0 "Electrical Specifications".

- 5: INTF is enabled to be set any time during the Q4-Q1 cycles.

#### 5.0 LOW DROPOUT (LDO) VOLTAGE REGULATOR

The PIC16F722A/723A devices differ from the PIC16LF722A/723A devices due to an internal Low Dropout (LDO) voltage regulator. The PIC16F722A/723A devices contain an internal LDO, while the PIC16LF722A/723A ones do not.

The lithography of the die allows a maximum operating voltage of 3.6V on the internal digital logic. In order to continue to support 5.0V designs, a LDO voltage regulator is integrated on the die. The LDO voltage regulator allows for the internal digital logic to operate at 3.2V, while I/O's operate at 5.0V (VDD).

The LDO voltage regulator requires an external bypass capacitor for stability. One of three pins, denoted as VCAP, can be configured for the external bypass capacitor. It is recommended that the capacitor be a ceramic cap between 0.1 to  $1.0 \,\mu$ F. The VCAP pin is not intended to supply power to external loads. An external voltage regulator should be used if this functionality is required. In addition, external devices should not supply power to the VCAP pin.

On power-up, the external capacitor will look like a large load on the LDO voltage regulator. To prevent erroneous operation, the device is held in Reset while a constant current source charges the external capacitor. After the cap is fully charged, the device is released from Reset. For more information, refer to **Section 23.0 "Electrical Specifications"**.

See Configuration Word 2 register (Register 8-2) for VCAP enable bits.

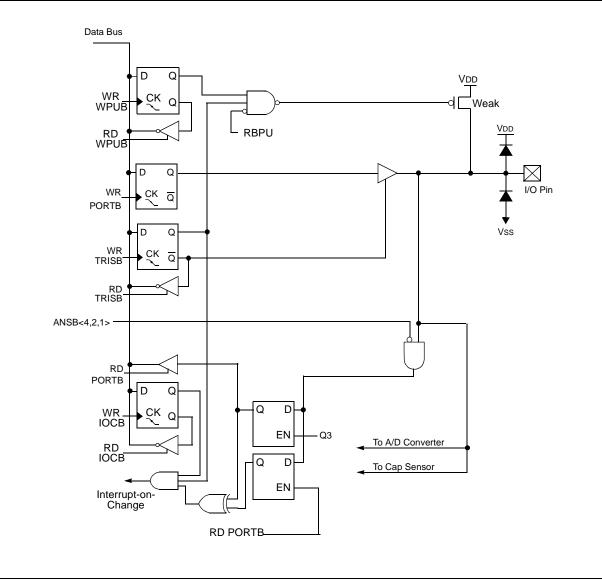

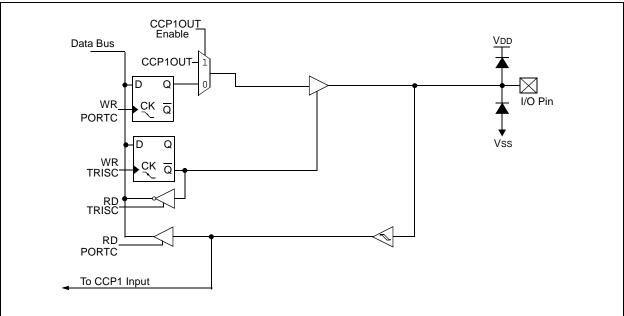

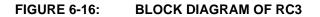

### 6.2.2 PIN DESCRIPTIONS AND DIAGRAMS

Each PORTA pin is multiplexed with other functions. The pins and their combined functions are briefly described here. For specific information about individual functions such as the A/D Converter (ADC), refer to the appropriate section in this data sheet.

#### 6.2.2.1 RA0/AN0/SS/VCAP

Figure 6-1 shows the diagram for this pin. This pin is configurable to function as one of the following:

- General purpose I/O

- Analog input for the ADC

- Slave select input for the SSP(1)

- Voltage regulator capacitor pin (PIC16F722A/ 723A only)

### Note 1: SS pin location may be selected as RA5 or RA0.

#### 6.2.2.2 RA1/AN1

Figure 6-2 shows the diagram for this pin. This pin is configurable to function as one of the following:

- General purpose I/O

- Analog input for the ADC

#### 6.2.2.3 RA2/AN2

Figure 6-2 shows the diagram for this pin. This pin is configurable to function as one of the following:

- General purpose I/O

- Analog input for the ADC

#### 6.2.2.4 RA3/AN3/VREF

Figure 6-2 shows the diagram for this pin. This pin is configurable to function as one of the following:

- General purpose I/O

- · Analog input for the ADC

- Voltage reference input for the ADC

#### 6.2.2.5 RA4/CPS6/T0CKI

Figure 6-3 shows the diagram for this pin. This pin is configurable to function as one of the following:

- General purpose I/O

- Capacitive sensing input

- Clock input for Timer0

The Timer0 clock input function works independently of any TRIS register setting. Effectively, if TRISA4 = 0, the PORTA4 register bit will output to the pad and clock Timer0 at the same time.

#### 6.2.2.6 RA5/AN4/CPS7/SS/VCAP

Figure 6-4 shows the diagram for this pin. This pin is configurable to function as one of the following:

- General purpose I/O

- Analog input for the ADC

- · Capacitive sensing input

- Slave select input for the SSP<sup>(1)</sup>

- Voltage regulator capacitor pin (PIC16F722A/ 723A only)

**Note 1:** SS pin location may be selected as RA5 or RA0.

#### 6.2.2.7 RA6/OSC2/CLKOUT/VCAP

Figure 6-5 shows the diagram for this pin. This pin is configurable to function as one of the following:

- General purpose I/O

- Crystal/resonator connection

- Clock output

- Voltage regulator capacitor pin (PIC16F722A/ 723A only)

#### 6.2.2.8 RA7/OSC1/CLKIN

Figure 6-6 shows the diagram for this pin. This pin is configurable to function as one of the following:

- General purpose I/O

- Crystal/resonator connection

- Clock input

# PIC16(L)F722A/723A

# PIC16(L)F722A/723A

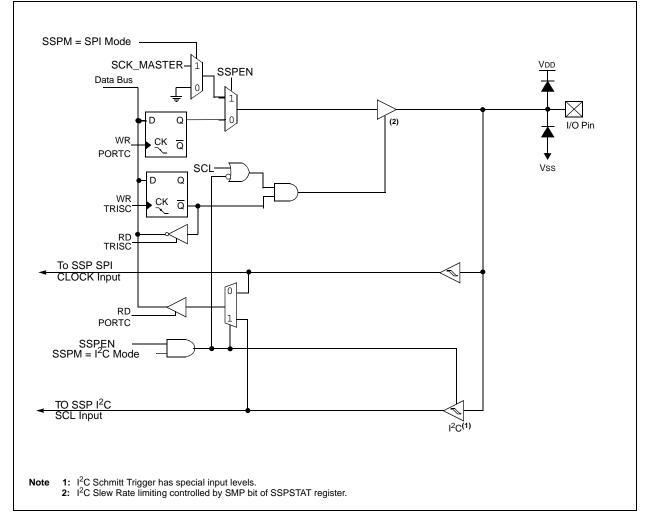

### 7.0 OSCILLATOR MODULE

#### 7.1 Overview

The oscillator module has a wide variety of clock sources and selection features that allow it to be used in a wide range of applications while maximizing performance and minimizing power consumption. Figure 7-1 illustrates a block diagram of the oscillator module.

Clock sources can be configured from external oscillators, quartz crystal resonators, ceramic resonators and Resistor-Capacitor (RC) circuits. In addition, the system can be configured to use an internal calibrated high-frequency oscillator as clock source, with a choice of selectable speeds via software.

Clock source modes are configured by the FOSC bits in Configuration Word 1 (CONFIG1). The oscillator module can be configured for one of eight modes of operation.

- 1. RC External Resistor-Capacitor (RC) with Fosc/4 output on OSC2/CLKOUT.

- 2. RCIO External Resistor-Capacitor (RC) with I/O on OSC2/CLKOUT.

- 3. INTOSC Internal oscillator with Fosc/4 output on OSC2 and I/O on OSC1/CLKIN.

- 4. INTOSCIO Internal oscillator with I/O on OSC1/CLKIN and OSC2/CLKOUT.

- 5. EC External clock with I/O on OSC2/CLKOUT.

- HS High Gain Crystal or Ceramic Resonator mode.

- 7. XT Medium Gain Crystal or Ceramic Resonator Oscillator mode.

- 8. LP Low-Power Crystal mode.

FIGURE 7-1: SIMPLIFIED PIC<sup>®</sup> MCU CLOCK SOURCE BLOCK DIAGRAM

#### 15.0 CAPTURE/COMPARE/PWM (CCP) MODULE

The Capture/Compare/PWM module is a peripheral which allows the user to time and control different events. In Capture mode, the peripheral allows the timing of the duration of an event. The Compare mode allows the user to trigger an external event when a predetermined amount of time has expired. The PWM mode can generate a Pulse-Width Modulated signal of varying frequency and duty cycle.

The timer resources used by the module are shown in Table 15-1.

Additional information on CCP modules is available in the Application Note *AN594, Using the CCP Modules* (DS00594).

#### TABLE 15-1: CCP MODE – TIMER RESOURCES REQUIRED

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

| CCP1 Mode | CCP2 Mode | Interaction                                                                                                  |

|-----------|-----------|--------------------------------------------------------------------------------------------------------------|

| Capture   | Capture   | Same TMR1 time base                                                                                          |

| Capture   | Compare   | Same TMR1 time base <sup>(1, 2)</sup>                                                                        |

| Compare   | Compare   | Same TMR1 time base <sup>(1, 2)</sup>                                                                        |

| PWM       | PWM       | The PWMs will have the same frequency and update rate (TMR2 interrupt).<br>The rising edges will be aligned. |

| PWM       | Capture   | None                                                                                                         |

| PWM       | Compare   | None                                                                                                         |

#### TABLE 15-2: INTERACTION OF TWO CCP MODULES

**Note 1:** If CCP2 is configured as a Special Event Trigger, CCP1 will clear Timer1, affecting the value captured on the CCP2 pin.

2: If CCP1 is in Capture mode and CCP2 is configured as a Special Event Trigger, CCP2 will clear Timer1, affecting the value captured on the CCP1 pin.

| Note: | CCPRx   | and      | CCPx     | throughout  | this |

|-------|---------|----------|----------|-------------|------|

|       | documer | nt refer | to CCP   | R1 or CCPR2 | and  |

|       | CCP1 or | CCP2     | , respec | tively.     |      |

| R/W-0        | R/W-0                                  | R/W-0                                | R/W-0         | U-0              | R/W-0           | R-1             | R/W-0 |

|--------------|----------------------------------------|--------------------------------------|---------------|------------------|-----------------|-----------------|-------|

| CSRC         | TX9                                    | TXEN <sup>(1)</sup>                  | SYNC          | —                | BRGH            | TRMT            | TX9D  |

| bit 7        |                                        |                                      |               |                  |                 |                 | bit   |

| Legend:      |                                        |                                      |               |                  |                 |                 |       |

| R = Readable | e bit                                  | W = Writable                         | bit           | U = Unimple      | mented bit, rea | d as '0'        |       |

| n = Value at | POR                                    | '1' = Bit is set                     |               | '0' = Bit is cle |                 | x = Bit is unkr | nown  |

| bit 7        | <b>CSRC:</b> Cloc<br><u>Asynchronc</u> | ck Source Select                     | bit           |                  |                 |                 |       |

|              | Don't care                             | <u></u> .                            |               |                  |                 |                 |       |

|              | <u>Synchronou</u>                      |                                      |               |                  |                 |                 |       |

|              |                                        | r mode (clock ge                     |               |                  | i)              |                 |       |

| oit 6        |                                        | mode (clock from<br>ransmit Enable t |               | irce)            |                 |                 |       |

|              |                                        | s 9-bit transmiss                    |               |                  |                 |                 |       |

|              |                                        | s 8-bit transmiss                    |               |                  |                 |                 |       |

| bit 5        | TXEN: Tran                             | ismit Enable bit <sup>(1</sup>       | )             |                  |                 |                 |       |

|              | 1 = Transm                             |                                      |               |                  |                 |                 |       |

|              | 0 = Transm                             |                                      |               |                  |                 |                 |       |

| oit 4        |                                        | SART Mode Sele                       | ct bit        |                  |                 |                 |       |

|              |                                        | onous mode<br>Ironous mode           |               |                  |                 |                 |       |

| bit 3        | •                                      | ented: Read as '                     | 0'            |                  |                 |                 |       |

| bit 2        | -                                      | h Baud Rate Sel                      |               |                  |                 |                 |       |

|              | Asynchrono                             |                                      |               |                  |                 |                 |       |

|              | 1 = High sp                            |                                      |               |                  |                 |                 |       |

|              | 0 = Low sp                             |                                      |               |                  |                 |                 |       |

|              | <u>Synchronou</u><br>Unused in t       |                                      |               |                  |                 |                 |       |

| oit 1        |                                        | ismit Shift Regist                   | er Status bit |                  |                 |                 |       |

|              | 1 = TSR er                             |                                      |               |                  |                 |                 |       |

|              | 0 = TSR fu                             |                                      |               |                  |                 |                 |       |

| bit 0        | TX9D: Ninth                            | n bit of Transmit                    | Data          |                  |                 |                 |       |

|              | Can be add                             |                                      |               |                  |                 |                 |       |

#### REGISTER 16-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER

| R/W-0         | R/W-0                                                                                       | R-0                                                        | R-0                                 | R-0              | R-0             | R-0             | R-0  |

|---------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------|-------------------------------------|------------------|-----------------|-----------------|------|

| SMP           | CKE                                                                                         | D/A                                                        | Р                                   | S                | R/W             | UA              | BF   |

| oit 7         |                                                                                             |                                                            |                                     |                  |                 |                 | bit  |

|               |                                                                                             |                                                            |                                     |                  |                 |                 |      |

| Legend:       |                                                                                             |                                                            |                                     |                  |                 |                 |      |

| R = Readable  | e bit                                                                                       | W = Writable                                               | bit                                 | U = Unimpler     | mented bit, rea | nd as '0'       |      |

| -n = Value at | POR                                                                                         | '1' = Bit is set                                           |                                     | '0' = Bit is cle | ared            | x = Bit is unkr | nown |

| bit 7         |                                                                                             | ata Input Sample                                           | e Phase bit                         |                  |                 |                 |      |

|               | 0 = Input dat<br><u>SPI Slave m</u>                                                         | a sampled at er<br>a sampled at m                          | iddle of data o                     | output time      |                 |                 |      |

| bit 6         | CKE: SPI CI                                                                                 | ock Edge Selec                                             | t bit                               |                  |                 |                 |      |

|               | <u>SPI mode, C</u><br>1 = Data stat<br>0 = Data stat<br><u>SPI mode, C</u><br>1 = Data stat | <u>KP = 0:</u><br>ble on rising edg<br>ble on falling ed   | ge of SCK<br>ge of SCK<br>ge of SCK |                  |                 |                 |      |

| bit 5         | <b>D/A:</b> Data/Ad<br>Used in I <sup>2</sup> C r                                           | ddress bit                                                 | ,                                   |                  |                 |                 |      |

| bit 4         | <b>P:</b> Stop bit<br>Used in I <sup>2</sup> C r                                            | node only.                                                 |                                     |                  |                 |                 |      |

| bit 3         | <b>S:</b> Start bit<br>Used in I <sup>2</sup> C r                                           | <b>S:</b> Start bit<br>Used in I <sup>2</sup> C mode only. |                                     |                  |                 |                 |      |

| bit 2         | <b>R/W</b> : Read/V<br>Used in I <sup>2</sup> C r                                           | Vrite Information node only.                               | n bit                               |                  |                 |                 |      |

| bit 1         | <b>UA:</b> Update<br>Used in I <sup>2</sup> C r                                             |                                                            |                                     |                  |                 |                 |      |

| bit 0         |                                                                                             | ull Status bit<br>complete, SSPI<br>not complete, S        |                                     | npty             |                 |                 |      |

#### © 2010-2016 Microchip Technology Inc.

| R/W-0         | R/W-0                                               | R-0                                                                                    | R-0            | R-0              | R-0             | R-0                           | R-0            |

|---------------|-----------------------------------------------------|----------------------------------------------------------------------------------------|----------------|------------------|-----------------|-------------------------------|----------------|

| SMP           | CKE                                                 | D/A                                                                                    | Р              | S                | R/W             | UA                            | BF             |

| bit 7         |                                                     |                                                                                        |                |                  |                 |                               | bit (          |

| Legend:       |                                                     |                                                                                        |                |                  |                 |                               |                |

| R = Readable  | e bit                                               | W = Writable                                                                           | bit            | U = Unimple      | mented bit, rea | ad as '0'                     |                |

| -n = Value at | POR                                                 | '1' = Bit is set                                                                       |                | ʻ0' = Bit is cle | eared           | x = Bit is unkr               | nown           |

| bit 7         | 1 = Slew Rate                                       | ta Input Sample<br>e Control (limiti<br>e Control (limiti                              | ng) disabled.  |                  |                 | ode (100 kHz an<br>400 kHz).  | id 1 MHz).     |

| bit 6         |                                                     | ock Edge Selec<br>be maintained                                                        |                | n SPI mode on    | ly.             |                               |                |

| bit 5         | 1 = Indicates                                       | DDRESS bit (I <sup>2</sup><br>that the last by<br>that the last by                     | te received o  | r transmitted w  |                 |                               |                |

| bit 4         | 1 = Indicates                                       | ared when the<br>that a Stop bit<br>as not detecte                                     | has been det   |                  |                 | : bit is detected la<br>eset) | ast.           |

| bit 3         | 1 = Indicates                                       | ared when the<br>that a Start bit<br>/as not detecte                                   | has been det   |                  |                 | bit is detected la<br>eset)   | ast.           |

| bit 2         | This bit holds                                      | VRITE bit Infor<br>the R/W bit inf<br>h to the next S                                  | ormation follo |                  | address match.  | . This bit is only v          | valid from the |

| bit 1         | 1 = Indicates                                       | Address bit (10-<br>that the user n<br>does not need t                                 | eeds to upda   | te the address   | in the SSPAD    | D register                    |                |

| bit 0         | 0 = Receive r<br><u>Transmit:</u><br>1 = Transmit i | Il Status bit<br>complete, SSPI<br>not complete, S<br>in progress, SS<br>complete, SSP | SPBUF is en    |                  |                 |                               |                |

#### REGISTER 17-4: SSPSTAT: SYNCHRONOUS SERIAL PORT STATUS REGISTER (I<sup>2</sup>C MODE)

| REGISTER 17-5: | SSPMSK: SSP MASK REGISTER |

|----------------|---------------------------|

|                |                           |

| R/W-1 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| MSK7  | MSK6  | MSK5  | MSK4  | MSK3  | MSK2  | MSK1  | MSK0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-1 | MSK<7:1>: Mask bits  |

|---------|----------------------|

|         | 1 - The received add |

| 1 = The received address bit n is compared to SSPADD <n> to detect I</n>            |   |

|-------------------------------------------------------------------------------------|---|

| 0 = The received address bit n is not used to detect I <sup>2</sup> C address match | ۱ |

#### bit 0 MSK<0>: Mask bit for I<sup>2</sup>C Slave Mode, 10-bit Address

I<sup>2</sup>C Slave Mode, 10-bit Address (SSPM<3:0> = 0111):

1 = The received address bit '0' is compared to SSPADD<0> to detect  $I^2C$  address match

0 = The received address bit '0' is not used to detect I<sup>2</sup>C address match

All other SSP modes: this bit has no effect.

#### REGISTER 17-6: SSPADD: SSP I<sup>2</sup>C ADDRESS REGISTER

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| ADD7  | ADD6  | ADD5  | ADD4  | ADD3  | ADD2  | ADD1  | ADD0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

|       |       |       |       |       |       |       |       |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 7-0 ADD<7:0>: Address bits Received address

#### TABLE 17-7: SUMMARY OF REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

| Name                                                                                        | Bit 7                                                           | Bit 6              | Bit 5                    | Bit 4        | Bit 3    | Bit 2  | Bit 1  | Bit 0  | Register on<br>Page |

|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--------------------|--------------------------|--------------|----------|--------|--------|--------|---------------------|

| INTCON                                                                                      | GIE                                                             | PEIE               | TOIE                     | INTE         | RBIE     | TOIF   | INTF   | RBIF   | 36                  |

| PIR1                                                                                        | TMR1GIF                                                         | ADIF               | RCIF                     | TXIF         | SSPIF    | CCP1IF | TMR2IF | TMR1IF | 39                  |

| PIE1                                                                                        | TMR1GIE                                                         | ADIE               | RCIE                     | TXIE         | SSPIE    | CCP1IE | TMR2IE | TMR1IE | 37                  |

| SSPBUF                                                                                      | SSPBUF Synchronous Serial Port Receive Buffer/Transmit Register |                    |                          |              |          |        |        |        | 147                 |

| SSPADD                                                                                      | Synchronous                                                     | Serial Por         | t (I <sup>2</sup> C mode | e) Address F | Register |        |        |        | 155                 |

| SSPCON                                                                                      | WCOL                                                            | SSPOV              | SSPEN                    | CKP          | SSPM3    | SSPM2  | SSPM1  | SSPM0  | 164                 |

| SSPMSK <sup>(2)</sup> Synchronous Serial Port (I <sup>2</sup> C mode) Address Mask Register |                                                                 |                    |                          |              |          |        |        | 166    |                     |

| SSPSTAT                                                                                     | SMP <sup>(1)</sup>                                              | CKE <sup>(1)</sup> | D/Ā                      | Р            | S        | R/W    | UA     | BF     | 165                 |

| TRISC                                                                                       | TRISC7                                                          | TRISC6             | TRISC5                   | TRISC4       | TRISC3   | TRISC2 | TRISC1 | TRISC0 | 62                  |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by SSP module in I<sup>2</sup>C mode.

**Note 1:** Maintain these bits clear in  $I^2C$  mode.

**2:** Accessible only when SSPM < 3:0 > = 1001.

# PIC16(L)F722A/723A

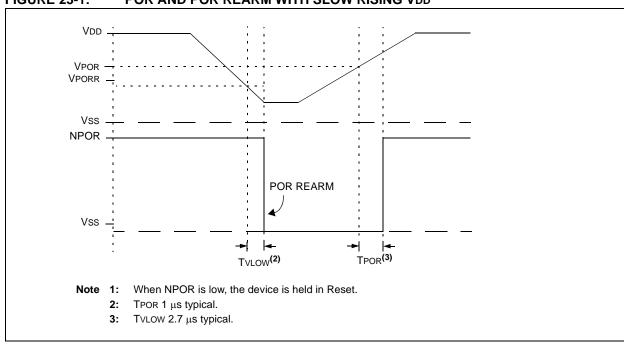

#### FIGURE 23-1: POR AND POR REARM WITH SLOW RISING VDD

#### 23.2 DC Characteristics: PIC16(L)F722A/723A-I/E (Industrial, Extended) (Continued)

| PIC16LF7 | 722A/723A                           | Operating | g tempera | ature -                                              | 40°C ≤ T.<br>40°C ≤ T. | less otherwise stated)<br>A ≤ +85°C for industrial<br>A ≤ +125°C for extended |                             |  |  |

|----------|-------------------------------------|-----------|-----------|------------------------------------------------------|------------------------|-------------------------------------------------------------------------------|-----------------------------|--|--|

| PIC16F72 | 22A/723A                            | 1         |           | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                        |                                                                               |                             |  |  |

| Param    | Device                              | Min.      | Тур†      | Max.                                                 | Units                  |                                                                               | Conditions                  |  |  |

| No.      | Characteristics                     |           |           |                                                      |                        | VDD                                                                           | Note                        |  |  |

|          | Supply Current (IDD) <sup>(1,</sup> | , 2)      |           |                                                      |                        |                                                                               |                             |  |  |

| D014     |                                     | _         | 290       | 330                                                  | μA                     | 1.8                                                                           | Fosc = 4 MHz                |  |  |

|          | _                                   | 460       | 500       | μA                                                   | 3.0                    | EC Oscillator mode                                                            |                             |  |  |

| D014     |                                     |           | 300       | 430                                                  | μA                     | 1.8                                                                           | Fosc = 4 MHz                |  |  |

|          |                                     |           | 450       | 655                                                  | μA                     | 3.0                                                                           | EC Oscillator mode (Note 5) |  |  |

|          |                                     | —         | 500       | 730                                                  | μA                     | 5.0                                                                           |                             |  |  |

| D015     |                                     | —         | 100       | 130                                                  | μA                     | 1.8                                                                           | Fosc = 500 kHz              |  |  |

|          |                                     |           | 120       | 150                                                  | μA                     | 3.0                                                                           | MFINTOSC mode               |  |  |

| D015     |                                     | _         | 115       | 195                                                  | μA                     | 1.8                                                                           | Fosc = 500 kHz              |  |  |

|          |                                     | _         | 135       | 200                                                  | μA                     | 3.0                                                                           | MFINTOSC mode (Note 5)      |  |  |

|          |                                     | _         | 150       | 220                                                  | μA                     | 5.0                                                                           |                             |  |  |

| D016     |                                     |           | 650       | 800                                                  | μA                     | 1.8                                                                           | Fosc = 8 MHz                |  |  |

|          |                                     | —         | 1000      | 1200                                                 | μA                     | 3.0                                                                           | HFINTOSC mode               |  |  |

| D016     |                                     | —         | 625       | 850                                                  | μA                     | 1.8                                                                           | Fosc = 8 MHz                |  |  |

|          |                                     | —         | 1000      | 1200                                                 | μA                     | 3.0                                                                           | HFINTOSC mode (Note 5)      |  |  |

|          |                                     | —         | 1100      | 1500                                                 | μA                     | 5.0                                                                           |                             |  |  |

| D017     |                                     | _         | 1.0       | 1.2                                                  | mA                     | 1.8                                                                           | Fosc = 16 MHz               |  |  |

|          |                                     | —         | 1.5       | 1.85                                                 | mA                     | 3.0                                                                           | HFINTOSC mode               |  |  |

| D017     |                                     | _         | 1         | 1.2                                                  | mA                     | 1.8                                                                           | Fosc = 16 MHz               |  |  |

|          |                                     | _         | 1.5       | 1.7                                                  | mA                     | 3.0                                                                           | HFINTOSC mode (Note 5)      |  |  |

|          |                                     |           | 1.7       | 2.1                                                  | mA                     | 5.0                                                                           |                             |  |  |

| D018     |                                     | _         | 210       | 240                                                  | μA                     | 1.8                                                                           | Fosc = 4 MHz                |  |  |

|          |                                     | _         | 340       | 380                                                  | μA                     | 3.0                                                                           | EXTRC mode (Note 3, Note 5) |  |  |

| D018     |                                     |           | 225       | 320                                                  | μA                     | 1.8                                                                           | Fosc = 4 MHz                |  |  |

|          |                                     |           | 360       | 445                                                  | μA                     | 3.0                                                                           | EXTRC mode (Note 3, Note 5) |  |  |

|          |                                     |           | 410       | 650                                                  | μA                     | 5.0                                                                           |                             |  |  |

| D019     |                                     | —         | 1.6       | 1.9                                                  | mA                     | 3.0                                                                           | Fosc = 20 MHz               |  |  |

|          |                                     | _         | 2.0       | 2.8                                                  | mA                     | 3.6                                                                           | HS Oscillator mode          |  |  |

| D019     |                                     | _         | 1.6       | 2                                                    | mA                     | 3.0                                                                           | Fosc = 20 MHz               |  |  |

|          |                                     | _         | 1.9       | 3.2                                                  | mA                     | 5.0                                                                           | HS Oscillator mode (Note 5) |  |  |

**Note 1:** The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

**3:** For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in kΩ.

4: FVR and BOR are disabled.

5: 0.1 μF capacitor on VCAP (RA0).

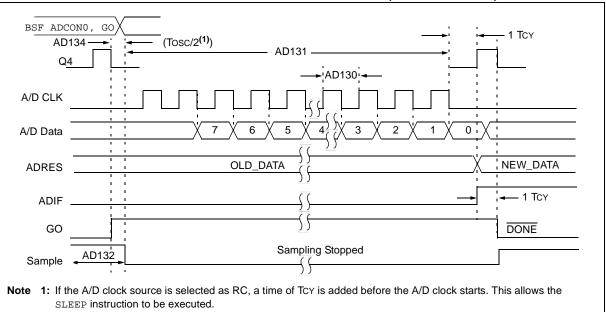

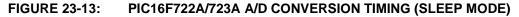

**Note** 1: If the A/D clock source is selected as RC, a time of TCY is added before the A/D clock starts. This allows the SLEEP instruction to be executed.

| Param<br>No. | Symbol                               | Characteristic                                               | Min.         | Тур†     | Max. | Units | Conditions |  |

|--------------|--------------------------------------|--------------------------------------------------------------|--------------|----------|------|-------|------------|--|

| SP70*        | TssL2scH,<br>TssL2scL                | $\overline{SS}$ ↓ to SCK↓ or SCK↑ input                      | Тсү          |          | -    | ns    |            |  |

| SP71*        | TscH                                 | SCK input high time (Slave mode                              | e)           | Tcy + 20 |      |       | ns         |  |

| SP72*        | TscL                                 | SCK input low time (Slave mode                               | )            | Tcy + 20 |      |       | ns         |  |

| SP73*        | TDIV2scH,<br>TDIV2scL                | Setup time of SDI data input to S                            | SCK edge     | 100      |      | —     | ns         |  |

| SP74*        | TscH2diL,<br>TscL2diL                | Hold time of SDI data input to SO                            | 100          |          | —    | ns    |            |  |

| SP75*        | SP75* TDOR SDO data output rise time |                                                              | 3.0-5.5V     |          | 10   | 25    | ns         |  |

|              |                                      |                                                              | 1.8-5.5V     | _        | 25   | 50    | ns         |  |

| SP76*        | TDOF                                 | SDO data output fall time                                    | —            | 10       | 25   | ns    |            |  |

| SP77*        | TssH2doZ                             | SS↑ to SDO output high-impeda                                | nce          | 10       | _    | 50    | ns         |  |

| SP78*        | TscR                                 | SCK output rise time                                         | 3.0-5.5V     |          | 10   | 25    | ns         |  |

|              |                                      | (Master mode)                                                | 1.8-5.5V     |          | 25   | 50    | ns         |  |

| SP79*        | TscF                                 | SCK output fall time (Master mo                              | de)          |          | 10   | 25    | ns         |  |

| SP80*        | TscH2doV,                            | SDO data output valid after                                  | 3.0-5.5V     | —        |      | 50    | ns         |  |

|              | TscL2doV                             | SCK edge                                                     | 1.8-5.5V     | —        | _    | 145   | ns         |  |

| SP81*        | TDOV2SCH,<br>TDOV2SCL                | SDO data output setup to SCK e                               | Тсу          | _        | —    | ns    |            |  |

| SP82*        | TssL2doV                             | SDO data output valid after $\overline{\text{SS}}\downarrow$ | —            | _        | 50   | ns    |            |  |

| SP83*        | TscH2ssH,<br>TscL2ssH                | SS ↑ after SCK edge                                          | 1.5 TCY + 40 |          | -    | ns    |            |  |

#### TABLE 23-11: SPI MODE REQUIREMENTS

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance † only and are not tested.

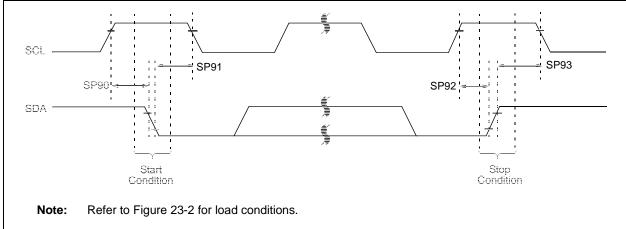

#### I<sup>2</sup>C BUS START/STOP BITS TIMING **FIGURE 23-20:**

# PIC16(L)F722A/723A

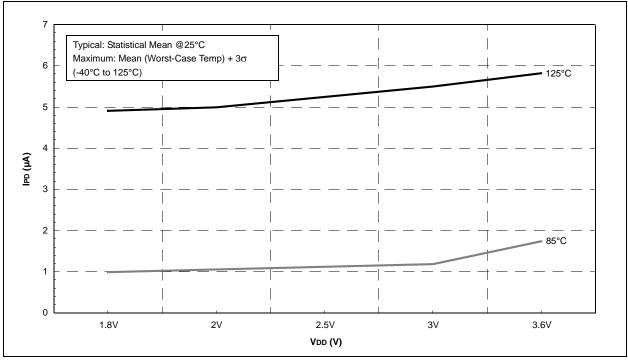

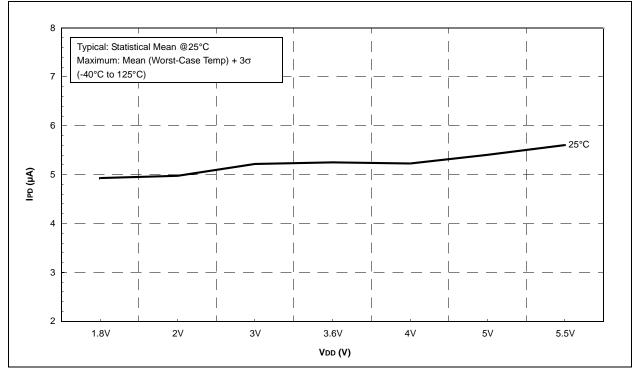

#### FIGURE 24-28: PIC16LF722A/723A MAXIMUM BASE IPD vs. VDD

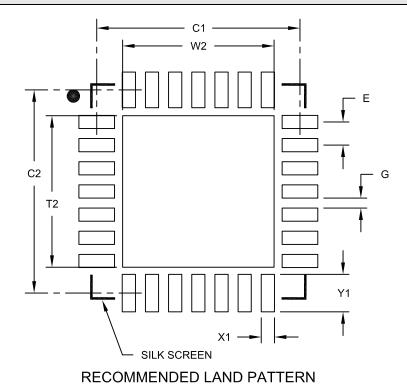

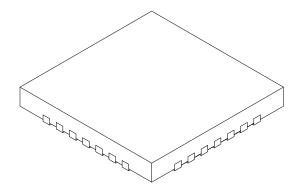

### 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS      |      |      |      |

|----------------------------|------------------|------|------|------|

| Dimensior                  | Dimension Limits |      |      |      |

| Contact Pitch              | E                |      |      |      |

| Optional Center Pad Width  | W2               |      |      | 4.25 |

| Optional Center Pad Length | T2               |      |      | 4.25 |

| Contact Pad Spacing        | C1               |      | 5.70 |      |

| Contact Pad Spacing        | C2               |      | 5.70 |      |

| Contact Pad Width (X28)    | X1               |      |      | 0.37 |

| Contact Pad Length (X28)   | Y1               |      |      | 1.00 |

| Distance Between Pads      | G                | 0.20 |      |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2105A

#### 28-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) – 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units            |                |          | S    |

|------------------------|------------------|----------------|----------|------|

| Dimens                 | Dimension Limits |                |          | MAX  |

| Number of Pins         | N                |                | 28       |      |

| Pitch                  | е                |                | 0.40 BSC |      |

| Overall Height         | A                | 0.45           | 0.50     | 0.55 |

| Standoff               | A1               | 0.00           | 0.02     | 0.05 |

| Contact Thickness      | A3               | 0.127 REF      |          |      |

| Overall Width          | E                | 4.00 BSC       |          |      |

| Exposed Pad Width      | E2               | 2.55 2.65 2.75 |          |      |

| Overall Length         | D                | 4.00 BSC       |          |      |

| Exposed Pad Length     | D2               | 2.55           | 2.65     | 2.75 |

| Contact Width          | b                | 0.15 0.20 0.25 |          |      |

| Contact Length         | L                | 0.30           | 0.40     | 0.50 |

| Contact-to-Exposed Pad | K                | 0.20           | -        | -    |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2 Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-152A Sheet 2 of 2