Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I²C, SPI, UART/USART                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 192 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                                |

| Data Converters            | A/D 11x8b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-UQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f723at-i-mv |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| 1.0   | Device Overview                                                              | 7    |

|-------|------------------------------------------------------------------------------|------|

| 2.0   | Memory Organization                                                          | . 11 |

| 3.0   | Resets                                                                       | . 23 |

| 4.0   | Interrupts                                                                   | . 33 |

| 5.0   | Low Dropout (LDO) Voltage Regulator                                          | . 41 |

| 6.0   | I/O Ports                                                                    | . 42 |

| 7.0   | Oscillator Module                                                            | . 71 |

| 8.0   | Device Configuration                                                         | 77   |

| 9.0   | Analog-to-Digital Converter (ADC) Module                                     | . 80 |

| 10.0  | Fixed Voltage Reference                                                      | . 90 |

| 11.0  | Timer0 Module                                                                | . 91 |

| 12.0  | Timer1 Module with Gate Control                                              | 103  |

| 13.0  | Timer2 Module                                                                | 115  |

| 14.0  | Capacitive Sensing Module                                                    | 108  |

| 15.0  | Capture/Compare/PWM (CCP) Module                                             | 114  |

| 16.0  | Addressable Universal Synchronous Asynchronous Receiver Transmitter (AUSART) | 124  |

| 17.0  |                                                                              |      |

| 18.0  | Program Memory Read                                                          | 167  |

| 19.0  | Power-Down Mode (Sleep)                                                      | 170  |

| 20.0  | In-Circuit Serial Programming™ (ICSP™)                                       | 172  |

| 21.0  | Instruction Set Summary                                                      | 173  |

| 22.0  | Development Support                                                          | 182  |

| 23.0  | Electrical Specifications                                                    | 186  |

| 24.0  |                                                                              |      |

| 25.0  | Packaging Information                                                        | 249  |

| Appe  | ndix A: Data Sheet Revision History                                          | 261  |

| Appe  | ndix B: Migrating From Other PIC <sup>®</sup> Devices                        | 261  |

| The I | Nicrochip Website                                                            | 262  |

| Cust  | omer Change Notification Service                                             | 262  |

| Cust  | omer Support                                                                 | 262  |

| Prod  | uct Identification System                                                    | 263  |

#### 2.2.2.2 **OPTION** register

The OPTION register, shown in Register 2-2, is a readable and writable register, which contains various control bits to configure:

- Timer0/WDT prescaler

- External RB0/INT interrupt

- Timer0

- Weak pull ups on PORTB

Note: To achieve a 1:1 prescaler assignment for Timer0, assign the prescaler to the WDT by setting PSA bit of the OPTION register to '1'. Refer to Section 12.3 "Timer1 Prescaler".

bit 0

| <b>REGISTER 2-</b> | 2: OPTIO | N_REG: OP | FION REGIS | TER   |       |       |       |

|--------------------|----------|-----------|------------|-------|-------|-------|-------|

| R/W-1              | R/W-1    | R/W-1     | R/W-1      | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

| RBPU               | INTEDG   | TOCS      | TOSE       | PSA   | PS2   | PS1   | PS0   |

| bit 7              |          |           |            |       |       |       | bit   |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7   | RBPU: PORTB Pull-up Enable bit                                                                                     |  |  |  |  |  |

|---------|--------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|         | 1 = PORTB pull ups are disabled                                                                                    |  |  |  |  |  |

|         | 0 = PORTB pull ups are enabled by individual bits in the WPUB register                                             |  |  |  |  |  |

| bit 6   | INTEDG: Interrupt Edge Select bit                                                                                  |  |  |  |  |  |

|         | <ul><li>1 = Interrupt on rising edge of RB0/INT pin</li><li>0 = Interrupt on falling edge of RB0/INT pin</li></ul> |  |  |  |  |  |

| bit 5   | TOCS: Timer0 Clock Source Select bit                                                                               |  |  |  |  |  |

|         | <ul><li>1 = Transition on RA4/T0CKI pin</li><li>0 = Internal instruction cycle clock (Fosc/4)</li></ul>            |  |  |  |  |  |

| bit 4   | T0SE: Timer0 Source Edge Select bit                                                                                |  |  |  |  |  |

|         | 1 = Increment on high-to-low transition on RA4/T0CKI pin                                                           |  |  |  |  |  |

|         | 0 = Increment on low-to-high transition on RA4/T0CKI pin                                                           |  |  |  |  |  |

| bit 3   | PSA: Prescaler Assignment bit                                                                                      |  |  |  |  |  |

|         | 1 = Prescaler is assigned to the WDT                                                                               |  |  |  |  |  |

|         | 0 = Prescaler is assigned to the Timer0 module                                                                     |  |  |  |  |  |

| bit 2-0 | PS<2:0>: Prescaler Rate Select bits                                                                                |  |  |  |  |  |

|         | Bit Value Timer0 Rate WDT Rate                                                                                     |  |  |  |  |  |

|         | 000 1:2 1:1                                                                                                        |  |  |  |  |  |

|         |                                                                                                                    |  |  |  |  |  |

|         | 010 1:8 1:4<br>011 1:16 1:8                                                                                        |  |  |  |  |  |

|         |                                                                                                                    |  |  |  |  |  |

|         | 101 1:64 1:32                                                                                                      |  |  |  |  |  |

|         | 110 1:128 1:64                                                                                                     |  |  |  |  |  |

|         | 111 <b>1:256 1:128</b>                                                                                             |  |  |  |  |  |

### 2.2.2.3 PCON Register

The Power Control (PCON) register contains flag bits (refer to Table 3-2) to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Watchdog Timer Reset (WDT)

- External MCLR Reset

The PCON register also controls the software enable of the BOR.

The PCON register bits are shown in Register 2-3.

### REGISTER 2-3: PCON: POWER CONTROL REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-q | R/W-q |

|-------|-----|-----|-----|-----|-----|-------|-------|

| —     | _   | _   | _   | —   | —   | POR   | BOR   |

| bit 7 |     |     |     |     |     |       | bit 0 |

| Legend:                |                  |                       |                    |

|------------------------|------------------|-----------------------|--------------------|

| R = Readable bit       | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR      | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| q = Value depends on c | ondition         |                       |                    |

| bit 7-2 | Unimplemented: Read as '0'                                                                                                                                                                                      |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 1   | POR: Power-on Reset Status bit                                                                                                                                                                                  |

|         | <ul> <li>1 = No Power-on Reset occurred</li> <li>0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)</li> </ul>                                                               |

| bit 0   | <ul> <li>BOR: Brown-out Reset Status bit</li> <li>1 = No Brown-out Reset occurred</li> <li>0 = A Brown-out Reset occurred (must be set in software after a Power-on Reset or Brown-out Reset occurs)</li> </ul> |

**Note 1:** Set BOREN<1:0> = 01 in the Configuration Word register for this bit to control the  $\overline{\text{BOR}}$ .

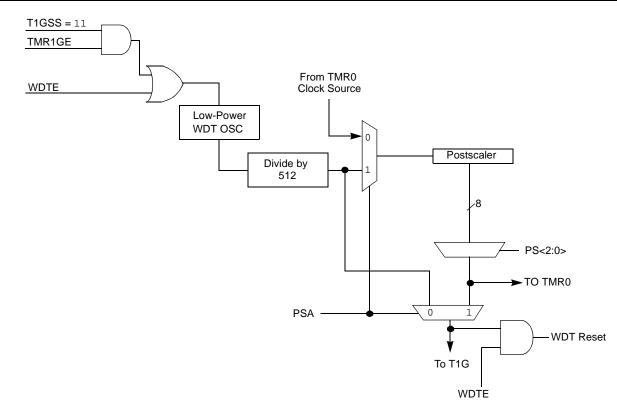

#### 3.4.2 WDT CONTROL

The WDTE bit is located in the Configuration Word Register 1. When set, the WDT runs continuously.

The PSA and PS<2:0> bits of the OPTION register control the WDT period. See **Section 11.0 "Timer0 Module"** for more information.

#### TABLE 3-1: WDT STATUS

| Conditions                                               | WDT                          |

|----------------------------------------------------------|------------------------------|

| WDTE = 0                                                 | Cleared                      |

| CLRWDT Command                                           |                              |

| Exit Sleep + System Clock = T1OSC, EXTRC, INTOSC, EXTCLK |                              |

| Exit Sleep + System Clock = XT, HS, LP                   | Cleared until the end of OST |

| Register   | Address               | Power-on Reset/<br>Brown-out Reset <sup>(1)</sup> | MCLR Reset/<br>WDT Reset | Wake-up from Sleep through<br>Interrupt/Time out |

|------------|-----------------------|---------------------------------------------------|--------------------------|--------------------------------------------------|

| W          | _                     | xxxx xxxx                                         | uuuu uuuu                | սսսս սսսս                                        |

| INDF       | 00h/80h/<br>100h/180h | XXXX XXXX                                         | xxxx xxxx                | นนนน นนนน                                        |

| TMR0       | 01h/101h              | xxxx xxxx                                         | uuuu uuuu                | սսսս սսսս                                        |

| PCL        | 02h/82h/<br>102h/182h | 0000 0000                                         | 0000 0000                | PC + 1 <sup>(3)</sup>                            |

| STATUS     | 03h/83h/<br>103h/183h | 0001 1xxx                                         | 000q quuu <sup>(4)</sup> | uuuq quuu <sup>(4)</sup>                         |

| FSR        | 04h/84h/<br>104h/184h | XXXX XXXX                                         | սսսս սսսս                | սսսս սսսս                                        |

| PORTA      | 05h                   | XXXX XXXX                                         | xxxx xxxx                | uuuu uuuu                                        |

| PORTB      | 06h                   | xxxx xxxx                                         | XXXX XXXX                | นนนน นนนน                                        |

| PORTC      | 07h                   | XXXX XXXX                                         | XXXX XXXX                | սսսս սսսս                                        |

| PORTE      | 09h                   | x                                                 | x                        | u                                                |

| PCLATH     | 0Ah/8Ah/<br>10Ah/18Ah | 0 0000                                            | 0 0000                   | u uuuu                                           |

| INTCON     | 0Bh/8Bh/<br>10Bh/18Bh | 0000 000x                                         | 0000 000x                | uuuu uuuu <sup>(2)</sup>                         |

| PIR1       | 0Ch                   | 0000 0000                                         | 0000 0000                | uuuu uuuu <sup>(2)</sup>                         |

| PIR2       | 0Dh                   | 0                                                 | 0                        | u                                                |

| TMR1L      | 0Eh                   | XXXX XXXX                                         | uuuu uuuu                | սսսս սսսս                                        |

| TMR1H      | 0Fh                   | XXXX XXXX                                         | uuuu uuuu                | սսսս սսսս                                        |

| T1CON      | 10h                   | 0000 00-0                                         | uuuu uu-u                | uuuu uu-u                                        |

| TMR2       | 11h                   | 0000 0000                                         | 0000 0000                | սսսս սսսս                                        |

| T2CON      | 12h                   | -000 0000                                         | -000 0000                | -uuu uuuu                                        |

| SSPBUF     | 13h                   | XXXX XXXX                                         | XXXX XXXX                | սսսս սսսս                                        |

| SSPCON     | 14h                   | 0000 0000                                         | 0000 0000                | սսսս սսսս                                        |

| CCPR1L     | 15h                   | xxxx xxxx                                         | xxxx xxxx                | սսսս սսսս                                        |

| CCPR1H     | 16h                   | xxxx xxxx                                         | xxxx xxxx                | սսսս սսսս                                        |

| CCP1CON    | 17h                   | 00 0000                                           | 00 0000                  | uu uuuu                                          |

| RCSTA      | 18h                   | 0000 000x                                         | 0000 000x                | uuuu uuuu                                        |

| TXREG      | 19h                   | 0000 0000                                         | 0000 0000                | uuuu uuuu                                        |

| RCREG      | 1Ah                   | 0000 0000                                         | 0000 0000                | uuuu uuuu                                        |

| CCPR2L     | 1Bh                   | XXXX XXXX                                         | XXXX XXXX                | uuuu uuuu                                        |

| CCPR2H     | 1Ch                   | XXXX XXXX                                         | XXXX XXXX                | uuuu uuuu                                        |

| CCP2CON    | 1Dh                   | 00 0000                                           | 00 0000                  | uu uuuu                                          |

| ADRES      | 1Eh                   | xxxx xxxx                                         | uuuu uuuu                | uuuu uuuu                                        |

| ADCON0     | 1Fh                   | 00 0000                                           | 00 0000                  | uu uuuu                                          |

| OPTION_REG | 81h/181h              | 1111 1111                                         | 1111 1111                | uuuu uuuu                                        |

| TRISA      | 85h                   | 1111 1111                                         | 1111 1111                | սսսս սսսս                                        |

| TRISB      | 86h                   | 1111 1111                                         | 1111 1111                | սսսս սսսս                                        |

| TRISC      | 87h                   | 1111 1111                                         | 1111 1111                | <u>uuuu</u> uuuu                                 |

| TRISE      | 89h                   | 1                                                 | 1                        | u                                                |

#### TABLE 3-4:INITIALIZATION CONDITION FOR REGISTERS

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition.

Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2: One or more bits in INTCON and/or PIR1 and PIR2 will be affected (to cause wake-up).

3: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

4: See Table 3-5 for Reset value for specific condition.

5: If Reset was due to brown-out, then bit 0 = 0. All other Resets will cause bit 0 = u.

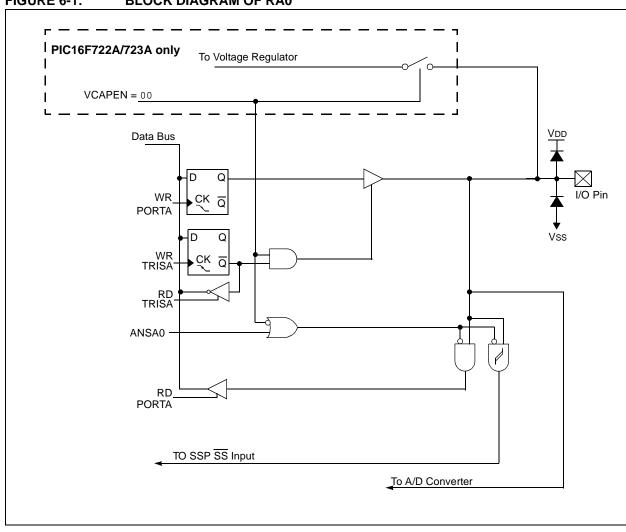

#### 6.2 PORTA and the TRISA Registers

PORTA is a 8-bit wide, bidirectional port. The corresponding data direction register is TRISA (Register 6-3). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). Example 6-1 shows how to initialize PORTA.

Reading the PORTA register (Register 6-2) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch.

The TRISA register (Register 6-3) controls the PORTA pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the

**REGISTER 6-2:** PORTA: PORTA REGISTER R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x RA6 RA5 RA2 RA7 RA4 RA3 RA1 RA0 bit 7 bit 0

| Legend:           |                                                                    |                      |                    |  |  |

|-------------------|--------------------------------------------------------------------|----------------------|--------------------|--|--|

| R = Readable bit  | = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                                   | '0' = Bit is cleared | x = Bit is unknown |  |  |

bit 7-0 RA<7:0>: PORTA I/O Pin bit

1 = Port pin is > VIH 0 = Port pin is < VIL

#### REGISTER 6-3: TRISA: PORTA TRI-STATE REGISTER

| R/W-1  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 7-0 TRISA<7:0>: PORTA Tri-State Control bit

1 = PORTA pin configured as an input (tri-stated)

0 = PORTA pin configured as an output

TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

| Note: | The ANSELA register must be initialized     |

|-------|---------------------------------------------|

|       | to configure an analog channel as a digital |

|       | input. Pins configured as analog inputs     |

|       | will read '0'.                              |

| BANKSEL PORTA ;<br>CLRF PORTA ;Init PORTA<br>BANKSEL ANSELA ;<br>CLRF ANSELA ;digital I/O<br>BANKSEL TRISA ;<br>MOVLW 0Ch ;Set RA<3:2> as inputs<br>MOVWF TRISA ;and set RA<7:4,1:0> | EXAMPLE 6-1:                                                              | INITIALIZING PORTA                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------|

| , as outputs                                                                                                                                                                         | CLRF PORTA<br>BANKSEL ANSELA<br>CLRF ANSELA<br>BANKSEL TRISA<br>MOVLW OCh | ;Init PORTA<br>;<br>;digital I/O<br>;<br>;Set RA<3:2> as inputs |

|         |         | •••••  |        |             |             |        |             |        |                     |

|---------|---------|--------|--------|-------------|-------------|--------|-------------|--------|---------------------|

| Name    | Bit 7   | Bit 6  | Bit 5  | Bit 4       | Bit 3       | Bit 2  | Bit 1       | Bit 0  | Register<br>on Page |

| ADCON0  |         |        | CHS3   | CHS2        | CHS1        | CHS0   | GO/<br>DONE | ADON   | 85                  |

| ADCON1  | _       | ADCS2  | ADCS1  | ADCS0       | —           | —      | ADREF1      | ADREF0 | 86                  |

| ANSELA  |         |        | ANSA5  | ANSA4       | ANSA3       | ANSA2  | ANSA1       | ANSA0  | 44                  |

| ANSELB  | _       | —      | ANSB5  | ANSB4       | ANSB3       | ANSB2  | ANSB1       | ANSB0  | 53                  |

| ADRES   |         |        | A/[    | D Result Re | gister Byte |        |             |        | 86                  |

| CCP2CON | _       | _      | DC2B1  | DC2B0       | CCP2M3      | CCP2M2 | CCP2M1      | CCP2M0 | 115                 |

| FVRCON  | FVRRDY  | FVREN  | _      | —           | —           | —      | ADFVR1      | ADFVR0 | 90                  |

| INTCON  | GIE     | PEIE   | T0IE   | INTE        | RBIE        | T0IF   | INTF        | RBIF   | 36                  |

| PIE1    | TMR1GIE | ADIE   | RCIE   | TXIE        | SSPIE       | CCP1IE | TMR2IE      | TMR1IE | 37                  |

| PIR1    | TMR1GIF | ADIF   | RCIF   | TXIF        | SSPIF       | CCP1IF | TMR2IF      | TMR1IF | 39                  |

| TRISA   | TRISA7  | TRISA6 | TRISA5 | TRISA4      | TRISA3      | TRISA2 | TRISA1      | TRISA0 | 43                  |

| TRISB   | TRISB7  | TRISB6 | TRISB5 | TRISB4      | TRISB3      | TRISB2 | TRISB1      | TRISB0 | 52                  |

#### TABLE 9-2: SUMMARY OF ASSOCIATED ADC REGISTERS

**Legend:** x = unknown, u = unchanged, - = unimplemented read as '0', <math>q = value depends on condition. Shaded cells are not used for ADC module.

## 14.1 Analog MUX

The capacitive sensing module can monitor up to 8 inputs. The capacitive sensing inputs are defined as CPS<7:0>. To determine if a frequency change has occurred the user must:

- Select the appropriate CPS pin by setting the CPSCH<2:0> bits of the CPSCON1 register

- Set the corresponding ANSEL bit

- Set the corresponding TRIS bit

- Run the software algorithm

Selection of the CPSx pin while the module is enabled will cause the capacitive sensing oscillator to be on the CPSx pin. Failure to set the corresponding ANSEL and TRIS bits can cause the capacitive sensing oscillator to stop, leading to false frequency readings.

### 14.2 Capacitive Sensing Oscillator

The capacitive sensing oscillator consists of a constant current source and a constant current sink, to produce a triangle waveform. The CPSOUT bit of the CPSCON0 register shows the status of the capacitive sensing oscillator, whether it is a sinking or sourcing current. The oscillator is designed to drive a capacitive load (single PCB pad) and at the same time, be a clock source to either Timer0 or Timer1. The oscillator has three different current settings as defined by CPS-RNG<1:0> of the CPSCON0 register. The different current settings for the oscillator serve two purposes:

- Maximize the number of counts in a timer for a fixed-time base

- Maximize the count differential in the timer during a change in frequency

### 14.3 Timer Resources

To measure the change in frequency of the capacitive sensing oscillator, a fixed-time base is required. For the period of the fixed-time base, the capacitive sensing oscillator is used to clock either Timer0 or Timer1. The frequency of the capacitive sensing oscillator is equal to the number of counts in the timer divided by the period of the fixed-time base.

### 14.4 Fixed-Time Base

To measure the frequency of the capacitive sensing oscillator, a fixed-time base is required. Any timer resource or software loop can be used to establish the fixed-time base. It is up to the end user to determine the method in which the fixed-time base is generated.

Note: The fixed-time base can not be generated by the timer resource the capacitive sensing oscillator is clocking.

### 14.4.1 TIMER0

To select Timer0 as the timer resource for the capacitive sensing module:

- · Set the T0XCS bit of the CPSCON0 register

- · Clear the T0CS bit of the OPTION register

When Timer0 is chosen as the timer resource, the capacitive sensing oscillator will be the clock source for Timer0. Refer to **Section 11.0** "**Timer0 Module**" for additional information.

#### 14.4.2 TIMER1

To select Timer1 as the timer resource for the capacitive sensing module, set the TMR1CS<1:0> of the T1CON register to '11'. When Timer1 is chosen as the timer resource, the capacitive sensing oscillator will be the clock source for Timer1. Because the Timer1 module has a gate control, developing a time base for the frequency measurement can be simplified using either:

- The Timer0 overflow flag

- The Timer2 overflow flag

- The WDT overflow flag

It is recommended that one of these flags, in conjunction with the toggle mode of the Timer1 gate, is used to develop the fixed-time base required by the software portion of the capacitive sensing module. Refer to **Section 12.0 "Timer1 Module with Gate Control**" for additional information.

#### TABLE 14-1: TIMER1 ENABLE FUNCTION

| TMR10N | TMR1GE | Timer1 Operation       |

|--------|--------|------------------------|

| 0      | 0      | Off                    |

| 0      | 1      | Off                    |

| 1      | 0      | On                     |

| 1      | 1      | Count Enabled by input |

| LOISTER       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                  |              |                  |                 |                 |        |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------|------------------|-----------------|-----------------|--------|

| U-0           | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | R/W-0            | R/W-0        | R/W-0            | R/W-0           | R/W-0           | R/W-0  |

|               | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | DCxB1            | DCxB0        | CCPxM3           | CCPxM2          | CCPxM1          | CCPxM0 |

| bit 7         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                  |              |                  |                 |                 | bit (  |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                  |              |                  |                 |                 |        |

| Legend:       | 1.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                  |              |                  |                 |                 |        |

| R = Readable  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | W = Writable     |              | •                | nented bit, rea |                 |        |

| -n = Value at | POR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | '1' = Bit is set |              | '0' = Bit is cle | ared            | x = Bit is unkr | nown   |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                  |              |                  |                 |                 |        |

| bit 7-6       | Unimplemen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ted: Read as '   | 0'           |                  |                 |                 |        |

|               | Capture mode<br>Unused<br>Compare mod<br>Unused<br><u>PWM mode:</u><br>These bits are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <u>de:</u>       | of the PWM c | luty cycle. The  | eight MSbs are  | e found in CCP  | RxL.   |

| bit 3-0       | These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.<br><b>CCPxM&lt;3:0&gt;:</b> CCP Mode Select bits<br>0000 = Capture/Compare/PWM Off (resets CCP module)<br>0011 = Unused (reserved)<br>0010 = Compare mode, toggle output on match (CCPxIF bit of the PIRx register is set)<br>0111 = Unused (reserved)<br>0100 = Capture mode, every falling edge<br>0101 = Capture mode, every falling edge<br>0101 = Capture mode, every 4th rising edge<br>0111 = Capture mode, every 16th rising edge<br>1000 = Compare mode, set output on match (CCPxIF bit of the PIRx register is set)<br>1011 = Compare mode, clear output on match (CCPxIF bit of the PIRx register is set)<br>1010 = Compare mode, generate software interrupt on match (CCPxIF bit is set of the PIRx register is set)<br>1010 = Compare mode, generate software interrupt on match (CCPxIF bit is set of the PIRx register is set, TMR1<br>and A/D conversion <sup>(1)</sup> is started if the ADC module is enabled. CCPx pin is unaffected<br>11xx = PWM mode. |                  |              |                  |                 | PIRx registe    |        |

#### REGISTER 15-1: CCPxCON: CCPx CONTROL REGISTER

**Note 1:** A/D conversion start feature is available only on CCP2.

| FIGURE 16-8:            | SYNCHRONOUS RECEPTION (MASTER MODE, SREN)                                          |     |

|-------------------------|------------------------------------------------------------------------------------|-----|

| RX/DT<br>pin            | bit 0 bit 1 bit 2 bit 3 bit 4 bit 5 bit 6 bit 7                                    |     |

| TX/CK pin               |                                                                                    |     |

| Write to<br>bit SREN    |                                                                                    |     |

| SREN bit                | l                                                                                  |     |

| CREN bit <u>'</u> 0'    |                                                                                    | ʻ0' |

| RCIF bit<br>(Interrupt) |                                                                                    |     |

| Read<br>RCREG           |                                                                                    |     |

| Note: Timing d          | iagram demonstrates Synchronous Master mode with bit SREN = 1 and bit BRGH = $0$ . |     |

| Name   | Bit 7                        | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1     | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|------------------------------|--------|--------|--------|--------|--------|-----------|-----------|----------------------|---------------------------------|

| INTCON | GIE                          | PEIE   | TOIE   | INTE   | RBIE   | T0IF   | INTF      | RBIF      | 0000 000x            | 0000 000x                       |

| PIE1   | TMR1GIE                      | ADIE   | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE    | TMR1IE    | 0000 0000            | 0000 0000                       |

| PIR1   | TMR1GIF                      | ADIF   | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF    | TMR1IF    | 0000 0000            | 0000 0000                       |

| RCREG  | AUSART Receive Data Register |        |        |        |        |        | 0000 0000 | 0000 0000 |                      |                                 |

| RCSTA  | SPEN                         | RX9    | SREN   | CREN   | ADDEN  | FERR   | OERR      | RX9D      | 0000 000x            | 0000 000x                       |

| TRISC  | TRISC7                       | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1    | TRISC0    | 1111 1111            | 1111 1111                       |

| TXSTA  | CSRC                         | TX9    | TXEN   | SYNC   | —      | BRGH   | TRMT      | TX9D      | 0000 -010            | 0000 -010                       |

#### TABLE 16-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for synchronous master reception.

## 16.4 AUSART Operation During Sleep

The AUSART will remain active during Sleep only in the Synchronous Slave mode. All other modes require the system clock and therefore can not generate the necessary signals to run the Transmit or Receive Shift registers during Sleep.

Synchronous Slave mode uses an externally generated clock to run the Transmit and Receive Shift registers.

#### 16.4.1 SYNCHRONOUS RECEIVE DURING SLEEP

To receive during Sleep, all the following conditions must be met before entering Sleep mode:

- RCSTA and TXSTA Control registers must be configured for Synchronous Slave Reception (refer to Section 16.3.2.4 "Synchronous Slave Reception Setup:").

- If interrupts are desired, set the RCIE bit of the PIE1 register and the PEIE bit of the INTCON register.

- The RCIF interrupt flag must be cleared by reading RCREG to unload any pending characters in the receive buffer.

Upon entering Sleep mode, the device will be ready to accept data and clocks on the RX/DT and TX/CK pins, respectively. When the data word has been completely clocked in by the external device, the RCIF interrupt flag bit of the PIR1 register will be set, thereby waking the processor from Sleep.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the Global Interrupt Enable (GIE) bit of the INTCON register is also set, then the Interrupt Service Routine at address 0004h will be called.

#### 16.4.2 SYNCHRONOUS TRANSMIT DURING SLEEP

To transmit during Sleep, all the following conditions must be met before entering Sleep mode:

- RCSTA and TXSTA Control registers must be configured for Synchronous Slave Transmission (refer to Section 16.3.2.2 "Synchronous Slave Transmission Setup:").

- The TXIF interrupt flag must be cleared by writing the output data to the TXREG, thereby filling the TSR and transmit buffer.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the PEIE bit of the INTCON register.

Upon entering Sleep mode, the device will be ready to accept clocks on TX/CK pin and transmit data on the RX/DT pin. When the data word in the TSR has been completely clocked out by the external device, the pending byte in the TXREG will transfer to the TSR and the TXIF flag will be set, thereby waking the processor from Sleep. At this point, the TXREG is available to accept another character for transmission, which will clear the TXIF flag.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the Global Interrupt Enable (GIE) bit is also set then the Interrupt Service Routine at address 0004h will be called.

#### 17.1.1 MASTER MODE

In Master mode, data transfer can be initiated at any time because the master controls the SCK line. Master mode determines when the slave (Figure 17-1, Processor 2) transmits data via control of the SCK line.

#### 17.1.1.1 Master Mode Operation

The SSP consists of a transmit/receive shift register (SSPSR) and a buffer register (SSPBUF). The SSPSR register shifts the data in and out of the device, MSb first. The SSPBUF register holds the data that is written out of the master until the received data is ready. Once the eight bits of data have been received, the byte is moved to the SSPBUF register. The Buffer Full Status bit, BF of the SSPSTAT register, and the SSP Interrupt Flag bit, SSPIF of the PIR1 register, are then set.

Any write to the SSPBUF register during transmission/ reception of data will be ignored and the Write Collision Detect bit, WCOL of the SSPCON register, will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPBUF register completed successfully.

When the application software is expecting to receive valid data, the SSPBUF should be read before the next byte of data is written to the SSPBUF. The BF bit of the SSPSTAT register is set when SSPBUF has been loaded with the received data (transmission is complete). When the SSPBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. The SSP interrupt may be used to determine when the transmission/reception is complete and the SSPBUF must be read and/or written. If interrupts are not used, then software polling can be done to ensure that a write collision does not occur. Example 17-1 shows the loading of the SSPBUF (SSPSR) for data transmission.

Note: The SSPSR is not directly readable or writable and can only be accessed by addressing the SSPBUF register.

#### 17.1.1.2 Enabling Master I/O

To enable the serial port, the SSPEN bit of the SSPCON register, must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, re-initialize the SSPCON register and then set the SSPEN bit. If a Master mode of operation is selected in the SSPM bits of the SSPCON register, the SDI, SDO and SCK pins will be assigned as serial port pins.

For these pins to function as serial port pins, they must have their corresponding data direction bits set or cleared in the associated TRIS register as follows:

- SDI configured as input

- SDO configured as output

- SCK configured as output

#### 17.1.1.3 Master Mode Setup

In Master mode, the data is transmitted/received as soon as the SSPBUF register is loaded with a byte value. If the master is only going to receive, SDO output could be disabled (programmed and used as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate.

When initializing SPI Master mode operation, several options need to be specified. This is accomplished by programming the appropriate control bits in the SSPCON and SSPSTAT registers. These control bits allow the following to be specified:

- SCK as clock output

- Idle state of SCK (CKP bit)

- Data input sample phase (SMP bit)

- Output data on rising/falling edge of SCK (CKE bit)

- · Clock bit rate

In Master mode, the SPI clock rate (bit rate) is user selectable to be one of the following:

- Fosc/4 (or TCY)

- Fosc/16 (or 4 TCY)

- Fosc/64 (or 16 TCY)

- (Timer2 output)/2

This allows a maximum data rate of 5 Mbps (at Fosc = 20 MHz).

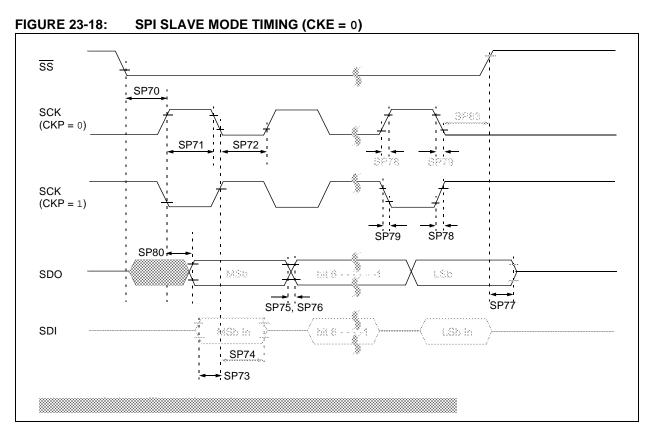

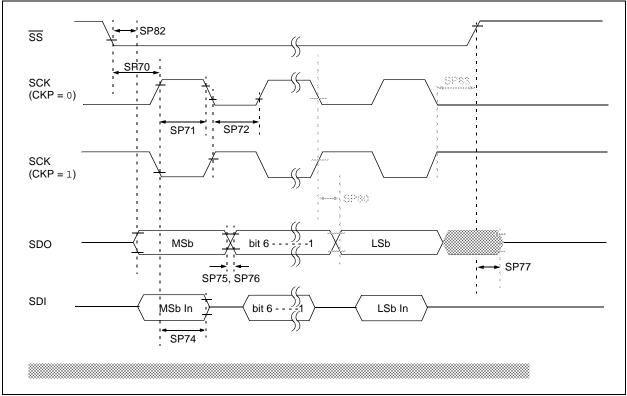

Figure 17-3 shows the waveforms for Master mode. The clock polarity is selected by appropriately programming the CKP bit of the SSPCON register. When the CKE bit is set, the SDO data is valid before there is a clock edge on SCK. The sample time of the input data is shown based on the state of the SMP bit and can occur at the middle or end of the data output time. The time when the SSPBUF is loaded with the received data is shown.

#### 17.1.1.4 Sleep in Master Mode

In Master mode, all module clocks are halted and the transmission/reception will remain in their current state, paused, until the device wakes from Sleep. After the device wakes up from Sleep, the module will continue to transmit/receive data.

| R/W-0        | R/W-0                                                                                                                                                                                                                                                          | R-0                                               | R-0                            | R-0              | R-0             | R-0             | R-0  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--------------------------------|------------------|-----------------|-----------------|------|

| SMP          | CKE                                                                                                                                                                                                                                                            | D/A                                               | Р                              | S                | R/W             | UA              | BF   |

| bit 7        |                                                                                                                                                                                                                                                                | ·                                                 |                                |                  |                 | •               | bit  |

| Legend:      |                                                                                                                                                                                                                                                                |                                                   |                                |                  |                 |                 |      |

| R = Readab   | le bit                                                                                                                                                                                                                                                         | W = Writable                                      | bit                            | U = Unimpler     | mented bit, rea | d as '0'        |      |

| -n = Value a | It POR                                                                                                                                                                                                                                                         | '1' = Bit is set                                  |                                | '0' = Bit is cle | ared            | x = Bit is unkr | nown |

| bit 7        | <u>SPI Master m</u><br>1 = Input data<br>0 = Input data<br><u>SPI Slave mo</u>                                                                                                                                                                                 | a sampled at er<br>a sampled at m                 | nd of data ou<br>iddle of data | output time      |                 |                 |      |

| bit 6        | CKE: SPI Clock Edge Select bit<br><u>SPI mode, CKP = 0:</u><br>1 = Data stable on rising edge of SCK<br>0 = Data stable on falling edge of SCK<br><u>SPI mode, CKP = 1:</u><br>1 = Data stable on falling edge of SCK<br>0 = Data stable on rising edge of SCK |                                                   |                                |                  |                 |                 |      |

| bit 5        | <b>D/A:</b> Data/Address bit<br>Used in I <sup>2</sup> C mode only.                                                                                                                                                                                            |                                                   |                                |                  |                 |                 |      |

| bit 4        | <b>P:</b> Stop bit<br>Used in $I^2C$ mode only.                                                                                                                                                                                                                |                                                   |                                |                  |                 |                 |      |

| bit 3        | <b>S:</b> Start bit<br>Used in I <sup>2</sup> C mode only.                                                                                                                                                                                                     |                                                   |                                |                  |                 |                 |      |

| bit 2        | <b>R/W</b> : Read/Write Information bit<br>Used in I <sup>2</sup> C mode only.                                                                                                                                                                                 |                                                   |                                |                  |                 |                 |      |

| bit 1        | <b>UA:</b> Update Address bit<br>Used in I <sup>2</sup> C mode only.                                                                                                                                                                                           |                                                   |                                |                  |                 |                 |      |

| bit 0        |                                                                                                                                                                                                                                                                | Il Status bit<br>complete, SSP<br>not complete, S |                                | npty             |                 |                 |      |

## REGISTER 17-2: SSPSTAT: SYNC SERIAL PORT STATUS REGISTER (SPI MODE)

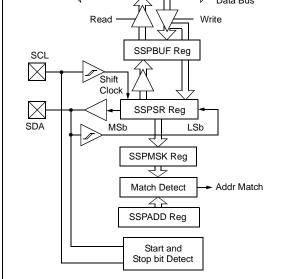

## 17.2 I<sup>2</sup>C Mode

The SSP module, in  $I^2C$  mode, implements all slave functions, except general call support. It provides interrupts on Start and Stop bits in hardware to facilitate firmware implementations of the master functions. The SSP module implements the  $I^2C$  Standard mode specifications:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- Start and Stop bit interrupts enabled to support firmware Master mode

- Address masking

Two pins are used for data transfer; the SCL pin (clock line) and the SDA pin (data line). The user must configure the two pin's data direction bits as inputs in the appropriate TRIS register. Upon enabling  $I^2C$  mode, the  $I^2C$  slew rate limiters in the I/O pads are controlled by the SMP bit of SSPSTAT register. The SSP module functions are enabled by setting the SSPEN bit of SSPCON register.

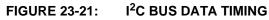

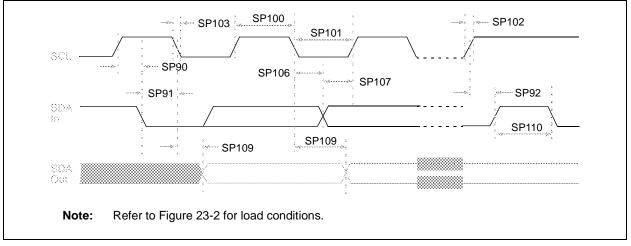

Data is sampled on the rising edge and shifted out on the falling edge of the clock. This ensures that the SDA signal is valid during the SCL high time. The SCL clock input must have minimum high and low times for proper operation. Refer to **Section 23.0** "**Electrical Specifications**".

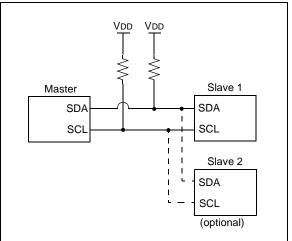

## FIGURE 17-7: I<sup>2</sup>C MODE BLOCK DIAGRAM

## FIGURE 17-8: TYPICAL I<sup>2</sup>C

#### CONNECTIONS

The SSP module has six registers for  $\mathsf{I}^2\mathsf{C}$  operation. They are:

- SSP Control (SSPCON) register

- SSP Status (SSPSTAT) register

- Serial Receive/Transmit Buffer (SSPBUF) register

- SSP Shift Register (SSPSR), not directly accessible

- SSP Address (SSPADD) register

- SSP Address Mask (SSPMSK) register

#### 17.2.1 HARDWARE SETUP

Selection of  $I^2C$  mode, with the SSPEN bit of the SSPCON register set, forces the SCL and SDA pins to be open drain, provided these pins are programmed as inputs by setting the appropriate TRISC bits. The SSP module will override the input state with the output data, when required, such as for Acknowledge and slave-transmitter sequences.

**Note:** Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the I<sup>2</sup>C module.

| MOVF             | Move f                                                                                                                                                                                                                                                                               |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                            |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                                                                                          |

| Operation:       | (f) $\rightarrow$ (dest)                                                                                                                                                                                                                                                             |

| Status Affected: | Z                                                                                                                                                                                                                                                                                    |

| Description:     | The contents of register f is<br>moved to a destination dependent<br>upon the status of d. If $d = 0$ ,<br>destination is W register. If $d = 1$ ,<br>the destination is file register f<br>itself. $d = 1$ is useful to test a file<br>register since status flag Z is<br>affected. |

| Words:           | 1                                                                                                                                                                                                                                                                                    |

| Cycles:          | 1                                                                                                                                                                                                                                                                                    |

| Example:         | MOVF FSR, 0                                                                                                                                                                                                                                                                          |

|                  | After Instruction<br>W = value in FSR<br>register<br>Z = 1                                                                                                                                                                                                                           |

| MOVWF            | Move W to f                                                                           |

|------------------|---------------------------------------------------------------------------------------|

| Syntax:          | [ label ] MOVWF f                                                                     |

| Operands:        | $0 \leq f \leq 127$                                                                   |

| Operation:       | $(W) \rightarrow (f)$                                                                 |

| Status Affected: | None                                                                                  |

| Description:     | Move data from W register to register 'f'.                                            |

| Words:           | 1                                                                                     |

| Cycles:          | 1                                                                                     |

| Example:         | MOVW OPTION<br>F                                                                      |

|                  | Before Instruction<br>OPTION = 0xFF<br>W = 0x4F<br>After Instruction<br>OPTION = 0x4F |

|                  | W = 0x4F                                                                              |

| MOVLW            | Move literal to W                                                                         |

|------------------|-------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                  |

| Operands:        | $0 \le k \le 255$                                                                         |

| Operation:       | $k \rightarrow (W)$                                                                       |

| Status Affected: | None                                                                                      |

| Description:     | The 8-bit literal 'k' is loaded into W register. The "don't cares" will assemble as '0's. |

| Words:           | 1                                                                                         |

| Cycles:          | 1                                                                                         |

| Example:         | MOVLW 0x5A                                                                                |

|                  | After Instruction<br>W = 0x5A                                                             |

| NOP              | No Operation  |  |  |  |

|------------------|---------------|--|--|--|

| Syntax:          | [label] NOP   |  |  |  |

| Operands:        | None          |  |  |  |

| Operation:       | No operation  |  |  |  |

| Status Affected: | None          |  |  |  |

| Description:     | No operation. |  |  |  |

| Words:           | 1             |  |  |  |

| Cycles:          | 1             |  |  |  |

| Example:         | NOP           |  |  |  |

| Param<br>No. | Symbol  | Characteristic  |              | Min. | Тур | Max. | Units | Conditions                                            |

|--------------|---------|-----------------|--------------|------|-----|------|-------|-------------------------------------------------------|

| SP90*        | TSU:STA | Start condition | 100 kHz mode | 4700 | _   |      | ns    | Only relevant for Repeated                            |

|              |         | Setup time      | 400 kHz mode | 600  |     | _    |       | Start condition                                       |

| SP91*        | THD:STA | Start condition | 100 kHz mode | 4000 |     | _    | ns    | After this period, the first clock pulse is generated |

|              |         | Hold time       | 400 kHz mode | 600  |     | _    |       |                                                       |

| SP92*        | TSU:STO | Stop condition  | 100 kHz mode | 4700 | _   | _    | ns    |                                                       |

|              |         | Setup time      | 400 kHz mode | 600  |     | _    |       |                                                       |

| SP93         | THD:STO | Stop condition  | 100 kHz mode | 4000 |     | _    | ns    |                                                       |

|              |         | Hold time       | 400 kHz mode | 600  |     | _    |       |                                                       |

## TABLE 23-12: I<sup>2</sup>C BUS START/STOP BITS REQUIREMENTS

\* These parameters are characterized but not tested.

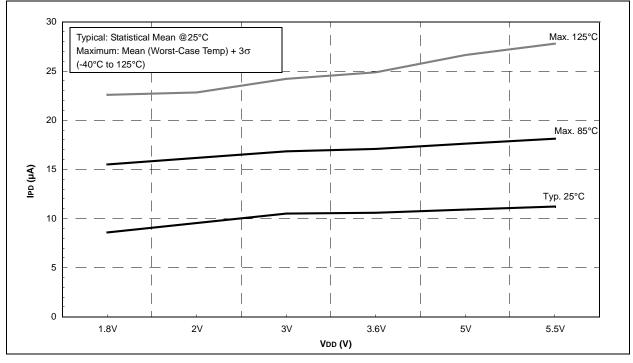

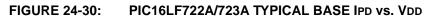

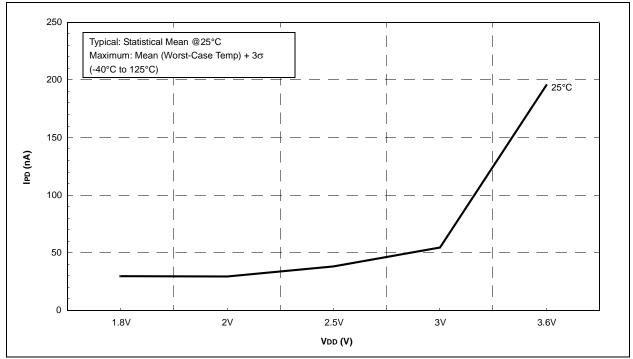

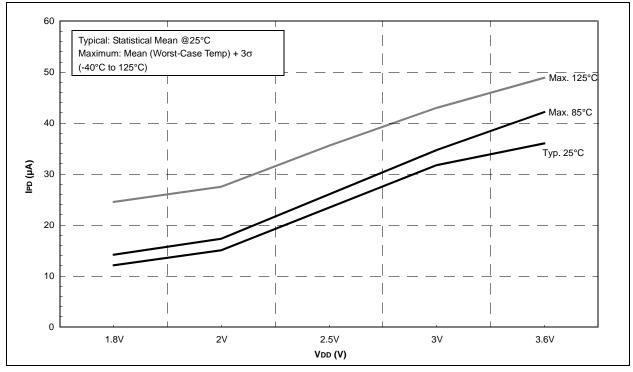

#### FIGURE 24-36: PIC16LF722A/723A CAP SENSE HIGH POWER IPD vs. VDD