Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

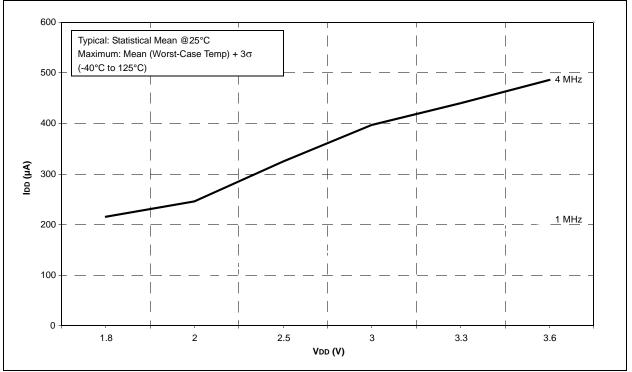

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 11x8b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-UQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf722a-e-mv |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1.0   | Device Overview                                                              | 7    |

|-------|------------------------------------------------------------------------------|------|

| 2.0   | Memory Organization                                                          | . 11 |

| 3.0   | Resets                                                                       | . 23 |

| 4.0   | Interrupts                                                                   | . 33 |

| 5.0   | Low Dropout (LDO) Voltage Regulator                                          | . 41 |

| 6.0   | I/O Ports                                                                    | . 42 |

| 7.0   | Oscillator Module                                                            | . 71 |

| 8.0   | Device Configuration                                                         | 77   |

| 9.0   | Analog-to-Digital Converter (ADC) Module                                     | . 80 |

| 10.0  | Fixed Voltage Reference                                                      | . 90 |

| 11.0  | Timer0 Module                                                                | . 91 |

| 12.0  | Timer1 Module with Gate Control                                              | 103  |

| 13.0  | Timer2 Module                                                                | 115  |

| 14.0  | Capacitive Sensing Module                                                    | 108  |

| 15.0  | Capture/Compare/PWM (CCP) Module                                             | 114  |

| 16.0  | Addressable Universal Synchronous Asynchronous Receiver Transmitter (AUSART) | 124  |

| 17.0  |                                                                              |      |

| 18.0  | Program Memory Read                                                          | 167  |

| 19.0  | Power-Down Mode (Sleep)                                                      | 170  |

| 20.0  | In-Circuit Serial Programming™ (ICSP™)                                       | 172  |

| 21.0  | Instruction Set Summary                                                      | 173  |

| 22.0  | Development Support                                                          | 182  |

| 23.0  | Electrical Specifications                                                    | 186  |

| 24.0  |                                                                              |      |

| 25.0  | Packaging Information                                                        | 249  |

| Appe  | ndix A: Data Sheet Revision History                                          | 261  |

| Appe  | ndix B: Migrating From Other PIC <sup>®</sup> Devices                        | 261  |

| The I | Nicrochip Website                                                            | 262  |

| Cust  | omer Change Notification Service                                             | 262  |

| Cust  | omer Support                                                                 | 262  |

| Prod  | uct Identification System                                                    | 263  |

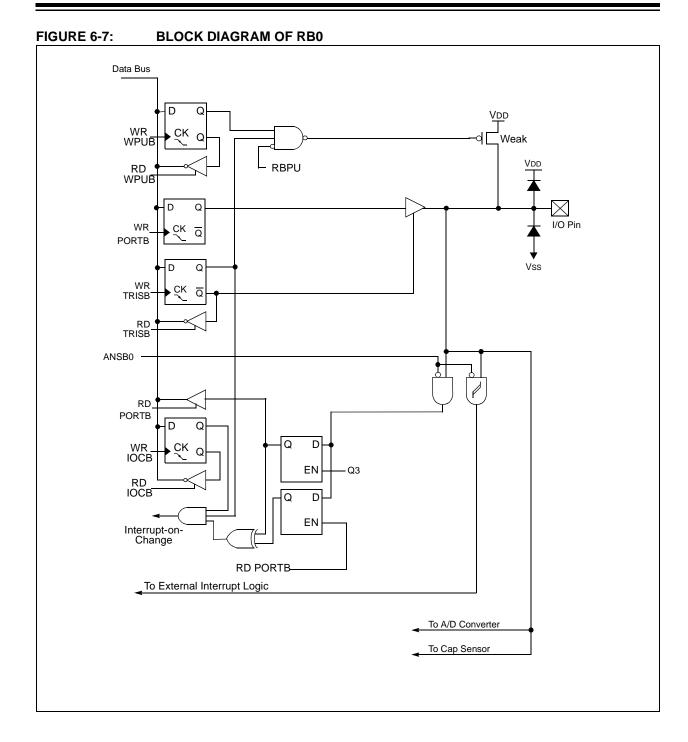

# 6.2.2 PIN DESCRIPTIONS AND DIAGRAMS

Each PORTA pin is multiplexed with other functions. The pins and their combined functions are briefly described here. For specific information about individual functions such as the A/D Converter (ADC), refer to the appropriate section in this data sheet.

# 6.2.2.1 RA0/AN0/SS/VCAP

Figure 6-1 shows the diagram for this pin. This pin is configurable to function as one of the following:

- General purpose I/O

- Analog input for the ADC

- Slave select input for the SSP(1)

- Voltage regulator capacitor pin (PIC16F722A/ 723A only)

# Note 1: SS pin location may be selected as RA5 or RA0.

# 6.2.2.2 RA1/AN1

Figure 6-2 shows the diagram for this pin. This pin is configurable to function as one of the following:

- General purpose I/O

- Analog input for the ADC

### 6.2.2.3 RA2/AN2

Figure 6-2 shows the diagram for this pin. This pin is configurable to function as one of the following:

- General purpose I/O

- Analog input for the ADC

### 6.2.2.4 RA3/AN3/VREF

Figure 6-2 shows the diagram for this pin. This pin is configurable to function as one of the following:

- General purpose I/O

- · Analog input for the ADC

- Voltage reference input for the ADC

### 6.2.2.5 RA4/CPS6/T0CKI

Figure 6-3 shows the diagram for this pin. This pin is configurable to function as one of the following:

- General purpose I/O

- Capacitive sensing input

- Clock input for Timer0

The Timer0 clock input function works independently of any TRIS register setting. Effectively, if TRISA4 = 0, the PORTA4 register bit will output to the pad and clock Timer0 at the same time.

# 6.2.2.6 RA5/AN4/CPS7/SS/VCAP

Figure 6-4 shows the diagram for this pin. This pin is configurable to function as one of the following:

- General purpose I/O

- Analog input for the ADC

- · Capacitive sensing input

- Slave select input for the SSP<sup>(1)</sup>

- Voltage regulator capacitor pin (PIC16F722A/ 723A only)

**Note 1:** SS pin location may be selected as RA5 or RA0.

# 6.2.2.7 RA6/OSC2/CLKOUT/VCAP

Figure 6-5 shows the diagram for this pin. This pin is configurable to function as one of the following:

- General purpose I/O

- Crystal/resonator connection

- Clock output

- Voltage regulator capacitor pin (PIC16F722A/ 723A only)

# 6.2.2.8 RA7/OSC1/CLKIN

Figure 6-6 shows the diagram for this pin. This pin is configurable to function as one of the following:

- General purpose I/O

- Crystal/resonator connection

- Clock input

# 6.5 PORTE and TRISE Registers

PORTE<sup>(1)</sup> is an 1-bit wide, input-only port. RE3 is inputonly and its TRIS bit will always read as '1'.

Reading the PORTE register (Register 6-12) reads the status of the pins. RE3 reads '0' when MCLRE = 1.

#### REGISTER 6-12: PORTE: PORTE REGISTER

| U-0   | U-0 | U-0 | U-0 | R-x | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| —     | —   | —   | _   | RE3 | —   | —   | —     |

| bit 7 |     |     |     |     |     |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-4 | Unimplemented: Read as '0'             |

|---------|----------------------------------------|

| bit 3   | RE3: PORTE I/O Pin bits <sup>(1)</sup> |

|         | 1 = Port pin is > VIH                  |

|         | 0 = Port pin is < VIL                  |

| bit 2-0 | Unimplemented: Read as '0'             |

#### **REGISTER 6-13:** TRISE: PORTE TRI-STATE REGISTER

| U-0   | U-0 | U-0 | U-0 | R-1    | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|--------|-----|-----|-------|

| _     | —   | —   | —   | TRISE3 | —   | —   | —     |

| bit 7 |     |     |     | •      |     |     | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-4 | Unimplemented: Read as '0'                     |

|---------|------------------------------------------------|

| bit 3   | TRISE3: RE3 Port Tri-state Control bit         |

|         | This bit is always '1' as RE3 is an input-only |

| bit 2-0 | Unimplemented: Read as '0'                     |

#### TABLE 6-5: SUMMARY OF REGISTERS ASSOCIATED WITH PORTE

| Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3                 | Bit 2 | Bit 1 | Bit 0 | Register on<br>Page |

|-------|-------|-------|-------|-------|-----------------------|-------|-------|-------|---------------------|

| PORTE | —     |       |       |       | RE3                   |       |       |       | 69                  |

| TRISE | _     |       |       |       | TRISE3 <sup>(1)</sup> |       | _     |       | 69                  |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTE

**Note 1:** This bit is always '1' as RE3 is input-only.

# 7.5 Oscillator Tuning

The INTOSC is factory-calibrated but can be adjusted in software by writing to the OSCTUNE register (Register 7-2).

The default value of the OSCTUNE register is '0'. The value is a 6-bit two's complement number.

When the OSCTUNE register is modified, the INTOSC frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred.

#### REGISTER 7-2: OSCTUNE: OSCILLATOR TUNING REGISTER

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     |     | TUN5  | TUN4  | TUN3  | TUN2  | TUN1  | TUN0  |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 7-6 Unimplemented: Read as '0'

bit 5-0

# 8.0 DEVICE CONFIGURATION

Device configuration consists of Configuration Word 1 and Configuration Word 2 registers, code protection and device ID.

# 8.1 Configuration Words

There are several Configuration Word bits that allow different oscillator and memory protection options. These are implemented as Configuration Word 1 register at 2007h and Configuration Word 2 register at 2008h. These registers are only accessible during programming.

#### REGISTER 8-1: CONFIG1: CONFIGURATION WORD REGISTER 1

|                    |                                                                            | R/P-1                                                                                                                             | R/P-1                                      | U-1 <sup>(4)</sup>                    | R/P-1              | R/P-1            | R/P-1  |

|--------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|---------------------------------------|--------------------|------------------|--------|

|                    |                                                                            | DEBUG                                                                                                                             | PLLEN                                      | —                                     | BORV               | BOREN1           | BOREN0 |

|                    |                                                                            | bit 13                                                                                                                            | 1                                          |                                       |                    |                  | bit    |

|                    |                                                                            |                                                                                                                                   |                                            |                                       |                    |                  |        |

| U-1 <sup>(4)</sup> | R/P-1                                                                      | R/P-1                                                                                                                             | R/P-1                                      | R/P-1                                 | R/P-1              | R/P-1            | R/P-1  |

| —                  | CP                                                                         | MCLRE                                                                                                                             | PWRTE                                      | WDTE                                  | FOSC2              | FOSC1            | FOSC0  |

| oit 7              |                                                                            |                                                                                                                                   |                                            |                                       |                    |                  | bit    |

|                    |                                                                            |                                                                                                                                   |                                            |                                       |                    |                  |        |

| Legend:            |                                                                            | P = Programma                                                                                                                     | able bit                                   |                                       |                    |                  |        |

| R = Readable       | bit                                                                        | W = Writable bi                                                                                                                   | t                                          | U = Unimplem                          | ented bit, read as | s 'O'            |        |

| -n = Value at F    | POR                                                                        | '1' = Bit is set                                                                                                                  |                                            | '0' = Bit is clea                     | ired               | x = Bit is unkno | own    |

| oit 13<br>oit 12   | 1 = In-circuit o<br>0 = In-circuit o<br><b>PLLEN:</b> INTC<br>0 = INTOSC f | ircuit Debugger M<br>debugger disabled<br>debugger enabled<br>DSC PLL Enable b<br>requency is 500 k<br>requency is 16 Mł          | , RB6/ICSPCLI<br>, RB6/ICSPCLI<br>it<br>Hz |                                       | 0                  |                  |        |

| bit 11             |                                                                            | ted: Read as '1'                                                                                                                  | (- )                                       |                                       |                    |                  |        |

| bit 10             | 0 = Brown-ou                                                               | n-out Reset Voltag<br>t Reset Voltage (V<br>t Reset Voltage (V                                                                    | BOR) set to 2.5                            |                                       |                    |                  |        |

| bit 9-8            | BOREN<1:0><br>0x = BOR dis                                                 | Brown-out Rese<br>abled (preconditio<br>abled during opera                                                                        | t Selection bits                           | 1)                                    |                    |                  |        |

| oit 7              | Unimplemen                                                                 | ted: Read as '1'                                                                                                                  |                                            |                                       |                    |                  |        |

| bit 6              | CP: Code Pro                                                               | otection bit <sup>(2)</sup>                                                                                                       |                                            |                                       |                    |                  |        |

|                    |                                                                            | memory code prot                                                                                                                  |                                            |                                       |                    |                  |        |

| bit 5              | MCLRE: RE3<br>1 = RE3/MCL                                                  | memory code prot<br>$\sqrt{MCLR}$ Pin Functi<br>$\overline{R}$ pin function is $\overline{R}$<br>$\overline{R}$ pin function is d | on Select bit <sup>(3)</sup><br>ICLR       |                                       | d to VDD           |                  |        |

| bit 4              |                                                                            | ver-up Timer Enab<br>sabled                                                                                                       | •                                          |                                       |                    |                  |        |

| bit 3              | WDTE: Watch<br>1 = WDT enal<br>0 = WDT disa                                |                                                                                                                                   | e bit                                      |                                       |                    |                  |        |

| 2: TI<br>3: W      | he entire program<br>/hen MCLR is ass                                      | t Reset does not a<br>memory will be el<br>erted in INTOSC o<br>sks unimplemente                                                  | rased when the<br>or RC mode, the          | code protection<br>e internal clock c | is turned off.     | ed.              |        |

4: MPLAB<sup>®</sup> X IDE masks unimplemented Configuration bits to '0'.

# TABLE 9-1: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES

| ADC Clock           | Period (TAD) | Device Frequency (Fosc)     |                             |                              |                               |                               |  |  |

|---------------------|--------------|-----------------------------|-----------------------------|------------------------------|-------------------------------|-------------------------------|--|--|

| ADC<br>Clock Source | ADCS<2:0>    | 20 MHz                      | 16 MHz                      | 8 MHz                        | 4 MHz                         | 1 MHz                         |  |  |

| Fosc/2              | 000          | 100 ns <sup>(2)</sup>       | 125 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>        | 500 ns <sup>(2)</sup>         | 2.0 μs                        |  |  |

| Fosc/4              | 100          | 200 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>        | 1.0 μs                        | 4.0 μs                        |  |  |

| Fosc/8              | 001          | 400 ns <sup>(2)</sup>       | 0.5 μs <b>(2)</b>           | 1.0 μs                       | 2.0 μs                        | 8.0 μs <b><sup>(3)</sup></b>  |  |  |

| Fosc/16             | 101          | 800 ns                      | 1.0 μs                      | 2.0 μs                       | 4.0 μs                        | 16.0 μs <b><sup>(3)</sup></b> |  |  |

| Fosc/32             | 010          | 1.6 μs                      | 2.0 μs                      | 4.0 μs                       | 8.0 μs <sup>(3)</sup>         | 32.0 μs <b><sup>(3)</sup></b> |  |  |

| Fosc/64             | 110          | 3.2 μs                      | 4.0 μs                      | 8.0 μs <b><sup>(3)</sup></b> | 16.0 μs <b><sup>(3)</sup></b> | 64.0 μs <b><sup>(3)</sup></b> |  |  |

| FRC                 | x11          | 1.0-6.0 μs <sup>(1,4)</sup> | 1.0-6.0 μs <sup>(1,4)</sup> | 1.0-6.0 μs <sup>(1,4)</sup>  | 1.0-6.0 μs <sup>(1,4)</sup>   | 1.0-6.0 μs <sup>(1,4)</sup>   |  |  |

Legend: Shaded cells are outside of recommended range.

**Note 1:** The FRC source has a typical TAD time of 1.6 μs for VDD.

- 2: These values violate the minimum required TAD time.

- **3:** For faster conversion times, the selection of another clock source is recommended.

- 4: When the device frequency is greater than 1 MHz, the FRC clock source is only recommended if the conversion will be performed during Sleep.

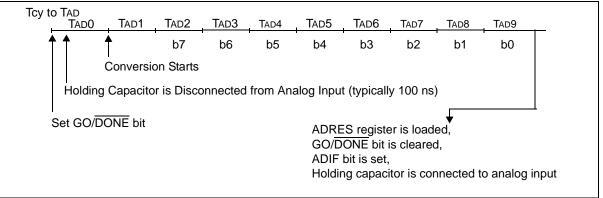

### FIGURE 9-2: ANALOG-TO-DIGITAL CONVERSION TAD CYCLES

#### 11.1.3 SOFTWARE PROGRAMMABLE PRESCALER

A single software programmable prescaler is available for use with either Timer0 or the Watchdog Timer (WDT), but not both simultaneously. The prescaler assignment is controlled by the PSA bit of the OPTION register. To assign the prescaler to Timer0, the PSA bit must be cleared to a '0'.

There are eight prescaler options for the Timer0 module ranging from 1:2 to 1:256. The pres ca le values are selectable via the PS<2:0> bits of the OPTION register. In order to have a 1:1 prescaler value for the Timer0 module, the prescaler must be assigned to the WDT module.

The prescaler is not readable or writable. When assigned to the Timer0 module, all instructions writing to the TMR0 register will clear the prescaler.

| Note: | When the prescaler is assigned to WDT, a    |

|-------|---------------------------------------------|

|       | CLRWDT instruction will clear the prescaler |

|       | along with the WDT.                         |

#### 11.1.4 TIMER0 INTERRUPT

Timer0 will generate an interrupt when the TMR0 register overflows from PH to 00h. The T0IF interrupt flag bit of the INTCON register is set every time the TMR0 register overflows, regardless of whether or not the Timer0 interrupt is enabled. The T0IF bit can only be cleared in software. The Timer0 interrupt enable is the T0IE bit of the INTCON register.

| Note: | The Timer0 interrupt cannot wake the    |  |  |  |  |  |

|-------|-----------------------------------------|--|--|--|--|--|

|       | processor from Sleep since the timer is |  |  |  |  |  |

|       | frozen during Sleep.                    |  |  |  |  |  |

#### 11.1.5 8-BIT COUNTER MODE SYNCHRONIZATION

When in 8-Bit Counter mode, the incrementing edge on the T0CKI pin must be synchronized to the instruction clock. Synchronization can be accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the instruction clock. The high and low periods of the external clocking source must meet the timing requirements as shown in **Section 23.0** "**Electrical Specifications**".

# 12.1 Timer1 Operation

The Timer1 module is a 16-bit incrementing counter which is accessed through the TMR1H:TMR1L register pair. Writes to TMR1H or TMR1L directly update the counter.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

Timer1 is enabled by configuring the TMR1ON and TMR1GE bits in the T1CON and T1GCON registers, respectively. Table 12-1 displays the Timer1 enable selections.

TABLE 12-1: TIMER1 ENABLE SELECTIONS

| TMR10N | TMR1GE | Timer1<br>Operation |

|--------|--------|---------------------|

| 0      | 0      | Off                 |

| 0      | 1      | Off                 |

| 1      | 0      | Always On           |

| 1      | 1      | Count Enabled       |

# 12.2 Clock Source Selection

The TMR1CS<1:0> and T1OSCEN bits of the T1CON register are used to select the clock source for Timer1. Table 12-2 displays the clock source selections.

#### 12.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected the TMR1H:TMR1L register pair will increment on multiples of FISC as determined by the Timer1 prescaler.

## 12.2.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1 module may work as a timer or a counter.

When enabled to count, Timer1 is increment ed on the rising edge of the external clock input T1CKI or the capacitive sensing oscillator signal. Either of these external clock sources can be synchronized to the microcontroller system clock or they can run asynchronously.

When used as a timer with a clock oscillator, an external 32.768 kHz crystal can be used in conjunction with the dedicated internal oscillator circuit.

| Note: | In Counter mode, a falling edge must be<br>registered by the counter prior to the first<br>incrementing rising edge after any one or |

|-------|--------------------------------------------------------------------------------------------------------------------------------------|

|       | more of the following conditions:                                                                                                    |

|       | •Timer1 enabled after POP                                                                                                            |

•Timer1 enabled after POR

•Write to TMR1H or TMR1L

- Timer1 is disabled

- •Timer1 is disabled (TMR1ON = 0) when T1CKI is high then Timer1 is enabled (TMR1ON= 1) when T1CKI is low.

| TMR1CS1 | TMR1CS0 | T10SCEN | Clock Source                           |  |

|---------|---------|---------|----------------------------------------|--|

| 0       | 1       | x       | System Clock (FOSC)                    |  |

| 0       | 0       | x       | Instruction Clock (Fosc/4)             |  |

| 1       | 1       | x       | Capacitive Sensing Oscillator          |  |

| 1       | 0       | 0       | External Clocking on T1CKI Pin         |  |

| 1       | 0       | 1       | Oscillator Circuit on T1OSI/T1OSO Pins |  |

### TABLE 12-2: CLOCK SOURCE SELECTIONS

| <b>REGISTER 14</b>                                                         | -2: CPSC | ON1: CAPAC   | ITIVE SENS | SING CONTR   | OL REGISTE       | R 1      |        |

|----------------------------------------------------------------------------|----------|--------------|------------|--------------|------------------|----------|--------|

| U-0                                                                        | U-0      | U-0          | U-0        | U-0          | R/W-0            | R/W-0    | R/W-0  |

| —                                                                          | —        | —            | —          | _            | CPSCH2           | CPSCH1   | CPSCH0 |

| bit 7                                                                      |          |              |            |              |                  |          | bit 0  |

|                                                                            |          |              |            |              |                  |          |        |

| Legend:                                                                    |          |              |            |              |                  |          |        |

| R = Readable b                                                             | bit      | W = Writable | bit        | U = Unimpler | mented bit, read | l as '0' |        |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |          |              |            |              | nown             |          |        |

| bit 7-3 | Unimplemented: Read as '0'                         |  |  |  |  |  |

|---------|----------------------------------------------------|--|--|--|--|--|

| bit 2-0 | CPSCH<2:0>: Capacitive Sensing Channel Select bits |  |  |  |  |  |

|         | If CPSON = 0:                                      |  |  |  |  |  |

|         | These bits are ignored. No channel is selected.    |  |  |  |  |  |

|         | <u>If CPSON = 1</u> :                              |  |  |  |  |  |

|         | 000 = channel 0, (CPS0)                            |  |  |  |  |  |

|         | 001 = channel 1, (CPS1)                            |  |  |  |  |  |

|         | 010 = channel 2, (CPS2)                            |  |  |  |  |  |

|         | 011 = channel 3, (CPS3)                            |  |  |  |  |  |

|         | 100 = channel 4, (CPS4)                            |  |  |  |  |  |

|         | 101 = channel 5, (CPS5)                            |  |  |  |  |  |

|         | 110 = channel 6, (CPS6)                            |  |  |  |  |  |

|         | 111 = channel 7, (CPS7)                            |  |  |  |  |  |

#### TABLE 14-2: SUMMARY OF REGISTERS ASSOCIATED WITH CAPACITIVE SENSING

| Name       | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Register<br>on Page |

|------------|---------|---------|---------|---------|---------|--------|---------|---------|---------------------|

| ANSELA     |         | —       | ANSA5   | ANSA4   | ANSA3   | ANSA2  | ANSA1   | ANSA0   | 44                  |

| ANSELB     | -       | —       | ANSB5   | ANSB4   | ANSB3   | ANSB2  | ANSB1   | ANSB0   | 53                  |

| OPTION_REG | RBPU    | INTEDG  | TOCS    | T0SE    | PSA     | PS2    | PS1     | PS0     | 19                  |

| PIE1       | TMR1GIE | ADIE    | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 37                  |

| PIR1       | TMR1GIF | ADIF    | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 39                  |

| T1CON      | TMR1CS1 | TMR1CS0 | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | —       | TMR10N  | 103                 |

| T2CON      | -       | TOUTPS3 | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | 107                 |

| TRISA      | TRISA7  | TRISA6  | TRISA5  | TRISA4  | TRISA3  | TRISA2 | TRISA1  | TRISA0  | 43                  |

| TRISB      | TRISB7  | TRISB6  | TRISB5  | TRISB4  | TRISB3  | TRISB2 | TRISB1  | TRISB0  | 52                  |

Legend: - = Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the capacitive sensing module.

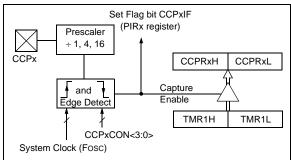

# 15.1 Capture Mode

In Capture mode, CCPRxH:CCPRxL captures the 16-bit value of the TMR1 register when an event occurs on pin CCPx. An event is defined as one of the following and is configured by the CCPxM<3:0> bits of the CCPxCON register:

- Every falling edge

- Every rising edge

- Every 4th rising edge

- Every 16th rising edge

When a capture is made, the Interrupt Request Flag bit CCPxIF of the PIRx register is set. The interrupt flag must be cleared in software. If another capture occurs before the value in the CCPRxH, CCPRxL register pair is read, the old captured value is overwritten by the new captured value (refer to Figure 15-1).

#### 15.1.1 CCPx PIN CONFIGURATION

In Capture mode, the CCPx pin should be configured as an input by setting the associated TRIS control bit.

Either RC1 or RB3 can be selected as the CCP2 pin. Refer to **Section 6.1** "Alternate Pin Function" for more information.

**Note:** If the CCPx pin is configured as an output, a write to the port can cause a capture condition.

#### FIGURE 15-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

### 15.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode or when Timer1 is clocked at Fosc, the capture operation may not work.

## 15.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit of the PIEx register clear to avoid false interrupts. Additionally, the user should clear the CCPxIF interrupt flag bit of the PIRx register following any change in operating mode.

Note: Clocking Timer1 from the system clock (Fosc) should not be used in Capture mode. In order for Capture mode to recognize the trigger event on the CCPx pin, Timer1 must be clocked from the instruction clock (Fosc/4) or from an external clock source.

### 15.1.4 CCP PRESCALER

There are four prescaler settings specified by the CCPxM<3:0> bits of the CCPxCON register. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another does not clear the prescaler and may generate a false interrupt. To avoid this unexpected operation, turn the module off by clearing the CCPxCON register before changing the prescaler (refer to Example 15-1).

#### EXAMPLE 15-1: CHANGING BETWEEN CAPTURE PRESCALERS

| BANKSEL | CCP1CON     | ;Set Bank bits to point |

|---------|-------------|-------------------------|

|         |             | ;to CCP1CON             |

| CLRF    | CCP1CON     | ;Turn CCP module off    |

| MOVLW   | NEW_CAPT_PS | ;Load the W reg with    |

|         |             | ; the new prescaler     |

|         |             | ; move value and CCP ON |

| MOVWF   | CCP1CON     | ;Load CCP1CON with this |

|         |             | ; value                 |

|         |             |                         |

### 15.1.5 CAPTURE DURING SLEEP

Capture mode depends upon the Timer1 module for proper operation. There are two options for driving the Timer1 module in Capture mode. It can be driven by the instruction clock (Fosc/4), or by an external clock source.

If Timer1 is clocked by FOSC/4, then Timer1 will not increment during Sleep. When the device wakes from Sleep, Timer1 will continue from its previous state.

If Timer1 is clocked by an external clock source, then Capture mode will operate as defined in **Section 15.1** "**Capture Mode**".

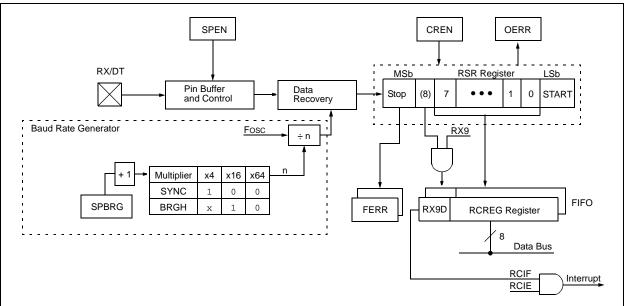

The operation of the AUSART module is controlled through two registers:

- Transmit Status and Control (TXSTA)

- Receive Status and Control (RCSTA)

These registers are detailed in Register 16-1 and Register 16-2, respectively.

# 16.3.2.3 AUSART Synchronous Slave Reception

The operation of the Synchronous Master and Slave modes is identical (Section 16.3.1.4 "Synchronous Master Reception"), with the following exceptions:

- Sleep

- CREN bit is always set, therefore the receiver is never Idle

- SREN bit, which is a "don't care" in Slave mode

A character may be received while in Sleep mode by setting the CREN bit prior to entering Sleep. Once the word is received, the RSR register will transfer the data to the RCREG register. If the RCIE interrupt enable bit of the PIE1 register is set, the interrupt generated will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will branch to the interrupt vector.

- 16.3.2.4 Synchronous Slave Reception Setup:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 3. If 9-bit reception is desired, set the RX9 bit.

- 4. Verify address detection is disabled by clearing the ADDEN bit of the RCSTA register.

- 5. Set the CREN bit to enable reception.

- The RCIF bit of the PIR1 register will be set when reception is complete. An interrupt will be generated if the RCIE bit of the PIE1 register was set.

- 7. If 9-bit mode is enabled, retrieve the Most Significant bit from the RX9D bit of the RCSTA register.

- 8. Retrieve the eight Least Significant bits from the receive FIFO by reading the RCREG register.

- 9. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register.

| Name   | Bit 7                        | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1     | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|------------------------------|--------|--------|--------|--------|--------|-----------|-----------|----------------------|---------------------------------|

| INTCON | GIE                          | PEIE   | TOIE   | INTE   | RBIE   | T0IF   | INTF      | RBIF      | 0000 000x            | 0000 000x                       |

| PIE1   | TMR1GIE                      | ADIE   | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE    | TMR1IE    | 0000 0000            | 0000 0000                       |

| PIR1   | TMR1GIF                      | ADIF   | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF    | TMR1IF    | 0000 0000            | 0000 0000                       |

| RCREG  | AUSART Receive Data Register |        |        |        |        |        | 0000 0000 | 0000 0000 |                      |                                 |

| RCSTA  | SPEN                         | RX9    | SREN   | CREN   | ADDEN  | FERR   | OERR      | RX9D      | 0000 000X            | 0000 000X                       |

| TRISC  | TRISC7                       | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1    | TRISC0    | 1111 1111            | 1111 1111                       |

| TXSTA  | CSRC                         | TX9    | TXEN   | SYNC   | —      | BRGH   | TRMT      | TX9D      | 0000 -010            | 0000 -010                       |

#### TABLE 16-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE RECEPTION

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for synchronous slave reception.

# 16.4 AUSART Operation During Sleep

The AUSART will remain active during Sleep only in the Synchronous Slave mode. All other modes require the system clock and therefore can not generate the necessary signals to run the Transmit or Receive Shift registers during Sleep.

Synchronous Slave mode uses an externally generated clock to run the Transmit and Receive Shift registers.

#### 16.4.1 SYNCHRONOUS RECEIVE DURING SLEEP

To receive during Sleep, all the following conditions must be met before entering Sleep mode:

- RCSTA and TXSTA Control registers must be configured for Synchronous Slave Reception (refer to Section 16.3.2.4 "Synchronous Slave Reception Setup:").

- If interrupts are desired, set the RCIE bit of the PIE1 register and the PEIE bit of the INTCON register.

- The RCIF interrupt flag must be cleared by reading RCREG to unload any pending characters in the receive buffer.

Upon entering Sleep mode, the device will be ready to accept data and clocks on the RX/DT and TX/CK pins, respectively. When the data word has been completely clocked in by the external device, the RCIF interrupt flag bit of the PIR1 register will be set, thereby waking the processor from Sleep.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the Global Interrupt Enable (GIE) bit of the INTCON register is also set, then the Interrupt Service Routine at address 0004h will be called.

#### 16.4.2 SYNCHRONOUS TRANSMIT DURING SLEEP

To transmit during Sleep, all the following conditions must be met before entering Sleep mode:

- RCSTA and TXSTA Control registers must be configured for Synchronous Slave Transmission (refer to Section 16.3.2.2 "Synchronous Slave Transmission Setup:").

- The TXIF interrupt flag must be cleared by writing the output data to the TXREG, thereby filling the TSR and transmit buffer.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the PEIE bit of the INTCON register.

Upon entering Sleep mode, the device will be ready to accept clocks on TX/CK pin and transmit data on the RX/DT pin. When the data word in the TSR has been completely clocked out by the external device, the pending byte in the TXREG will transfer to the TSR and the TXIF flag will be set, thereby waking the processor from Sleep. At this point, the TXREG is available to accept another character for transmission, which will clear the TXIF flag.

Upon waking from Sleep, the instruction following the SLEEP instruction will be executed. If the Global Interrupt Enable (GIE) bit is also set then the Interrupt Service Routine at address 0004h will be called.

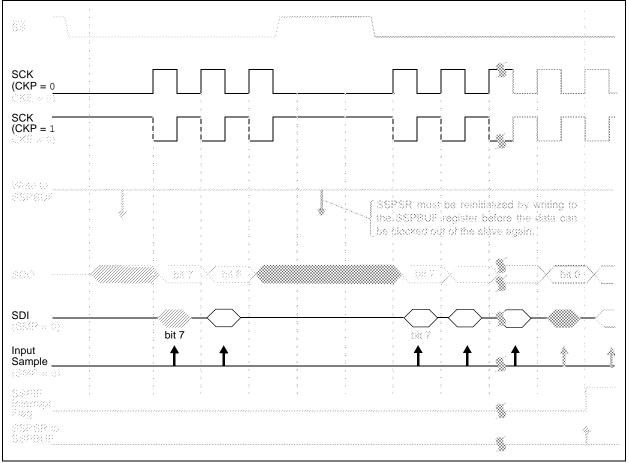

#### 17.1.2.4 Slave Select Operation

The  $\overline{SS}$  pin allows Synchronous Slave mode operation. The SPI must be in Slave mode with  $\overline{SS}$  pin control enabled (SSPM<3:0> = 0100). The associated TRIS bit for the  $\overline{SS}$  pin must be set, making  $\overline{SS}$  an input.

In Slave Select mode, when:

- SS = 0, The device operates as specified in Section 17.1.2 "Slave Mode".

- $\overline{SS} = 1$ , The SPI module is held in Reset and the SDO pin will be tri-stated.

- **Note 1:** When the SPI is in Slave mode with  $\overline{SS}$  pin control enabled (SSPM<3:0> = 0100), the SPI module will reset if the  $\overline{SS}$  pin is driven high.

- 2: If the SPI is used in Slave mode with CKE set, the SS pin control must be enabled.

When the SPI module resets, the bit counter is cleared to '0'. This can be done by either forcing the SS pin to a high level or clearing the SSPEN bit. Figure 17-6 shows the timing waveform for such a synchronization event.

| Note: | SSPSR must be reinitialized by writing to |

|-------|-------------------------------------------|

|       | the SSPBUF register before the data can   |

|       | be clocked out of the slave again.        |

#### 17.1.2.5 Sleep in Slave Mode

While in Sleep mode, the slave can transmit/receive data. The SPI Transmit/Receive Shift register operates asynchronously to the device on the externally supplied clock source. This allows the device to be placed in Sleep mode and data to be shifted into the SPI Transmit/Receive Shift register. When all eight bits have been received, the SSP Interrupt Flag bit will be set and if enabled, will wake the device from Sleep.

| R/W-0             | R/W-0                                                                                                                                                                                              | R/W-0            | R/W-0           | R/W-0                | R/W-0            | R/W-0              | R/W-0          |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------|----------------------|------------------|--------------------|----------------|--|

| WCOL              | SSPOV                                                                                                                                                                                              | SSPEN            | CKP             | SSPM3                | SSPM2            | SSPM1              | SSPM0          |  |

| bit 7             | •                                                                                                                                                                                                  |                  |                 |                      |                  |                    | bit (          |  |

| Legend:           |                                                                                                                                                                                                    |                  |                 |                      |                  |                    |                |  |

| R = Reada         | ble bit                                                                                                                                                                                            | W = Writable     | bit             | U = Unimple          | mented bit, rea  | d as '0'           |                |  |

| -n = Value at POR |                                                                                                                                                                                                    | '1' = Bit is set |                 | '0' = Bit is cleared |                  | x = Bit is unknown |                |  |

| bit 7             | WCOL: Writ                                                                                                                                                                                         | e Collision Dete | ct bit          |                      |                  |                    |                |  |

|                   | software                                                                                                                                                                                           | ,                | s written while | e it is still transr | mitting the prev | ious word (mus     | t be cleared i |  |

| 1.11.0            |                                                                                                                                                                                                    | 0 = No collision |                 |                      |                  |                    |                |  |

| bit 6             | SSPOV: Receive Overflow Indicator bit                                                                                                                                                              |                  |                 |                      |                  |                    |                |  |

|                   | 1 = A byte is received while the SSPBUF register is still holding the previous byte. SSPOV is a "don<br>care" in Transmit mode. SSPOV must be cleared in software in either mode.                  |                  |                 |                      |                  |                    |                |  |

|                   | 0 = No  overflow                                                                                                                                                                                   |                  |                 |                      |                  |                    |                |  |

| bit 5             | SSPEN: Synchronous Serial Port Enable bit                                                                                                                                                          |                  |                 |                      |                  |                    |                |  |

|                   | <ul> <li>1 = Enables the serial port and configures the SDA and SCL pins as serial port pins<sup>(2)</sup></li> <li>0 = Disables serial port and configures these pins as I/O port pins</li> </ul> |                  |                 |                      |                  |                    |                |  |

| bit 4             | CKP: Clock Polarity Select bit                                                                                                                                                                     |                  |                 |                      |                  |                    |                |  |

|                   | 1 = Release control of SCL                                                                                                                                                                         |                  |                 |                      |                  |                    |                |  |

|                   | 0 = Holds clock low (clock stretch). (Used to ensure data setup time.)                                                                                                                             |                  |                 |                      |                  |                    |                |  |

| bit 3-0           | SSPM<3:0>: Synchronous Serial Port Mode Select bits                                                                                                                                                |                  |                 |                      |                  |                    |                |  |

|                   | $0110 = I^2 C$ Slave mode, 7-bit address                                                                                                                                                           |                  |                 |                      |                  |                    |                |  |

|                   | 0111 = I <sup>2</sup> C Slave mode, 10-bit address                                                                                                                                                 |                  |                 |                      |                  |                    |                |  |

|                   | 1000 = Reserved<br>1001 = Load SSPMSK register at SSPADD SFR Address <sup>(1)</sup>                                                                                                                |                  |                 |                      |                  |                    |                |  |

|                   | 1001 = Reserved                                                                                                                                                                                    |                  |                 |                      |                  |                    |                |  |

|                   | 1011 = I <sup>2</sup> C Firmware Controlled Master mode (Slave Idle)                                                                                                                               |                  |                 |                      |                  |                    |                |  |

|                   | 1100 = Reserved                                                                                                                                                                                    |                  |                 |                      |                  |                    |                |  |

|                   | 1101 = Reserved 1110 = I <sup>2</sup> C Slave mode, 7-bit address with Start and Stop bit interrupts enabled                                                                                       |                  |                 |                      |                  |                    |                |  |

|                   | $1110 = 1^{\circ}$ C Slave mode, 10-bit address with Start and Stop bit interrupts enabled                                                                                                         |                  |                 |                      |                  |                    |                |  |

| Note 1.           | When this mode                                                                                                                                                                                     |                  |                 |                      |                  |                    | DMCK register  |  |

# REGISTER 17-3: SSPCON: SYNCHRONOUS SERIAL PORT CONTROL REGISTER (I<sup>2</sup>C MODE)

2: When enabled, these pins must be properly configured as input or output using the associated TRIS bit.

| ADDLW            | Add literal and W                                                                                                      |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] ADDLW k                                                                                                        |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                    |  |  |  |

| Operation:       | $(W) + k \to (W)$                                                                                                      |  |  |  |

| Status Affected: | C, DC, Z                                                                                                               |  |  |  |

| Description:     | The contents of the W register<br>are added to the 8-bit literal 'k'<br>and the result is placed in the<br>W register. |  |  |  |

| BCF              | Bit Clear f                                                         |  |  |

|------------------|---------------------------------------------------------------------|--|--|

| Syntax:          | [label]BCF f,b                                                      |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |  |  |

| Operation:       | $0 \rightarrow (f < b >)$                                           |  |  |

| Status Affected: | None                                                                |  |  |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |  |  |

| ADDWF            | Add W and f                                                                                                                                                                        |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                                  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                    |  |  |  |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                              |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                           |  |  |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the<br>result is stored in the W register. If<br>'d' is '1', the result is stored back<br>in register 'f'. |  |  |  |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| ANDLW            | AND literal with W                                                                                                   |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                             |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                    |  |  |  |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                      |  |  |  |

| Status Affected: | Z                                                                                                                    |  |  |  |

| Description:     | The contents of W register are<br>AND'ed with the 8-bit literal 'k'.<br>The result is placed in the W reg-<br>ister. |  |  |  |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                                     |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] BTFSC f,b                                                                                                                                                                                                    |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                           |  |  |  |

| Operation:       | skip if (f <b>) = <math>0</math></b>                                                                                                                                                                                          |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                          |  |  |  |

| Description:     | If bit 'b' in register 'f' is '1', the next<br>instruction is executed.<br>If bit 'b', in register 'f', is '0', the<br>next instruction is discarded, and<br>a NOP is executed instead, making<br>this a 2-cycle instruction. |  |  |  |

| ANDWF                                                                                                                                                    | AND W with f                                                    |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--|--|

| Syntax:                                                                                                                                                  | [label] ANDWF f,d                                               |  |  |

| Operands:                                                                                                                                                | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$ |  |  |

| Operation:                                                                                                                                               | (W) .AND. (f) $\rightarrow$ (destination)                       |  |  |

| Status Affected:                                                                                                                                         | Z                                                               |  |  |

| Description: AND the W register with reg<br>'f'. If 'd' is '0', the result is sto<br>the W register. If 'd' is '1', th<br>result is stored back in regis |                                                                 |  |  |

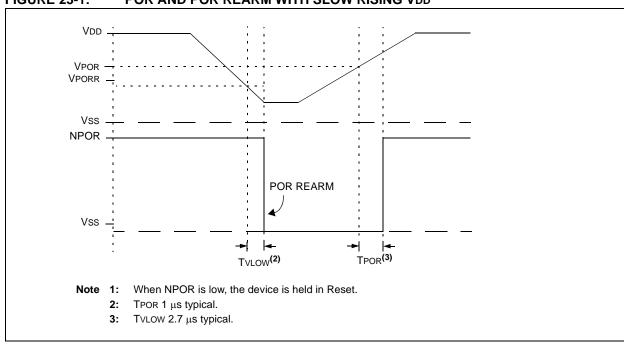

#### FIGURE 23-1: POR AND POR REARM WITH SLOW RISING VDD

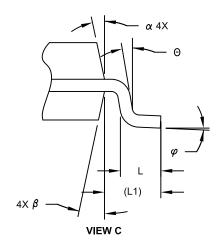

# 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |           |     |      |  |

|--------------------------|-------------|-----------|-----|------|--|

| Dimension Limits         |             | MIN       | NOM | MAX  |  |

| Number of Pins           | N           | 28        |     |      |  |

| Pitch                    | е           | 1.27 BSC  |     |      |  |

| Overall Height           | A           | -         | -   | 2.65 |  |

| Molded Package Thickness | A2          | 2.05      | -   | -    |  |

| Standoff §               | A1          | 0.10      | -   | 0.30 |  |

| Overall Width            | E           | 10.30 BSC |     |      |  |

| Molded Package Width     | E1          | 7.50 BSC  |     |      |  |

| Overall Length           | D           | 17.90 BSC |     |      |  |

| Chamfer (Optional)       | h           | 0.25      | -   | 0.75 |  |

| Foot Length              | L           | 0.40      | -   | 1.27 |  |

| Footprint                | L1          | 1.40 REF  |     |      |  |

| Lead Angle               | Θ           | 0°        | -   | -    |  |

| Foot Angle               | φ           | 0°        | -   | 8°   |  |

| Lead Thickness           | С           | 0.18      | -   | 0.33 |  |

| Lead Width               | b           | 0.31      | -   | 0.51 |  |

| Mold Draft Angle Top     | α           | 5°        | -   | 15°  |  |

| Mold Draft Angle Bottom  | β           | 5°        | _   | 15°  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- Dimensioning and tolerancing per ASME Y14.5M BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing C04-052C Sheet 2 of 2