#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 11x8b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf722a-e-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## PIC16(L)F72X Family Types

| Device        | Data Sheet Index | Program Memory<br>Flash (words) | Data SRAM<br>(bytes) | High-Endurance Flash<br>Memory (bytes) | I/O's <sup>(2)</sup> | 8-bit ADC (ch) | CapSense (ch) | Timers<br>(8/16-bit) | AUSART | SSP (I <sup>2</sup> C/SPI) | ССР | Debug <sup>(1)</sup> | ХГР |

|---------------|------------------|---------------------------------|----------------------|----------------------------------------|----------------------|----------------|---------------|----------------------|--------|----------------------------|-----|----------------------|-----|

| PIC16(L)F707  | (1)              | 8192                            | 363                  | 0                                      | 36                   | 14             | 32            | 4/2                  | 1      | 1                          | 2   | I                    | Y   |

| PIC16(L)F720  | (2)              | 2048                            | 128                  | 128                                    | 18                   | 12             | _             | 2/1                  | 1      | 1                          | 1   | I                    | Y   |

| PIC16(L)F721  | (2)              | 4096                            | 256                  | 128                                    | 18                   | 12             | _             | 2/1                  | 1      | 1                          | 1   | I                    | Y   |

| PIC16(L)F722  | (4)              | 2048                            | 128                  | 0                                      | 25                   | 11             | 8             | 2/1                  | 1      | 1                          | 2   | I                    | Y   |

| PIC16(L)F722A | (3)              | 2048                            | 128                  | 0                                      | 25                   | 11             | 8             | 2/1                  | 1      | 1                          | 2   | I                    | Y   |

| PIC16(L)F723  | (4)              | 4096                            | 192                  | 0                                      | 25                   | 11             | 8             | 2/1                  | 1      | 1                          | 2   | I                    | Y   |

| PIC16(L)F723A | (3)              | 4096                            | 192                  | 0                                      | 25                   | 11             | 8             | 2/1                  | 1      | 1                          | 2   | I                    | Y   |

| PIC16(L)F724  | (4)              | 4096                            | 192                  | 0                                      | 36                   | 14             | 16            | 2/1                  | 1      | 1                          | 2   | I                    | Y   |

| PIC16(L)F726  | (4)              | 8192                            | 368                  | 0                                      | 25                   | 11             | 8             | 2/1                  | 1      | 1                          | 2   | I                    | Y   |

| PIC16(L)F727  | (4)              | 8192                            | 368                  | 0                                      | 36                   | 14             | 16            | 2/1                  | 1      | 1                          | 2   | I                    | Y   |

**Note 1:** I - Debugging, Integrated on Chip; H - Debugging, Requires Debug Header.

2: One pin is input-only.

Data Sheet Index: (Unshaded devices are described in this document.)

- 1: DS41418 PIC16(L)F707 Data Sheet, 40/44-Pin Flash, 8-bit Microcontrollers

- 2: DS41430 PIC16(L)F720/721 Data Sheet, 20-Pin Flash, 8-bit Microcontrollers

- 3: DS41417 PIC16(L)F722A/723A Data Sheet, 28-Pin Flash, 8-bit Microcontrollers

- 4: DS41341 PIC16(L)F72X Data Sheet, 28/40/44-Pin Flash, 8-bit Microcontrollers

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS3000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

## 1.0 DEVICE OVERVIEW

The PIC16(L)F722A/723A devices are covered by this data sheet. They are available in 28-pin packages. Figure 1-1 shows a block diagram of the PIC16(L)F722A/723A devices. Table 1-1 shows the pinout descriptions.

| Address               | Name                  | Bit 7         | Bit 6                     | Bit 5                     | Bit 4         | Bit 3                 | Bit 2        | Bit 1          | Bit 0    | Value on:<br>POR, BOR | Page   |  |

|-----------------------|-----------------------|---------------|---------------------------|---------------------------|---------------|-----------------------|--------------|----------------|----------|-----------------------|--------|--|

| Bank 1                |                       |               |                           |                           |               |                       |              |                |          |                       |        |  |

| 80h <sup>(2)</sup>    | INDF                  | Addressing    | this location             | uses conter               | nts of FSR to | address data          | a memory (no | t a physical r | egister) | xxxx xxxx             | 22,30  |  |

| 81h                   | OPTION_REG            | RBPU          | INTEDG                    | TOCS                      | TOSE          | PSA                   | PS2          | PS1            | PS0      | 1111 1111             | 19,30  |  |

| 82h <sup>(2)</sup>    | PCL                   | Program Co    | ounter (PC) L             | east Signifie             | cant Byte     |                       |              |                |          | 0000 0000             | 21,30  |  |

| 83h <sup>(2)</sup>    | STATUS                | IRP           | RP1                       | RP0                       | TO            | PD                    | Z            | DC             | С        | 0001 1xxx             | 18,30  |  |

| 84h <sup>(2)</sup>    | FSR                   | Indirect Data | a Memory A                | ddress Point              | ter           |                       |              |                |          | xxxx xxxx             | 22,30  |  |

| 85h                   | TRISA                 | TRISA7        | TRISA6                    | TRISA5                    | 1111 1111     | 43,30                 |              |                |          |                       |        |  |

| 86h                   | TRISB                 | TRISB7        | TRISB6                    | TRISB5                    | TRISB4        | TRISB3                | TRISB2       | TRISB1         | TRISB0   | 1111 1111             | 52,30  |  |

| 87h                   | TRISC                 | TRISC7        | TRISC6                    | TRISC5                    | TRISC4        | TRISC3                | TRISC2       | TRISC1         | TRISC0   | 1111 1111             | 62,30  |  |

| 89h                   | TRISE                 | _             |                           |                           | _             | TRISE3 <sup>(5)</sup> | _            | _              | _        | 1111                  | 69,30  |  |

| 8Ah <sup>(1, 2)</sup> | PCLATH                | _             |                           |                           |               |                       |              |                |          | 0 0000                | 21,30  |  |

| 8Bh <sup>(2)</sup>    | INTCON                | GIE           | PEIE                      | TOIE                      | INTE          | RBIE                  | T0IF         | INTF           | RBIF     | x000 000x             | 36,30  |  |

| 8Ch                   | PIE1                  | TMR1GIE       | ADIE                      | RCIE                      | TXIE          | SSPIE                 | CCP1IE       | TMR2IE         | TMR1IE   | 0000 0000             | 37,31  |  |

| 8Dh                   | PIE2                  | —             | -                         | -                         | —             | —                     | _            | —              | CCP2IE   | 0                     | 38,31  |  |

| 8Eh                   | PCON                  | _             |                           | -                         | _             | _                     | _            | POR            | BOR      | dd                    | 20,31  |  |

| 8Fh                   | T1GCON                | TMR1GE        | T1GPOL                    | T1GTM                     | T1GSPM        | T1GGO<br>DONE         | T1GVAL       | T1GSS1         | T1GSS0   | 0000 0x00             | 104,31 |  |

| 90h                   | OSCCON                | —             | -                         | IRCF1                     | IRCF0         | ICSL                  | ICSS         | —              | _        | 10 qq                 | 73,31  |  |

| 91h                   | OSCTUNE               | —             |                           | TUN5                      | TUN4          | TUN3                  | TUN2         | TUN1           | TUN0     | 00 0000               | 74,31  |  |

| 92h                   | PR2                   | Timer2 Peri   | od Register               |                           |               |                       |              |                |          | 1111 1111             | 106,31 |  |

| 93h                   | SSPADD(4)             | Synchronou    | s Serial Port             | t (I <sup>2</sup> C mode) | Address Reg   | ister                 |              |                |          | 0000 0000             | 155,31 |  |

| 93h                   | SSPMSK <sup>(3)</sup> | Synchronou    | s Serial Port             | t (I <sup>2</sup> C mode) | Address Mas   | k Register            |              |                |          | 1111 1111             | 166,31 |  |

| 94h                   | SSPSTAT               | SMP           | CKE                       | D/A                       | Р             | S                     | R/W          | UA             | BF       | 0000 0000             | 153,31 |  |

| 95h                   | WPUB                  | WPUB7         | WPUB6                     | WPUB5                     | WPUB4         | WPUB3                 | WPUB2        | WPUB1          | WPUB0    | 1111 1111             | 52,31  |  |

| 96h                   | IOCB                  | IOCB7         | IOCB6                     | IOCB5                     | IOCB4         | IOCB3                 | IOCB2        | IOCB1          | IOCB0    | 0000 0000             | 53,31  |  |

| 97h                   |                       | Unimpleme     | nted                      |                           |               |                       |              |                |          | _                     |        |  |

| 98h                   | TXSTA                 | CSRC          | TX9                       | TXEN                      | SYNC          | _                     | BRGH         | TRMT           | TX9D     | 0000 -010             | 133,31 |  |

| 99h                   | SPBRG                 | BRG7          | BRG6                      | BRG5                      | BRG4          | BRG3                  | BRG2         | BRG1           | BRG0     | 0000 0000             | 135,31 |  |

| 9Ah                   | _                     | Unimpleme     | nted                      |                           |               |                       |              |                |          | —                     | —      |  |

| 9Bh                   | —                     | Unimpleme     | nted                      |                           |               |                       |              |                |          | _                     | _      |  |

| 9Ch                   | APFCON                | _             | — — — — — — SSSEL CCP2SEL |                           |               |                       |              |                |          |                       |        |  |

| 9Dh                   | FVRCON                | FVRRDY        | FVREN                     | —                         | _             | _                     | _            | ADFVR1         | ADFVR0   | q000                  | 90,31  |  |

| 9Eh                   | —                     | Unimpleme     | nted                      |                           |               |                       |              |                |          | _                     | —      |  |

| 9Fh                   | ADCON1                | _             | ADCS2                     | ADCS1                     | ADCS0         | _                     | _            | ADREF1         | ADREF0   | 000000                | 86,31  |  |

## TABLE 2-1:PIC16(L)F722A/723A SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved.

Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter.

**2:** These registers can be addressed from any bank.

3: Accessible only when SSPM<3:0> = 1001.

4: Accessible only when SSPM<3:0>  $\neq$  1001.

5: This bit is always '1' as RE3 is input-only.

| R/W-x                          | R/W-x | R/W-x        | R/W-x | R/W-x        | R/W-x            | R/W-x  | R/W-x |  |  |  |  |

|--------------------------------|-------|--------------|-------|--------------|------------------|--------|-------|--|--|--|--|

| RB7                            | RB6   | RB5          | RB4   | RB3          | RB2              | RB1    | RB0   |  |  |  |  |

| bit 7 bit 0                    |       |              |       |              |                  |        |       |  |  |  |  |

|                                |       |              |       |              |                  |        |       |  |  |  |  |

|                                |       |              |       |              |                  |        |       |  |  |  |  |

| Legend:                        |       |              |       |              |                  |        |       |  |  |  |  |

| <b>Legend:</b><br>R = Readable | bit   | W = Writable | bit   | U = Unimplen | nented bit, read | as '0' |       |  |  |  |  |

## REGISTER 6-5: PORTB: PORTB REGISTER

bit 7-0 RB<7:0>: PORTB I/O Pin bits

1 = Port pin is > VIH

0 = Port pin is < VIL

## REGISTER 6-6: TRISB: PORTB TRI-STATE REGISTER

| R/W-1  | R/W-1 R/W-1                       |  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|--------|-----------------------------------|--|--------|--------|--------|--------|--------|

| TRISB7 | TRISB7 TRISB6 TRISB5 <sup>-</sup> |  | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 |

| bit 7  |                                   |  |        |        |        |        | bit 0  |

| Legend:           |                                                        |                      |                    |  |  |

|-------------------|--------------------------------------------------------|----------------------|--------------------|--|--|

| R = Readable bit  | it W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                       | '0' = Bit is cleared | x = Bit is unknown |  |  |

bit 7-0

**—**

TRISB<7:0>: PORTB Tri-State Control bits

1 = PORTB pin configured as an input (tri-stated)

0 = PORTB pin configured as an output

## REGISTER 6-7: WPUB: WEAK PULL-UP PORTB REGISTER

| R/W-1 | R/W-1             | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-------------------|-------|-------|-------|-------|-------|-------|

| WPUB7 | WPUB7 WPUB6 WPUB5 |       | WPUB4 | WPUB3 | WPUB2 | WPUB1 | WPUB0 |

| bit 7 |                   |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 **WPUB<7:0>**: Weak Pull-up Register bits

1 = Pull up enabled

0 = Pull up disabled

**Note 1:** Global RBPU bit of the OPTION register must be cleared for individual pull ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is in configured as an output.

| IADLE 0-3. | SOMMARY OF REGISTERS ASSOCIATED WITH ORTD |        |        |        |                         |         |             |         |                     |  |  |  |

|------------|-------------------------------------------|--------|--------|--------|-------------------------|---------|-------------|---------|---------------------|--|--|--|

| Name       | ne Bit 7 Bit 6 Bit 5                      |        | Bit 5  | Bit 4  | Bit 3                   | Bit 2   | Bit 1       | Bit 0   | Register<br>on Page |  |  |  |

| ADCON0     |                                           |        | CHS3   | CHS2   | CHS1                    | CHS0    | GO/<br>DONE | ADON    | 85                  |  |  |  |

| ANSELB     | _                                         | _      | ANSB5  | ANSB4  | ANSB3                   | ANSB2   | ANSB1       | ANSB0   | 53                  |  |  |  |

| APFCON     | _                                         | —      | —      | —      | _                       | —       | SSSEL       | CCP2SEL | 42                  |  |  |  |

| CCP2CON    | _                                         | _      | DC2B1  | DC2B0  | CCP2M3                  | CCP2M2  | CCP2M1      | CCP2M0  | 115                 |  |  |  |

| CPSCON0    | CPSON                                     | _      | —      | —      | CPSRNG1                 | CPSRNG0 | CPSOUT      | T0XCS   | 112                 |  |  |  |

| CPSCON1    | _                                         | —      | —      | —      | _                       | CPSCH2  | CPSCH1      | CPSCH0  | 113                 |  |  |  |

| INTCON     | GIE                                       | PEIE   | TOIE   | INTE   | RBIE                    | T0IF    | INTF        | RBIF    | 36                  |  |  |  |

| IOCB       | IOCB7                                     | IOCB6  | IOCB5  | IOCB4  | IOCB3                   | IOCB2   | IOCB1       | IOCB0   | 53                  |  |  |  |

| OPTION_REG | RBPU                                      | INTEDG | T0CS   | TOSE   | PSA                     | PS2     | PS1         | PS0     | 19                  |  |  |  |

| PORTB      | RB7                                       | RB6    | RB5    | RB4    | RB3                     | RB2     | RB1         | RB0     | 52                  |  |  |  |

| T1GCON     | TMR1GE                                    | T1GPOL | T1GTM  | T1GSPM | T <u>1GGO</u> /<br>DONE | T1GVAL  | T1GSS1      | T1GSS0  | 104                 |  |  |  |

| TRISB      | TRISB7                                    | TRISB6 | TRISB5 | TRISB4 | TRISB3                  | TRISB2  | TRISB1      | TRISB0  | 52                  |  |  |  |

| WPUB       | WPUB7                                     | WPUB6  | WPUB5  | WPUB4  | WPUB3                   | WPUB2   | WPUB1       | WPUB0   | 52                  |  |  |  |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTB.

## 6.4.1 RC0/T1OSO/T1CKI

Figure 6-13 shows the diagram for this pin. This pin is configurable to function as one of the following:

- General purpose I/O

- Timer1 oscillator output

- Timer1 clock input

## 6.4.2 RC1/T1OSI/CCP2

Figure 6-14 shows the diagram for this pin. This pin is configurable to function as one of the following:

- General purpose I/O

- Timer1 oscillator input

- Capture 2 input, Compare 2 output, and PWM2 output

Note: CCP2 pin location may be selected as RB3 or RC1.

## 6.4.3 RC2/CCP1

Figure 6-15 shows the diagram for this pin. This pin is configurable to function as one of the following:

- General purpose I/O

- Capture 1 input, Compare 1 output, and PWM1 output

## 6.4.4 RC3/SCK/SCL

Figure 6-16 shows the diagram for this pin. This pin is configurable to function as one of the following:

- General purpose I/O

- SPI clock

- I<sup>2</sup>C clock

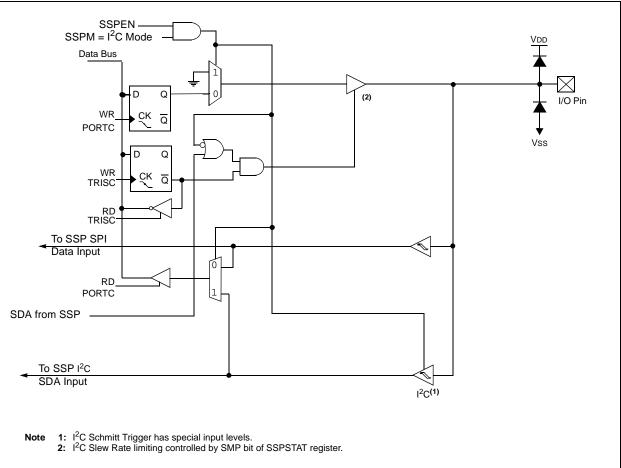

## 6.4.5 RC4/SDI/SDA

Figure 6-17 shows the diagram for this pin. This pin is configurable to function as one of the following:

- General purpose I/O

- SPI data input

- I<sup>2</sup>C data I/O

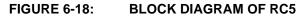

## 6.4.6 RC5/SDO

Figure 6-18 shows the diagram for this pin. This pin is configurable to function as one of the following:

- General purpose I/O

- SPI data output

## 6.4.7 RC6/TX/CK

Figure 6-19 shows the diagram for this pin. This pin is configurable to function as one of the following:

- General purpose I/O

- Asynchronous serial output

- Synchronous clock I/O

## 6.4.8 RC7/RX/DT

Figure 6-20 shows the diagram for this pin. This pin is configurable to function as one of the following:

- General purpose I/O

- · Asynchronous serial input

- Synchronous serial data I/O

## FIGURE 6-17: BLOCK DIAGRAM OF RC4

## 9.2.6 A/D CONVERSION PROCEDURE

This is an example procedure for using the ADC to perform an Analog-to-Digital conversion:

- 1. Configure Port:

- Disable pin output driver (Refer to the TRIS register)

- Configure pin as analog (Refer to the ANSEL register)

- 2. Configure the ADC module:

- Select ADC conversion clock

- Configure voltage reference

- Select ADC input channel

- Turn on ADC module

- 3. Configure ADC interrupt (optional):

- Clear ADC interrupt flag

- Enable ADC interrupt

- Enable peripheral interrupt

- Enable global interrupt<sup>(1)</sup>

- 4. Wait the required acquisition time<sup>(2)</sup>.

- 5. Start conversion by setting the GO/DONE bit.

- 6. Wait for ADC conversion to complete by one of the following:

- Polling the GO/DONE bit

- Waiting for the ADC interrupt (interrupts enabled)

- 7. Read ADC Result.

- 8. Clear the ADC interrupt flag (required if interrupt is enabled).

- Note 1: The global interrupt can be disabled if the user is attempting to wake-up from Sleep and resume in-line code execution.

- 2: Refer to Section 9.3 "A/D Acquisition Requirements".

## EXAMPLE 9-1: A/D CONVERSION

;This code block configures the ADC ;for polling, Vdd reference, Frc clock ;and ANO input. ;

;Conversion start & polling for completion ; are included.

| ;       |             |                      |

|---------|-------------|----------------------|

| BANKSEL | ADCON1      | ;                    |

| MOVLW   | B'01110000' | ;ADC Frc clock,      |

|         |             | ;VDD reference       |

| MOVWF   | ADCON1      | ;                    |

| BANKSEL | TRISA       | ;                    |

| BSF     | TRISA,0     | ;Set RA0 to input    |

| BANKSEL | ANSELA      | ;                    |

| BSF     | ANSELA,0    | ;Set RA0 to analog   |

| BANKSEL | ADCON0      | ;                    |

| MOVLW   | B'0000001'  | ;AN0, On             |

| MOVWF   | ADCON0      | ;                    |

| CALL    | SampleTime  | ;Acquisiton delay    |

| BSF     | ADCON0,GO   | ;Start conversion    |

| BTFSC   | ADCON0,GO   | ;Is conversion done? |

| GOTO    | \$-1        | ;No, test again      |

| BANKSEL | ADRES       | ;                    |

| MOVF    | ADRES,W     | ;Read result         |

| MOVWF   | RESULT      | ;store in GPR space  |

|         |             |                      |

## 16.0 ADDRESSABLE UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (AUSART)

The Addressable Universal Synchronous Asynchronous Receiver Transmitter (AUSART) module is a serial I/O communications peripheral. It contains all the clock generators, shift registers and data buffers necessary to perform an input or output serial data transfer independent of device program execution. The AUSART, also known as a Serial Communications Interface (SCI), can be configured as a full-duplex asynchronous system or half-duplex synchronous system. Full-Duplex mode is useful for communications with peripheral systems, such as CRT terminals and personal computers. Half-Duplex Synchronous mode is intended for communications with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs or other microcontrollers. These devices typically do not have internal clocks for baud rate generation and require the external clock signal provided by a master synchronous device.

The AUSART module includes the following capabilities:

- Full-duplex asynchronous transmit and receive

- Two-character input buffer

- One-character output buffer

- Programmable 8-bit or 9-bit character length

- Address detection in 9-bit mode

- Input buffer overrun error detection

- Received character framing error detection

- Half-duplex synchronous master

- Half-duplex synchronous slave

- Sleep operation

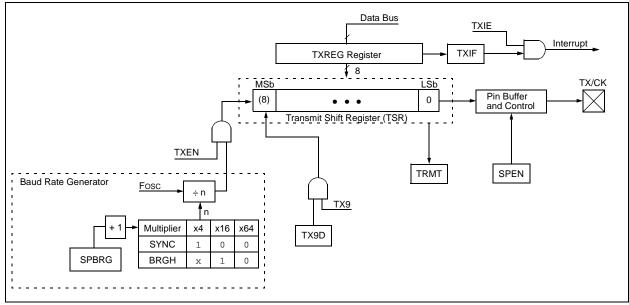

Block diagrams of the AUSART transmitter and receiver are shown in Figure 16-1 and Figure 16-2.

## FIGURE 16-1: AUSART TRANSMIT BLOCK DIAGRAM

## 16.1.2.8 Asynchronous Reception Setup:

- Initialize the SPBRG register and the BRGH bit to achieve the desired baud rate (refer to Section 16.2 "AUSART Baud Rate Generator (BRG)").

- 2. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 3. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. If 9-bit reception is desired, set the RX9 bit.

- 5. Enable reception by setting the CREN bit.

- 6. The RCIF interrupt flag bit of the PIR1 register will be set when a character is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE bit of the PIE1 register was also set.

- 7. Read the RCSTA register to get the error flags and, if 9-bit data reception is enabled, the ninth data bit.

- 8. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register.

- 9. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

## 16.1.2.9 9-bit Address Detection Mode Setup

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- Initialize the SPBRG register and the BRGH bit to achieve the desired baud rate (refer to Section 16.2 "AUSART Baud Rate Generator (BRG)").

- 2. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 3. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. Enable 9-bit reception by setting the RX9 bit.

- 5. Enable address detection by setting the ADDEN bit.

- 6. Enable reception by setting the CREN bit.

- 7. The RCIF interrupt flag bit of the PIR1 register will be set when a character with the ninth bit set is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit of the PIE1 register was also set.

- 8. Read the RCSTA register to get the error flags. The ninth data bit will always be set.

- 9. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register. Software determines if this is the device's address.

- 10. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

- 11. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and generate interrupts.

#### **FIGURE 16-5: ASYNCHRONOUS RECEPTION** Start Start Star bit 7/8/ Stop Stop RX/DT pin bit ΄bit 0 🗙 bit 1 (bit 7/8/ bit 7/8/ Stop bit bit bit 0 bit bit Rcv Shift Reg → Rcv Buffer Reg Word 2 RCREG Word 1 RCREG Read Rcv Buffer Reg RCREG RCIF (Interrupt Flag) OFRR bit CREN This timing diagram shows three words appearing on the RX input. The RCREG (receive buffer) is read after the third word, Note: causing the OERR (overrun) bit to be set.

|        |                | <b>SYNC</b> = 0, <b>BRGH</b> = 0 |                             |                |           |       |                |            |                             |                |            |                             |  |

|--------|----------------|----------------------------------|-----------------------------|----------------|-----------|-------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|--|

| BAUD   | Fosc           | ; = 20.00                        | 0 MHz                       | Fosc           | : = 18.43 | 2 MHz | Fosc           | = 16.000   | 00 MHz                      | Fosc           | = 11.059   | 92 MHz                      |  |

| RATE   | Actual<br>Rate | %<br>Error                       | SPBRG<br>value<br>(decimal) | Actual<br>Rate | va        |       | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |  |

| 300    |                | _                                | _                           |                | _         | _     | —              | —          | —                           |                | _          | _                           |  |

| 1200   | 1221           | 1.73                             | 255                         | 1200           | 0.00      | 239   | 1201           | 0.08       | 207                         | 1200           | 0.00       | 143                         |  |

| 2400   | 2404           | 0.16                             | 129                         | 2400           | 0.00      | 119   | 2403           | 0.16       | 103                         | 2400           | 0.00       | 71                          |  |

| 9600   | 9470           | -1.36                            | 32                          | 9600           | 0.00      | 29    | 9615           | 0.16       | 25                          | 9600           | 0.00       | 17                          |  |

| 10417  | 10417          | 0.00                             | 29                          | 10286          | -1.26     | 27    | 10416          | -0.01      | 23                          | 10165          | -2.42      | 16                          |  |

| 19.2k  | 19.53k         | 1.73                             | 15                          | 19.20k         | 0.00      | 14    | 19.23k         | 0.16       | 12                          | 19.20k         | 0.00       | 8                           |  |

| 57.6k  | —              | —                                | _                           | 57.60k         | 0.00      | 7     | —              | —          | _                           | 57.60k         | 0.00       | 2                           |  |

| 115.2k | —              | _                                | —                           | _              | _         | —     | _              | —          | —                           | —              | —          | —                           |  |

## TABLE 16-5: BAUD RATES FOR ASYNCHRONOUS MODES

|        |                  |            |                             |                  |            | SYNC = 0,                   | BRGH = 0          | )          |                             |                  |            |                             |

|--------|------------------|------------|-----------------------------|------------------|------------|-----------------------------|-------------------|------------|-----------------------------|------------------|------------|-----------------------------|

| BAUD   | Fosc = 8.000 MHz |            |                             | Fosc = 4.000 MHz |            |                             | Fosc = 3.6864 MHz |            |                             | Fosc = 1.000 MHz |            |                             |

| RATE   | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | _                | _          | _                           | 300              | 0.16       | 207                         | 300               | 0.00       | 191                         | 300              | 0.16       | 51                          |

| 1200   | 1202             | 0.16       | 103                         | 1202             | 0.16       | 51                          | 1200              | 0.00       | 47                          | 1202             | 0.16       | 12                          |

| 2400   | 2404             | 0.16       | 51                          | 2404             | 0.16       | 25                          | 2400              | 0.00       | 23                          | —                | _          | _                           |

| 9600   | 9615             | 0.16       | 12                          | —                | _          | _                           | 9600              | 0.00       | 5                           | —                | _          | _                           |

| 10417  | 10417            | 0.00       | 11                          | 10417            | 0.00       | 5                           | —                 | _          | _                           | —                | _          | _                           |

| 19.2k  | —                | _          | _                           | —                | _          | _                           | 19.20k            | 0.00       | 2                           | —                | _          | _                           |

| 57.6k  | —                | _          | —                           | —                | —          | —                           | 57.60k            | 0.00       | 0                           | —                | _          | —                           |

| 115.2k |                  | —          | —                           |                  | _          | —                           |                   | _          | —                           |                  | —          | —                           |

|        |                   |            |                             |                |            | SYNC = 0,                   | BRGH = 2       | L          |                             |                |            |                             |

|--------|-------------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Fosc = 20.000 MHz |            | Fosc = 18.432 MHz           |                |            | Fosc = 16.0000 MHz          |                |            | Fosc = 11.0592 MHz          |                |            |                             |

| RATE   | Actual<br>Rate    | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | —                 |            | _                           |                |            | _                           | _              | —          | —                           | —              | —          | _                           |

| 1200   | —                 | —          | —                           | —              | —          | —                           | —              | —          | —                           | —              | —          | —                           |

| 2400   | —                 | _          | _                           | _              | _          | _                           | _              | _          | —                           | —              | —          | _                           |

| 9600   | 9615              | 0.16       | 129                         | 9600           | 0.00       | 119                         | 9615           | 0.16       | 103                         | 9600           | 0.00       | 71                          |

| 10417  | 10417             | 0.00       | 119                         | 10378          | -0.37      | 110                         | 10417          | 0.00       | 95                          | 10473          | 0.53       | 65                          |

| 19.2k  | 19.23k            | 0.16       | 64                          | 19.20k         | 0.00       | 59                          | 19.23k         | 0.16       | 51                          | 19.20k         | 0.00       | 35                          |

| 57.6k  | 56.82k            | -1.36      | 21                          | 57.60k         | 0.00       | 19                          | 58.8k          | 2.12       | 16                          | 57.60k         | 0.00       | 11                          |

| 115.2k | 113.64k           | -1.36      | 10                          | 115.2k         | 0.00       | 9                           | —              | _          | _                           | 115.2k         | 0.00       | 5                           |

|        |                  |            |                             | _              |            | <b>SYNC</b> = 0,            | BRGH = 1       | 1          |                             |                |            |                             |

|--------|------------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|

| BAUD   | Fosc = 8.000 MHz |            | Fosc = 4.000 MHz            |                |            | Fosc = 3.6864 MHz           |                |            | Fosc = 1.000 MHz            |                |            |                             |

| RATE   | Actual<br>Rate   | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300    | —                |            | —                           | _              | _          | _                           |                | _          | _                           | 300            | 0.16       | 207                         |

| 1200   | —                | —          | —                           | 1202           | 0.16       | 207                         | 1200           | 0.00       | 191                         | 1202           | 0.16       | 51                          |

| 2400   | 2404             | 0.16       | 207                         | 2404           | 0.16       | 103                         | 2400           | 0.00       | 95                          | 2404           | 0.16       | 25                          |

| 9600   | 9615             | 0.16       | 51                          | 9615           | 0.16       | 25                          | 9600           | 0.00       | 23                          | _              | _          | _                           |

| 10417  | 10417            | 0.00       | 47                          | 10417          | 0.00       | 23                          | 10473          | 0.53       | 21                          | 10417          | 0.00       | 5                           |

| 19.2k  | 19231            | 0.16       | 25                          | 19.23k         | 0.16       | 12                          | 19.2k          | 0.00       | 11                          | —              | _          | _                           |

| 57.6k  | 55556            | -3.55      | 8                           | —              | _          | _                           | 57.60k         | 0.00       | 3                           | —              | _          | _                           |

| 115.2k | _                | —          | _                           | _              | —          | —                           | 115.2k         | 0.00       | 1                           | _              | —          | _                           |

## TABLE 16-5: BAUD RATES FOR ASYNCHRONOUS MODES

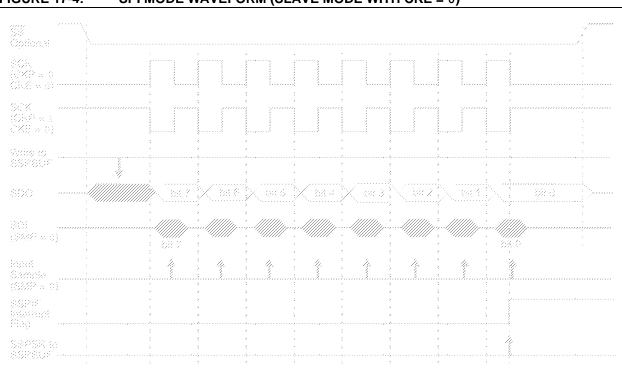

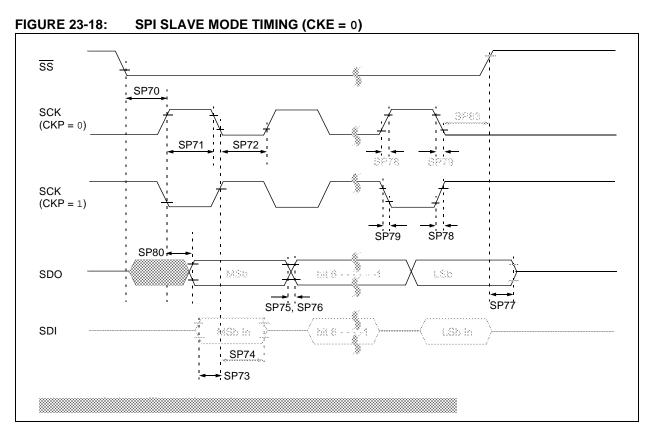

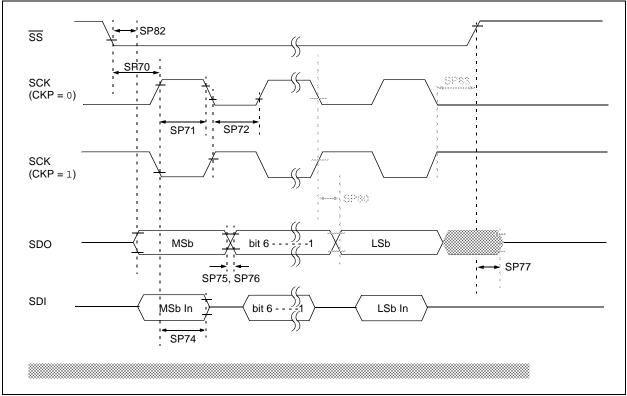

## FIGURE 17-4: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 0)

#### SS SCK (CKP = 0 $\dot{C}KE = 1)$ SCK (CKP = 1 CKE = 1) Write to SSPBUF bit 6 bit 5 bit 4 bit 2 bit 1 bit 0 SDO bit '7 bit 3 ï SDI (SMP = 0)I bit 0 bit 7 Input Sample (SMP = 0)SSPIF Interrupt Flag SSPSR to SSPBUF 1 . i . . . .

## FIGURE 17-5: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

| REGISTER 17-5: | SSPMSK: SSP MASK REGISTER |

|----------------|---------------------------|

|                |                           |

| R/W-1 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| MSK7  | MSK6  | MSK5  | MSK4  | MSK3  | MSK2  | MSK1  | MSK0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-1 | MSK<7:1>: Mask bits  |

|---------|----------------------|

|         | 1 - The received add |

| 1 = The received address bit n is compared to SSPADD <n> to detect I</n>            |   |

|-------------------------------------------------------------------------------------|---|

| 0 = The received address bit n is not used to detect I <sup>2</sup> C address match | ۱ |

## bit 0 MSK<0>: Mask bit for I<sup>2</sup>C Slave Mode, 10-bit Address

I<sup>2</sup>C Slave Mode, 10-bit Address (SSPM<3:0> = 0111):

1 = The received address bit '0' is compared to SSPADD<0> to detect  $I^2C$  address match

0 = The received address bit '0' is not used to detect I<sup>2</sup>C address match

All other SSP modes: this bit has no effect.

## REGISTER 17-6: SSPADD: SSP I<sup>2</sup>C ADDRESS REGISTER

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| ADD7  | ADD6  | ADD5  | ADD4  | ADD3  | ADD2  | ADD1  | ADD0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

|       |       |       |       |       |       |       |       |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 7-0 ADD<7:0>: Address bits Received address

## TABLE 17-7: SUMMARY OF REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

| Name                  | Bit 7                                                                                       | Bit 6              | Bit 5                    | Bit 4        | Bit 3    | Bit 2  | Bit 1  | Bit 0  | Register on<br>Page |

|-----------------------|---------------------------------------------------------------------------------------------|--------------------|--------------------------|--------------|----------|--------|--------|--------|---------------------|

| INTCON                | GIE                                                                                         | PEIE               | TOIE                     | INTE         | RBIE     | TOIF   | INTF   | RBIF   | 36                  |

| PIR1                  | TMR1GIF                                                                                     | ADIF               | RCIF                     | TXIF         | SSPIF    | CCP1IF | TMR2IF | TMR1IF | 39                  |

| PIE1                  | TMR1GIE                                                                                     | ADIE               | RCIE                     | TXIE         | SSPIE    | CCP1IE | TMR2IE | TMR1IE | 37                  |

| SSPBUF                | SPBUF Synchronous Serial Port Receive Buffer/Transmit Register                              |                    |                          |              |          |        |        |        | 147                 |

| SSPADD                | Synchronous                                                                                 | Serial Por         | t (I <sup>2</sup> C mode | e) Address F | Register |        |        |        | 155                 |

| SSPCON                | WCOL                                                                                        | SSPOV              | SSPEN                    | CKP          | SSPM3    | SSPM2  | SSPM1  | SSPM0  | 164                 |

| SSPMSK <sup>(2)</sup> | SSPMSK <sup>(2)</sup> Synchronous Serial Port (I <sup>2</sup> C mode) Address Mask Register |                    |                          |              |          |        |        |        | 166                 |

| SSPSTAT               | SMP <sup>(1)</sup>                                                                          | CKE <sup>(1)</sup> | D/Ā                      | Р            | S        | R/W    | UA     | BF     | 165                 |

| TRISC                 | TRISC7                                                                                      | TRISC6             | TRISC5                   | TRISC4       | TRISC3   | TRISC2 | TRISC1 | TRISC0 | 62                  |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by SSP module in I<sup>2</sup>C mode.

**Note 1:** Maintain these bits clear in  $I^2C$  mode.

**2:** Accessible only when SSPM < 3:0 > = 1001.

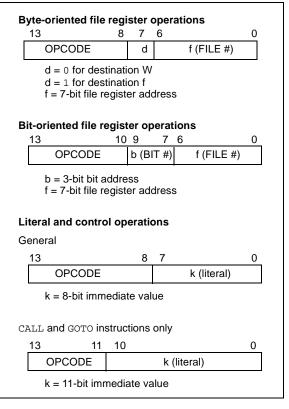

## 21.0 INSTRUCTION SET SUMMARY

The PIC16(L)F722A/723A instruction set is highly orthogonal and is comprised of three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

Each PIC16 instruction is a 14-bit word divided into an **opcode**, which specifies the instruction type and one or more **operands**, which further specify the operation of the instruction. The formats for each of the categories is presented in Figure 21-1, while the various opcode fields are summarized in Table 21-1.

Table 21-2 lists the instructions recognized by the MPASM<sup>TM</sup> assembler.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator, which selects the bit affected by the operation, while 'f' represents the address of the file in which the bit is located.

For **literal and control** operations, 'k' represents an 8bit or 11-bit constant, or literal value.

One instruction cycle consists of four oscillator periods; for an oscillator frequency of 4 MHz, this gives a nominal instruction execution time of 1  $\mu$ s. All instructions are executed within a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of an instruction. When this occurs, the execution takes two instruction cycles, with the second cycle executed as a NOP.

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

## 21.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

For example, a CLRF PORTB instruction will read PORTB, clear all the data bits, then write the result back to PORTB. This example would have the unintended consequence of clearing the condition that set the RBIF flag.

## TABLE 21-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                     |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                            |

| W     | Working register (accumulator)                                                                                                                                                  |

| b     | Bit address within an 8-bit file register                                                                                                                                       |

| k     | Literal field, constant data or label                                                                                                                                           |

| x     | Don't care location (= 0 or 1).<br>The assembler will generate code with $x = 0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; $d = 0$ : store result in W,<br>d = 1: store result in file register f.<br>Default is $d = 1$ .                                                             |

| PC    | Program Counter                                                                                                                                                                 |

| TO    | Time-out bit                                                                                                                                                                    |

| С     | Carry bit                                                                                                                                                                       |

| DC    | Digit carry bit                                                                                                                                                                 |

| Z     | Zero bit                                                                                                                                                                        |

| PD    | Power-down bit                                                                                                                                                                  |

## FIGURE 21-1: GENERAL FORMAT FOR INSTRUCTIONS

© 2010-2016 Microchip Technology Inc.

## 22.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

## 22.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

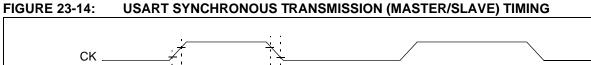

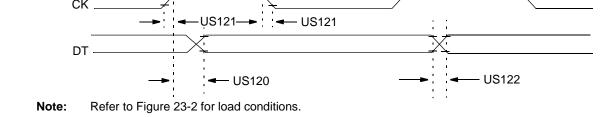

## TABLE 23-9: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |          |                                                              |          |      |      |       |            |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------|----------|------|------|-------|------------|--|--|--|--|

| Param.<br>No.                                                                                                        | Symbol   | Characteristic                                               |          | Min. | Max. | Units | Conditions |  |  |  |  |

| US120                                                                                                                | TCKH2DTV | SYNC XMIT (Master and Slave)<br>Clock high to data-out valid | 3.0-5.5V | _    | 80   | ns    |            |  |  |  |  |

|                                                                                                                      |          |                                                              | 1.8-5.5V |      | 100  | ns    |            |  |  |  |  |

| US121                                                                                                                | TCKRF    | Clock out rise time and fall time (Master mode)              | 3.0-5.5V | —    | 45   | ns    |            |  |  |  |  |

|                                                                                                                      |          |                                                              | 1.8-5.5V | —    | 50   | ns    |            |  |  |  |  |

| US122                                                                                                                | TDTRF    | Data-out rise time and fall time                             | 3.0-5.5V | —    | 45   | ns    |            |  |  |  |  |

|                                                                                                                      |          |                                                              | 1.8-5.5V | —    | 50   | ns    |            |  |  |  |  |

## FIGURE 23-15: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

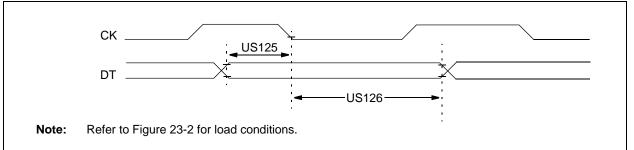

## TABLE 23-10: USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |          |                                                                                |      |      |       |            |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------------|------|------|-------|------------|--|--|--|--|

| Param.<br>No.                                                                                                        | Symbol   | Characteristic                                                                 | Min. | Max. | Units | Conditions |  |  |  |  |

| US125                                                                                                                | TDTV2CKL | SYNC RCV (Master and Slave)<br>Data-hold before CK $\downarrow$ (DT hold time) | 10   |      | ns    |            |  |  |  |  |

| US126                                                                                                                | TCKL2DTL | Data-hold after CK $\downarrow$ (DT hold time)                                 | 15   | _    | ns    |            |  |  |  |  |

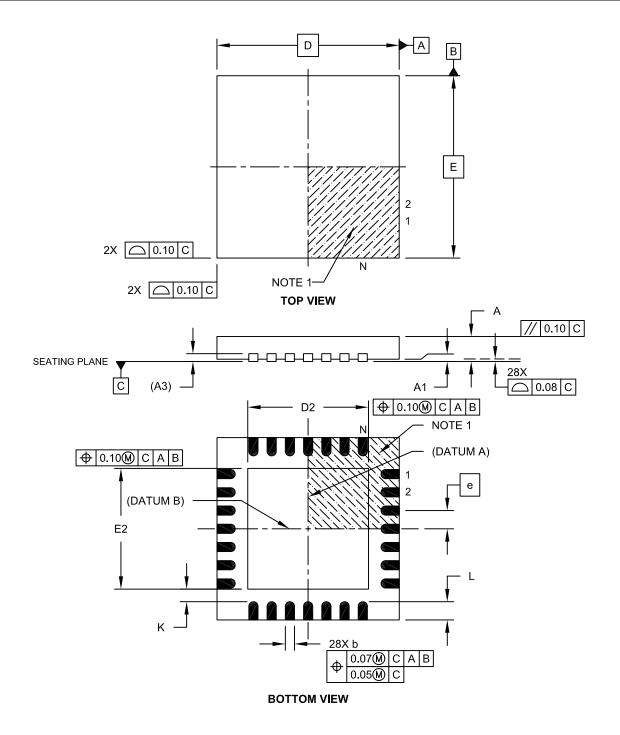

28-Lead Plastic Ultra Thin Quad Flat, No Lead Package (MV) – 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-152A Sheet 1 of 2