Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

|                            |                                                                            |

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 11x8b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-QFN (6x6)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf722a-i-ml |

#### 2.3 PCL and PCLATH

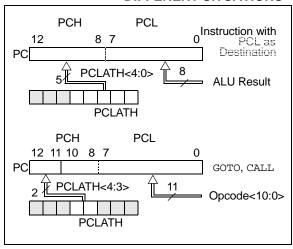

The Program Counter (PC) is 13 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<12:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 2-5 shows the two situations for the loading of the PC. The upper example in Figure 2-5 shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in Figure 2-5 shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

FIGURE 2-5: LOADING OF PC IN DIFFERENT SITUATIONS

#### 2.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When performing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to Application Note AN556, Implementing a Table Read (DS00556).

#### 2.3.2 STACK

All devices have an 8-level x 13-bit wide hardware stack (refer to Figures 2-1 and 2-2). The stack space is not part of either program or data space and the Stack Pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth PUSH overwrites the value that was stored from the first PUSH. The tenth PUSH overwrites the second PUSH (and so on).

- Note 1: There are no Status bits to indicate stack overflow or stack underflow conditions.

- 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions or the vectoring to an interrupt address.

## 2.4 Program Memory Paging

All devices are capable of addressing a continuous 8K word block of program memory. The CALL and GOTO instructions provide only 11 bits of address to allow branching within any 2K program memory page. When doing a CALL or GOTO instruction, the upper 2 bits of the address are provided by PCLATH<4:3>. When doing a CALL or GOTO instruction, the user must ensure that the page select bits are programmed so that the desired program memory page is addressed. If a return from a CALL instruction (or interrupt) is executed, the entire 13-bit PC is POPed off the stack. Therefore, manipulation of the PCLATH<4:3> bits is not required for the RETURN instructions (which POPs the address from the stack).

Note: The contents of the PCLATH register are unchanged after a RETURN or RETFIE instruction is executed. The user must rewrite the contents of the PCLATH register for any subsequent subroutine

Example 2-1 shows the calling of a subroutine in page 1 of the program memory. This example assumes that PCLATH is saved and restored by the Interrupt Service Routine (if interrupts are used).

calls or GOTO instructions.

# EXAMPLE 2-1: CALL OF A SUBROUTINE IN PAGE 1 FROM PAGE 0

```

ORG 500h

PAGESEL SUB_P1

;Select page 1

; (800h-FFFh)

CALL

SUB1_P1; Call subroutine in

;page 1 (800h-FFFh)

ORG

900h

;page 1 (800h-FFFh)

SUB1 P1

; called subroutine

;page 1 (800h-FFFh)

RETURN

;return to

;Call subroutine

;in page 0

; (000h-7FFh)

```

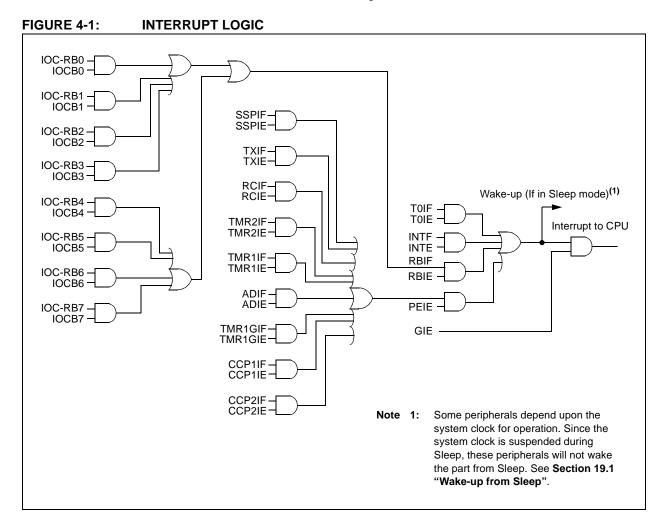

## 4.0 INTERRUPTS

The PIC16(L)F722A/723A device family features an interruptible core, allowing certain events to preempt normal program flow. An Interrupt Service Routine (ISR) is used to determine the source of the interrupt and act accordingly. Some interrupts can be configured to wake the MCU from Sleep mode.

The PIC16(L)F722A/723A device family has 12 interrupt sources, differentiated by corresponding interrupt enable and flag bits:

- Timer0 Overflow Interrupt

- External Edge Detect on INT Pin Interrupt

- PORTB Change Interrupt

- Timer1 Gate Interrupt

- A/D Conversion Complete Interrupt

- AUSART Receive Interrupt

- AUSART Transmit Interrupt

- SSP Event Interrupt

- CCP1 Event Interrupt

- Timer2 Match with PR2 Interrupt

- Timer1 Overflow Interrupt

- CCP2 Event Interrupt

A block diagram of the interrupt logic is shown in Figure 4-1.

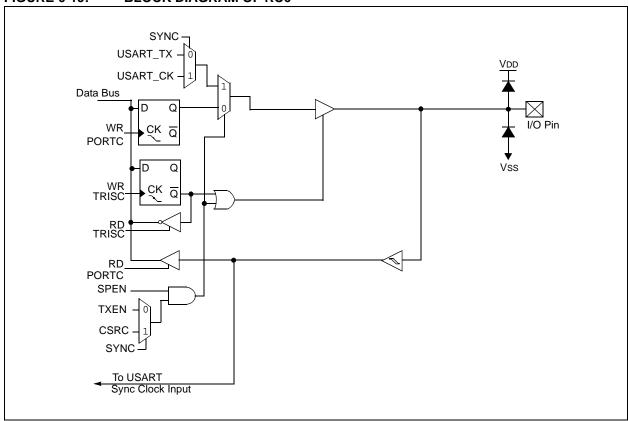

FIGURE 6-19: BLOCK DIAGRAM OF RC6

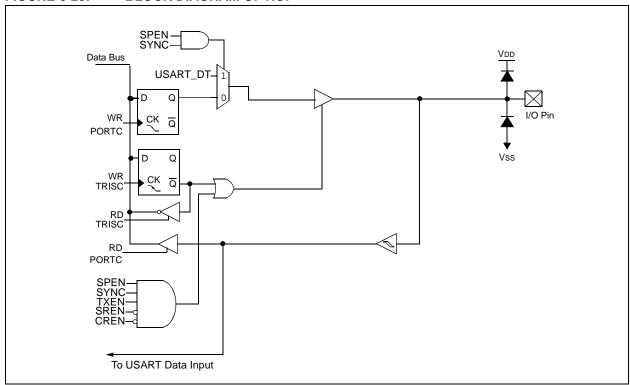

FIGURE 6-20: BLOCK DIAGRAM OF RC7

TABLE 6-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Name    | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0   | Register on Page |

|---------|---------|---------|---------|---------|---------|--------|--------|---------|------------------|

| APFCON  | _       | _       | _       | _       | _       | _      | SSSEL  | CCP2SEL | 42               |

| CCP1CON | _       | _       | DC1B1   | DC1B0   | CCP1M3  | CCP1M2 | CCP1M1 | CCP1M0  | 115              |

| CCP2CON | _       |         | DC2B1   | DC2B0   | CCP2M3  | CCP2M2 | CCP2M1 | CCP2M0  | 115              |

| PORTC   | RC7     | RC6     | RC5     | RC4     | RC3     | RC2    | RC1    | RC0     | 62               |

| RCSTA   | SPEN    | RX9     | SREN    | CREN    | ADDEN   | FERR   | OERR   | RX9D    | 134              |

| SSPCON  | WCOL    | SSPOV   | SSPEN   | CKP     | SSPM3   | SSPM2  | SSPM1  | SSPM0   | 152              |

| SSPSTAT | SMP     | CKE     | D/Ā     | Р       | S       | R/W    | UA     | BF      | 153              |

| T1CON   | TMR1CS1 | TMR1CS0 | T1CKPS1 | T1CKPS0 | T10SCEN | T1SYNC | -      | TMR10N  | 103              |

| TXSTA   | CSRC    | TX9     | TXEN    | SYNC    | _       | BRGH   | TRMT   | TX9D    | 133              |

| TRISC   | TRISC7  | TRISC6  | TRISC5  | TRISC4  | TRISC3  | TRISC2 | TRISC1 | TRISC0  | 62               |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTC.

# 7.5 Oscillator Tuning

The INTOSC is factory-calibrated but can be adjusted in software by writing to the OSCTUNE register (Register 7-2).

The default value of the OSCTUNE register is '0'. The value is a 6-bit two's complement number.

When the OSCTUNE register is modified, the INTOSC frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred.

## REGISTER 7-2: OSCTUNE: OSCILLATOR TUNING REGISTER

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| _     | _   | TUN5  | TUN4  | TUN3  | TUN2  | TUN1  | TUN0  |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 **TUN<5:0>:** Frequency Tuning bits

01 1111 = Maximum frequency

01 1110 =

•

.

00 0001 =

00 0000 = Oscillator module is running at the factory-calibrated frequency.

11 1111 =

•

Ī

10 0000 = Minimum frequency

#### 9.1.5 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital conversion. The ADC interrupt flag is the ADIF bit in the PIR1 register. The ADC interrupt enable is the ADIE bit in the PIE1 register. The ADIF bit must be cleared in software.

- **Note 1:** The ADIF bit is set at the completion of every conversion, regardless of whether or not the ADC interrupt is enabled.

- **2:** The ADC operates during Sleep only when the FRC oscillator is selected.

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake-up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake-up from Sleep and resume in-line code execution, the GIE and PEIE bits of the INTCON register must be disabled. If the GIE and PEIE bits of the INTCON register are enabled, execution will switch to the Interrupt Service Routine.

Please refer to **Section 9.1.5 "Interrupts"** for more information.

## 9.2 ADC Operation

#### 9.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/DONE bit of the ADCON0 register to a '1' will start the Analog-to-Digital conversion.

Note:

The GO/DONE bit should not be set in the same instruction that turns on the ADC. Refer to Section 9.2.6 "A/D Conversion Procedure".

### 9.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- Set the ADIF Interrupt Flag bit

- Update the ADRES register with new conversion result

#### 9.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRES register will be updated with the partially complete Analog-to-Digital conversion sample. Incomplete bits will match the last bit converted.

**Note:** A device Reset forces all registers to their Reset state. Thus, the ADC module is turned off and any pending conversion is terminated.

# 9.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC clock source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

### 9.2.5 SPECIAL EVENT TRIGGER

The Special Event Trigger of the CCP module allows periodic ADC measurements without software intervention. When this trigger occurs, the GO/DONE bit is set by hardware and the Timer1 counter resets to zero.

Using the Special Event Trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met.

Refer to **Section 15.0** "Capture/Compare/PWM (CCP) Module" for more information.

## REGISTER 11-1: OPTION\_REG: OPTION REGISTER

| R/W-1 | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|--------|-------|-------|-------|-------|-------|-------|

| RBPU  | INTEDG | T0CS  | T0SE  | PSA   | PS2   | PS1   | PS0   |

| bit 7 |        |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 RBPU: PORTB Pull-up Enable bit

1 = PORTB pull ups are disabled

0 = PORTB pull ups are enabled by individual PORT latch values

bit 6 **INTEDG:** Interrupt Edge Select bit

1 = Interrupt on rising edge of INT pin0 = Interrupt on falling edge of INT pin

bit 5 TOCS: TMR0 Clock Source Select bit

1 = Transition on T0CKI pin or CPSOSC signal 0 = Internal instruction cycle clock (Fosc/4)

bit 4 T0SE: TMR0 Source Edge Select bit

1 = Increment on high-to-low transition on T0CKI pin 0 = Increment on low-to-high transition on T0CKI pin

bit 3 **PSA:** Prescaler Assignment bit

1 = Prescaler is assigned to the WDT

0 = Prescaler is assigned to the Timer0 module

bit 2-0 **PS<2:0>:** Prescaler Rate Select bits

| BIT VALUE | TMR0 RATE | WDT RATE |

|-----------|-----------|----------|

| 000       | 1:2       | 1:1      |

| 001       | 1:4       | 1:2      |

| 010       | 1:8       | 1:4      |

| 011       | 1:16      | 1:8      |

| 100       | 1:32      | 1:16     |

| 101       | 1:64      | 1:32     |

| 110       | 1:128     | 1:64     |

| 111       | 1:256     | 1 : 128  |

#### TABLE 11-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMERO

| Name           | Bit 7                  | Bit 6  | Bit 5  | Bit 4  | Bit 3        | Bit 2   | Bit 1  | Bit 0  | Register on Page |

|----------------|------------------------|--------|--------|--------|--------------|---------|--------|--------|------------------|

| CPSCON0        | CPSON                  |        |        |        | CPS-<br>RNG1 | CPSRNG0 | CPSOUT | T0XCS  | 112              |

| INTCON         | GIE                    | PEIE   | TOIE   | INTE   | RBIE         | TOIF    | INTF   | RBIF   | 36               |

| OPTION_RE<br>G | RBPU                   | INTEDG | T0CS   | T0SE   | PSA          | PS2     | PS1    | PS0    | 93               |

| TMR0           | Timer0 Module Register |        |        |        |              |         | _      |        |                  |

| TRISA          | TRISA7                 | TRISA6 | TRISA5 | TRISA4 | TRISA3       | TRISA2  | TRISA1 | TRISA0 | 43               |

**Legend:** -= Un implemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the Timer0 module.

#### REGISTER 15-1: CCPxCON: CCPx CONTROL REGISTER

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-------|-------|--------|--------|--------|--------|

| _     | _   | DCxB1 | DCxB0 | CCPxM3 | CCPxM2 | CCPxM1 | CCPxM0 |

| bit 7 |     |       |       |        |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-6 Unimplemented: Read as '0'

bit 5-4 DCxB<1:0>: PWM Duty Cycle Least Significant bits

> Capture mode: Unused

Compare mode:

Unused

PWM mode:

These bits are the two LSbs of the PWM duty cycle. The eight MSbs are found in CCPRxL.

bit 3-0 CCPxM<3:0>: CCP Mode Select bits

0000 = Capture/Compare/PWM Off (resets CCP module)

0001 = Unused (reserved)

0010 = Compare mode, toggle output on match (CCPxIF bit of the PIRx register is set)

0011 = Unused (reserved)

0100 = Capture mode, every falling edge

0101 = Capture mode, every rising edge

0110 = Capture mode, every 4th rising edge 0111 = Capture mode, every 16th rising edge

1000 = Compare mode, set output on match (CCPxIF bit of the PIRx register is set)

1001 = Compare mode, clear output on match (CCPxIF bit of the PIRx register is set)

1010 = Compare mode, generate software interrupt on match (CCPxIF bit is set of the PIRx register, CCPx pin is unaffected)

1011 = Compare mode, trigger special event (CCPxIF bit of the PIRx register is set, TMR1 is reset and A/D conversion<sup>(1)</sup> is started if the ADC module is enabled. CCPx pin is unaffected.)

11xx = PWM mode.

**Note 1:** A/D conversion start feature is available only on CCP2.

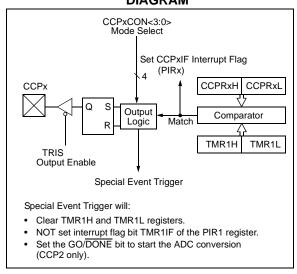

### 15.2 Compare Mode

In Compare mode, the 16-bit CCPRx register value is constantly compared against the TMR1 register pair value. When a match occurs, the CCPx module may:

- Toggle the CCPx output

- · Set the CCPx output

- · Clear the CCPx output

- Generate a Special Event Trigger

- · Generate a Software Interrupt

The action on the pin is based on the value of the CCPxM<3:0> control bits of the CCPxCON register.

All Compare modes can generate an interrupt.

# FIGURE 15-2: COMPARE MODE OPERATION BLOCK DIAGRAM

#### 15.2.1 CCPx PIN CONFIGURATION

The user must configure the CCPx pin as an output by clearing the associated TRIS bit.

Either RC1 or RB3 can be selected as the CCP2 pin. Refer to **Section 6.1 "Alternate Pin Function"** for more information.

Note: Clearing the CCPxCON register will force the CCPx compare output latch to the default low level. This is not the PORT I/O data latch.

#### 15.2.2 TIMER1 MODE SELECTION

In Compare mode, Timer1 must be running in either Timer mode or Synchronized Counter mode. The compare operation may not work in Asynchronous Counter mode.

Clocking Timer1 from the system clock (Fosc) should not be used in Compare mode. For the Compare operation of the TMR1 register to the CCPRx register to occur, Timer1 must be clocked from the instruction clock (Fosc/4) or from an external clock source.

#### 15.2.3 SOFTWARE INTERRUPT MODE

When Software Interrupt mode is chosen (CCPxM<3:0> = 1010), the CCPxIF bit in the PIRx register is set and the CCPx module does not assert control of the CCPx pin (refer to the CCPxCON register).

#### 15.2.4 SPECIAL EVENT TRIGGER

When Special Event Trigger mode is chosen (CCPxM<3:0> = 1011), the CCPx module does the following:

· Resets Timer1

Note:

Starts an ADC conversion if ADC is enabled (CCP2 only)

The CCPx module does not assert control of the CCPx pin in this mode (refer to the CCPxCON register).

The Special Event Trigger output of the CCP occurs immediately upon a match between the TMR1H, TMR1L register pair and the CCPRxH, CCPRxL register pair. The TMR1H, TMR1L register pair is not reset until the next rising edge of the Timer1 clock. This allows the CCPRxH, CCPRxL register pair to effectively provide a 16-bit programmable period register for Timer1.

- Note 1: The Special Event Trigger from the CCP module does not set interrupt flag bit TMR1IF of the PIR1 register.

- 2: Removing the match condition by changing the contents of the CCPRxH and CCPRxL register pair, between the clock edge that generates the Special Event Trigger and the clock edge that generates the Timer1 Reset, will preclude the Reset from occurring.

#### 15.2.5 COMPARE DURING SLEEP

The Compare mode is dependent upon the system clock (Fosc) for proper operation. Since Fosc is shut down during Sleep mode, the Compare mode will not function properly during Sleep.

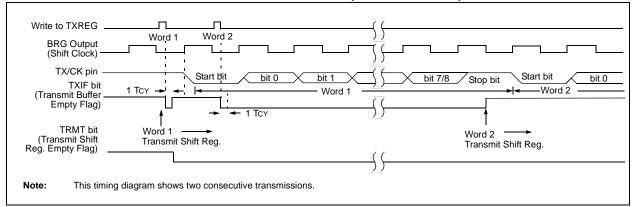

## FIGURE 16-4: ASYNCHRONOUS TRANSMISSION (BACK-TO-BACK)

TABLE 16-1: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Name   | Bit 7                         | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-------------------------------|--------|--------|--------|--------|--------|--------|-----------|----------------------|---------------------------------|

| INTCON | GIE                           | PEIE   | TOIE   | INTE   | RBIE   | T0IF   | INTF   | RBIF      | 0000 000x            | 0000 000x                       |

| PIE1   | TMR1GIE                       | ADIE   | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE    | 0000 0000            | 0000 0000                       |

| PIR1   | TMR1GIF                       | ADIF   | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF    | 0000 0000            | 0000 0000                       |

| RCSTA  | SPEN                          | RX9    | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D      | 0000 000x            | 0000 000x                       |

| SPBRG  | BRG7                          | BRG6   | BRG5   | BRG4   | BRG3   | BRG2   | BRG1   | BRG0      | 0000 0000            | 0000 0000                       |

| TRISC  | TRISC7                        | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0    | 1111 1111            | 1111 1111                       |

| TXREG  | AUSART Transmit Data Register |        |        |        |        |        |        | 0000 0000 | 0000 0000            |                                 |

| TXSTA  | CSRC                          | TX9    | TXEN   | SYNC   |        | BRGH   | TRMT   | TX9D      | 0000 -010            | 0000 -010                       |

**Legend:** x = unknown, - = unimplemented read as '0'. Shaded cells are not used for asynchronous transmission.

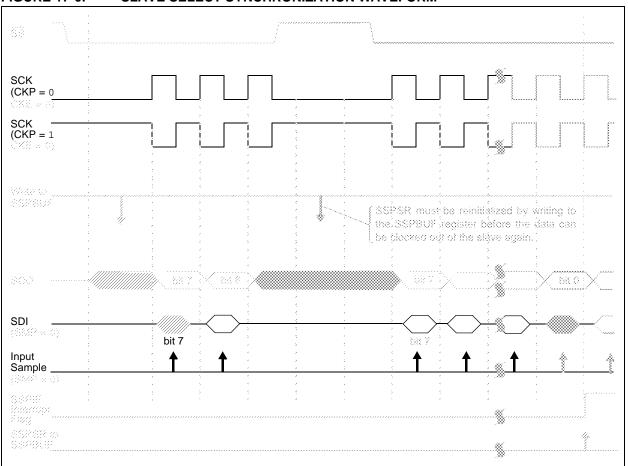

### 17.1.2.4 Slave Select Operation

The  $\overline{SS}$  pin allows Synchronous Slave mode operation. The SPI must be in Slave mode with  $\overline{SS}$  pin control enabled (SSPM<3:0> = 0100). The associated TRIS bit for the  $\overline{SS}$  pin must be set, making  $\overline{SS}$  an input.

In Slave Select mode, when:

- $\overline{SS}$  = 0, The device operates as specified in **Section 17.1.2 "Slave Mode"**.

- SS = 1, The SPI module is held in Reset and the SDO pin will be tri-stated.

- Note 1: When the SPI is in Slave mode with SS pin control enabled (SSPM<3:0> = 0100), the SPI module will reset if the SS pin is driven high.

- 2: If the SPI is used in Slave mode with CKE set, the SS pin control must be enabled.

When the SPI module resets, the bit counter is cleared to '0'. This can be done by either forcing the  $\overline{SS}$  pin to a high level or clearing the SSPEN bit. Figure 17-6 shows the timing waveform for such a synchronization event.

Note:

SSPSR must be reinitialized by writing to the SSPBUF register before the data can be clocked out of the slave again.

### 17.1.2.5 Sleep in Slave Mode

While in Sleep mode, the slave can transmit/receive data. The SPI Transmit/Receive Shift register operates asynchronously to the device on the externally supplied clock source. This allows the device to be placed in Sleep mode and data to be shifted into the SPI Transmit/Receive Shift register. When all eight bits have been received, the SSP Interrupt Flag bit will be set and if enabled, will wake the device from Sleep.

FIGURE 17-6: SLAVE SELECT SYNCHRONIZATION WAVEFORM

# 17.2 I<sup>2</sup>C Mode

The SSP module, in  $I^2C$  mode, implements all slave functions, except general call support. It provides interrupts on Start and Stop bits in hardware to facilitate firmware implementations of the master functions. The SSP module implements the  $I^2C$  Standard mode specifications:

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- Start and Stop bit interrupts enabled to support firmware Master mode

- · Address masking

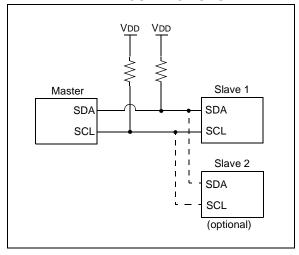

Two pins are used for data transfer; the SCL pin (clock line) and the SDA pin (data line). The user must configure the two pin's data direction bits as inputs in the appropriate TRIS register. Upon enabling  $\rm I^2C$  mode, the  $\rm I^2C$  slew rate limiters in the I/O pads are controlled by the SMP bit of SSPSTAT register. The SSP module functions are enabled by setting the SSPEN bit of SSPCON register.

Data is sampled on the rising edge and shifted out on the falling edge of the clock. This ensures that the SDA signal is valid during the SCL high time. The SCL clock input must have minimum high and low times for proper operation. Refer to Section 23.0 "Electrical Specifications".

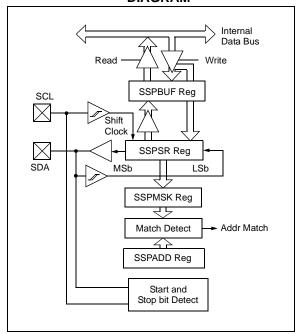

FIGURE 17-7: I<sup>2</sup>C MODE BLOCK DIAGRAM

# FIGURE 17-8: TYPICAL I<sup>2</sup>C CONNECTIONS

The SSP module has six registers for  $I^2C$  operation. They are:

- SSP Control (SSPCON) register

- SSP Status (SSPSTAT) register

- Serial Receive/Transmit Buffer (SSPBUF) register

- SSP Shift Register (SSPSR), not directly accessible

- SSP Address (SSPADD) register

- SSP Address Mask (SSPMSK) register

#### 17.2.1 HARDWARE SETUP

Selection of I<sup>2</sup>C mode, with the SSPEN bit of the SSPCON register set, forces the SCL and SDA pins to be open drain, provided these pins are programmed as inputs by setting the appropriate TRISC bits. The SSP module will override the input state with the output data, when required, such as for Acknowledge and slave-transmitter sequences.

**Note:** Pull-up resistors must be provided externally to the SCL and SDA pins for proper operation of the I<sup>2</sup>C module.

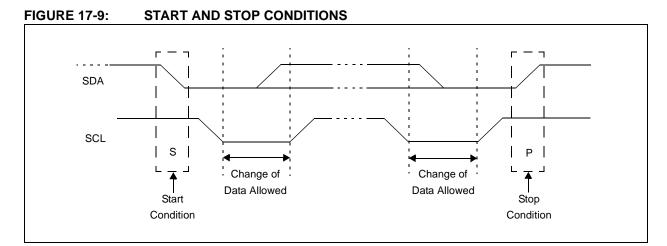

#### 17.2.2 START AND STOP CONDITIONS

During times of no data transfer (Idle time), both the clock line (SCL) and the data line (SDA) are pulled high through external pull-up resistors. The Start and Stop conditions determine the start and stop of data transmission. The Start condition is defined as a high-to-low transition of the SDA line while SCL is high. The Stop condition is defined as a low-to-high transition of the SDA line while SCL is high.

Figure 17-9 shows the Start and Stop conditions. A master device generates these conditions for starting and terminating data transfer. Due to the definition of the Start and Stop conditions, when data is being transmitted, the SDA line can only change state when the SCL line is low.

#### 17.2.3 ACKNOWLEDGE

After the valid reception of an address or data byte, the hardware automatically will generate the Acknowledge ( $\overline{ACK}$ ) pulse and load the SSPBUF register with the received value currently in the SSPSR register. There are certain conditions that will cause the SSP module not to generate this  $\overline{ACK}$  pulse. They include any or all of the following:

- The Buffer Full bit, BF of the SSPSTAT register, was set before the transfer was received.

- The SSP Overflow bit, SSPOV of the SSPCON register, was set before the transfer was received.

- The SSP module is being operated in Firmware Master mode.

In such a case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF of the PIR1 register is set. Table 17-2 shows the results of when a data transfer byte is received, given the status of bits BF and SSPOV. Flag bit BF is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

TABLE 17-2: DATA TRANSFER RECEIVED BYTE ACTIONS

|    | ts as Data<br>s Received | SSPSR → SSPBUF | Generate ACK Pulse | Set bit SSPIF<br>(SSP Interrupt occurs |  |

|----|--------------------------|----------------|--------------------|----------------------------------------|--|

| BF | SSPOV                    |                | Puise              | if enabled)                            |  |

| 0  | 0                        | Yes            | Yes                | Yes                                    |  |

| 1  | 0                        | No             | No                 | Yes                                    |  |

| 1  | 1                        | No             | No                 | Yes                                    |  |

| 0  | 1                        | No             | No                 | Yes                                    |  |

Note 1: Shaded cells show the conditions where the user software did not properly clear the overflow condition.

#### SSPSTAT: SYNCHRONOUS SERIAL PORT STATUS REGISTER (I<sup>2</sup>C MODE) REGISTER 17-4:

| R/W-0 | R/W-0 | R-0 | R-0 | R-0 | R-0 | R-0 | R-0   |

|-------|-------|-----|-----|-----|-----|-----|-------|

| SMP   | CKE   | D/Ā | Р   | S   | R/W | UA  | BF    |

| bit 7 |       |     |     |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 SMP: SPI Data Input Sample Phase bit

1 = Slew Rate Control (limiting) disabled. Operating in I<sup>2</sup>C Standard mode (100 kHz and 1 MHz).

0 = Slew Rate Control (limiting) enabled. Operating in I<sup>2</sup>C Fast mode (400 kHz).

bit 6 CKE: SPI Clock Edge Select bit

This bit must be maintained clear. Used in SPI mode only.

**D/A**: DATA/ADDRESS bit (I<sup>2</sup>C mode only) bit 5

1 = Indicates that the last byte received or transmitted was data

0 = Indicates that the last byte received or transmitted was address

bit 4

This bit is cleared when the SSP module is disabled, or when the Start bit is detected last.

1 = Indicates that a Stop bit has been detected last (this bit is '0' on Reset)

0 = Stop bit was not detected last

bit 3 S: Start bit

This bit is cleared when the SSP module is disabled, or when the Stop bit is detected last.

1 = Indicates that a Start bit has been detected last (this bit is '0' on Reset)

0 = Start bit was not detected last

R/W: READ/WRITE bit Information bit 2

> This bit holds the  $R/\overline{W}$  bit information following the last address match. This bit is only valid from the address match to the next Start bit, Stop bit or ACK bit.

1 = Read

0 = Write

**UA**: Update Address bit (10-bit I<sup>2</sup>C mode only) bit 1

1 = Indicates that the user needs to update the address in the SSPADD register

0 = Address does not need to be updated

bit 0 BF: Buffer Full Status bit

Receive:

1 = Receive complete, SSPBUF is full

0 = Receive not complete, SSPBUF is empty

**Transmit:**

1 = Transmit in progress, SSPBUF is full

0 = Transmit complete, SSPBUF is empty

| RLF              | Rotate Left f through Carry                                                                                                                                                                           |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] RLF f,d                                                                                                                                                                                     |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                    |

| Operation:       | See description below                                                                                                                                                                                 |

| Status Affected: | С                                                                                                                                                                                                     |

| Description:     | The contents of register 'f' are rotated one bit to the left through the Carry flag. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is stored back in register 'f'. |

| Words:           | 1                                                                                                                                                                                                     |

| Cycles:          | 1                                                                                                                                                                                                     |

| Example:         | RLF REG1,0                                                                                                                                                                                            |

|                  | Before Instruction  REG1 = 1110 0110  C = 0  After Instruction                                                                                                                                        |

|                  | REG1 = 1110 0110<br>W = 1100 1100<br>C = 1                                                                                                                                                            |

| SLEEP            | Enter Sleep mode                                                                                                                                                                           |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] SLEEP                                                                                                                                                                              |  |  |  |  |  |

| Operands:        | None $00h \rightarrow WDT,$ $0 \rightarrow \underline{WDT} \text{ prescaler,}$ $1 \rightarrow \overline{TO},$ $0 \rightarrow \overline{PD}$                                                |  |  |  |  |  |

| Operation:       |                                                                                                                                                                                            |  |  |  |  |  |

| Status Affected: | TO, PD                                                                                                                                                                                     |  |  |  |  |  |

| Description:     | The power-down Status bit, PD is cleared. Time-out Status bit, TO is set. Watchdog Timer and its prescaler are cleared.  The processor is put into Sleep mode with the oscillator stopped. |  |  |  |  |  |

|                  |                                                                                                                                                                                            |  |  |  |  |  |

| RRF              | Rotate Right f through Carry                                                                                                                                                                           |  |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ label ] RRF f,d                                                                                                                                                                                      |  |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                     |  |  |  |  |  |  |  |

| Operation:       | See description below                                                                                                                                                                                  |  |  |  |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are rotated one bit to the right through the Carry flag. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'. |  |  |  |  |  |  |  |

|                  | C Register f                                                                                                                                                                                           |  |  |  |  |  |  |  |

| SUBLW            | Subtract W from literal                                                                                                  |                 |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|--|--|--|

| Syntax:          | [label] S                                                                                                                | UBLW k          |  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                      |                 |  |  |  |  |  |  |

| Operation:       | $k - (W) \rightarrow (W)$                                                                                                |                 |  |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                 |                 |  |  |  |  |  |  |

| Description:     | The W register is subtracted (2's complement method) from the 8-bit literal 'k'. The result is placed in the W register. |                 |  |  |  |  |  |  |

|                  | <b>C</b> = 0                                                                                                             | W > k           |  |  |  |  |  |  |

|                  | <b>C</b> = 1                                                                                                             | $W \le k$       |  |  |  |  |  |  |

|                  | <b>DC</b> = 0                                                                                                            | W<3:0> > k<3:0> |  |  |  |  |  |  |

|                  | DC = 1                                                                                                                   | W<3:0> ≤ k<3:0> |  |  |  |  |  |  |

# 23.3 DC Characteristics: PIC16(L)F722A/723A-I/E (Power-Down)

| PIC16LF722A/723A                             |                        | Standard Operating Conditions (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for extended |                                                                                                                                                                                                                                    |               |                |       |            |                                    |  |

|----------------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------|-------|------------|------------------------------------|--|

| PIC16F722A/723A                              |                        |                                                                                                                                                                                                                                    | Standard Operating Conditions (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for extended |               |                |       |            |                                    |  |

| Param                                        | Device Characteristics | Min.                                                                                                                                                                                                                               | Тур†                                                                                                                                                                                                                               | Max.<br>+85°C | Max.<br>+125°C | Units | Conditions |                                    |  |

| No.                                          |                        |                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                    |               |                |       | VDD        | Note                               |  |

| Power-down Base Current (IPD) <sup>(2)</sup> |                        |                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                    |               |                |       |            |                                    |  |

| D020                                         |                        | _                                                                                                                                                                                                                                  | 0.02                                                                                                                                                                                                                               | 0.7           | 3.9            | μА    | 1.8        | WDT, BOR, FVR, and T1OSC           |  |

|                                              |                        | _                                                                                                                                                                                                                                  | 0.08                                                                                                                                                                                                                               | 1.0           | 4.3            | μА    | 3.0        | disabled, all Peripherals Inactive |  |

| D020                                         |                        | _                                                                                                                                                                                                                                  | 4.3                                                                                                                                                                                                                                | 10.2          | 17             | μΑ    | 1.8        | WDT, BOR, FVR, and T1OSC           |  |

|                                              |                        | _                                                                                                                                                                                                                                  | 5                                                                                                                                                                                                                                  | 10.5          | 18             | μΑ    | 3.0        | disabled, all Peripherals Inactive |  |

|                                              |                        | _                                                                                                                                                                                                                                  | 5.5                                                                                                                                                                                                                                | 11.8          | 21             | μА    | 5.0        |                                    |  |

| D021                                         |                        | _                                                                                                                                                                                                                                  | 0.5                                                                                                                                                                                                                                | 1.7           | 4.1            | μΑ    | 1.8        | LPWDT Current (Note 1)             |  |

|                                              |                        | _                                                                                                                                                                                                                                  | 0.8                                                                                                                                                                                                                                | 2.5           | 4.8            | μΑ    | 3.0        |                                    |  |

| D021                                         |                        | _                                                                                                                                                                                                                                  | 6                                                                                                                                                                                                                                  | 13.5          | 16.4           | μА    | 1.8        | LPWDT Current (Note 1)             |  |

|                                              |                        | _                                                                                                                                                                                                                                  | 6.5                                                                                                                                                                                                                                | 14.5          | 16.8           | μΑ    | 3.0        |                                    |  |

|                                              |                        | _                                                                                                                                                                                                                                  | 7.5                                                                                                                                                                                                                                | 16            | 18.7           | μА    | 5.0        |                                    |  |

| D021A                                        |                        | _                                                                                                                                                                                                                                  | 8.5                                                                                                                                                                                                                                | 14            | 19             | μА    | 1.8        | FVR current (Note 1. Note 3)       |  |

|                                              |                        | _                                                                                                                                                                                                                                  | 8.5                                                                                                                                                                                                                                | 14            | 20             | μΑ    | 3.0        |                                    |  |

| D021A                                        |                        | _                                                                                                                                                                                                                                  | 23                                                                                                                                                                                                                                 | 44            | 48             | μА    | 1.8        | FVR current (Note 1, Note 3,       |  |

|                                              |                        | _                                                                                                                                                                                                                                  | 25                                                                                                                                                                                                                                 | 45            | 55             | μА    | 3.0        | Note 5)                            |  |

|                                              |                        | _                                                                                                                                                                                                                                  | 26                                                                                                                                                                                                                                 | 60            | 70             | μА    | 5.0        |                                    |  |

| D022                                         |                        | _                                                                                                                                                                                                                                  | _                                                                                                                                                                                                                                  | _             | _              | μА    | 1.8        | BOR Current (Note 1, Note 3)       |  |

|                                              |                        | _                                                                                                                                                                                                                                  | 7.5                                                                                                                                                                                                                                | 12            | 22             | μА    | 3.0        |                                    |  |

| D022                                         |                        | _                                                                                                                                                                                                                                  | _                                                                                                                                                                                                                                  | _             | _              | μА    | 1.8        | BOR Current (Note 1, Note 3,       |  |

|                                              |                        | _                                                                                                                                                                                                                                  | 23                                                                                                                                                                                                                                 | 42            | 49             | μА    | 3.0        | Note 5)                            |  |

|                                              |                        | _                                                                                                                                                                                                                                  | 25                                                                                                                                                                                                                                 | 46            | 50             | μА    | 5.0        |                                    |  |

| D026                                         |                        | _                                                                                                                                                                                                                                  | 0.6                                                                                                                                                                                                                                | 2             | _              | μА    | 1.8        | T1OSC Current (Note 1)             |  |

|                                              |                        | _                                                                                                                                                                                                                                  | 1.8                                                                                                                                                                                                                                | 3.0           | _              | μΑ    | 3.0        | ]                                  |  |

| D026                                         |                        |                                                                                                                                                                                                                                    | 4.5                                                                                                                                                                                                                                | 11.1          | _              | μА    | 1.8        | T1OSC Current (Note 1)             |  |

|                                              |                        | _                                                                                                                                                                                                                                  | 6                                                                                                                                                                                                                                  | 12.5          | _              | μА    | 3.0        |                                    |  |

|                                              |                        | _                                                                                                                                                                                                                                  | 7                                                                                                                                                                                                                                  | 13.5          | _              | μА    | 5.0        |                                    |  |

<sup>†</sup> Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral Δ current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

- 2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD.

- 3: Fixed Voltage Reference is automatically enabled whenever the BOR is enabled.

- 4: A/D oscillator source is FRC.

- 5:  $0.1 \mu F$  capacitor on VCAP (RA0).

# 23.3 DC Characteristics: PIC16(L)F722A/723A-I/E (Power-Down) (Continued)

| PIC16LF722A/723A                             |                        | ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` ` |                            |               | ditions (unless otherwise stated) -40°C ≤ TA ≤ +85°C for industrial -40°C ≤ TA ≤ +125°C for extended |       |                                                                                                                                                                                         |                                         |  |

|----------------------------------------------|------------------------|-----------------------------------------|----------------------------|---------------|------------------------------------------------------------------------------------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--|

| PIC16F722A/723A                              |                        |                                         | Operating temperature -40° |               |                                                                                                      |       | ions (unless otherwise stated)<br>$40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial<br>$40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for extended |                                         |  |

| Param                                        | Device Characteristics | Min.                                    | Typ†                       | Max.<br>+85°C | Max.<br>+125°C                                                                                       | Unite |                                                                                                                                                                                         | Conditions                              |  |

| No.                                          |                        |                                         |                            | +65 C         | +125 C                                                                                               |       | VDD                                                                                                                                                                                     | Note                                    |  |

| Power-down Base Current (IPD) <sup>(2)</sup> |                        |                                         |                            |               |                                                                                                      |       |                                                                                                                                                                                         |                                         |  |

| D027                                         |                        |                                         | 0.06                       | 0.7           | 5.0                                                                                                  | μΑ    | 1.8                                                                                                                                                                                     | A/D Current (Note 1, Note 4), no        |  |

|                                              |                        | _                                       | 0.08                       | 1.0           | 5.5                                                                                                  | μΑ    | 3.0                                                                                                                                                                                     | conversion in progress                  |  |

| D027                                         |                        | _                                       | 6                          | 10.7          | 18                                                                                                   | μΑ    | 1.8                                                                                                                                                                                     | A/D Current (Note 1, Note 4), no        |  |

|                                              |                        |                                         | 7                          | 10.6          | 20                                                                                                   | μΑ    | 3.0                                                                                                                                                                                     | conversion in progress                  |  |

|                                              |                        | _                                       | 7.2                        | 11.9          | 22                                                                                                   | μΑ    | 5.0                                                                                                                                                                                     |                                         |  |

| D027A                                        |                        |                                         | 250                        | 400           | _                                                                                                    | μΑ    | 1.8                                                                                                                                                                                     | A/D Current (Note 1, Note 4),           |  |

|                                              |                        |                                         | 250                        | 400           | _                                                                                                    | μΑ    | 3.0                                                                                                                                                                                     | conversion in progress                  |  |

| D027A                                        |                        | _                                       | 280                        | 430           | _                                                                                                    | μΑ    | 1.8                                                                                                                                                                                     | A/D Current (Note 1, Note 4,            |  |

|                                              |                        | _                                       | 280                        | 430           | _                                                                                                    | μΑ    | 3.0                                                                                                                                                                                     | Note 5), conversion in progress         |  |

|                                              |                        | _                                       | 280                        | 430           | _                                                                                                    | μΑ    | 5.0                                                                                                                                                                                     |                                         |  |

| D028                                         |                        |                                         | 2.2                        | 3.2           | 14.4                                                                                                 | μΑ    | 1.8                                                                                                                                                                                     | Cap Sense Low Power                     |  |

|                                              |                        | _                                       | 3.3                        | 4.4           | 15.6                                                                                                 | μΑ    | 3.0                                                                                                                                                                                     | Oscillator mode                         |  |

| D028                                         |                        |                                         | 6.5                        | 13            | 21                                                                                                   | μΑ    | 1.8                                                                                                                                                                                     | Cap Sense Low Power                     |  |

|                                              |                        | _                                       | 8                          | 14            | 23                                                                                                   | μΑ    | 3.0                                                                                                                                                                                     | Oscillator mode                         |  |

|                                              |                        | _                                       | 8                          | 14            | 25                                                                                                   | μΑ    | 5.0                                                                                                                                                                                     |                                         |  |

| D028A                                        |                        | _                                       | 4.2                        | 6             | 17                                                                                                   | μΑ    | 1.8                                                                                                                                                                                     | Cap Sense Medium Power                  |  |

|                                              |                        | _                                       | 6                          | 7             | 18                                                                                                   | μΑ    | 3.0                                                                                                                                                                                     | Oscillator mode                         |  |

| D028A                                        |                        | _                                       | 8.5                        | 15.5          | 23                                                                                                   | μΑ    | 1.8                                                                                                                                                                                     | Cap Sense Medium Power                  |  |

|                                              | _                      | 11                                      | 17                         | 24            | μΑ                                                                                                   | 3.0   | Oscillator mode                                                                                                                                                                         |                                         |  |

|                                              |                        | _                                       | 11                         | 18            | 27                                                                                                   | μΑ    | 5.0                                                                                                                                                                                     |                                         |  |

| D028B                                        |                        | _                                       | 12                         | 14            | 25                                                                                                   | μА    | 1.8                                                                                                                                                                                     | Cap Sense High Power<br>Oscillator mode |  |

|                                              |                        | _                                       | 32                         | 35            | 44                                                                                                   | μА    | 3.0                                                                                                                                                                                     |                                         |  |

| D028B                                        |                        | _                                       | 16                         | 20            | 31                                                                                                   | μА    | 1.8                                                                                                                                                                                     | Cap Sense High Power                    |  |

|                                              |                        |                                         | 36                         | 41            | 50                                                                                                   | μΑ    | 3.0                                                                                                                                                                                     | Oscillator mode                         |  |

|                                              | _                      | 42                                      | 49                         | 58            | μΑ                                                                                                   | 5.0   |                                                                                                                                                                                         |                                         |  |

<sup>†</sup> Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral Δ current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

- 2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD.

- 3: Fixed Voltage Reference is automatically enabled whenever the BOR is enabled.

- 4: A/D oscillator source is FRC.

- 5: 0.1 μF capacitor on VCAP (RA0).

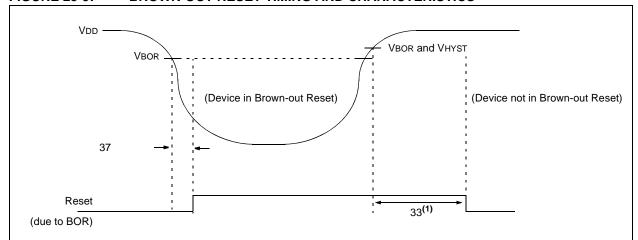

# FIGURE 23-9: BROWN-OUT RESET TIMING AND CHARACTERISTICS

Note 1: 64 ms delay only if PWRTE bit in the Configuration Word register is programmed to '0'. 2 ms delay if PWRTE = 0 and VREGEN = 1.

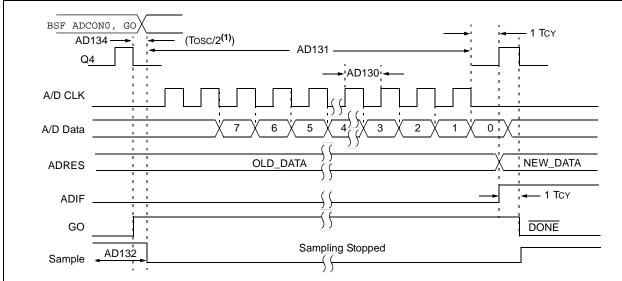

## FIGURE 23-12: PIC16F722A/723A A/D CONVERSION TIMING (NORMAL MODE)

Note 1: If the A/D clock source is selected as RC, a time of Tcy is added before the A/D clock starts. This allows the SLEEP instruction to be executed.

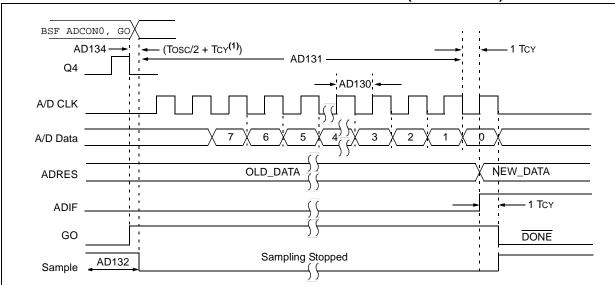

# FIGURE 23-13: PIC16F722A/723A A/D CONVERSION TIMING (SLEEP MODE)

Note 1: If the A/D clock source is selected as RC, a time of Tcy is added before the A/D clock starts. This allows the SLEEP instruction to be executed.