Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

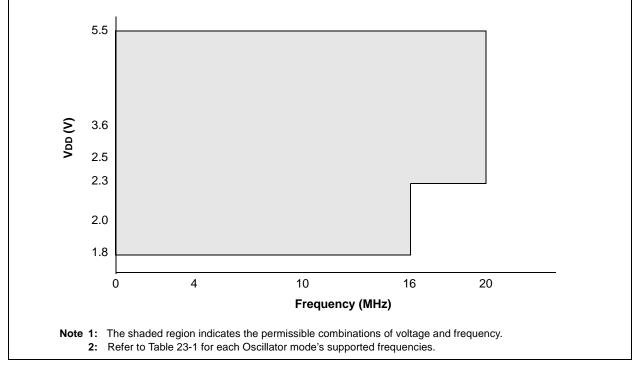

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 3.5КВ (2К х 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 11x8b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf722a-i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 1.0   | Device Overview                                                              | 7    |

|-------|------------------------------------------------------------------------------|------|

| 2.0   | Memory Organization                                                          | . 11 |

| 3.0   | Resets                                                                       | . 23 |

| 4.0   | Interrupts                                                                   | . 33 |

| 5.0   | Low Dropout (LDO) Voltage Regulator                                          | . 41 |

| 6.0   | I/O Ports                                                                    | . 42 |

| 7.0   | Oscillator Module                                                            | . 71 |

| 8.0   | Device Configuration                                                         | 77   |

| 9.0   | Analog-to-Digital Converter (ADC) Module                                     | . 80 |

| 10.0  | Fixed Voltage Reference                                                      | . 90 |

| 11.0  | Timer0 Module                                                                | . 91 |

| 12.0  | Timer1 Module with Gate Control                                              | 103  |

| 13.0  | Timer2 Module                                                                | 115  |

| 14.0  | Capacitive Sensing Module                                                    | 108  |

| 15.0  | Capture/Compare/PWM (CCP) Module                                             | 114  |

| 16.0  | Addressable Universal Synchronous Asynchronous Receiver Transmitter (AUSART) | 124  |

| 17.0  |                                                                              |      |

| 18.0  | Program Memory Read                                                          | 167  |

| 19.0  | Power-Down Mode (Sleep)                                                      | 170  |

| 20.0  | In-Circuit Serial Programming™ (ICSP™)                                       | 172  |

| 21.0  | Instruction Set Summary                                                      | 173  |

| 22.0  | Development Support                                                          | 182  |

| 23.0  | Electrical Specifications                                                    | 186  |

| 24.0  |                                                                              |      |

| 25.0  | Packaging Information                                                        | 249  |

| Appe  | ndix A: Data Sheet Revision History                                          | 261  |

| Appe  | ndix B: Migrating From Other PIC <sup>®</sup> Devices                        | 261  |

| The I | Nicrochip Website                                                            | 262  |

| Cust  | omer Change Notification Service                                             | 262  |

| Cust  | omer Support                                                                 | 262  |

| Prod  | uct Identification System                                                    | 263  |

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS3000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

## 1.0 DEVICE OVERVIEW

The PIC16(L)F722A/723A devices are covered by this data sheet. They are available in 28-pin packages. Figure 1-1 shows a block diagram of the PIC16(L)F722A/723A devices. Table 1-1 shows the pinout descriptions.

| Address                | Name       | Bit 7                                              | Bit 6         | Bit 5         | Bit 4         | Bit 3         | Bit 2           | Bit 1        | Bit 0     | Value on:<br>POR, BOR | Page   |

|------------------------|------------|----------------------------------------------------|---------------|---------------|---------------|---------------|-----------------|--------------|-----------|-----------------------|--------|

| Bank 2                 |            |                                                    |               |               |               |               |                 |              |           |                       |        |

| 100h <sup>(2)</sup>    | INDF       |                                                    |               |               |               |               |                 |              |           |                       | 22,30  |

| 101h                   | TMR0       | Timer0 Mod                                         | lule Register |               |               |               |                 |              |           | xxxx xxxx             | 91,30  |

| 102h <sup>(2)</sup>    | PCL        | Program Co                                         | ounter's (PC) | Least Signi   | ificant Byte  |               |                 |              |           | 0000 0000             | 21,30  |

| 103h <sup>(2)</sup>    | STATUS     | IRP                                                | RP1           | RP0           | TO            | PD            | Z               | DC           | С         | 0001 1xxx             | 18,30  |

| 104h <sup>(2)</sup>    | FSR        | Indirect Dat                                       | a Memory A    | ddress Point  | ter           | •             | •               |              |           | xxxx xxxx             | 22,30  |

| 105h                   | —          | Unimpleme                                          | nted          |               |               |               |                 |              |           | _                     | _      |

| 106h                   | —          | Unimpleme                                          | nted          |               |               |               |                 |              |           | _                     | _      |

| 107h                   | —          | Unimpleme                                          | nted          |               |               |               |                 |              |           | _                     | _      |

| 108h                   | CPSCON0    | CPSON                                              | _             | _             | _             | CPSRNG1       | CPSRNG0         | CPSOUT       | TOXCS     | 0 0000                | 112,31 |

| 109h                   | CPSCON1    | _                                                  | _             | _             | _             | _             | CPSCH2          | CPSCH1       | CPSCH0    | 0000                  | 113,31 |

| 10Ah <sup>(1, 2)</sup> | PCLATH     | —                                                  | —             | —             | Write Buffer  | for the upper | r 5 bits of the | Program Cou  | unter     | 0 0000                | 21,30  |

| 10Bh <sup>(2)</sup>    | INTCON     | GIE                                                | PEIE          | TOIE          | INTE          | RBIE          | T0IF            | INTF         | RBIF      | 0000 000x             | 36,30  |

| 10Ch                   | PMDATL     | Program Memory Read Data Register Low Byte         |               |               |               |               |                 |              |           | xxxx xxxx             | 167,31 |

| 10Dh                   | PMADRL     | Program Memory Read Address Register Low Byte      |               |               |               |               |                 |              | xxxx xxxx | 167,31                |        |

| 10Eh                   | PMDATH     | — Program Memory Read Data Register High Byte      |               |               |               |               |                 |              | xx xxxx   | 167,31                |        |

| 10Fh                   | PMADRH     | — — Program Memory Read Address Register High Byte |               |               |               |               |                 | e            | x xxxx    | 167,31                |        |

| Bank 3                 |            | •                                                  |               | •             | •             |               |                 |              |           | •                     |        |

| 180h <sup>(2)</sup>    | INDF       | Addressing                                         | this location | uses conter   | nts of FSR to | address data  | a memory (not   | a physical r | egister)  | xxxx xxxx             | 22,30  |

| 181h                   | OPTION_REG | RBPU                                               | INTEDG        | TOCS          | TOSE          | PSA           | PS2             | PS1          | PS0       | 1111 1111             | 19,30  |

| 182h <sup>(2)</sup>    | PCL        | Program Co                                         | ounter (PC) L | east Signific | cant Byte     | •             | •               |              |           | 0000 0000             | 21,30  |

| 183h <sup>(2)</sup>    | STATUS     | IRP                                                | RP1           | RP0           | TO            | PD            | Z               | DC           | С         | 0001 1xxx             | 18,30  |

| 184h <sup>(2)</sup>    | FSR        | Indirect Dat                                       | a Memory A    | ddress Point  | ter           |               |                 |              |           | xxxx xxxx             | 22,30  |

| 185h                   | ANSELA     | —                                                  | _             | ANSA5         | ANSA4         | ANSA3         | ANSA2           | ANSA1        | ANSA0     | 11 1111               | 44,31  |

| 186h                   | ANSELB     | —                                                  | _             | ANSB5         | ANSB4         | ANSB3         | ANSB2           | ANSB1        | ANSB0     | 11 1111               | 53,31  |

| 187h                   | —          | Unimplemented                                      |               |               |               |               |                 |              | —         | _                     |        |

| 18Ah <sup>(1, 2)</sup> | PCLATH     | _                                                  | _             | _             | Write Buffer  | for the upper | r 5 bits of the | Program Cou  | unter     | 0 0000                | 21,30  |

| 18Bh <sup>(2)</sup>    | INTCON     | GIE                                                | PEIE          | TOIE          | INTE          | RBIE          | T0IF            | INTF         | RBIF      | 0000 000x             | 36,30  |

| 18Ch                   | PMCON1     | Reserved                                           | —             | —             | —             | —             | —               | —            | RD        | 10                    | 168,31 |

| 18Dh                   | —          | Unimpleme                                          | nted          |               |               |               |                 |              |           | —                     | _      |

| 18Eh                   | _          | Unimpleme                                          | nted          |               |               |               |                 |              |           | —                     | —      |

| 18Fh                   | —          | Unimpleme                                          | nted          |               |               |               |                 |              |           | _                     | —      |

#### TABLE 2-1: PIC16(L)F722A/723A SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

**Legend:** x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

Note 1: The upper byte of the program counter is not directly accessible. PCLATH is a holding register for the PC<12:8>, whose contents are transferred to the upper byte of the program counter.

2: These registers can be addressed from any bank.

**3:** Accessible only when SSPM<3:0 > = 1001.

4: Accessible only when SSPM<3:0>  $\neq$  1001.

5: This bit is always '1' as RE3 is input-only.

#### 2.2.2.3 PCON Register

The Power Control (PCON) register contains flag bits (refer to Table 3-2) to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Watchdog Timer Reset (WDT)

- External MCLR Reset

The PCON register also controls the software enable of the BOR.

The PCON register bits are shown in Register 2-3.

### REGISTER 2-3: PCON: POWER CONTROL REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-q | R/W-q |

|-------|-----|-----|-----|-----|-----|-------|-------|

| —     | _   | _   | _   | —   | —   | POR   | BOR   |

| bit 7 |     |     |     |     |     |       | bit 0 |

| Legend:                |                  |                       |                    |

|------------------------|------------------|-----------------------|--------------------|

| R = Readable bit       | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR      | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| q = Value depends on c | ondition         |                       |                    |

| bit 7-2 | Unimplemented: Read as '0'                                                                                                                                                                                      |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 1   | POR: Power-on Reset Status bit                                                                                                                                                                                  |

|         | <ul> <li>1 = No Power-on Reset occurred</li> <li>0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)</li> </ul>                                                               |

| bit 0   | <ul> <li>BOR: Brown-out Reset Status bit</li> <li>1 = No Brown-out Reset occurred</li> <li>0 = A Brown-out Reset occurred (must be set in software after a Power-on Reset or Brown-out Reset occurs)</li> </ul> |

**Note 1:** Set BOREN<1:0> = 01 in the Configuration Word register for this bit to control the  $\overline{\text{BOR}}$ .

| Name       | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3   | Bit 2   | Bit 1       | Bit 0   | Register<br>on Page |

|------------|--------|--------|--------|--------|---------|---------|-------------|---------|---------------------|

| ADCON0     | _      | _      | CHS3   | CHS2   | CHS1    | CHS0    | GO/<br>DONE | ADON    | 85                  |

| ADCON1     | _      | ADCS2  | ADCS1  | ADCS0  | —       | —       | ADREF1      | ADREF0  | 86                  |

| ANSELA     | _      | —      | ANSA5  | ANSA4  | ANSA3   | ANSA2   | ANSA1       | ANSA0   | 44                  |

| APFCON     | _      | —      | _      | _      | —       | —       | SSSEL       | CCP2SEL | 42                  |

| CPSCON0    | CPSON  | —      | _      | _      | CPSRNG1 | CPSRNG0 | CPSOUT      | TOXCS   | 112                 |

| CPSCON1    | _      | —      |        | _      | —       | CPSCH2  | CPSCH1      | CPSCH0  | 113                 |

| OPTION_REG | RBPU   | INTEDG | TOCS   | T0SE   | PSA     | PS2     | PS1         | PS0     | 19                  |

| PORTA      | RA7    | RA6    | RA5    | RA4    | RA3     | RA2     | RA1         | RA0     | 43                  |

| SSPCON     | WCOL   | SSPOV  | SSPEN  | CKP    | SSPM3   | SSPM2   | SSPM1       | SSPM0   | 152                 |

| TRISA      | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3  | TRISA2  | TRISA1      | TRISA0  | 43                  |

#### TABLE 6-1: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

**Legend:** x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

#### TABLE 6-2: SUMMARY OF CONFIGURATION WORD WITH CLOCK SOURCES

| Name                   | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|------------------------|------|---------|---------|----------|----------|----------|----------|---------|---------|---------------------|

| CONFIG2 <sup>(1)</sup> | 13:8 | _       | _       | _        | _        | _        | —        | _       | —       | 70                  |

|                        | 7:0  | _       | _       | VCAPEN1  | VCAPEN0  | WDTE     | _        | _       | —       | 78                  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

Note 1: PIC16F722A/723A only.

## 7.2 Clock Source Modes

Clock source modes can be classified as external or internal.

- Internal clock source (INTOSC) is contained within the oscillator module and derived from a 500 kHz high precision oscillator. The oscillator module has eight selectable output frequencies, with a maximum internal frequency of 16 MHz.

- External clock modes rely on external circuitry for the clock source. Examples are: oscillator modules (EC mode), quartz crystal resonators or ceramic resonators (LP, XT and HS modes) and Resistor-Capacitor (RC) mode circuits.

The system clock can be selected between external or internal clock sources via the FOSC bits of the Configuration Word 1.

## 7.3 Internal Clock Modes

The oscillator module has eight output frequencies derived from a 500 kHz high precision oscillator. The IRCF bits of the OSCCON register select the postscaler applied to the clock source dividing the frequency by 1, 2, 4 or 8. Setting the PLLEN bit of the Configuration Word 1 locks the internal clock source to 16 MHz before the postscaler is selected by the IRCF bits. The PLLEN bit must be set or cleared at the time of programming; therefore, only the upper or low four clock source frequencies are selectable in software.

### 7.3.1 INTOSC AND INTOSCIO MODES

The INTOSC and INTOSCIO modes configure the internal oscillators as the system clock source when the device is programmed using the oscillator selection or the FOSC<2:0> bits in the CONFIG1 register. See **Section 8.0** "**Device Configuration**" for more information.

In INTOSC mode, OSC1/CLKIN is available for general purpose I/O. OSC2/CLKOUT outputs the selected internal oscillator frequency divided by 4. The CLKOUT signal may be used to provide a clock for external circuitry, synchronization, calibration, test or other application requirements.

In INTOSCIO mode, OSC1/CLKIN and OSC2/ CLKOUT are available for general purpose I/O.

## 7.3.2 FREQUENCY SELECT BITS (IRCF)

The output of the 500 kHz INTOSC and 16 MHz INTOSC, with Phase-Locked Loop enabled, connect to a postscaler and multiplexer (see Figure 7-1). The Internal Oscillator Frequency Select bits (IRCF) of the OSCCON register select the frequency output of the internal oscillator. Depending upon the PLLEN bit, one of four frequencies of two frequency sets can be selected via software:

If PLLEN = 1, frequency selection is as follows:

- 16 MHz

- 8 MHz (Default after Reset)

- 4 MHz

- 2 MHz

- If PLLEN = 0, frequency selection is as follows:

- 500 kHz

- 250 kHz (Default after Reset)

- 125 kHz

- 62.5 kHz

- Note: Following any Reset, the IRCF<1:0> bits of the OSCCON register are set to '10' and the frequency selection is set to 8 MHz or 250 kHz. The user can modify the IRCF bits to select a different frequency.

There is no start-up delay before a new frequency selected in the IRCF bits takes effect. This is because the old and new frequencies are derived from INTOSC via the postscaler and multiplexer.

Start-up delay specifications are located in Table 23-2 in Section 23.0 "Electrical Specifications".

## 12.1 Timer1 Operation

The Timer1 module is a 16-bit incrementing counter which is accessed through the TMR1H:TMR1L register pair. Writes to TMR1H or TMR1L directly update the counter.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

Timer1 is enabled by configuring the TMR1ON and TMR1GE bits in the T1CON and T1GCON registers, respectively. Table 12-1 displays the Timer1 enable selections.

TABLE 12-1: TIMER1 ENABLE SELECTIONS

| TMR10N | TMR1GE | Timer1<br>Operation |

|--------|--------|---------------------|

| 0      | 0      | Off                 |

| 0      | 1      | Off                 |

| 1      | 0      | Always On           |

| 1      | 1      | Count Enabled       |

## 12.2 Clock Source Selection

The TMR1CS<1:0> and T1OSCEN bits of the T1CON register are used to select the clock source for Timer1. Table 12-2 displays the clock source selections.

#### 12.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected the TMR1H:TMR1L register pair will increment on multiples of FISC as determined by the Timer1 prescaler.

#### 12.2.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1 module may work as a timer or a counter.

When enabled to count, Timer1 is increment ed on the rising edge of the external clock input T1CKI or the capacitive sensing oscillator signal. Either of these external clock sources can be synchronized to the microcontroller system clock or they can run asynchronously.

When used as a timer with a clock oscillator, an external 32.768 kHz crystal can be used in conjunction with the dedicated internal oscillator circuit.

| Note: | In Counter mode, a falling edge must be<br>registered by the counter prior to the first<br>incrementing rising edge after any one or |

|-------|--------------------------------------------------------------------------------------------------------------------------------------|

|       | more of the following conditions:                                                                                                    |

|       | •Timer1 enabled after POP                                                                                                            |

•Timer1 enabled after POR

•Write to TMR1H or TMR1L

- •Timer1 is disabled

- •Timer1 is disabled (TMR1ON = 0) when T1CKI is high then Timer1 is enabled (TMR1ON= 1) when T1CKI is low.

| TMR1CS1 | TMR1CS0 | T10SCEN | Clock Source                           |  |

|---------|---------|---------|----------------------------------------|--|

| 0       | 1       | x       | System Clock (FOSC)                    |  |

| 0       | 0       | x       | Instruction Clock (Fosc/4)             |  |

| 1       | 1       | x       | Capacitive Sensing Oscillator          |  |

| 1       | 0       | 0       | External Clocking on T1CKI Pin         |  |

| 1       | 0       | 1       | Oscillator Circuit on T1OSI/T1OSO Pins |  |

#### TABLE 12-2: CLOCK SOURCE SELECTIONS

## 12.6 Timer1 Gate

Timer1 can be configured to count freely or the count can be enabled and disabled using Timer1 gate circuitry. This is also referred to as Timer1 Gate Count Enable.

Timer1 gate can also be driven by multiple selectable sources.

#### 12.6.1 TIMER1 GATE COUNT ENABLE

The Timer1 gate is enabled by setting the TMR1GE bit of the T1GCON register. The polarity of the Timer1 gate is configured using the T1GPOL bit of the T1GCON register.

When Timer1 Gate (T1G) input is active, Timer1 will increment on the rising edge of the Timer1 clock source. When Timer1 gate input is inactive, no incrementing will occur and Timer1 will hold the current count. See Figure 12-4 for timing details.

## TABLE 12-3: TIMER1 GATE ENABLE SELECTIONS

| T1CLK      | T1GPOL | T1G | Timer1 Operation |

|------------|--------|-----|------------------|

| 1          | 0      | 0   | Counts           |

| $\uparrow$ | 0      | 1   | Holds Count      |

| $\uparrow$ | 1      | 0   | Holds Count      |

| $\uparrow$ | 1      | 1   | Counts           |

#### 12.6.2 TIMER1 GATE SOURCE SELECTION

The Timer1 gate source can be selected from one of four different sources. Source selection is controlled by the T1GSS bits of the T1GCON register. The polarity for each available source is also selectable. Polarity selection is controlled by the T1GPOL bit of the T1GCON register.

#### TABLE 12-4: TIMER1 GATE SOURCES

| T1GSS | Timer1 Gate Source                                                    |

|-------|-----------------------------------------------------------------------|

| 00    | Timer1 Gate Pin                                                       |

| 01    | Overflow of Timer0<br>(TMR0 increments from FFh to 00h)               |

| 10    | Timer2 match PR2<br>(TMR2 increments to match PR2)                    |

| 11    | Count Enabled by WDT Overflow<br>(Watchdog Time-out interval expired) |

#### 12.6.2.1 T1G Pin Gate Operation

The T1G pin is one source for Timer1 gate control. It can be used to supply an external source to the Timer1 gate circuitry.

#### 12.6.2.2 Timer0 Overflow Gate Operation

When Timer0 increments from FFh to 00h, a low-tohigh pulse will automatically be generated and internally supplied to the Timer1 gate circuitry.

#### 12.6.2.3 Timer2 Match Gate Operation

The TMR2 register will increment until it matches the value in the PR2 register. On the very next increment cycle, TMR2 will be reset to 00h. When this Reset occurs, a low-to-high pulse will automatically be generated and internally supplied to the Timer1 gate circuitry.

#### 12.6.2.4 Watchdog Overflow Gate Operation

The Watchdog Timer oscillator, prescaler and counter will be automatically turned on when TMR1GE = 1 and T1GSS selects the WDT as a gate source for Timer1 (T1GSS = 11). TMR1ON does not factor into the oscillator, prescaler and counter enable. See Table .

The PSA and PS bits of the OPTION register still control what time-out interval is selected. Changing the prescaler during operation may result in a spurious capture.

Enabling the Watchdog Timer oscillator does not automatically enable a Watchdog Reset or Wake-up from Sleep upon counter overflow.

| Note: | When using the WDT as a gate source for     |

|-------|---------------------------------------------|

|       | 5 5                                         |

|       | Timer1, operations that clear the Watchdog  |

|       | Timer (CLRWDT, SLEEP instructions) will     |

|       | affect the time interval being measured for |

|       | capacitive sensing. This includes waking    |

|       | from Sleep. All other interrupts that might |

|       | wake the device from Sleep should be        |

|       | disabled to prevent them from disturbing    |

|       | the measurement period.                     |

As the gate signal coming from the WDT counter will generate different pulse widths depending on if the WDT is enabled, when the CLRWDT instruction is executed, and so on, Toggle mode must be used. A specific sequence is required to put the device into the correct state to capture the next WDT counter interval.

## 13.0 TIMER2 MODULE

The Timer2 module is an 8-bit timer with the following features:

- 8-bit timer register (TMR2)

- 8-bit period register (PR2)

- Interrupt on TMR2 match with PR2

- Software programmable prescaler (1:1, 1:4, 1:16)

- Software programmable postscaler (1:1 to 1:16)

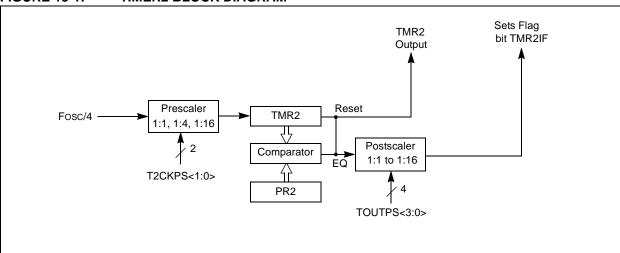

See Figure 13-1 for a block diagram of Timer2.

#### 13.1 Timer2 Operation

The clock input to the Timer2 module is the system instruction clock (Fosc/4). The clock is fed into the Timer2 prescaler, which has prescale options of 1:1, 1:4 or 1:16. The output of the prescaler is then used to increment the TMR2 register.

The values of TMR2 and PR2 are constantly compared to determine when they match. TMR2 will increment from 00h until it matches the value in PR2. When a match occurs, two things happen:

- TMR2 is reset to 00h on the next increment cycle.

- The Timer2 postscaler is incremented.

The match output of the Timer2/PR2 comparator is then fed into the Timer2 postscaler. The postscaler has postscale options of 1:1 to 1:16 inclusive. The output of the Timer2 postscaler is used to set the TMR2IF interrupt flag bit in the PIR1 register.

FIGURE 13-1: TIMER2 BLOCK DIAGRAM

The TMR2 and PR2 registers are both fully readable and writable. On any Reset, the TMR2 register is set to 00h and the PR2 register is set to FFh.

Timer2 is turned on by setting the TMR2ON bit in the T2CON register to a '1'. Timer2 is turned off by clearing the TMR2ON bit to a '0'.

The Timer2 prescaler is controlled by the T2CKPS bits in the T2CON register. The Timer2 postscaler is controlled by the TOUTPS bits in the T2CON register. The prescaler and postscaler counters are cleared when:

- A write to TMR2 occurs.

- A write to T2CON occurs.

- Any device Reset occurs (Power-on Reset, MCLR Reset, Watchdog Timer Reset, or Brown-out Reset).

Note: TMR2 is not cleared when T2CON is written.

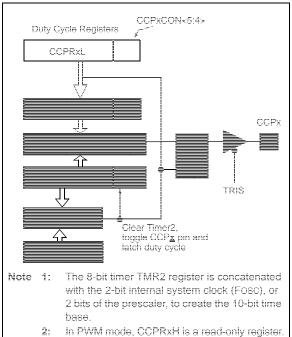

#### 15.3 PWM Mode

The PWM mode generates a Pulse-Width Modulated signal on the CCPx pin. The duty cycle, period and resolution are determined by the following registers:

- PR2

- T2CON

- CCPRxL

- CCPxCON

In Pulse-Width Modulation (PWM) mode, the CCP module produces up to a 10-bit resolution PWM output on the CCPx pin.

Figure 15-3 shows a simplified block diagram of PWM operation.

Figure 15-4 shows a typical waveform of the PWM signal.

For a step-by-step procedure on how to set up the CCP module for PWM operation, refer to **Section 15.3.8** "Setup for PWM Operation".

FIGURE 15-3: SIMPLIFIED PWM BLOCK DIAGRAM

The PWM output (Figure 15-4) has a time base (period) and a time that the output stays high (duty cycle).

FIGURE 15-4: CCP PWM OUTPUT

#### 15.3.1 CCPX PIN CONFIGURATION

In PWM mode, the CCPx pin is multiplexed with the PORT data latch. The user must configure the CCPx pin as an output by clearing the associated TRIS bit.

Either RC1 or RB3 can be selected as the CCP2 pin. Refer to **Section 6.1** "Alternate Pin Function" for more information.

| Note: | Clearing   | the | CCPxCON         | register  | will |

|-------|------------|-----|-----------------|-----------|------|

|       | relinquish | CCP | x control of th | ne CCPx j | oin. |

| FIGURE 16-8:            | SYNCHRONOUS RECEPTION (MASTER MODE, SREN)                                          |     |

|-------------------------|------------------------------------------------------------------------------------|-----|

| RX/DT<br>pin            | bit 0 bit 1 bit 2 bit 3 bit 4 bit 5 bit 6 bit 7                                    |     |

| TX/CK pin               |                                                                                    |     |

| Write to<br>bit SREN    |                                                                                    |     |

| SREN bit                | l                                                                                  |     |

| CREN bit <u>'</u> 0'    |                                                                                    | ʻ0' |

| RCIF bit<br>(Interrupt) |                                                                                    |     |

| Read<br>RCREG           |                                                                                    |     |

| Note: Timing d          | iagram demonstrates Synchronous Master mode with bit SREN = 1 and bit BRGH = $0$ . |     |

| Name   | Bit 7                             | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-----------------------------------|--------|--------|--------|--------|--------|--------|-----------|----------------------|---------------------------------|

| INTCON | GIE                               | PEIE   | TOIE   | INTE   | RBIE   | T0IF   | INTF   | RBIF      | 0000 000x            | 0000 000x                       |

| PIE1   | TMR1GIE                           | ADIE   | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE    | 0000 0000            | 0000 0000                       |

| PIR1   | TMR1GIF                           | ADIF   | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF    | 0000 0000            | 0000 0000                       |

| RCREG  | CREG AUSART Receive Data Register |        |        |        |        |        |        | 0000 0000 | 0000 0000            |                                 |

| RCSTA  | SPEN                              | RX9    | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D      | 0000 000x            | 0000 000x                       |

| TRISC  | TRISC7                            | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0    | 1111 1111            | 1111 1111                       |

| TXSTA  | CSRC                              | TX9    | TXEN   | SYNC   | —      | BRGH   | TRMT   | TX9D      | 0000 -010            | 0000 -010                       |

#### TABLE 16-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for synchronous master reception.

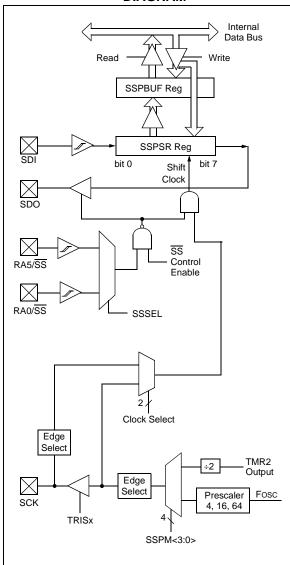

FIGURE 17-2: SPI MODE BLOCK DIAGRAM

| REGISTER 17-5: | SSPMSK: SSP MASK REGISTER |

|----------------|---------------------------|

|                |                           |

| R/W-1 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| MSK7  | MSK6  | MSK5  | MSK4  | MSK3  | MSK2  | MSK1  | MSK0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-1 | MSK<7:1>: Mask bits  |

|---------|----------------------|

|         | 1 - The received add |

| 1 = The received address bit n is compared to SSPADD <n> to detect I</n>            |   |

|-------------------------------------------------------------------------------------|---|

| 0 = The received address bit n is not used to detect I <sup>2</sup> C address match | ۱ |

#### bit 0 MSK<0>: Mask bit for I<sup>2</sup>C Slave Mode, 10-bit Address

I<sup>2</sup>C Slave Mode, 10-bit Address (SSPM<3:0> = 0111):

1 = The received address bit '0' is compared to SSPADD<0> to detect  $I^2C$  address match

0 = The received address bit '0' is not used to detect I<sup>2</sup>C address match

All other SSP modes: this bit has no effect.

## REGISTER 17-6: SSPADD: SSP I<sup>2</sup>C ADDRESS REGISTER

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| ADD7  | ADD6  | ADD5  | ADD4  | ADD3  | ADD2  | ADD1  | ADD0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

|       |       |       |       |       |       |       |       |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 7-0 ADD<7:0>: Address bits Received address

## TABLE 17-7: SUMMARY OF REGISTERS ASSOCIATED WITH I<sup>2</sup>C OPERATION

| Name                  | Bit 7                                                                 | Bit 6              | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register on<br>Page |

|-----------------------|-----------------------------------------------------------------------|--------------------|--------|--------|--------|--------|--------|--------|---------------------|

| INTCON                | GIE                                                                   | PEIE               | TOIE   | INTE   | RBIE   | TOIF   | INTF   | RBIF   | 36                  |

| PIR1                  | TMR1GIF                                                               | ADIF               | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 39                  |

| PIE1                  | TMR1GIE                                                               | ADIE               | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 37                  |

| SSPBUF                | Synchronous Serial Port Receive Buffer/Transmit Register              |                    |        |        |        |        | 147    |        |                     |

| SSPADD                | Synchronous Serial Port (I <sup>2</sup> C mode) Address Register      |                    |        |        |        |        | 155    |        |                     |

| SSPCON                | WCOL                                                                  | SSPOV              | SSPEN  | CKP    | SSPM3  | SSPM2  | SSPM1  | SSPM0  | 164                 |

| SSPMSK <sup>(2)</sup> | Synchronous Serial Port (I <sup>2</sup> C mode) Address Mask Register |                    |        |        |        |        | 166    |        |                     |

| SSPSTAT               | SMP <sup>(1)</sup>                                                    | CKE <sup>(1)</sup> | D/Ā    | Р      | S      | R/W    | UA     | BF     | 165                 |

| TRISC                 | TRISC7                                                                | TRISC6             | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 62                  |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by SSP module in I<sup>2</sup>C mode.

**Note 1:** Maintain these bits clear in  $I^2C$  mode.

**2:** Accessible only when SSPM < 3:0 > = 1001.

| MOVF             | Move f                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                            |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                   |  |  |  |  |  |

| Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                                             |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| Description:     | The contents of register f is<br>moved to a destination dependent<br>upon the status of d. If $d = 0$ ,<br>destination is W register. If $d = 1$ ,<br>the destination is file register f<br>itself. $d = 1$ is useful to test a file<br>register since status flag Z is<br>affected. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| Example:         | MOVF FSR, 0                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|                  | After Instruction<br>W = value in FSR<br>register<br>Z = 1                                                                                                                                                                                                                           |  |  |  |  |  |

| MOVWF            | Move W to f                                                                           |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] MOVWF f                                                                       |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$                                                                     |  |  |  |  |  |

| Operation:       | $(W) \rightarrow (f)$                                                                 |  |  |  |  |  |

| Status Affected: | None                                                                                  |  |  |  |  |  |

| Description:     | Move data from W register to<br>register 'f'.                                         |  |  |  |  |  |

| Words:           | 1                                                                                     |  |  |  |  |  |

| Cycles:          | 1                                                                                     |  |  |  |  |  |

| Example:         | MOVW OPTION<br>F                                                                      |  |  |  |  |  |

|                  | Before Instruction<br>OPTION = 0xFF<br>W = 0x4F<br>After Instruction<br>OPTION = 0x4F |  |  |  |  |  |

|                  | W = 0x4F                                                                              |  |  |  |  |  |

| MOVLW            | Move literal to W                                                                         |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                  |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                         |  |  |  |  |  |

| Operation:       | $k \rightarrow (W)$                                                                       |  |  |  |  |  |

| Status Affected: | None                                                                                      |  |  |  |  |  |

| Description:     | The 8-bit literal 'k' is loaded into W register. The "don't cares" will assemble as '0's. |  |  |  |  |  |

| Words:           | 1                                                                                         |  |  |  |  |  |

| Cycles:          | 1                                                                                         |  |  |  |  |  |

| Example:         | MOVLW 0x5A                                                                                |  |  |  |  |  |

|                  | After Instruction<br>W = 0x5A                                                             |  |  |  |  |  |

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| Words:           | 1             |

| Cycles:          | 1             |

| Example:         | NOP           |

## 23.7 AC Characteristics: PIC16F722A/723A-I/E

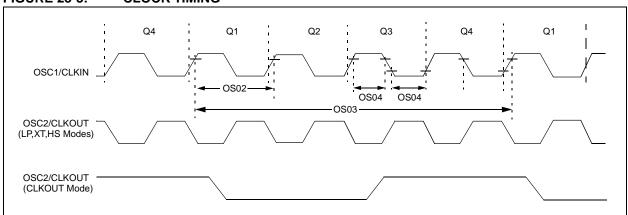

#### FIGURE 23-3: CLOCK TIMING

| Param.<br>No. | Symbol                        | Characteristic             |               | Min.          | Max. | Units                                    | Conditions                                  |

|---------------|-------------------------------|----------------------------|---------------|---------------|------|------------------------------------------|---------------------------------------------|

| SP100* Thigh  |                               | Clock high time            | 100 kHz mode  | 4.0           |      | μS                                       | Device must operate at a minimum of 1.5 MHz |

|               |                               |                            | 400 kHz mode  | 0.6           | -    | μS                                       | Device must operate at a minimum of 10 MHz  |

|               |                               |                            | SSP Module    | 1.5Tcy        | —    |                                          |                                             |

| SP101*        | TLOW                          | Clock low time             | 100 kHz mode  | 4.7           | —    | μS                                       | Device must operate at a minimum of 1.5 MHz |

|               |                               |                            | 400 kHz mode  | 1.3           | —    | μS                                       | Device must operate at a minimum of 10 MHz  |

|               |                               |                            | SSP Module    | 1.5Tcy        | —    |                                          |                                             |

| SP102*        | SP102* TR                     | SDA and SCL rise           | 100 kHz mode  | —             | 1000 | ns                                       |                                             |

|               | time                          | 400 kHz mode               | 20 +<br>0.1Св | 300           | ns   | CB is specified to be from 10-400 pF     |                                             |

| SP103*        | P103* TF                      | SDA and SCL fall           | 100 kHz mode  | —             | 250  | ns                                       |                                             |

|               |                               | time                       | 400 kHz mode  | 20 +<br>0.1Св | 250  | ns                                       | CB is specified to be from 10-400 pF        |

| SP106*        | THD:DAT                       | Data input hold time       | 100 kHz mode  | 0             | _    | ns                                       |                                             |

|               |                               |                            | 400 kHz mode  | 0             | 0.9  | μs                                       |                                             |

| SP107*        | SP107* TSU:DAT                | Data input setup time      | 100 kHz mode  | 250           | —    | ns                                       | (Note 2)                                    |

|               |                               |                            | 400 kHz mode  | 100           | —    | ns                                       |                                             |

| SP109*        | ΤΑΑ                           | Output valid from<br>clock | 100 kHz mode  | —             | 3500 | ns                                       | (Note 1)                                    |

|               |                               |                            | 400 kHz mode  | —             | _    | ns                                       |                                             |

| SP110* TBUF   | Bus free time                 | 100 kHz mode               | 4.7           | _             | μs   | Time the bus must be free                |                                             |

|               |                               | 400 kHz mode               | 1.3           | —             | μS   | before a new transmis-<br>sion can start |                                             |

| SP111         | 111 CB Bus capacitive loading |                            | —             | 400           | pF   |                                          |                                             |

## TABLE 23-13: I<sup>2</sup>C BUS DATA REQUIREMENTS

\* These parameters are characterized but not tested.

**Note 1:** As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of Start or Stop conditions.

**2:** A Fast mode (400 kHz)  $I^2C$  bus device can be used in a Standard mode (100 kHz)  $I^2C$  bus system, but the requirement TsU:DAT  $\ge$  250 ns must then be met. This will automatically be the case if the device does not stretch the low period of the SCL signal. If such a device does stretch the low period of the SCL signal, it must output the next data bit to the SDA line TR max. + TSU:DAT = 1000 + 250 = 1250 ns (according to the Standard mode  $I^2C$  bus specification), before the SCL line is released.

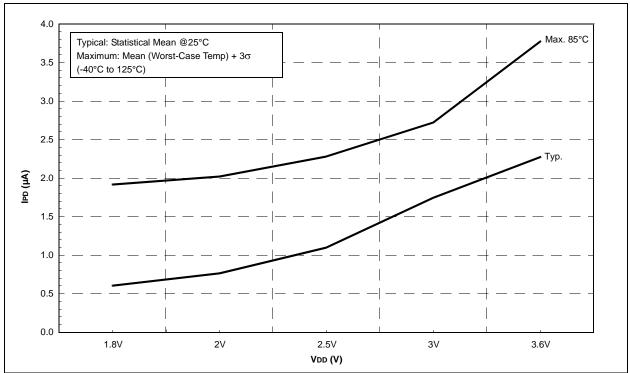

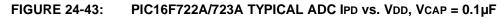

## FIGURE 24-42: PIC16LF722A/723A T1OSC 32 kHz IPD vs. VDD

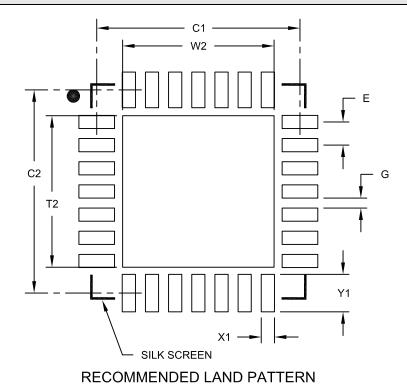

## 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS |          |      |      |

|----------------------------|-------------|----------|------|------|

| Dimensior                  | MIN         | NOM      | MAX  |      |

| Contact Pitch              | E           | 0.65 BSC |      |      |

| Optional Center Pad Width  | W2          |          |      | 4.25 |

| Optional Center Pad Length | T2          |          |      | 4.25 |

| Contact Pad Spacing        | C1          |          | 5.70 |      |

| Contact Pad Spacing        | C2          |          | 5.70 |      |

| Contact Pad Width (X28)    | X1          |          |      | 0.37 |

| Contact Pad Length (X28)   | Y1          |          |      | 1.00 |

| Distance Between Pads      | G           | 0.20     |      |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2105A