Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

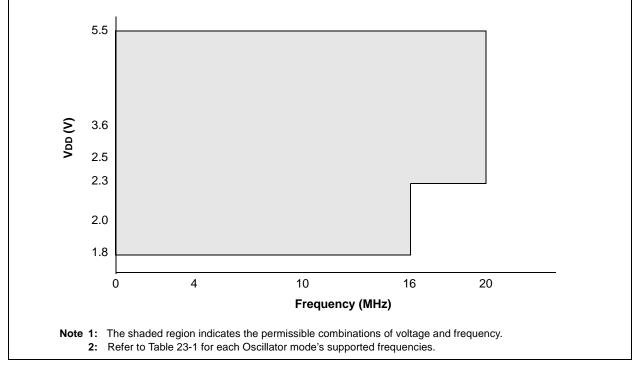

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

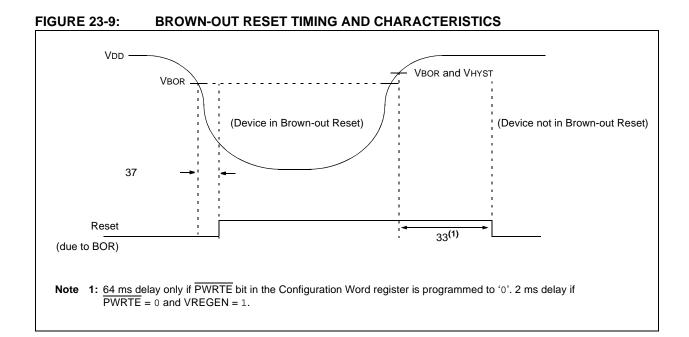

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

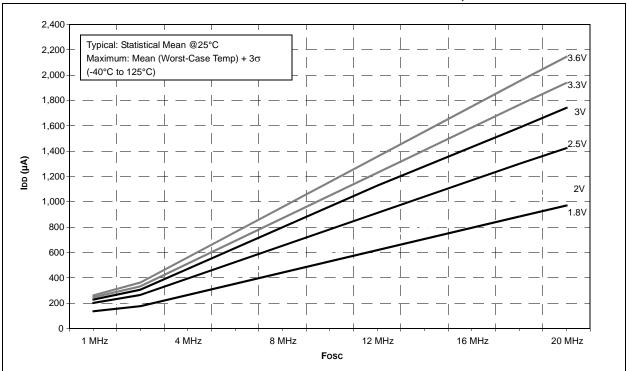

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 11x8b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf722a-i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1.0 DEVICE OVERVIEW

The PIC16(L)F722A/723A devices are covered by this data sheet. They are available in 28-pin packages. Figure 1-1 shows a block diagram of the PIC16(L)F722A/723A devices. Table 1-1 shows the pinout descriptions.

#### FIGURE 2-3:

#### PIC16(L)F722A SPECIAL FUNCTION REGISTERS

| Indirect addr.(*)  | 00h | Indirect addr. <sup>(*)</sup>              | 80h       | Indirect addr. <sup>(*)</sup> | 100h | Indirect addr.(*)   | 180h |

|--------------------|-----|--------------------------------------------|-----------|-------------------------------|------|---------------------|------|

| TMR0               | 01h | OPTION                                     | 81h       | TMR0                          | 101h | OPTION              | 181h |

| PCL                | 02h | PCL                                        | 82h       | PCL                           | 102h | PCL                 | 182h |

| STATUS             | 03h | STATUS                                     | 83h       | STATUS                        | 103h | STATUS              | 183h |

| FSR                | 04h | FSR                                        | 84h       | FSR                           | 104h | FSR                 | 184h |

| PORTA              | 05h | TRISA                                      | 85h       |                               | 105h | ANSELA              | 185h |

| PORTB              | 06h | TRISB                                      | 86h       |                               | 106h | ANSELB              | 186h |

| PORTC              | 07h | TRISC                                      | 87h       |                               | 107h |                     | 187h |

|                    | 08h |                                            | 88h       | CPSCON0                       | 108h |                     | 188h |

| PORTE              | 09h | TRISE                                      | 89h       | CPSCON1                       | 109h |                     | 189h |

| PCLATH             | 0Ah | PCLATH                                     | 8Ah       | PCLATH                        | 10Ah | PCLATH              | 18Ah |

| INTCON             | 0Bh | INTCON                                     | 8Bh       | INTCON                        | 10Bh | INTCON              | 18Bh |

| PIR1               | 0Ch | PIE1                                       | 8Ch       | PMDATL                        | 10Ch | PMCON1              | 18Ch |

| PIR2               | 0Dh | PIE2                                       | 8Dh       | PMADRL                        | 10Dh | Reserved            | 18Dh |

| TMR1L              | 0Eh | PCON                                       | 8Eh       | PMDATH                        | 10Eh | Reserved            | 18Eh |

| TMR1H              | 0Fh | T1GCON                                     | 8Fh       | PMADRH                        | 10Fh | Reserved            | 18Fh |

| T1CON              | 10h | OSCCON                                     | 90h       |                               | 110h |                     | 190h |

| TMR2               | 11h | OSCTUNE                                    | 91h       |                               | 111h |                     | 191h |

| T2CON              | 12h | PR2                                        | 92h       |                               | 112h |                     | 192h |

| SSPBUF             | 13h | SSPADD/SSPMSK                              | 93h       |                               | 113h |                     | 193h |

| SSPCON             | 14h | SSPSTAT                                    | 94h       |                               | 114h |                     | 194h |

| CCPR1L             | 15h | WPUB                                       | 95h       |                               | 115h |                     | 195h |

| CCPR1H             | 16h | IOCB                                       | 96h       |                               | 116h |                     | 196h |

| CCP1CON            | 17h |                                            | 97h       |                               | 117h |                     | 197h |

| RCSTA              | 18h | TXSTA                                      | 98h       |                               | 118h |                     | 198h |

| TXREG              | 19h | SPBRG                                      | 99h       |                               | 119h |                     | 199h |

| RCREG              | 1Ah |                                            | 9Ah       |                               | 11Ah |                     | 19Ah |

| CCPR2L             | 1Bh |                                            | 9Bh       |                               | 11Bh |                     | 19Bh |

| CCPR2H             | 1Ch | APFCON                                     | 9Ch       |                               | 11Ch |                     | 19Ch |

| CCP2CON            | 1Dh | FVRCON                                     | 9Dh       |                               | 11Dh |                     | 19Dh |

| ADRES              | 1Eh |                                            | 9Eh       |                               | 11Eh |                     | 19Eh |

| ADCON0             | 1Fh | ADCON1                                     | 9Fh       |                               | 11Fh |                     | 19Fh |

|                    | 20h |                                            | A0h       |                               | 120h |                     | 1A0h |

| General<br>Purpose |     | General<br>Purpose<br>Register<br>32 Bytes | BFh       |                               |      |                     |      |

| Register           |     |                                            | C0h       |                               |      |                     |      |

| 96 Bytes           |     |                                            | EFh       |                               | 16Fh |                     | 1EFh |

| -                  |     |                                            | F0h       |                               | 170h |                     | 1F0h |

|                    |     | Accesses<br>70h-7Fh                        |           | Accesses<br>70h-7Fh           |      | Accesses<br>70h-7Fh |      |

|                    | 7Fh |                                            | FFh       |                               | 17Fh |                     | 1FFh |

| Bank 0             |     | Bank 1                                     |           | Bank 2                        |      | Bank 3              |      |

|                    |     | nted data memory loc<br>cal register.      | ations, I | read as '0'.                  |      |                     |      |

#### 6.2 PORTA and the TRISA Registers

PORTA is a 8-bit wide, bidirectional port. The corresponding data direction register is TRISA (Register 6-3). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). Example 6-1 shows how to initialize PORTA.

Reading the PORTA register (Register 6-2) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch.

The TRISA register (Register 6-3) controls the PORTA pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the

**REGISTER 6-2:** PORTA: PORTA REGISTER R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x R/W-x RA6 RA5 RA2 RA7 RA4 RA3 RA1 RA0 bit 7 bit 0

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 RA<7:0>: PORTA I/O Pin bit

1 = Port pin is > VIH 0 = Port pin is < VIL

#### REGISTER 6-3: TRISA: PORTA TRI-STATE REGISTER

| R/W-1  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 7-0 TRISA<7:0>: PORTA Tri-State Control bit

1 = PORTA pin configured as an input (tri-stated)

0 = PORTA pin configured as an output

TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

| Note: | The ANSELA register must be initialized     |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|

|       | to configure an analog channel as a digital |  |  |  |  |  |

|       | input. Pins configured as analog inputs     |  |  |  |  |  |

|       | will read '0'.                              |  |  |  |  |  |

| BANKSEL PORTA ;<br>CLRF PORTA ;Init PORTA<br>BANKSEL ANSELA ;<br>CLRF ANSELA ;digital I/O<br>BANKSEL TRISA ;<br>MOVLW 0Ch ;Set RA<3:2> as inputs<br>MOVWF TRISA ;and set RA<7:4,1:0> | EXAMPLE 6-1:                                                              | INITIALIZING PORTA                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------|

| , as outputs                                                                                                                                                                         | CLRF PORTA<br>BANKSEL ANSELA<br>CLRF ANSELA<br>BANKSEL TRISA<br>MOVLW OCh | ;Init PORTA<br>;<br>;digital I/O<br>;<br>;Set RA<3:2> as inputs |

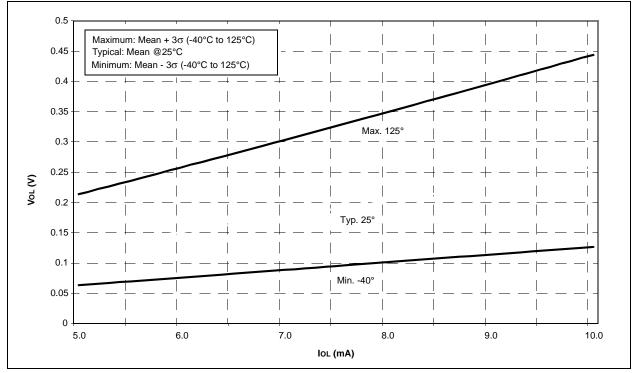

#### 6.5.1 RE3/MCLR/VPP

Figure 6-21 shows the diagram for this pin. This pin is configurable to function as one of the following:

- General purpose input

- Master Clear Reset with weak pull up

- Programming voltage reference input

#### FIGURE 6-21: BLOCK DIAGRAM OF RE3

### 7.0 OSCILLATOR MODULE

#### 7.1 Overview

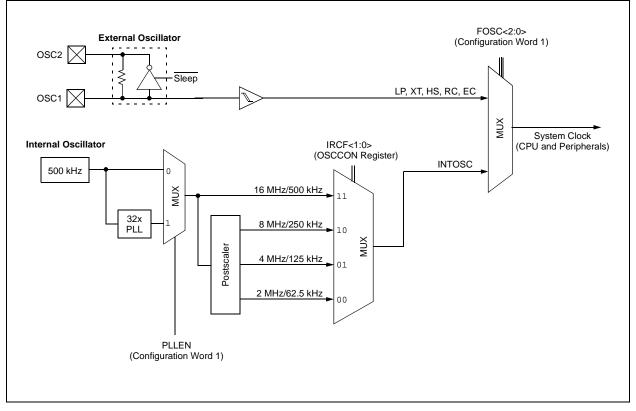

The oscillator module has a wide variety of clock sources and selection features that allow it to be used in a wide range of applications while maximizing performance and minimizing power consumption. Figure 7-1 illustrates a block diagram of the oscillator module.

Clock sources can be configured from external oscillators, quartz crystal resonators, ceramic resonators and Resistor-Capacitor (RC) circuits. In addition, the system can be configured to use an internal calibrated high-frequency oscillator as clock source, with a choice of selectable speeds via software.

Clock source modes are configured by the FOSC bits in Configuration Word 1 (CONFIG1). The oscillator module can be configured for one of eight modes of operation.

- 1. RC External Resistor-Capacitor (RC) with Fosc/4 output on OSC2/CLKOUT.

- 2. RCIO External Resistor-Capacitor (RC) with I/O on OSC2/CLKOUT.

- 3. INTOSC Internal oscillator with Fosc/4 output on OSC2 and I/O on OSC1/CLKIN.

- 4. INTOSCIO Internal oscillator with I/O on OSC1/CLKIN and OSC2/CLKOUT.

- 5. EC External clock with I/O on OSC2/CLKOUT.

- HS High Gain Crystal or Ceramic Resonator mode.

- 7. XT Medium Gain Crystal or Ceramic Resonator Oscillator mode.

- 8. LP Low-Power Crystal mode.

FIGURE 7-1: SIMPLIFIED PIC<sup>®</sup> MCU CLOCK SOURCE BLOCK DIAGRAM

#### 7.4 Oscillator Control

The Oscillator Control (OSCCON) register (Figure 7-1) displays the status and allows frequency selection of the internal oscillator (INTOSC) system clock. The OSCCON register contains the following bits:

- Frequency selection bits (IRCF)

- Status Locked bits (ICSL)

- Status Stable bits (ICSS)

#### REGISTER 7-1: OSCCON: OSCILLATOR CONTROL REGISTER

| U-0     | U-0 | R/W-1 | R/W-0 | R-q  | R-q  | U-0 | U-0   |

|---------|-----|-------|-------|------|------|-----|-------|

|         | —   | IRCF1 | IRCF0 | ICSL | ICSS |     | _     |

| bit 7   |     |       |       |      |      |     | bit 0 |

|         |     |       |       |      |      |     |       |

| Legend: |     |       |       |      |      |     |       |

| R = Readable bit       | W = Writable bit | U = Unimplemented bit | , read as '0'      |  |

|------------------------|------------------|-----------------------|--------------------|--|

| -n = Value at POR      | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |  |

| q = Value depends on c | ondition         |                       |                    |  |

| bit 7-6 | Unimplemented: Read as '0'                                                               |

|---------|------------------------------------------------------------------------------------------|

| bit 5-4 | IRCF<1:0>: Internal Oscillator Frequency Select bits                                     |

|         | <u>When PLLEN = 1 (16 MHz INTOSC)</u>                                                    |

|         | 11 <b>= 16 MHz</b>                                                                       |

|         | 10 = 8 MHz (POR value)                                                                   |

|         | 01 = 4  MHz                                                                              |

|         | 00 = 2 MHz                                                                               |

|         | $\frac{\text{When PLLEN} = 0 (500 \text{ kHz INTOSC})}{11 - 500 \text{ kHz}}$            |

|         | 11 = 500 kHz                                                                             |

|         | 10 = 250 kHz (POR value)<br>01 = 125 kHz                                                 |

|         | 01 = 125  kHz<br>00 = 62.5  kHz                                                          |

| h it 0  |                                                                                          |

| bit 3   | ICSL: Internal Clock Oscillator Status Locked bit (2% Stable)                            |

|         | 1 = 16 MHz/500 kHz Internal Oscillator (HFIOSC) is in lock                               |

|         | 0 = 16 MHz/500 kHz Internal Oscillator (HFIOSC) has not yet locked                       |

| bit 2   | ICSS: Internal Clock Oscillator Status Stable bit (0.5% Stable)                          |

|         | 1 = 16 MHz/500 kHz Internal Oscillator (HFIOSC) has stabilized to its maximum accuracy   |

|         | 0 = 16 MHz/500 kHz Internal Oscillator (HFIOSC) has not yet reached its maximum accuracy |

| bit 1-0 | Unimplemented: Read as '0'                                                               |

|         |                                                                                          |

#### 12.6 Timer1 Gate

Timer1 can be configured to count freely or the count can be enabled and disabled using Timer1 gate circuitry. This is also referred to as Timer1 Gate Count Enable.

Timer1 gate can also be driven by multiple selectable sources.

#### 12.6.1 TIMER1 GATE COUNT ENABLE

The Timer1 gate is enabled by setting the TMR1GE bit of the T1GCON register. The polarity of the Timer1 gate is configured using the T1GPOL bit of the T1GCON register.

When Timer1 Gate (T1G) input is active, Timer1 will increment on the rising edge of the Timer1 clock source. When Timer1 gate input is inactive, no incrementing will occur and Timer1 will hold the current count. See Figure 12-4 for timing details.

### TABLE 12-3: TIMER1 GATE ENABLE SELECTIONS

| T1CLK      | T1GPOL | T1G Timer1 Operation |             |

|------------|--------|----------------------|-------------|

| 1          | 0      | 0                    | Counts      |

| $\uparrow$ | 0      | 1                    | Holds Count |

| $\uparrow$ | 1      | 0                    | Holds Count |

| $\uparrow$ | 1      | 1                    | Counts      |

#### 12.6.2 TIMER1 GATE SOURCE SELECTION

The Timer1 gate source can be selected from one of four different sources. Source selection is controlled by the T1GSS bits of the T1GCON register. The polarity for each available source is also selectable. Polarity selection is controlled by the T1GPOL bit of the T1GCON register.

#### TABLE 12-4: TIMER1 GATE SOURCES

| T1GSS | Timer1 Gate Source                                                    |

|-------|-----------------------------------------------------------------------|

| 00    | Timer1 Gate Pin                                                       |

| 01    | Overflow of Timer0<br>(TMR0 increments from FFh to 00h)               |

| 10    | Timer2 match PR2<br>(TMR2 increments to match PR2)                    |

| 11    | Count Enabled by WDT Overflow<br>(Watchdog Time-out interval expired) |

#### 12.6.2.1 T1G Pin Gate Operation

The T1G pin is one source for Timer1 gate control. It can be used to supply an external source to the Timer1 gate circuitry.

#### 12.6.2.2 Timer0 Overflow Gate Operation

When Timer0 increments from FFh to 00h, a low-tohigh pulse will automatically be generated and internally supplied to the Timer1 gate circuitry.

#### 12.6.2.3 Timer2 Match Gate Operation

The TMR2 register will increment until it matches the value in the PR2 register. On the very next increment cycle, TMR2 will be reset to 00h. When this Reset occurs, a low-to-high pulse will automatically be generated and internally supplied to the Timer1 gate circuitry.

#### 12.6.2.4 Watchdog Overflow Gate Operation

The Watchdog Timer oscillator, prescaler and counter will be automatically turned on when TMR1GE = 1 and T1GSS selects the WDT as a gate source for Timer1 (T1GSS = 11). TMR1ON does not factor into the oscillator, prescaler and counter enable. See Table .

The PSA and PS bits of the OPTION register still control what time-out interval is selected. Changing the prescaler during operation may result in a spurious capture.

Enabling the Watchdog Timer oscillator does not automatically enable a Watchdog Reset or Wake-up from Sleep upon counter overflow.

| Note: | When using the WDT as a gate source for     |

|-------|---------------------------------------------|

|       | <b>.</b> .                                  |

|       | Timer1, operations that clear the Watchdog  |

|       | Timer (CLRWDT, SLEEP instructions) will     |

|       | affect the time interval being measured for |

|       | capacitive sensing. This includes waking    |

|       | from Sleep. All other interrupts that might |

|       | wake the device from Sleep should be        |

|       | disabled to prevent them from disturbing    |

|       | the measurement period.                     |

As the gate signal coming from the WDT counter will generate different pulse widths depending on if the WDT is enabled, when the CLRWDT instruction is executed, and so on, Toggle mode must be used. A specific sequence is required to put the device into the correct state to capture the next WDT counter interval.

| FIGURE 12-6:           | TIMER1 GATE SINGLE-PULSE MODE              |                                                                 |

|------------------------|--------------------------------------------|-----------------------------------------------------------------|

|                        |                                            |                                                                 |

| TMR1GE                 |                                            |                                                                 |

| T1GPOL                 |                                            |                                                                 |

| T1GSPM                 |                                            |                                                                 |

| T1GGO <u>/</u><br>DONE | ← Set by software ←<br>Counting enabled on | Cleared by hardware on falling edge of T1GVAL                   |

| T1G_IN                 | rising edge of T1G                         |                                                                 |

| T1CKI                  |                                            |                                                                 |

| T1GVAL                 |                                            |                                                                 |

| TIMER1                 | N + 1                                      | N + 2                                                           |

| TMR1GIF                | Cleared by software                        | — Set by hardware on falling edge of T1GVAL Cleared by software |

| REGISTER      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  |              |                  |                 |                 |        |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------|------------------|-----------------|-----------------|--------|

| U-0           | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W-0            | R/W-0        | R/W-0            | R/W-0           | R/W-0           | R/W-0  |

|               | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | DCxB1            | DCxB0        | CCPxM3           | CCPxM2          | CCPxM1          | CCPxM0 |

| bit 7         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  |              |                  |                 |                 | bit (  |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  |              |                  |                 |                 |        |

| Legend:       | 1.12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                  |              |                  |                 |                 |        |

| R = Readable  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | W = Writable bit |              | •                | nented bit, rea |                 |        |

| -n = Value at | POR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | '1' = Bit is set |              | '0' = Bit is cle | ared            | x = Bit is unki | nown   |

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  |              |                  |                 |                 |        |

| bit 7-6       | Unimplemen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ted: Read as '   | 0'           |                  |                 |                 |        |

|               | Capture mode<br>Unused<br>Compare mod<br>Unused<br><u>PWM mode:</u><br>These bits are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <u>de:</u>       | of the PWM c | luty cycle. The  | eight MSbs are  | e found in CCP  | RxL.   |

| bit 3-0       | <pre>CCPxM&lt;3:0&gt;: CCP Mode Select bits<br/>0000 = Capture/Compare/PWM Off (resets CCP module)<br/>0011 = Unused (reserved)<br/>0010 = Compare mode, toggle output on match (CCPxIF bit of the PIRx register is set)<br/>0011 = Unused (reserved)<br/>0100 = Capture mode, every falling edge<br/>0101 = Capture mode, every falling edge<br/>0111 = Capture mode, every 4th rising edge<br/>0111 = Capture mode, every 16th rising edge<br/>1000 = Compare mode, set output on match (CCPxIF bit of the PIRx register is set)<br/>1001 = Compare mode, clear output on match (CCPxIF bit of the PIRx register is set)<br/>1010 = Compare mode, generate software interrupt on match (CCPxIF bit is set of the PIRx register<br/>1010 = Compare mode, generate software interrupt on match (CCPxIF bit is set of the PIRx register<br/>1011 = Compare mode, trigger special event (CCPxIF bit of the PIRx register is set, TMR1 is r<br/>and A/D conversion<sup>(T)</sup> is started if the ADC module is enabled. CCPx pin is unaffected.)<br/>11xx = PWM mode.</pre> |                  |              |                  |                 | PIRx registe    |        |

#### REGISTER 15-1: CCPxCON: CCPx CONTROL REGISTER

**Note 1:** A/D conversion start feature is available only on CCP2.

#### 16.1.2.8 Asynchronous Reception Setup:

- Initialize the SPBRG register and the BRGH bit to achieve the desired baud rate (refer to Section 16.2 "AUSART Baud Rate Generator (BRG)").

- 2. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 3. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. If 9-bit reception is desired, set the RX9 bit.

- 5. Enable reception by setting the CREN bit.

- 6. The RCIF interrupt flag bit of the PIR1 register will be set when a character is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE bit of the PIE1 register was also set.

- 7. Read the RCSTA register to get the error flags and, if 9-bit data reception is enabled, the ninth data bit.

- 8. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register.

- 9. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

#### 16.1.2.9 9-bit Address Detection Mode Setup

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- Initialize the SPBRG register and the BRGH bit to achieve the desired baud rate (refer to Section 16.2 "AUSART Baud Rate Generator (BRG)").

- 2. Enable the serial port by setting the SPEN bit. The SYNC bit must be clear for asynchronous operation.

- 3. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. Enable 9-bit reception by setting the RX9 bit.

- 5. Enable address detection by setting the ADDEN bit.

- 6. Enable reception by setting the CREN bit.

- 7. The RCIF interrupt flag bit of the PIR1 register will be set when a character with the ninth bit set is transferred from the RSR to the receive buffer. An interrupt will be generated if the RCIE interrupt enable bit of the PIE1 register was also set.

- 8. Read the RCSTA register to get the error flags. The ninth data bit will always be set.

- 9. Get the received eight Least Significant data bits from the receive buffer by reading the RCREG register. Software determines if this is the device's address.

- 10. If an overrun occurred, clear the OERR flag by clearing the CREN receiver enable bit.

- 11. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and generate interrupts.

#### **FIGURE 16-5: ASYNCHRONOUS RECEPTION** Start Start Star bit 7/8/ Stop Stop RX/DT pin bit ΄bit 0 🗙 bit 1 (bit 7/8/ bit 7/8/ Stop bit bit bit 0 bit bit Rcv Shift Reg → Rcv Buffer Reg Word 2 RCREG Word 1 RCREG Read Rcv Buffer Reg RCREG RCIF (Interrupt Flag) OFRR bit CREN This timing diagram shows three words appearing on the RX input. The RCREG (receive buffer) is read after the third word, Note: causing the OERR (overrun) bit to be set.

| Name   | Bit 7                        | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2     | Bit 1     | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|------------------------------|--------|--------|--------|--------|-----------|-----------|--------|----------------------|---------------------------------|

| INTCON | GIE                          | PEIE   | TOIE   | INTE   | RBIE   | T0IF      | INTF      | RBIF   | 0000 000x            | 0000 000x                       |

| PIE1   | TMR1GIE                      | ADIE   | RCIE   | TXIE   | SSPIE  | CCP1IE    | TMR2IE    | TMR1IE | 0000 0000            | 0000 0000                       |

| PIR1   | TMR1GIF                      | ADIF   | RCIF   | TXIF   | SSPIF  | CCP1IF    | TMR2IF    | TMR1IF | 0000 0000            | 0000 0000                       |

| RCREG  | AUSART Receive Data Register |        |        |        |        | 0000 0000 | 0000 0000 |        |                      |                                 |

| RCSTA  | SPEN                         | RX9    | SREN   | CREN   | ADDEN  | FERR      | OERR      | RX9D   | 0000 000x            | 0000 000x                       |

| SPBRG  | BRG7                         | BRG6   | BRG5   | BRG4   | BRG3   | BRG2      | BRG1      | BRG0   | 0000 0000            | 0000 0000                       |

| TRISC  | TRISC7                       | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2    | TRISC1    | TRISC0 | 1111 1111            | 1111 1111                       |

| TXSTA  | CSRC                         | TX9    | TXEN   | SYNC   | —      | BRGH      | TRMT      | TX9D   | 0000 -010            | 0000 -010                       |

#### TABLE 16-2: REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for asynchronous reception.

| Mnemonic,<br>Operands                  |      | Description                  | Cycles       | 14-Bit |      |      | e    | Status   |         |

|----------------------------------------|------|------------------------------|--------------|--------|------|------|------|----------|---------|

|                                        |      | Description                  | Cycles       | MSb    |      |      | LSb  | Affected | Notes   |

| BYTE-ORIENTED FILE REGISTER OPERATIONS |      |                              |              |        |      |      |      |          |         |

| ADDWF                                  | f, d | Add W and f                  | 1            | 00     | 0111 | dfff | ffff | C, DC, Z | 1, 2    |

| ANDWF                                  | f, d | AND W with f                 | 1            | 00     | 0101 | dfff | ffff | Z        | 1, 2    |

| CLRF                                   | f    | Clear f                      | 1            | 00     | 0001 | lfff | ffff | Z        | 2       |

| CLRW                                   | _    | Clear W                      | 1            | 00     | 0001 | 0xxx | xxxx | Z        |         |

| COMF                                   | f, d | Complement f                 | 1            | 00     | 1001 | dfff | ffff | Z        | 1, 2    |

| DECF                                   | f, d | Decrement f                  | 1            | 00     | 0011 | dfff | ffff | Z        | 1, 2    |

| DECFSZ                                 | f, d | Decrement f, Skip if 0       | 1 <b>(2)</b> | 00     | 1011 | dfff | ffff |          | 1, 2, 3 |

| INCF                                   | f, d | Increment f                  | 1            | 00     | 1010 | dfff | ffff | Z        | 1, 2    |

| INCFSZ                                 | f, d | Increment f, Skip if 0       | 1 <b>(2)</b> | 00     | 1111 | dfff | ffff |          | 1, 2, 3 |

| IORWF                                  | f, d | Inclusive OR W with f        | 1            | 00     | 0100 | dfff | ffff | Z        | 1, 2    |

| MOVF                                   | f, d | Move f                       | 1            | 00     | 1000 | dfff | ffff | Z        | 1, 2    |

| MOVWF                                  | f    | Move W to f                  | 1            | 00     | 0000 | lfff | ffff |          |         |

| NOP                                    | _    | No Operation                 | 1            | 00     | 0000 | 0xx0 | 0000 |          |         |

| RLF                                    | f, d | Rotate Left f through Carry  | 1            | 00     | 1101 | dfff | ffff | С        | 1, 2    |

| RRF                                    | f, d | Rotate Right f through Carry | 1            | 00     | 1100 | dfff | ffff | С        | 1, 2    |

| SUBWF                                  | f, d | Subtract W from f            | 1            | 00     | 0010 | dfff | ffff | C, DC, Z | 1, 2    |

| SWAPF                                  | f, d | Swap nibbles in f            | 1            | 00     | 1110 | dfff | ffff |          | 1, 2    |

| XORWF                                  | f, d | Exclusive OR W with f        | 1            | 00     | 0110 | dfff | ffff | Z        | 1, 2    |

|                                        |      | BIT-ORIENTED FILE REGIS      |              |        | NS   |      |      |          |         |

| BCF                                    | f, b | Bit Clear f                  | 1            | 01     | 00bb | bfff | ffff |          | 1, 2    |

| BSF                                    | f, b | Bit Set f                    | 1            | 01     | 01bb | bfff | ffff |          | 1, 2    |

| BTFSC                                  | f, b | Bit Test f, Skip if Clear    | 1 (2)        | 01     | 10bb | bfff | ffff |          | 3       |

| BTFSS                                  | f, b | Bit Test f, Skip if Set      | 1 (2)        | 01     | 11bb | bfff | ffff |          | 3       |

|                                        |      | LITERAL AND CONTRO           | L OPERAT     | IONS   |      |      |      |          |         |

| ADDLW                                  | k    | Add literal and W            | 1            | 11     | 111x | kkkk | kkkk | C, DC, Z |         |

| ANDLW                                  | k    | AND literal with W           | 1            | 11     | 1001 | kkkk | kkkk | Z        |         |

| CALL                                   | k    | Call Subroutine              | 2            | 10     | 0kkk | kkkk | kkkk |          |         |

| CLRWDT                                 | _    | Clear Watchdog Timer         | 1            | 00     | 0000 | 0110 | 0100 | TO, PD   |         |

| GOTO                                   | k    | Go to address                | 2            | 10     | 1kkk | kkkk | kkkk |          |         |

| IORLW                                  | k    | Inclusive OR literal with W  | 1            | 11     | 1000 | kkkk | kkkk | Z        |         |

| MOVLW                                  | k    | Move literal to W            | 1            | 11     | 00xx | kkkk | kkkk |          |         |

| RETFIE                                 | -    | Return from interrupt        | 2            | 00     | 0000 | 0000 | 1001 |          |         |

| RETLW                                  | k    | Return with literal in W     | 2            | 11     | 01xx | kkkk | kkkk |          |         |

| RETURN                                 | -    | Return from Subroutine       | 2            | 00     | 0000 | 0000 | 1000 |          |         |

| SLEEP                                  | -    | Go into Standby mode         | 1            | 00     | 0000 | 0110 | 0011 | TO, PD   |         |

| SUBLW                                  | k    | Subtract W from literal      | 1            | 11     | 110x | kkkk | kkkk | C, DC, Z |         |

| XORLW                                  | k    | Exclusive OR literal with W  | 1            | 11     | 1010 | kkkk | kkkk | Z        |         |

#### TABLE 21-2: PIC16(L)F722A/723A INSTRUCTION SET

**Note 1:** When an I/O register is modified as a function of itself (e.g., MOVF PORTA, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 module.

**3:** If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

| SUBWF            | Subtract W                                                      | from f                                                                                                                      |  |

|------------------|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:          | [label] SU                                                      | JBWF f,d                                                                                                                    |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$ |                                                                                                                             |  |

| Operation:       | (f) - (W) $\rightarrow$ (                                       | destination)                                                                                                                |  |

| Status Affected: | C, DC, Z                                                        |                                                                                                                             |  |

| Description:     | W register f<br>'0', the resu<br>register. If 'd                | s complement method)<br>rom register 'f'. If 'd' is<br>It is stored in the W<br>d' is '1', the result is<br>in register 'f. |  |

|                  | <b>C</b> = 0                                                    | W > f                                                                                                                       |  |

|                  | <b>C</b> = 1                                                    | $W \leq f$                                                                                                                  |  |

$\overline{DC} = 0$

**DC** = 1

W<3:0> > f<3:0> W<3:0>  $\leq$  f<3:0>

| XORLW            | Exclusive OR literal with W                                                                                            |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                               |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                    |  |  |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                          |  |  |  |

| Status Affected: | Z                                                                                                                      |  |  |  |

| Description:     | The contents of the W register<br>are XOR'ed with the 8-bit<br>literal 'k'. The result is placed in<br>the W register. |  |  |  |

| SWAPF            | Swap Nibbles in f                                                                                                                                                      |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SWAPF f,d                                                                                                                                                      |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                            |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                                |

| Status Affected: | None                                                                                                                                                                   |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed in register 'f'. |

| XORWF            | Exclusive OR W with f                                                                                                                                                           |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                      |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                     |  |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                       |  |  |  |

| Status Affected: | Z                                                                                                                                                                               |  |  |  |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |  |  |  |

#### 22.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

### 22.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

#### 23.7 AC Characteristics: PIC16F722A/723A-I/E

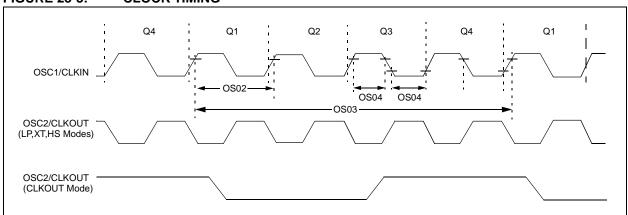

#### FIGURE 23-3: CLOCK TIMING

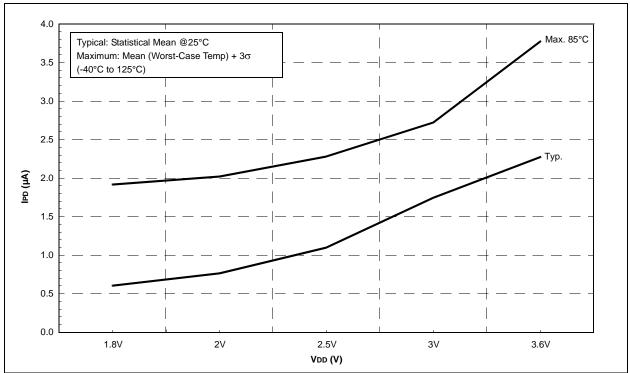

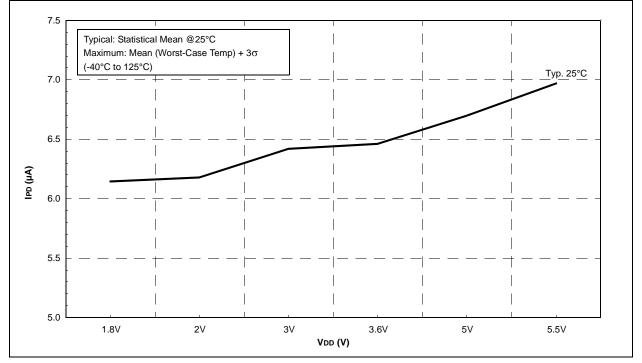

### FIGURE 24-42: PIC16LF722A/723A T1OSC 32 kHz IPD vs. VDD