Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                |                                                                             |

| RAM Size                   | 128 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 11x8b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-UQFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf722at-i-mv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

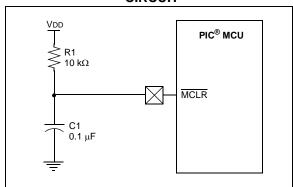

## 3.1 MCLR

The PIC16(L)F722A/723A has a noise filter in the  $\overline{\text{MCLR}}$  Reset path. The filter will detect and ignore small pulses.

It should be noted that a Reset does not drive the MCLR pin low.

Voltages applied to the pin that exceed its specification can result in both MCLR Resets and excessive current beyond the device specification during the ESD event. For this reason, Microchip recommends that the MCLR pin no longer be tied directly to VDD. The use of an RC network, as shown in Figure 3-2, is suggested.

An internal  $\overline{\text{MCLR}}$  option is enabled by clearing the MCLRE bit in the Configuration Word register. When MCLRE = 0, the Reset signal to the chip is generated internally. When the MCLRE = 1, the RE3/MCLR pin becomes an external Reset input. In this mode, the RE3/MCLR pin has a weak pull up to VDD. In-Circuit Serial Programming is not affected by selecting the internal  $\overline{\text{MCLR}}$  option.

#### FIGURE 3-2: RECOMMENDED MCLR CIRCUIT

### 3.2 Power-on Reset (POR)

The on-chip POR circuit holds the chip in Reset until VDD has reached a high enough level for proper operation. A maximum rise time for VDD is required. See **Section 23.0 "Electrical Specifications"** for details. If the BOR is enabled, the maximum rise time specification does not apply. The BOR circuitry will keep the device in Reset until VDD reaches VBOR (see **Section 3.5** "**Brown-Out Reset (BOR)**").

When the device starts normal operation (exits the Reset condition), device operating parameters (i.e., voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

For additional information, refer to Application Note *AN607, Power-up Trouble Shooting* (DS00607).

## 3.3 Power-up Timer (PWRT)

The Power-up Timer provides a fixed 64 ms (nominal) time-out on power-up only, from POR or Brown-out Reset. The Power-up Timer operates from the WDT oscillator. For more information, see **Section 7.3** "Internal Clock Modes". The chip is kept in Reset as long as PWRT is active. The PWRT delay allows the VDD to rise to an acceptable level. A Configuration bit, PWRTE, can disable (if set) or enable (if cleared or programmed) the Power-up Timer. The Power-up Timer should be enabled when Brown-out Reset is enabled, although it is not required.

The Power-up Timer delay will vary from chip-to-chip and vary due to:

- VDD variation

- Temperature variation

- · Process variation

See DC parameters for details (Section 23.0 "Electrical Specifications").

Note: The Power-up Timer is enabled by the PWRTE bit in the Configuration Word.

## 3.4 Watchdog Timer (WDT)

The WDT has the following features:

- Shares an 8-bit prescaler with Timer0

- Time-out period is from 17 ms to 2.2 seconds, nominal

- Enabled by a Configuration bit

WDT is cleared under certain conditions described in Table 3-1.

#### 3.4.1 WDT OSCILLATOR

The WDT derives its time base from 31 kHz internal oscillator.

Note: When the Oscillator Start-up Timer (OST) is invoked, the WDT is held in Reset, because the WDT Ripple Counter is used by the OST to perform the oscillator delay count. When the OST count has expired, the WDT will begin counting (if enabled).

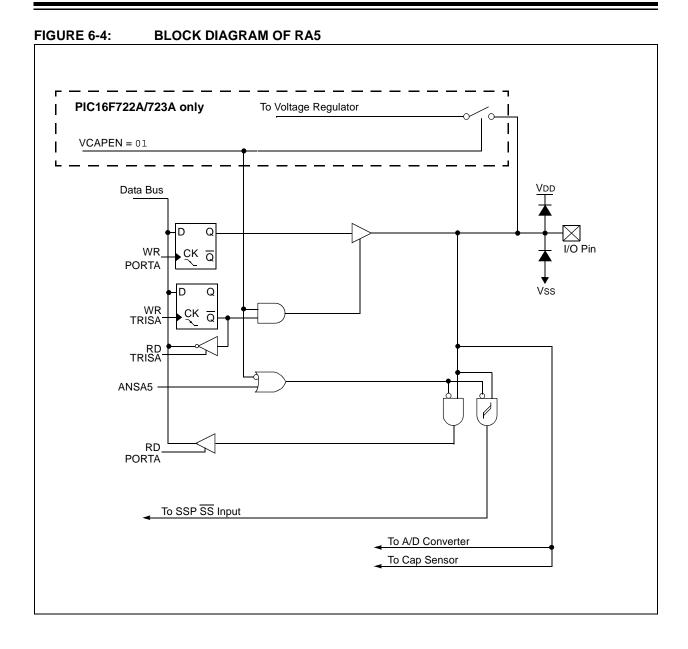

#### 6.2.1 ANSELA REGISTER

The ANSELA register (Register 6-4) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELA bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELA bits has no affect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

#### REGISTER 6-4: ANSELA: PORTA ANALOG SELECT REGISTER

'1' = Bit is set

| U-0          | U-0 | R/W-1        | R/W-1 | R/W-1        | R/W-1            | R/W-1    | R/W-1 |

|--------------|-----|--------------|-------|--------------|------------------|----------|-------|

| —            | —   | ANSA5        | ANSA4 | ANSA3        | ANSA2            | ANSA1    | ANSA0 |

| bit 7        |     |              |       |              |                  |          | bit 0 |

|              |     |              |       |              |                  |          |       |

| Legend:      |     |              |       |              |                  |          |       |

| R = Readable | bit | W = Writable | bit   | U = Unimpler | mented bit, read | l as '0' |       |

'0' = Bit is cleared

bit 7-6 Unimplemented: Read as '0'

-n = Value at POR

bit 5-0 **ANSA<5:0>**: Analog Select between Analog or Digital Function on pins RA<5:0>, respectively 0 = Digital I/O. Pin is assigned to port or digital special function. 1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

x = Bit is unknown

| R/W-x                          | R/W-x | R/W-x        | R/W-x | R/W-x        | R/W-x            | R/W-x  | R/W-x |

|--------------------------------|-------|--------------|-------|--------------|------------------|--------|-------|

| RB7                            | RB6   | RB5          | RB4   | RB3          | RB2              | RB1    | RB0   |

| bit 7                          |       |              |       |              |                  |        | bit 0 |

|                                |       |              |       |              |                  |        |       |

|                                |       |              |       |              |                  |        |       |

| Legend:                        |       |              |       |              |                  |        |       |

| <b>Legend:</b><br>R = Readable | bit   | W = Writable | bit   | U = Unimplen | nented bit, read | as '0' |       |

#### REGISTER 6-5: PORTB: PORTB REGISTER

bit 7-0 RB<7:0>: PORTB I/O Pin bits

1 = Port pin is > VIH

0 = Port pin is < VIL

#### REGISTER 6-6: TRISB: PORTB TRI-STATE REGISTER

| R/W-1  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0

**—**

TRISB<7:0>: PORTB Tri-State Control bits

1 = PORTB pin configured as an input (tri-stated)

0 = PORTB pin configured as an output

#### REGISTER 6-7: WPUB: WEAK PULL-UP PORTB REGISTER

| R/W-1 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| WPUB7 | WPUB6 | WPUB5 | WPUB4 | WPUB3 | WPUB2 | WPUB1 | WPUB0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 **WPUB<7:0>**: Weak Pull-up Register bits

1 = Pull up enabled

0 = Pull up disabled

**Note 1:** Global RBPU bit of the OPTION register must be cleared for individual pull ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is in configured as an output.

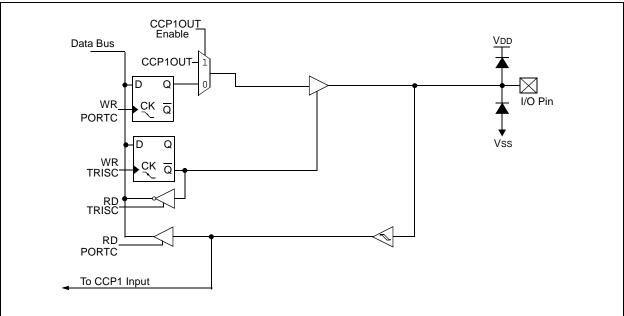

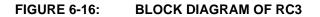

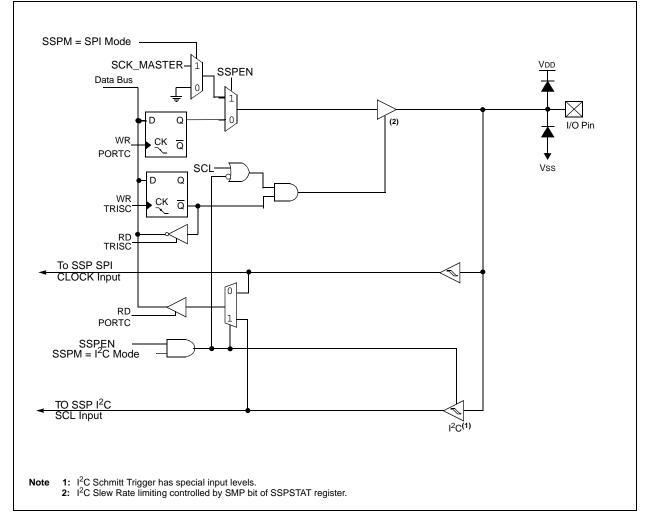

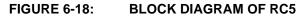

#### FIGURE 6-17: BLOCK DIAGRAM OF RC4

## 8.0 DEVICE CONFIGURATION

Device configuration consists of Configuration Word 1 and Configuration Word 2 registers, code protection and device ID.

### 8.1 Configuration Words

There are several Configuration Word bits that allow different oscillator and memory protection options. These are implemented as Configuration Word 1 register at 2007h and Configuration Word 2 register at 2008h. These registers are only accessible during programming.

#### REGISTER 8-1: CONFIG1: CONFIGURATION WORD REGISTER 1

|                    |                                                                            | R/P-1                                                                                                                             | R/P-1                                      | U-1 <sup>(4)</sup>                    | R/P-1              | R/P-1            | R/P-1  |

|--------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|---------------------------------------|--------------------|------------------|--------|

|                    |                                                                            | DEBUG                                                                                                                             | PLLEN                                      | —                                     | BORV               | BOREN1           | BOREN0 |

|                    |                                                                            | bit 13                                                                                                                            | 1                                          |                                       |                    |                  | bit    |

|                    |                                                                            |                                                                                                                                   |                                            |                                       |                    |                  |        |

| U-1 <sup>(4)</sup> | R/P-1                                                                      | R/P-1                                                                                                                             | R/P-1                                      | R/P-1                                 | R/P-1              | R/P-1            | R/P-1  |

| —                  | CP                                                                         | MCLRE                                                                                                                             | PWRTE                                      | WDTE                                  | FOSC2              | FOSC1            | FOSC0  |

| oit 7              |                                                                            |                                                                                                                                   |                                            |                                       |                    |                  | bit    |

|                    |                                                                            |                                                                                                                                   |                                            |                                       |                    |                  |        |

| Legend:            |                                                                            | P = Programma                                                                                                                     | able bit                                   |                                       |                    |                  |        |

| R = Readable       | bit                                                                        | W = Writable bi                                                                                                                   | t                                          | U = Unimplem                          | ented bit, read as | s 'O'            |        |

| -n = Value at F    | POR                                                                        | '1' = Bit is set                                                                                                                  |                                            | '0' = Bit is clea                     | ired               | x = Bit is unkno | own    |

| oit 13<br>oit 12   | 1 = In-circuit o<br>0 = In-circuit o<br><b>PLLEN:</b> INTC<br>0 = INTOSC f | ircuit Debugger M<br>debugger disabled<br>debugger enabled<br>DSC PLL Enable b<br>requency is 500 k<br>requency is 16 Mł          | , RB6/ICSPCLI<br>, RB6/ICSPCLI<br>it<br>Hz |                                       | 0                  |                  |        |

| bit 11             |                                                                            | ted: Read as '1'                                                                                                                  | (- )                                       |                                       |                    |                  |        |

| bit 10             | 0 = Brown-ou                                                               | n-out Reset Voltag<br>t Reset Voltage (V<br>t Reset Voltage (V                                                                    | BOR) set to 2.5                            |                                       |                    |                  |        |

| bit 9-8            | BOREN<1:0><br>0x = BOR dis                                                 | Brown-out Rese<br>abled (preconditio<br>abled during opera                                                                        | t Selection bits                           | 1)                                    |                    |                  |        |

| oit 7              | Unimplemen                                                                 | ted: Read as '1'                                                                                                                  |                                            |                                       |                    |                  |        |

| bit 6              | CP: Code Pro                                                               | otection bit <sup>(2)</sup>                                                                                                       |                                            |                                       |                    |                  |        |

|                    |                                                                            | memory code prot                                                                                                                  |                                            |                                       |                    |                  |        |

| bit 5              | MCLRE: RE3<br>1 = RE3/MCL                                                  | memory code prot<br>$\sqrt{MCLR}$ Pin Functi<br>$\overline{R}$ pin function is $\overline{R}$<br>$\overline{R}$ pin function is d | on Select bit <sup>(3)</sup><br>ICLR       |                                       | d to VDD           |                  |        |

| bit 4              |                                                                            | ver-up Timer Enab<br>sabled                                                                                                       | •                                          |                                       |                    |                  |        |

| bit 3              | WDTE: Watch<br>1 = WDT enal<br>0 = WDT disa                                |                                                                                                                                   | e bit                                      |                                       |                    |                  |        |

| 2: TI<br>3: W      | he entire program<br>/hen MCLR is ass                                      | t Reset does not a<br>memory will be el<br>erted in INTOSC o<br>sks unimplemente                                                  | rased when the<br>or RC mode, the          | code protection<br>e internal clock c | is turned off.     | ed.              |        |

4: MPLAB<sup>®</sup> X IDE masks unimplemented Configuration bits to '0'.

| WDTE | TMR1GE = 1<br>and<br>T1GSS = 11 | WDT Oscillator<br>Enable | WDT Reset | Wake-up | WDT Available for<br>T1G Source |

|------|---------------------------------|--------------------------|-----------|---------|---------------------------------|

| 1    | Ν                               | Y                        | Y         | Y       | Ν                               |

| 1    | Y                               | Y                        | Y         | Y       | Y                               |

| 0    | Y                               | Y                        | N         | Ν       | Y                               |

| 0    | Ν                               | Ν                        | N         | N       | Ν                               |

#### TABLE 12-2: WDT/TIMER1 GATE INTERACTION

#### 12.6.3 TIMER1 GATE TOGGLE MODE

When Timer1 Gate Toggle mode is enabled, it is possible to measure the full-cycle length of a Timer1 gate signal, as opposed to the duration of a single level pulse.

The Timer1 gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. See Figure 12-5 for timing details.

Timer1 Gate Toggle mode is enabled by setting the T1GTM bit of the T1GCON register. When the T1GTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

**Note:** Enabling Toggle mode at the same time as changing the gate polarity may result in indeterminate operation.

## 12.6.4 TIMER1 GATE SINGLE-PULSE MODE

When Timer1 Gate Single-Pulse mode is enabled, it is possible to capture a single pulse gate event. Timer1 Gate Single-Pulse mode is first enabled by setting the T1GSPM bit in the T1GCON register. Next, the T1GGO/DONE bit in the T1GCON register must be set. The Timer1 will be fully enabled on the next incrementing edge. On the next trailing edge of the pulse, the T1GGO/DONE bit will automatically be cleared. No other gate events will be allowed to increment Timer1 until the T1GGO/DONE bit is once again set in software.

Clearing the T1GSPM bit of the T1GCON register will also clear the T1GGO/DONE bit. See Figure 12-6 for timing details.

Enabling the Toggle mode and the Single-Pulse mode simultaneously will permit both sections to work together. This allows the cycle times on the Timer1 gate source to be measured. See Figure 12-7 for timing details.

#### 12.6.5 TIMER1 GATE VALUE STATUS

When Timer1 gate value status is utilized, it is possible to read the most current level of the gate control value. The value is stored in the T1GVAL bit in the T1GCON register. The T1GVAL bit is valid even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

#### 12.6.6 TIMER1 GATE EVENT INTERRUPT

When Timer1 gate event interrupt is enabled, it is possible to generate an interrupt upon the completion of a gate event. When the falling edge of T1GVAL occurs, the TMR1GIF flag bit in the PIR1 register will be set. If the TMR1GIE bit in the PIE1 register is set, then an interrupt will be recognized.

The TMR1GIF flag bit operates even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

## 12.11 Timer1 Control Register

The Timer1 Control register (T1CON), shown in Register 12-1, is used to control Timer1 and select the various features of the Timer1 module.

#### REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | U-0 | R/W-0  |

|---------|---------|---------|---------|---------|--------|-----|--------|

| TMR1CS1 | TMR1CS0 | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | _   | TMR10N |

| bit 7   |         |         |         |         |        |     | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7-6        | TMR1CS<1:0>: Timer1 Clock Source Select bits                                                                                                                                                                                                                                                                                     |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | <ul> <li>11 = Timer1 clock source is Capacitive Sensing Oscillator (CAPOSC)</li> <li>10 = Timer1 clock source is pin or oscillator:</li> </ul>                                                                                                                                                                                   |

|                | $\frac{\text{If } T10SCEN = 0}{T10SCEN = 0}$                                                                                                                                                                                                                                                                                     |

|                | External clock from T1CKI pin (on the rising edge)<br>If T1OSCEN = 1:                                                                                                                                                                                                                                                            |

|                | Crystal oscillator on T1OSI/T1OSO pins                                                                                                                                                                                                                                                                                           |

|                | 01 = Timer1 clock source is system clock (Fosc)<br>00 = Timer1 clock source is instruction clock (Fosc/4)                                                                                                                                                                                                                        |

| bit 5-4        | <b>T1CKPS&lt;1:0&gt;:</b> Timer1 Input Clock Prescale Select bits                                                                                                                                                                                                                                                                |

| bit 0 4        | 11 = 1.8 Prescale value                                                                                                                                                                                                                                                                                                          |

|                | 10 = 1:4 Prescale value                                                                                                                                                                                                                                                                                                          |

|                | 01 = 1:2 Prescale value<br>00 = 1:1 Prescale value                                                                                                                                                                                                                                                                               |

| bit 3          | <b>TIOSCEN:</b> LP Oscillator Enable Control bit                                                                                                                                                                                                                                                                                 |

| bit 5          | 1 = Dedicated Timer1 oscillator circuit enabled                                                                                                                                                                                                                                                                                  |

|                | 0 = Dedicated Timer1 oscillator circuit disabled                                                                                                                                                                                                                                                                                 |

| bit 2          | <b>T1SYNC:</b> Timer1 External Clock Input Synchronization Control bit                                                                                                                                                                                                                                                           |

|                | TISTIC. Timer External Clock input Synchronization Control bit                                                                                                                                                                                                                                                                   |

|                | <u>TMR1CS&lt;1:0&gt; = <math>1X</math></u>                                                                                                                                                                                                                                                                                       |

|                | $\frac{\text{TMR1CS}<1:0> = 1x}{1 = \text{Do not synchronize external clock input}}$                                                                                                                                                                                                                                             |

|                | $\underline{TMR1CS} = \underline{1X}$                                                                                                                                                                                                                                                                                            |

|                | $\frac{\text{TMR1CS} < 1:0> = 1x}{1 = \text{Do not synchronize external clock input}}$<br>0 = Synchronize external clock input with system clock (Fosc)<br>$\frac{\text{TMR1CS} < 1:0> = 0x}{10}$                                                                                                                                |

|                | $\frac{\text{TMR1CS}<1:0> = 1x}{1 = \text{ Do not synchronize external clock input}}$ $0 = \text{Synchronize external clock input with system clock (Fosc)}$ $\frac{\text{TMR1CS}<1:0> = 0x}{\text{This bit is ignored. Timer1 uses the internal clock when TMR1CS}<1:0> = 1x.$                                                  |

| bit 1          | $\frac{\text{TMR1CS} < 1:0 > = 1x}{1 = \text{Do not synchronize external clock input}}$ $0 = \text{Synchronize external clock input with system clock (Fosc)}$ $\frac{\text{TMR1CS} < 1:0 > = 0x}{\text{This bit is ignored. Timer1 uses the internal clock when TMR1CS} < 1:0 > = 1x.$ Unimplemented: Read as '0'               |

| bit 1<br>bit 0 | $\frac{\text{TMR1CS}<1:0> = 1x}{1 = \text{ Do not synchronize external clock input}}$ $0 = \text{Synchronize external clock input with system clock (Fosc)}$ $\frac{\text{TMR1CS}<1:0> = 0x}{\text{This bit is ignored. Timer1 uses the internal clock when TMR1CS}<1:0> = 1x.$ Unimplemented: Read as '0' TMR1ON: Timer1 On bit |

|                | $\frac{\text{TMR1CS} < 1:0 > = 1x}{1 = \text{Do not synchronize external clock input}}$ $0 = \text{Synchronize external clock input with system clock (Fosc)}$ $\frac{\text{TMR1CS} < 1:0 > = 0x}{\text{This bit is ignored. Timer1 uses the internal clock when TMR1CS} < 1:0 > = 1x.$ Unimplemented: Read as '0'               |

## 19.0 POWER-DOWN MODE (SLEEP)

The Power-down mode is entered by executing a  $\ensuremath{\mathtt{SLEEP}}$  instruction.

If the Watchdog Timer is enabled:

- WDT will be cleared but keeps running.

- PD bit of the STATUS register is cleared.

- TO bit of the STATUS register is set.

- Oscillator driver is turned off.

- Timer1 oscillator is unaffected

- I/O ports maintain the status they had before SLEEP was executed (driving high, low or highimpedance).

For lowest current consumption in this mode, all I/O pins should be either at VDD or VSs, with no external circuitry drawing current from the I/O pin. I/O pins that are high-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSs for lowest current consumption. The contribution from on-chip pull ups on PORTB should be considered.

The MCLR pin must be at a logic high level when external MCLR is enabled.

Note: A Reset generated by a WDT time out does not drive MCLR pin low.

#### 19.1 Wake-up from Sleep

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on  $\overline{\text{MCLR}}$  pin.

- 2. Watchdog Timer wake-up (if WDT was enabled).

- 3. Interrupt from RB0/INT pin, PORTB change or a peripheral interrupt.

The first event will cause a device Reset. The two latter events are considered a continuation of program execution. The TO and PD bits in the STATUS register can be used to determine the cause of device Reset. The PD bit, which is set on power-up, is cleared when Sleep is invoked. TO bit is cleared if WDT wake-up occurred. The following peripheral interrupts can wake the device from Sleep:

- 1. TMR1 Interrupt. Timer1 must be operating as an asynchronous counter.

- USART Receive Interrupt (Synchronous Slave mode only)

- 3. A/D conversion (when A/D clock source is RC)

- 4. Interrupt-on-change

- 5. External Interrupt from INT pin

- 6. Capture event on CCP1 or CCP2

- 7. SSP Interrupt in SPI or I<sup>2</sup>C Slave mode

Other peripherals cannot generate interrupts since during Sleep, no on-chip clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction, then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

| Note: | If the global interrupts are disabled (GIE is |  |  |  |  |  |  |  |  |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|--|

|       | cleared), but any interrupt source has both   |  |  |  |  |  |  |  |  |  |  |  |  |

|       | its interrupt enable bit and the              |  |  |  |  |  |  |  |  |  |  |  |  |

|       | corresponding interrupt flag bits set, the    |  |  |  |  |  |  |  |  |  |  |  |  |

|       | device will immediately wake-up from          |  |  |  |  |  |  |  |  |  |  |  |  |

|       | Sleep. The SLEEP instruction is               |  |  |  |  |  |  |  |  |  |  |  |  |

|       | completely executed.                          |  |  |  |  |  |  |  |  |  |  |  |  |

The WDT is cleared when the device wakes up from Sleep, regardless of the source of wake-up.

| SUBWF            | Subtract W from f                                |                                                                                                                             |  |  |  |  |

|------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] SU                                       | JBWF f,d                                                                                                                    |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$               |                                                                                                                             |  |  |  |  |

| Operation:       | (f) - (W) $\rightarrow$ (                        | destination)                                                                                                                |  |  |  |  |

| Status Affected: | C, DC, Z                                         |                                                                                                                             |  |  |  |  |

| Description:     | W register f<br>'0', the resu<br>register. If 'd | s complement method)<br>rom register 'f'. If 'd' is<br>It is stored in the W<br>d' is '1', the result is<br>in register 'f. |  |  |  |  |

|                  | <b>C</b> = 0                                     | W > f                                                                                                                       |  |  |  |  |

|                  | <b>C</b> = 1                                     | $W \leq f$                                                                                                                  |  |  |  |  |

$\overline{DC} = 0$

**DC** = 1

W<3:0> > f<3:0> W<3:0>  $\leq$  f<3:0>

| XORLW            | Exclusive OR literal with W                                                                                            |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                               |  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                    |  |  |  |  |  |  |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                          |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                      |  |  |  |  |  |  |

| Description:     | The contents of the W register<br>are XOR'ed with the 8-bit<br>literal 'k'. The result is placed in<br>the W register. |  |  |  |  |  |  |

| SWAPF            | Swap Nibbles in f                                                                                                                                                      |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] SWAPF f,d                                                                                                                                                      |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                            |  |  |  |  |  |  |

| Operation:       | $(f<3:0>) \rightarrow (destination<7:4>),$<br>$(f<7:4>) \rightarrow (destination<3:0>)$                                                                                |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                   |  |  |  |  |  |  |

| Description:     | The upper and lower nibbles of register 'f' are exchanged. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed in register 'f'. |  |  |  |  |  |  |

| XORWF            | Exclusive OR W with f                                                                                                                                                           |  |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                                                                                      |  |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                     |  |  |  |  |  |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (destination)                                                                                                                                       |  |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                               |  |  |  |  |  |  |  |

| Description:     | Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |  |  |  |  |  |  |  |

| PIC16LF       | 722A/723  | A                                                      | $ \begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for extended} \end{array} $ |                                                      |                                 |                  |                                                                                                                                                                                                                                                                     |  |  |  |

|---------------|-----------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|---------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PIC16F7       | 722A/723A | ۸.                                                     |                                                                                                                                                                                                                                                             | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                                 |                  |                                                                                                                                                                                                                                                                     |  |  |  |

| Param.<br>No. | Sym.      | Characteristic                                         | Min.                                                                                                                                                                                                                                                        | Min. Typ† M                                          |                                 | Units            | Conditions                                                                                                                                                                                                                                                          |  |  |  |

| D001          | Vdd       | Supply Voltage                                         |                                                                                                                                                                                                                                                             |                                                      |                                 |                  |                                                                                                                                                                                                                                                                     |  |  |  |

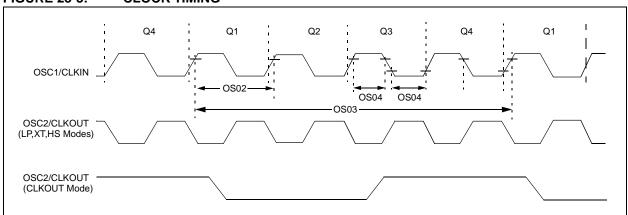

|               |           | PIC16LF722A/723A                                       | 1.8<br>1.8<br>2.3<br>2.5                                                                                                                                                                                                                                    |                                                      | 3.6<br>3.6<br>3.6<br>3.6        | V<br>V<br>V<br>V | Fosc $\leq$ 16 MHz: HFINTOSC, EC<br>Fosc $\leq$ 4 MHz<br>Fosc $\leq$ 20 MHz, EC<br>Fosc $\leq$ 20 MHz, HS                                                                                                                                                           |  |  |  |

| D001          |           | PIC16F722A/723A                                        | 1.8<br>1.8<br>2.3<br>2.5                                                                                                                                                                                                                                    |                                                      | 5.5<br>5.5<br>5.5<br>5.5<br>5.5 | V<br>V<br>V<br>V | Fosc $\leq$ 16 MHz: HFINTOSC, EC<br>Fosc $\leq$ 4 MHz<br>Fosc $\leq$ 20 MHz, EC<br>Fosc $\leq$ 20 MHz, HS                                                                                                                                                           |  |  |  |

| D002*         | Vdr       | RAM Data Retention Voltage <sup>(1)</sup>              |                                                                                                                                                                                                                                                             |                                                      |                                 |                  |                                                                                                                                                                                                                                                                     |  |  |  |

|               |           | PIC16LF722A/723A                                       | 1.5                                                                                                                                                                                                                                                         | —                                                    | -                               | V                | Device in Sleep mode                                                                                                                                                                                                                                                |  |  |  |

| D002*         |           | PIC16F722A/723A                                        | 1.7                                                                                                                                                                                                                                                         | _                                                    | _                               | V                | Device in Sleep mode                                                                                                                                                                                                                                                |  |  |  |

|               | VPOR*     | Power-on Reset Release Voltage                         |                                                                                                                                                                                                                                                             | 1.6                                                  | -                               | V                |                                                                                                                                                                                                                                                                     |  |  |  |

|               | VPORR*    | Power-on Reset Rearm Voltage                           |                                                                                                                                                                                                                                                             |                                                      |                                 |                  |                                                                                                                                                                                                                                                                     |  |  |  |

|               |           | PIC16LF722A/723A                                       |                                                                                                                                                                                                                                                             | 0.8                                                  | -                               | V                | Device in Sleep mode                                                                                                                                                                                                                                                |  |  |  |

|               |           | PIC16F722A/723A                                        |                                                                                                                                                                                                                                                             | 1.7                                                  | -                               | V                | Device in Sleep mode                                                                                                                                                                                                                                                |  |  |  |

| D003          | Vfvr      | Fixed Voltage Reference Voltage,<br>Initial Accuracy   | -5.5<br>-5.5<br>-5.5                                                                                                                                                                                                                                        | <br> <br>                                            | 5.5<br>5.5<br>5.5               | %<br>%<br>%      | $ \begin{array}{l} {\sf VFVR} = 1.024{\sf V},  {\sf VDD} \geq 2.5{\sf V} \\ {\sf VFVR} = 2.048{\sf V},  {\sf VDD} \geq 2.5{\sf V} \\ {\sf VFVR} = 4.096{\sf V},  {\sf VDD} \geq 4.75{\sf V}; \\ {\sf -40} \leq {\sf TA} \leq 85^{\circ}{\sf C} \end{array} $        |  |  |  |

|               |           |                                                        | -6<br>-6<br>-6                                                                                                                                                                                                                                              |                                                      | 6<br>6<br>6                     | %<br>%<br>%      | $ \begin{array}{l} V{\sf FVR} = 1.024{\sf V}, \ {\sf VDD} \geq 2.5{\sf V} \\ {\sf VFVR} = 2.048{\sf V}, \ {\sf VDD} \geq 2.5{\sf V} \\ {\sf VFVR} = 4.096{\sf V}, \ {\sf VDD} \geq 4.75{\sf V}; \\ {\sf -40} \leq {\sf TA} \leq 125{\rm ^{\circ}C} \\ \end{array} $ |  |  |  |

| D004*         | SVDD      | VDD Rise Rate to ensure internal Power-on Reset signal | 0.05                                                                                                                                                                                                                                                        | —                                                    | —                               | V/ms             | See Section 3.2 "Power-on Reset (POR)" for details.                                                                                                                                                                                                                 |  |  |  |

## 23.1 DC Characteristics: PIC16(L)F722A/723A-I/E (Industrial, Extended)

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

#### 23.2 DC Characteristics: PIC16(L)F722A/723A-I/E (Industrial, Extended) (Continued)

| PIC16LF7                               | 722A/723A       | $ \begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for extended} \end{array} $ |                               |         |                     |                                                                               |                             |  |  |  |  |

|----------------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|---------|---------------------|-------------------------------------------------------------------------------|-----------------------------|--|--|--|--|

| PIC16F722A/723A                        |                 |                                                                                                                                                                                                                                                                  | <b>l Operati</b><br>g tempera | ature - | $40^{\circ}C \le T$ | less otherwise stated)<br>A ≤ +85°C for industrial<br>A ≤ +125°C for extended |                             |  |  |  |  |

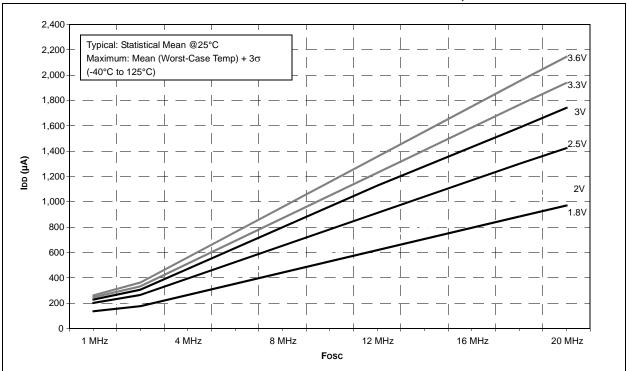

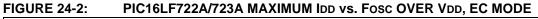

| Param                                  | Device          | Min.                                                                                                                                                                                                                                                             | Тур†                          | Max.    | Units               |                                                                               | Conditions                  |  |  |  |  |

| No.                                    | Characteristics |                                                                                                                                                                                                                                                                  |                               |         |                     | VDD                                                                           | Note                        |  |  |  |  |

| Supply Current (IDD) <sup>(1, 2)</sup> |                 |                                                                                                                                                                                                                                                                  |                               |         |                     |                                                                               |                             |  |  |  |  |

| D014                                   |                 | _                                                                                                                                                                                                                                                                | 290                           | 330     | μA                  | 1.8                                                                           | Fosc = 4 MHz                |  |  |  |  |

|                                        |                 | _                                                                                                                                                                                                                                                                | 460                           | 500     | μA                  | 3.0                                                                           | EC Oscillator mode          |  |  |  |  |

| D014                                   |                 |                                                                                                                                                                                                                                                                  | 300                           | 430     | μA                  | 1.8                                                                           | Fosc = 4 MHz                |  |  |  |  |

|                                        |                 |                                                                                                                                                                                                                                                                  | 450                           | 655     | μA                  | 3.0                                                                           | EC Oscillator mode (Note 5) |  |  |  |  |

|                                        |                 | —                                                                                                                                                                                                                                                                | 500                           | 730     | μA                  | 5.0                                                                           |                             |  |  |  |  |

| D015                                   |                 | —                                                                                                                                                                                                                                                                | 100                           | 130     | μA                  | 1.8                                                                           | Fosc = 500 kHz              |  |  |  |  |

|                                        |                 |                                                                                                                                                                                                                                                                  | 120                           | 150     | μA                  | 3.0                                                                           | MFINTOSC mode               |  |  |  |  |

| D015                                   |                 | _                                                                                                                                                                                                                                                                | 115                           | 195     | μA                  | 1.8                                                                           | Fosc = 500 kHz              |  |  |  |  |

|                                        |                 | _                                                                                                                                                                                                                                                                | 135                           | 200     | μA                  | 3.0                                                                           | MFINTOSC mode (Note 5)      |  |  |  |  |

|                                        |                 | _                                                                                                                                                                                                                                                                | 150                           | 220     | μA                  | 5.0                                                                           |                             |  |  |  |  |

| D016                                   |                 |                                                                                                                                                                                                                                                                  | 650                           | 800     | μA                  | 1.8                                                                           | Fosc = 8 MHz                |  |  |  |  |

|                                        |                 | —                                                                                                                                                                                                                                                                | 1000                          | 1200    | μA                  | 3.0                                                                           | HFINTOSC mode               |  |  |  |  |

| D016                                   |                 | —                                                                                                                                                                                                                                                                | 625                           | 850     | μA                  | 1.8                                                                           | Fosc = 8 MHz                |  |  |  |  |

|                                        |                 | —                                                                                                                                                                                                                                                                | 1000                          | 1200    | μA                  | 3.0                                                                           | HFINTOSC mode (Note 5)      |  |  |  |  |

|                                        |                 | —                                                                                                                                                                                                                                                                | 1100                          | 1500    | μA                  | 5.0                                                                           |                             |  |  |  |  |

| D017                                   |                 | _                                                                                                                                                                                                                                                                | 1.0                           | 1.2     | mA                  | 1.8                                                                           | Fosc = 16 MHz               |  |  |  |  |

|                                        |                 | —                                                                                                                                                                                                                                                                | 1.5                           | 1.85    | mA                  | 3.0                                                                           | HFINTOSC mode               |  |  |  |  |

| D017                                   |                 | _                                                                                                                                                                                                                                                                | 1                             | 1.2     | mA                  | 1.8                                                                           | Fosc = 16 MHz               |  |  |  |  |

|                                        |                 | _                                                                                                                                                                                                                                                                | 1.5                           | 1.7     | mA                  | 3.0                                                                           | HFINTOSC mode (Note 5)      |  |  |  |  |

|                                        |                 |                                                                                                                                                                                                                                                                  | 1.7                           | 2.1     | mA                  | 5.0                                                                           |                             |  |  |  |  |

| D018                                   |                 | _                                                                                                                                                                                                                                                                | 210                           | 240     | μA                  | 1.8                                                                           | Fosc = 4 MHz                |  |  |  |  |

|                                        |                 | _                                                                                                                                                                                                                                                                | 340                           | 380     | μA                  | 3.0                                                                           | EXTRC mode (Note 3, Note 5) |  |  |  |  |

| D018                                   |                 |                                                                                                                                                                                                                                                                  | 225                           | 320     | μA                  | 1.8                                                                           | Fosc = 4 MHz                |  |  |  |  |

|                                        |                 |                                                                                                                                                                                                                                                                  | 360                           | 445     | μA                  | 3.0                                                                           | EXTRC mode (Note 3, Note 5) |  |  |  |  |

|                                        |                 |                                                                                                                                                                                                                                                                  | 410                           | 650     | μA                  | 5.0                                                                           |                             |  |  |  |  |

| D019                                   |                 | —                                                                                                                                                                                                                                                                | 1.6                           | 1.9     | mA                  | 3.0                                                                           | Fosc = 20 MHz               |  |  |  |  |

|                                        |                 | _                                                                                                                                                                                                                                                                | 2.0                           | 2.8     | mA                  | 3.6                                                                           | HS Oscillator mode          |  |  |  |  |

| D019                                   |                 | _                                                                                                                                                                                                                                                                | 1.6                           | 2       | mA                  | 3.0                                                                           | Fosc = 20 MHz               |  |  |  |  |

|                                        |                 |                                                                                                                                                                                                                                                                  | 1.9                           | 3.2     | mA                  | 5.0                                                                           | HS Oscillator mode (Note 5) |  |  |  |  |

**Note 1:** The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

**3:** For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in kΩ.

4: FVR and BOR are disabled.

5: 0.1 μF capacitor on VCAP (RA0).

## 23.7 AC Characteristics: PIC16F722A/723A-I/E

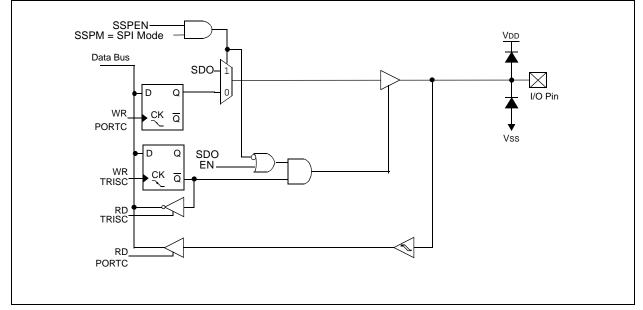

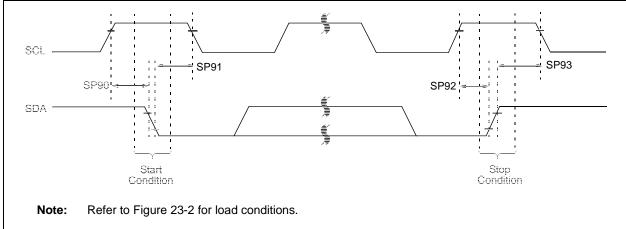

#### FIGURE 23-3: CLOCK TIMING

#### TABLE 23-7: PIC16F722A/723A A/D CONVERTER (ADC) CHARACTERISTICS:

|              | •    | rating Conditions (unless otherwi<br>perature $-40^{\circ}C \le TA \le +125^{\circ}C$ | se state | ed)  |      |       |                                                                     |  |  |

|--------------|------|---------------------------------------------------------------------------------------|----------|------|------|-------|---------------------------------------------------------------------|--|--|

| Param<br>No. | Sym. | Characteristic                                                                        | Min.     | Тур† | Max. | Units | s Conditions                                                        |  |  |

| AD01         | Nr   | Resolution                                                                            | —        | _    | 8    | bit   |                                                                     |  |  |

| AD02         | EIL  | Integral Error                                                                        | —        | _    | ±1.7 | LSb   | VREF = 3.0V                                                         |  |  |

| AD03         | Edl  | Differential Error                                                                    | _        | _    | ±1   | LSb   | No missing codes<br>VREF = 3.0V                                     |  |  |

| AD04         | EOFF | Offset Error                                                                          | —        | _    | ±2.2 | LSb   | VREF = 3.0V                                                         |  |  |

| AD05         | Egn  | Gain Error                                                                            | _        | _    | ±1.5 | LSb   | VREF = 3.0V                                                         |  |  |

| AD06         | Vref | Reference Voltage <sup>(3)</sup>                                                      | 1.8      | _    | Vdd  | V     |                                                                     |  |  |

| AD07         | VAIN | Full-Scale Range                                                                      | Vss      | _    | VREF | V     |                                                                     |  |  |

| AD08         | ZAIN | Recommended Impedance of<br>Analog Voltage Source                                     | _        | _    | 50   |       | Can go higher if external 0.01µF capacitor is present on input pin. |  |  |

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Total Absolute Error includes integral, differential, offset and gain errors.

- 2: The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

- **3:** When ADC is off, it will not consume any current other than leakage current. The power-down current specification includes any such leakage from the ADC module.

#### TABLE 23-8: PIC16F722A/723A A/D CONVERSION REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$     |      |                                                                 |            |         |            |          |                                          |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------|------|-----------------------------------------------------------------|------------|---------|------------|----------|------------------------------------------|--|--|--|

| Param<br>No.         Sym.         Characteristic         Min.         Typ†         Max.         Units         Conditions |      |                                                                 |            |         |            |          |                                          |  |  |  |

| AD130*                                                                                                                   | Tad  | A/D Clock Period<br>A/D Internal RC Oscillator<br>Period        | 1.0<br>1.0 | <br>2.0 | 9.0<br>6.0 | μs<br>μs | Tosc-based<br>ADCS<1:0> = 11 (ADRC mode) |  |  |  |

| AD131                                                                                                                    | TCNV | Conversion Time (not including Acquisition Time) <sup>(1)</sup> | _          | 10.5    | —          | Tad      | Set GO/DONE bit to conversion complete   |  |  |  |

| AD132*                                                                                                                   | TACQ | Acquisition Time                                                | —          | 1.0     | —          | μs       |                                          |  |  |  |

These parameters are characterized but not tested.