Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | •                                                                           |

| RAM Size                   | 128 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 11x8b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

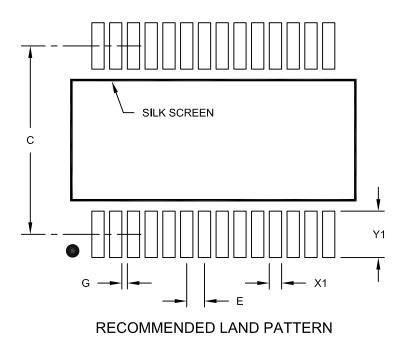

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 28-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf722at-i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.6 Time-out Sequence

On power-up, the time-out sequence is as follows: first, PWRT time out is invoked after POR has expired, then OST is activated after the PWRT time out has expired. The total time out will vary based on oscillator configuration and  $\overrightarrow{PWRTE}$  bit status. For example, in EC mode with  $\overrightarrow{PWRTE}$  bit = 1 ( $\overrightarrow{PWRT}$  disabled), there will be no time-out at all. Figure 3-4, Figure 3-5 and Figure 3-6 depict time-out sequences.

Since the time outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then, bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (see Figure 3-5). This is useful for testing purposes or to synchronize more than one PIC16(L)F722A/723A device operating in parallel.

Table 3-3 shows the Reset conditions for some special registers.

### 3.7 Power Control (PCON) Register

The Power Control (PCON) register has two Status bits to indicate what type of Reset that last occurred.

Bit 0 is  $\overrightarrow{BOR}$  (Brown-out Reset).  $\overrightarrow{BOR}$  is unknown on Power-on Reset. It must then be set by the user and checked on subsequent Resets to see if  $\overrightarrow{BOR} = 0$ , indicating that a brown-out has occurred. The  $\overrightarrow{BOR}$ Status bit is a "don't care" and is not necessarily predictable if the brown-out circuit is disabled (BOREN<1:0> = 00 in the Configuration Word register).

Bit 1 is POR (Power-on Reset). It is a '0' on Power-on Reset and unaffected otherwise. The user must write a '1' to this bit following a Power-on Reset. On a subsequent Reset, if POR is '0', it will indicate that a Power-on Reset has occurred (i.e., VDD may have gone too low).

For more information, see Section 3.5 "Brown-Out Reset (BOR)".

| Oscillator Configuration  | Powe                   | er-up       | Brown-o                | Wake-up from     |             |

|---------------------------|------------------------|-------------|------------------------|------------------|-------------|

| Oscillator Configuration  | <b>PWRTE</b> = 0       | PWRTE = 1   | <b>PWRTE</b> = 0       | <b>PWRTE</b> = 1 | Sleep       |

| XT, HS, LP <sup>(1)</sup> | TPWRT + 1024 •<br>Tosc | 1024 • Tosc | TPWRT + 1024 •<br>Tosc | 1024 • Tosc      | 1024 • Tosc |

| RC, EC, INTOSC            | TPWRT                  |             | TPWRT                  | _                | —           |

### TABLE 3-2: TIME OUT IN VARIOUS SITUATIONS

Note 1: LP mode with T1OSC disabled.

### TABLE 3-3: RESET BITS AND THEIR SIGNIFICANCE

| POR | BOR | то | PD | Condition                          |

|-----|-----|----|----|------------------------------------|

| 0   | u   | 1  | 1  | Power-on Reset                     |

| 1   | 0   | 1  | 1  | Brown-out Reset                    |

| u   | u   | 0  | u  | WDT Reset                          |

| u   | u   | 0  | 0  | WDT Wake-up                        |

| u   | u   | u  | u  | MCLR Reset during normal operation |

| u   | u   | 1  | 0  | MCLR Reset during Sleep            |

**Legend:** u = unchanged, x = unknown

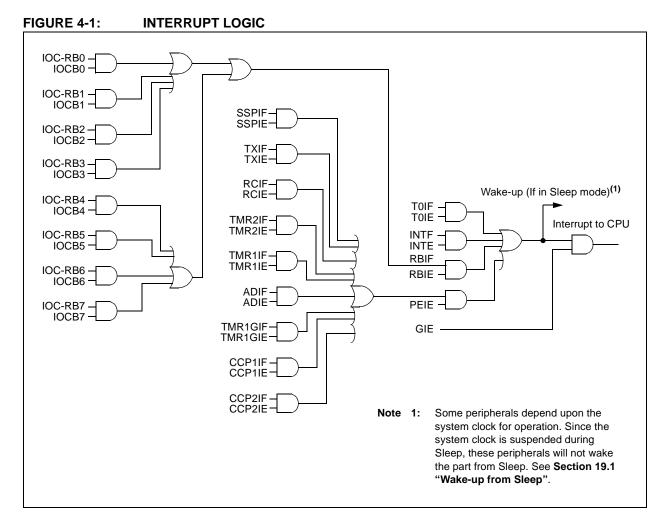

# 4.0 INTERRUPTS

The PIC16(L)F722A/723A device family features an interruptible core, allowing certain events to preempt normal program flow. An Interrupt Service Routine (ISR) is used to determine the source of the interrupt and act accordingly. Some interrupts can be configured to wake the MCU from Sleep mode.

The PIC16(L)F722A/723A device family has 12 interrupt sources, differentiated by corresponding interrupt enable and flag bits:

- Timer0 Overflow Interrupt

- External Edge Detect on INT Pin Interrupt

- PORTB Change Interrupt

- Timer1 Gate Interrupt

- A/D Conversion Complete Interrupt

- AUSART Receive Interrupt

- AUSART Transmit Interrupt

- SSP Event Interrupt

- CCP1 Event Interrupt

- Timer2 Match with PR2 Interrupt

- Timer1 Overflow Interrupt

- CCP2 Event Interrupt

A block diagram of the interrupt logic is shown in Figure 4-1.

### 4.5.5 PIR2 REGISTER

The PIR2 register contains the interrupt flag bits, as shown in Register 4-5.

| Note: | Interrupt flag bits are set when an interrupt   |

|-------|-------------------------------------------------|

|       | condition occurs, regardless of the state of    |

|       | its corresponding enable bit or the global      |

|       | enable bit, GIE of the INTCON register.         |

|       | User software should ensure the                 |

|       | appropriate interrupt flag bits are clear prior |

|       | to enabling an interrupt.                       |

### REGISTER 4-5: PIR2: PERIPHERAL INTERRUPT REQUEST REGISTER 2

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  |

|-------|-----|-----|-----|-----|-----|-----|--------|

| —     | —   | —   | -   | —   | —   | _   | CCP2IF |

| bit 7 |     |     |     |     |     |     | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

### bit 7-1 Unimplemented: Read as '0'

bit 0 CCP2IF: CCP2 Interrupt Flag bit

Capture Mode:

1 = A TMR1 register capture occurred (must be cleared in software)

0 = No TMR1 register capture occurred

### Compare Mode:

1 = A TMR1 register compare match occurred (must be cleared in software)

0 = No TMR1 register compare match occurred

PWM mode:

Unused in this mode

### TABLE 4-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

| Name       | Bit 7   | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Register on<br>Page |

|------------|---------|--------|-------|-------|-------|--------|--------|--------|---------------------|

| INTCON     | GIE     | PEIE   | TOIE  | INTE  | RBIE  | T0IF   | INTF   | RBIF   | 36                  |

| OPTION_REG | RBPU    | INTEDG | TOCS  | T0SE  | PSA   | PS2    | PS1    | PS0    | 19                  |

| PIE1       | TMR1GIE | ADIE   | RCIE  | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 37                  |

| PIE2       | _       | _      | -     | —     | _     | _      | _      | CCP2IE | 38                  |

| PIR1       | TMR1GIF | ADIF   | RCIF  | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 39                  |

| PIR2       | _       | _      | _     | _     | _     | _      | _      | CCP2IF | 40                  |

Legend: - = Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the Capture, Compare and PWM.

# PIC16(L)F722A/723A

| FIGURE 12-7:           | TIMER1 GATE SINGLE-PULSE AND TOGGLE COMBINED MODE                                                                  |

|------------------------|--------------------------------------------------------------------------------------------------------------------|

| TMR1GE                 |                                                                                                                    |

| T1GPOL                 |                                                                                                                    |

| T1GSPM                 |                                                                                                                    |

| T1GTM                  |                                                                                                                    |

| T1GG <u>O/</u><br>DONE | ← Set by software<br>Cleared by hardware on<br>falling edge of T1GVAL<br>Counting enabled on<br>riging edge of T1C |

| T1G_IN                 | rising edge of T1G                                                                                                 |

| Т1СКІ                  |                                                                                                                    |

| T1GVAL                 |                                                                                                                    |

| TIMER1                 | N N + 1 N + 2 N + 3 N + 4                                                                                          |

| TMR1GIF                | Set by hardware on Cleared by software falling edge of T1GVAL                                                      |

| R/W-0           | U-0                                                                       | U-0                                                | U-0                                            | R/W-0                                                                        | R/W-0                                 | R-0             | R/W-0 |

|-----------------|---------------------------------------------------------------------------|----------------------------------------------------|------------------------------------------------|------------------------------------------------------------------------------|---------------------------------------|-----------------|-------|

| CPSON           | _                                                                         | —                                                  | _                                              | CPSRNG1                                                                      | CPSRNG0                               | CPSOUT          | TOXCS |

| bit 7           |                                                                           |                                                    |                                                |                                                                              |                                       |                 | bit 0 |

|                 |                                                                           |                                                    |                                                |                                                                              |                                       |                 |       |

| Legend:         |                                                                           |                                                    |                                                |                                                                              |                                       |                 |       |

| R = Readable    | bit                                                                       | W = Writable I                                     | oit                                            | U = Unimpler                                                                 | nented bit, read                      | as '0'          |       |

| -n = Value at F | POR                                                                       | '1' = Bit is set                                   |                                                | '0' = Bit is cle                                                             | ared                                  | x = Bit is unkn | own   |

| bit 7           | 1 = Capacitiv                                                             | acitive Sensing<br>e sensing mod                   | ule is operat                                  | ing                                                                          |                                       |                 |       |

|                 | •                                                                         | •                                                  |                                                | ff and consumes                                                              | s no operating c                      | urrent          |       |

| bit 6-4         | Unimplement                                                               | ted: Read as '0                                    | )'                                             |                                                                              |                                       |                 |       |

| bit 3-2         | 00 = Oscillato<br>01 = Oscillato<br>10 = Oscillato                        | or is Off.<br>or is in low rang<br>or is in medium | e. Charge/di<br>range. Char                    | illator Range bit<br>ischarge current<br>ge/discharge cu<br>discharge currer | t is nominally 0.<br>Irrent is nomina | lly 1.2 μΑ.     |       |

| bit 1           | 1 = Oscillator                                                            | Ų                                                  | rrent (Currer                                  | Status bit<br>ht flowing out the<br>flowing into the                         | · /                                   |                 |       |

| bit 0           | If TOCS = 1<br>The TOXCS b<br>1 = Timer0 C<br>0 = Timer0 C<br>If TOCS = 0 | lock Source is<br>lock Source is                   | h clock exter<br>the capacitiv<br>the T0CKI pi | rnal to the core/<br>e sensing oscill                                        | ator                                  |                 | ):    |

### REGISTER 14-1: CPSCON0: CAPACITIVE SENSING CONTROL REGISTER 0

| LOISTER       |                                                                                                                                                                                       |                                                                                                                                                                                                                                         |                                                                                                                                                                        |                                                                                                                                    |                                                                   |                                                                              |              |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|------------------------------------------------------------------------------|--------------|

| U-0           | U-0                                                                                                                                                                                   | R/W-0                                                                                                                                                                                                                                   | R/W-0                                                                                                                                                                  | R/W-0                                                                                                                              | R/W-0                                                             | R/W-0                                                                        | R/W-0        |

|               | —                                                                                                                                                                                     | DCxB1                                                                                                                                                                                                                                   | DCxB0                                                                                                                                                                  | CCPxM3                                                                                                                             | CCPxM2                                                            | CCPxM1                                                                       | CCPxM0       |

| bit 7         |                                                                                                                                                                                       |                                                                                                                                                                                                                                         |                                                                                                                                                                        |                                                                                                                                    |                                                                   |                                                                              | bit (        |

|               |                                                                                                                                                                                       |                                                                                                                                                                                                                                         |                                                                                                                                                                        |                                                                                                                                    |                                                                   |                                                                              |              |

| Legend:       | 1.5                                                                                                                                                                                   |                                                                                                                                                                                                                                         |                                                                                                                                                                        |                                                                                                                                    |                                                                   |                                                                              |              |

| R = Readable  |                                                                                                                                                                                       | W = Writable                                                                                                                                                                                                                            |                                                                                                                                                                        | •                                                                                                                                  | nented bit, rea                                                   |                                                                              |              |

| -n = Value at | POR                                                                                                                                                                                   | '1' = Bit is set                                                                                                                                                                                                                        |                                                                                                                                                                        | '0' = Bit is cle                                                                                                                   | ared                                                              | x = Bit is unkr                                                              | nown         |

|               |                                                                                                                                                                                       |                                                                                                                                                                                                                                         |                                                                                                                                                                        |                                                                                                                                    |                                                                   |                                                                              |              |

| bit 7-6       | Unimplemen                                                                                                                                                                            | ted: Read as '                                                                                                                                                                                                                          | 0'                                                                                                                                                                     |                                                                                                                                    |                                                                   |                                                                              |              |

|               | Capture mode<br>Unused<br>Compare mod<br>Unused<br><u>PWM mode:</u><br>These bits are                                                                                                 | <u>de:</u>                                                                                                                                                                                                                              | of the PWM c                                                                                                                                                           | luty cycle. The                                                                                                                    | eight MSbs are                                                    | e found in CCP                                                               | RxL.         |

| bit 3-0       | 0000 = Captu<br>0001 = Unus<br>0010 = Comp<br>0011 = Unus<br>0100 = Captu<br>0101 = Captu<br>0110 = Captu<br>0111 = Captu<br>1000 = Comp<br>1001 = Comp<br>1010 = Comp<br>1011 = Comp | ed (reserved)<br>pare mode, tog<br>ed (reserved)<br>ure mode, even<br>ure mode, even<br>ure mode, even<br>pare mode, even<br>pare mode, set<br>pare mode, cle<br>pare mode, gen<br>coare mode, gen<br>pare mode, trig<br>A/D conversion | WM Off (reset<br>gle output on<br>y falling edge<br>y rising edge<br>y 4th rising ed<br>y 16th rising ed<br>output on ma<br>ar output on ma<br>herate softward<br>ted) | ts CCP module<br>match (CCPxIF<br>dge<br>tch (CCPxIF bit<br>atch (CCPxIF bit<br>e interrupt on m<br>vent (CCPxIF b<br>the ADC modu | of the PIRx<br>of the PIRx re<br>bit of the PIRx<br>hatch (CCPxIF | egister is set)<br>register is set)<br>bit is set of the<br>register is set. | PIRx registe |

### REGISTER 15-1: CCPxCON: CCPx CONTROL REGISTER

**Note 1:** A/D conversion start feature is available only on CCP2.

| Name    | Bit 7                                                                       | Bit 6          | Bit 5        | Bit 4        | Bit 3          | Bit 2    | Bit 1       | Bit 0   | Register<br>on Page |

|---------|-----------------------------------------------------------------------------|----------------|--------------|--------------|----------------|----------|-------------|---------|---------------------|

| ADCON0  | _                                                                           | _              | CHS3         | CHS2         | CHS1           | CHS0     | GO/<br>DONE | ADON    | 85                  |

| ANSELB  | _                                                                           | _              | ANSB5        | ANSB4        | ANSB3          | ANSB2    | ANSB1       | ANSB0   | 53                  |

| APFCON  | _                                                                           | _              | _            | _            | _              | —        | SSSEL       | CCP2SEL | 42                  |

| CCP1CON |                                                                             |                | DC1B1        | DC1B0        | CCP1M3         | CCP1M2   | CCP1M1      | CCP1M0  | 115                 |

| CCP2CON | _                                                                           | _              | DC2B1        | DC2B0        | CCP2M3         | CCP2M2   | CCP2M1      | CCP2M0  | 115                 |

| CCPRxL  | Capture/Co                                                                  | mpare/PWN      | I Register > | Low Byte     |                |          |             |         | 116                 |

| CCPRxH  | Capture/Co                                                                  | mpare/PWN      | I Register > | K High Byte  |                |          |             |         | 116                 |

| INTCON  | GIE                                                                         | PEIE           | TOIE         | INTE         | RBIE           | T0IF     | INTF        | RBIF    | 36                  |

| PIE1    | TMR1GIE                                                                     | ADIE           | RCIE         | TXIE         | SSPIE          | CCP1IE   | TMR2IE      | TMR1IE  | 37                  |

| PIE2    | _                                                                           | _              | _            | _            | _              |          | _           | CCP2IE  | 38                  |

| PIR1    | TMR1GIF                                                                     | ADIF           | RCIF         | TXIF         | SSPIF          | CCP1IF   | TMR2IF      | TMR1IF  | 39                  |

| PIR2    | _                                                                           | _              | _            | _            | _              |          | _           | CCP2IF  | 40                  |

| T1CON   | TMR1CS1                                                                     | TMR1CS0        | T1CKPS1      | T1CKPS0      | T1OSCEN        | T1SYNC   |             | TMR1ON  | 103                 |

| T1GCON  | TMR1GE                                                                      | T1GPOL         | T1GTM        | T1GSPM       | T1GGO/<br>DONE | T1GVAL   | T1GSS1      | T1GSS0  | 104                 |

| TMR1L   | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |                |              |              |                |          | 99          |         |                     |

| TMR1H   | Holding Re                                                                  | gister for the | Most Signi   | ificant Byte | of the 16-bit  | TMR1 Reg | gister      |         | 99                  |

| TRISB   | TRISB7                                                                      | TRISB6         | TRISB5       | TRISB4       | TRISB3         | TRISB2   | TRISB1      | TRISB0  | 52                  |

| TRISC   | TRISC7                                                                      | TRISC6         | TRISC5       | TRISC4       | TRISC3         | TRISC2   | TRISC1      | TRISC0  | 62                  |

| TABLE 15-4: | SUMMARY OF REGISTERS ASSOCIATED WITH COMPARE |

|-------------|----------------------------------------------|

|             |                                              |

Legend: - = Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the Compare.

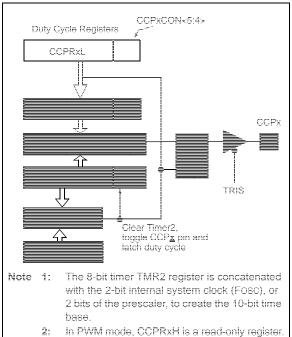

### 15.3 PWM Mode

The PWM mode generates a Pulse-Width Modulated signal on the CCPx pin. The duty cycle, period and resolution are determined by the following registers:

- PR2

- T2CON

- CCPRxL

- CCPxCON

In Pulse-Width Modulation (PWM) mode, the CCP module produces up to a 10-bit resolution PWM output on the CCPx pin.

Figure 15-3 shows a simplified block diagram of PWM operation.

Figure 15-4 shows a typical waveform of the PWM signal.

For a step-by-step procedure on how to set up the CCP module for PWM operation, refer to **Section 15.3.8** "Setup for PWM Operation".

FIGURE 15-3: SIMPLIFIED PWM BLOCK DIAGRAM

The PWM output (Figure 15-4) has a time base (period) and a time that the output stays high (duty cycle).

FIGURE 15-4: CCP PWM OUTPUT

### 15.3.1 CCPX PIN CONFIGURATION

In PWM mode, the CCPx pin is multiplexed with the PORT data latch. The user must configure the CCPx pin as an output by clearing the associated TRIS bit.

Either RC1 or RB3 can be selected as the CCP2 pin. Refer to **Section 6.1** "Alternate Pin Function" for more information.

| Note: | Clearing                                 | the | CCPxCON | register | will |  |  |  |  |

|-------|------------------------------------------|-----|---------|----------|------|--|--|--|--|

|       | relinquish CCPx control of the CCPx pin. |     |         |          |      |  |  |  |  |

# PIC16(L)F722A/723A

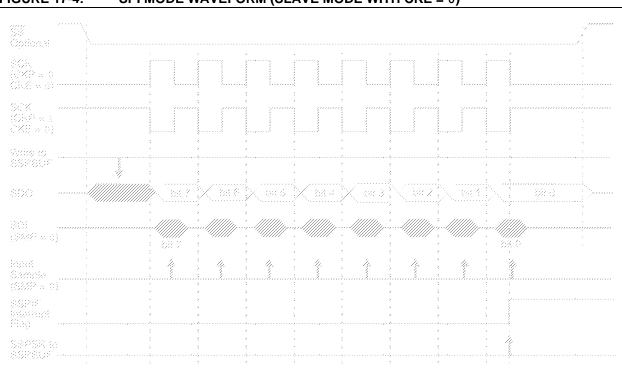

### FIGURE 17-4: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 0)

#### SS SCK (CKP = 0 $\dot{C}KE = 1)$ SCK (CKP = 1 CKE = 1) Write to SSPBUF bit 6 bit 5 bit 4 bit 2 bit 1 bit 0 SDO bit '7 bit 3 ï SDI (SMP = 0)I bit 0 bit 7 Input Sample (SMP = 0)SSPIF Interrupt Flag SSPSR to SSPBUF 1 . i . . . .

### FIGURE 17-5: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

| Name    | Bit 7                                                    | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Register<br>on Page |

|---------|----------------------------------------------------------|---------|---------|---------|---------|--------|---------|---------|---------------------|

| ANSELA  | —                                                        | —       | ANSA5   | ANSA4   | ANSA3   | ANSA2  | ANSA1   | ANSA0   | 44                  |

| APFCON  | —                                                        | —       | _       | _       | —       | _      | SSSEL   | CCP2SEL | 42                  |

| INTCON  | GIE                                                      | PEIE    | T0IE    | INTE    | RBIE    | TOIF   | INTF    | RBIF    | 36                  |

| PIE1    | TMR1GIE                                                  | ADIE    | RCIE    | TXIE    | SSPIE   | CCP1IE | TMR2IE  | TMR1IE  | 37                  |

| PIR1    | TMR1GIF                                                  | ADIF    | RCIF    | TXIF    | SSPIF   | CCP1IF | TMR2IF  | TMR1IF  | 39                  |

| PR2     | Timer2 Period Register                                   |         |         |         |         |        |         |         | 106                 |

| SSPBUF  | Synchronous Serial Port Receive Buffer/Transmit Register |         |         |         |         |        |         | 147     |                     |

| SSPCON  | WCOL                                                     | SSPOV   | SSPEN   | CKP     | SSPM3   | SSPM2  | SSPM1   | SSPM0   | 152                 |

| SSPSTAT | SMP                                                      | CKE     | D/A     | Р       | S       | R/W    | UA      | BF      | 153                 |

| TRISA   | TRISA7                                                   | TRISA6  | TRISA5  | TRISA4  | TRISA3  | TRISA2 | TRISA1  | TRISA0  | 43                  |

| TRISC   | TRISC7                                                   | TRISC6  | TRISC5  | TRISC4  | TRISC3  | TRISC2 | TRISC1  | TRISC0  | 62                  |

| T2CON   |                                                          | TOUTPS3 | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | 107                 |

### TABLE 17-1: SUMMARY OF REGISTERS ASSOCIATED WITH SPI OPERATION

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the SSP in SPI mode.

# 18.0 PROGRAM MEMORY READ

The Flash program memory is readable during normal operation over the full VDD range of the device. To read data from program memory, five Special Function Registers (SFRs) are used:

- PMCON1

- PMDATL

- PMDATH

- PMADRL

- PMADRH

The value written to the PMADRH:PMADRL register pair determines which program memory location is read. The read operation will be initiated by setting the RD bit of the PMCON1 register. The program memory Flash controller takes two instructions to complete the read. As a consequence, after the RD bit has been set, the next two instructions will be ignored. To avoid conflict with program execution, it is recommended that the two instructions following the setting of the RD bit are NOP. When the read completes, the result is placed in the PMDATLH:PMDATL register pair. Refer to Example 18-1 for sample code.

**Note:** Code-protect does not effect the CPU from performing a read operation on the program memory. For more information, refer to **Section 8.2 "Code Protection"**

### EXAMPLE 18-1: PROGRAM MEMORY READ

BANKSEL PMADRL ; MOVE MS PROG ADDR, W; MOVWF PMADRH ;MS Byte of Program Address to read MOVF LS\_PROG\_ADDR, W; MOVWF PMADRL ;LS Byte of Program Address to read BANKSEL PMCON1 ; BSF PMCON1, RD; Initiate Read Required NOP NOP ;Any instructions here are ignored as program ;memory is read in second cycle after BSF BANKSEL PMDATL ; MOVF PMDATL, W;W = LS Byte of Program Memory Read MOVWF LOWPMBYTE; MOVF PMDATH, W;W = MS Byte of Program Memory Read MOVWF HIGHPMBYTE;

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             | DC CH | IARACTERISTICS                       | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |      |          |       |                                                                        |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|-------|------------------------------------------------------------------------|--|--|--|

| $ \begin{array}{  c                                  $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |             | Sym.  | Characteristic                       | Min.                                                                                                                                                                                    | Тур† | Max.     | Units | Conditions                                                             |  |  |  |

| D030<br>D030A         with TTL buffer           0.8         V         4.5V ≤ VDD ≤ 5.5V           D031         with Schmitt Trigger buffer<br>with I <sup>2</sup> C levels          0.15 VDD         V         1.8V ≤ VDD ≤ 4.5V           D032         MCLR, OSC1 (RC mode) <sup>(1)</sup> 0.2 VDD         V         2.0V ≤ VDD ≤ 5.5V           D033A         OSC1 (HS mode)          0.3 VDD         V            D040         OSC1 (HS mode)           0.3 VDD         V            D040         VH         Input High Voltage           V         4.5V ≤ VDD ≤ 5.5V           D040         with TTL buffer         2.0           V         4.5V ≤ VDD ≤ 5.5V           D041         with Schmitt Trigger buffer<br>with I <sup>2</sup> C levels         0.8 VDD           V         1.8V ≤ VDD ≤ 5.5V           D042         OSC1 (HS mode)         0.7 VDD           V         2.0V ≤ VDD ≤ 5.5V           D043B         OSC1 (HC mode)         0.9 VDD           V         1.8V ≤ VDD ≤ 5.5V           D043B         IncLaR(3)          ± 5         ± 1000         n                                                                             | ١           | VIL   | Input Low Voltage                    |                                                                                                                                                                                         |      |          |       |                                                                        |  |  |  |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |       | I/O PORT:                            |                                                                                                                                                                                         |      |          |       |                                                                        |  |  |  |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | D030        |       | with TTL buffer                      | —                                                                                                                                                                                       | _    | 0.8      | V     | $4.5V \leq V\text{DD} \leq 5.5V$                                       |  |  |  |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | D030A       |       |                                      | —                                                                                                                                                                                       |      | 0.15 Vdd | V     | $1.8V \le V \text{DD} \le 4.5V$                                        |  |  |  |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | D031        |       | with Schmitt Trigger buffer          | —                                                                                                                                                                                       |      | 0.2 Vdd  | V     | $2.0V \le V \text{DD} \le 5.5 \text{V}$                                |  |  |  |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |       | with I <sup>2</sup> C levels         | —                                                                                                                                                                                       |      | 0.3 Vdd  | V     |                                                                        |  |  |  |

| Virit         Input High Voltage          V         4.5V $\leq$ VDD $\leq$ 5.5V           D040         with TTL buffer         2.0           V         4.5V $\leq$ VDD $\leq$ 5.5V           D041         with TTL buffer         2.0           V         4.5V $\leq$ VDD $\leq$ 5.5V           D041         with Schmitt Trigger buffer         0.8 VDD           V         1.8V $\leq$ VDD $\leq$ 5.5V           D042         MCLR         0.8 VDD           V         2.0V $\leq$ VDD $\leq$ 5.5V           D043A         OSC1 (HS mode)         0.7 VDD           V         2.0V $\leq$ VDD $\leq$ 5.5V           D043B         OSC1 (HS mode)         0.9 VDD           V         2.0V $\leq$ VDD, Pin at high impediance, 85°C           D043B         OSC1 (HS mode)         0.9 VDD         -         -         V         (Note 1)           D043B         IIL         Input Leakage Current <sup>(2)</sup> - $\pm$ 50 $\pm$ 1000         nA         VSS $\leq$ VPIN $\leq$ VDD, 85°C           D060         IPUR         PORTB Weak Pull-up Current         - $\pm$ 50 $\pm$ 1000         nA         VDS $\leq$ 5.0V, VPIN $=$ VSS           D | D032        |       | MCLR, OSC1 (RC mode) <sup>(1)</sup>  |                                                                                                                                                                                         | _    | 0.2 Vdd  | V     |                                                                        |  |  |  |

| D040         I/O ports:<br>with TTL buffer            V         4.5V ≤ VbD ≤ 5.5V           D041         with TTL buffer $0.25$ VbD +           V $1.8V \le VbD \le 5.5V$ D041         with Schmitt Trigger buffer<br>with I <sup>2</sup> C levels $0.8$ VbD           V $1.8V \le VbD \le 5.5V$ D042         MCLR $0.8$ VbD           V $2.0V \le VbD \le 5.5V$ D043         OSC1 (HS mode) $0.7$ VbD           V $0.0V \le VbD \le 5.5V$ D0438         OSC1 (RC mode) $0.7$ VbD           V $0.0V \le VbD \le 5.5V$ D0438         IIL         Input Leakage Current(2) $0.7$ VbD          -         V $0.0V \le 5.5V$ D060         IIL         Input Leakage Current(2) $0.9$ VbD         -         -         V $(Note 1)$ D060         IVCR <sup>(3)</sup> - $\pm 5$ $\pm 1000$ $nA$ $VSS \le VPIN \le VbD, Pin at higt impedance, 85°C           D060         IVCR(3)         -         \pm 5 \pm 1000 nA VSS \le VPIN \le VbD, $                                                                                                                                                                                                                   | D033A       |       | OSC1 (HS mode)                       |                                                                                                                                                                                         | _    | 0.3 Vdd  | V     |                                                                        |  |  |  |

| D040         with TTL buffer $2.0$ $  V$ $4.5V \le VDD \le 5.5V$ D041         with Schmitt Trigger buffer with 1 <sup>2</sup> C levels $0.25 VDD +$ $  V$ $1.8V \le VDD \le 5.5V$ D042         MCLR $0.8 VDD$ $  V$ $2.0V \le VDD \le 5.5V$ D043         OSC1 (HS mode) $0.7 VDD$ $  V$ D043B         OSC1 (RC mode) $0.9 VDD$ $  V$ D043B         OSC1 (RC mode) $0.9 VDD$ $  V$ (Note 1)           D040         Input Leakage Current( <sup>2</sup> ) $ \pm 5$ $\pm 1000$ $nA$ VSS $\le VPIN \le VDD$ , Pin at high impedance, $8^{SC}C$ D061         IPUR         IPUR         PORTB Weak Pull-up Current $ \pm 50$ $\pm 200$ $nA$ VSS $\le VPIN \le VDD, 8^{SC}C$ D070*         IPUR         PORTB Weak Pull-up Current $  0.6$ $V$ IoL = $8 mA, VDD = 5V$ D080         VoL         Output Low Voltage <sup>(4)</sup> $VDD - 0.7$ $ -$ <td< td=""><td>\</td><td>Vih</td><td>Input High Voltage</td><td></td><td></td><td></td><td></td><td></td></td<>                                                                                                                                                                                              | \           | Vih   | Input High Voltage                   |                                                                                                                                                                                         |      |          |       |                                                                        |  |  |  |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |       | I/O ports:                           |                                                                                                                                                                                         | _    | _        |       |                                                                        |  |  |  |

| D041         with Schmitt Trigger buffer<br>with $ ^2$ C levels         0.8              D042         MCLR         0.8 VDD           V         2.0V $\leq$ VDD $\leq$ 5.5V           D043A         OSC1 (HS mode)         0.7 VDD           V            D043B         OSC1 (RC mode)         0.7 VDD           V            D043B         OSC1 (RC mode)         0.9 VDD           V            D043B         ILL         Input Leakage Current(2)           V            D060         MCLR(3) $\pm$ 50 $\pm$ 1000         nA         VSS $\leq$ VPIN $\leq$ VDD, Pin at high<br>impedance, 85°C           D061         MCLR(3) $\pm$ 50 $\pm$ 200         nA         VSS $\leq$ VPIN $\leq$ VDD, 85°C           D070*         IPUR         PORTB Weak Pull-up Current           VDD $=$ 3.3V, VPIN $=$ VSS           D080         Vol         Output Low Voltage <sup>(4)</sup> D090         VOH         Output High Voltage <sup>(4)</sup>                                                                                                                                                                                                           | D040        |       | with TTL buffer                      | 2.0                                                                                                                                                                                     | _    | —        | V     | $4.5V \leq V\text{DD} \leq 5.5V$                                       |  |  |  |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | D040A       |       |                                      |                                                                                                                                                                                         | —    | -        | V     | $1.8V \leq V\text{DD} \leq 4.5V$                                       |  |  |  |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | D041        |       | with Schmitt Trigger buffer          | 0.8 VDD                                                                                                                                                                                 |      | —        | V     | $2.0V \le V \text{DD} \le 5.5 V$                                       |  |  |  |

| D043A<br>D043BOSC1 (HS mode)<br>OSC1 (RC mode) $0.7 \ VDD$ $  V$ D043BOSC1 (RC mode) $0.9 \ VDD$ $  V$ (Note 1)D060IIL<br>II/O portsInput Leakage Current(2) $V$ $V$ $V$ (Note 1)D061Input Leakage Current(2) $ \pm 5$ $\pm 125$ $nA$ $V$ (SS $\leq V$ PIN $\leq V$ DD, Pin at high<br>impedance, 85°CD061MCLR(3) $ \pm 5$ $\pm 1000$ $nA$ $V$ SS $\leq V$ PIN $\leq V$ DD, 85°CD070*PORTB Weak Pull-up Current $25$ $100$ $200$ $A$ $V$ SS $\leq V$ PIN $\leq V$ DD, 85°CD070*Vol.Output Low Voltage(4) $25$ $100$ $200$ $\mu A$ $V$ DD $= 3.3V, V$ PIN $= V$ SSD080Vol.Output Low Voltage(4) $   0.6$ $V$ $IOL = 8 \ mA, VDD = 5V$<br>$IOL = 6 \ mA, VDD = 3.3V$<br>$IOL = 1.8 \ mA, VDD = 1.8V$ D090VOHOutput High Voltage(4) $V$ $IOH = 3.5 \ mA, VDD = 5V$<br>$IOL = 3 \ mA, VDD = 3.3V$<br>$IOH = 1 \ mA, VDD = 1.8V$ D101*COSC2OSC2 pin $   15$ $pF$ $In XT, HS \ and LP \ modes \ wheexternal clock is used to driveOSC1D101*CioAll I/O pins  50pF$                                                                                                                                                                                             |             |       | with I <sup>2</sup> C levels         | 0.7 VDD                                                                                                                                                                                 | _    | —        | V     |                                                                        |  |  |  |

| D043BOSC1 (RC mode) $0.9 \text{ VDD}$ $  V$ (Note 1)D060IILInput Leakage Current <sup>(2)</sup> D060 $VO$ ports $ \pm 5$ $\pm 125$ nAVSS $\leq$ VPIN $\leq$ VDD, Pin at high impedance, 85°CD061MCLR <sup>(3)</sup> $ \pm 5$ $\pm 1000$ nA125°CD061MCLR <sup>(3)</sup> $ \pm 50$ $\pm 200$ nAVSS $\leq$ VPIN $\leq$ VDD, 85°CD070*PORTB Weak Pull-up Current $255$ 140 $300$ $\mu$ AVDD = 3.3V, VPIN $=$ VSSD070*Vol.Output Low Voltage <sup>(4)</sup> $VDD$ $200$ $\mu$ AVDD = 5.0V, VPIN $=$ VSSD080Vol.Output Low Voltage <sup>(4)</sup> $  0.6$ $V$ IOL = 8 mA, VDD $= 5V$ D080VOHOutput High Voltage <sup>(4)</sup> $  0.6$ $V$ IOL = 8 mA, VDD $= 5V$ D090VOHOutput High Voltage <sup>(4)</sup> $   0.6$ $V$ IOL = 8 mA, VDD $= 5V$ D101*COSC2OSC2 pin $    V$ IOH $= 3.5$ mA, VDD $= 5V$ D101*CioAll I/O pins $  15$ pFIn XT, HS and LP modes whe external clock is used to drive OSC1D101A*CioAll I/O pins $   50$ pF                                                                                                                                                                                                                           | D042        |       | MCLR                                 | 0.8 VDD                                                                                                                                                                                 | _    | —        | V     |                                                                        |  |  |  |

| IIL<br>D060Input Leakage Current <sup>(2)</sup> Input Leakage Current <sup>(2)</sup> D061I/O ports $ \pm 5$ $\pm 125$ nAVSS $\leq$ VPIN $\leq$ VDD, Pin at high<br>impedance, 85°CD061MCLR <sup>(3)</sup> $ \pm 5$ $\pm 1000$ nA125°CD061MCLR <sup>(3)</sup> $ \pm 50$ $\pm 200$ nAVSS $\leq$ VPIN $\leq$ VDD, 85°CD070*PORTB Weak Pull-up CurrentVDD $25$ 100200 $\mu$ AVDD = 3.3V, VPIN $=$ VSSD070*VolOutput Low Voltage <sup>(4)</sup> VDD $25$ 140300 $\mu$ AVDD = 5.0V, VPIN $=$ VSSD080VolOutput Low Voltage <sup>(4)</sup> $  0.6$ VIOL = 8 mA, VDD = 5VD080I/O ports $  0.6$ VIOL = 6 mA, VDD = 3.3VD090VOHOutput High Voltage <sup>(4)</sup> $VDD - 0.7$ $ -$ VIOH = 3.5 mA, VDD = 5VD091I/O portsVDD - 0.7 $ -$ VIOH = 3.5 mA, VDD = 5VD101*COSC2OSC2 pin $ -$ 15pFIn XT, HS and LP modes whe external clock is used to drive OSC1D1014*CioAll I/O pins $ -$ 50pF                                                                                                                                                                                                                                                                            | D043A       |       | OSC1 (HS mode)                       | 0.7 VDD                                                                                                                                                                                 | _    | —        | V     |                                                                        |  |  |  |

| D060 $VO$ ports $ \pm 5$ $\pm 125$ nA $VSS \le VPIN \le VDD$ , Pin at high<br>impedance, 85°C<br>125°CD061 $MCLR^{(3)}$ $ \pm 5$ $\pm 1000$ nA $VSS \le VPIN \le VDD$ , 85°CD070* $PORTB$ Weak Pull-up Current $\pm 50$ $\pm 200$ nA $VSS \le VPIN \le VDD$ , 85°CD070* $PORTB$ Weak Pull-up Current $25$ $100$ $200$ $\mu A$ $VDD = 3.3V, VPIN = VSS$ D070* $VOL$ $Output Low Voltage^{(4)}$ $VDD$ $250$ $\mu A$ $VDD = 5.0V, VPIN = VSS$ D080 $VOL$ $Output Low Voltage^{(4)}$ $  0.6$ $V$ $IOL = 8$ mA, VDD = 5VD080 $I/O$ ports $  0.6$ $V$ $IOL = 8$ mA, VDD = 5VD080 $I/O$ ports $  0.6$ $V$ $IOL = 8$ mA, VDD = 5VD090 $I/O$ ports $  0.6$ $V$ $IOL = 8$ mA, VDD = 5VD090 $I/O$ ports $VDD - 0.7$ $  V$ $IOH = 3.5$ mA, VDD = 5VD101* $COSC2$ $COSC2$ $OSC2$ pin $  15$ $pF$ In XT, HS and LP modes whe external clock is used to drive OSC1D101A*CioAll I/O pins $  50$ $pF$                                                                                                                                                                                                                                                                    | D043B       |       |                                      | 0.9 Vdd                                                                                                                                                                                 |      | —        | V     | (Note 1)                                                               |  |  |  |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1           | lı∟   | Input Leakage Current <sup>(2)</sup> | •                                                                                                                                                                                       |      | •        |       | ·                                                                      |  |  |  |

| D061 $\overline{\text{MCLR}^{(3)}}$ $ \pm 50$ $\pm 200$ nA $\text{VSS} \leq \text{VPIN} \leq \text{VDD}, 85^{\circ}\text{C}$ D070*IPUR <b>PORTB Weak Pull-up Current</b> $25$ 100200 $\mu A$ $\text{VDD} = 3.3\text{V}, \text{VPIN} = \text{VSS}$ D070* $VOL$ <b>Output Low Voltage</b> <sup>(4)</sup> $25$ 140300 $\mu A$ $\text{VDD} = 5.0\text{V}, \text{VPIN} = \text{VSS}$ D080 $VOL$ <b>Output Low Voltage</b> <sup>(4)</sup> $  0.6$ $V$ $IOL = 8 \text{ mA}, \text{VDD} = 5V$ D080 $VOH$ <b>Output High Voltage</b> <sup>(4)</sup> $  0.6$ $V$ $IOL = 6 \text{ mA}, \text{VDD} = 3.3V$ D090 $VOH$ <b>Output High Voltage</b> <sup>(4)</sup> $VDD - 0.7$ $  V$ $IOH = 3.5 \text{ mA}, \text{VDD} = 5V$ D090 $VOH$ <b>Output High Voltage</b> <sup>(4)</sup> $VDD - 0.7$ $  V$ $IOH = 3.5 \text{ mA}, \text{VDD} = 5V$ D101* $COSC2$ $OSC2 \text{ pin}$ $  15$ $pF$ $In XT, HS \text{ and } LP  modes whe external clock is used to drive OSC1D101A*CIOAll I/O pins   50pF$                                                                                                                                                                       | D060        |       | I/O ports                            | —                                                                                                                                                                                       | ± 5  |          | nA    |                                                                        |  |  |  |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |             |       |                                      |                                                                                                                                                                                         |      |          | nA    |                                                                        |  |  |  |

| D070*25100200VDD = 3.3V, VPIN = VSSD080VOLOutput Low Voltage(4) $300$ $\mu A$ VDD = 5.0V, VPIN = VSSD080VOLI/O ports $  0.6$ VIOL = 8 mA, VDD = 5VD090VOHOutput High Voltage(4) $  0.6$ VIOL = 6 mA, VDD = 3.3VD090VOHOutput High Voltage(4) $   0.6$ VIOH = 3.5 mA, VDD = 5VD090VOHOutput High Voltage(4) $VD - 0.7$ $  V$ IOH = 3.5 mA, VDD = 5VD090VOHOutput High Voltage(5)VDD - 0.7 $  V$ IOH = 3.5 mA, VDD = 5VD101*COSC2OSC2 pin $ -$ 15pFIn XT, HS and LP modes whe external clock is used to drive OSC1D101A*CIOAll I/O pins $ -$ 50pF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | D061        |       |                                      | —                                                                                                                                                                                       | ± 50 | ± 200    | nA    | $VSS \le VPIN \le VDD, 85^{\circ}C$                                    |  |  |  |

| $\frac{1}{10000000000000000000000000000000000$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1           | IPUR  | PORTB Weak Pull-up Current           |                                                                                                                                                                                         |      |          |       |                                                                        |  |  |  |

| VOL<br>D080Output Low Voltage(4)I/O portsI/O portsVOH<br>D090Output High Voltage(4)VOH<br>I/O portsOutput High Voltage(4)I/O portsVDD - 0.7I/O portsVDD - 0.7I/O portsVDD - 0.7IOL = 3 mA, VDD = 3.3V<br>IOH = 3 mA, VDD = 3.3V<br>IOH = 1 mA, VDD = 1.8VD101*COSC2OSC2 pinD101A*CioAll I/O pinsD101A*CioAll I/O pinsD101A*All I/O pinsD101A*CioD101A*All I/O pinsD101A*CioD101A*All I/O pinsD101A*CioD101A*CioD101A*CioD101A*CioD101A*CioD101A*CioD101A*CioD101A*CioD101A*CioD101A*CioD101A*CioD101A*CioD101A*CioD101A*CioD101A*CioD101A*CioD101A*CioD101A*CioD101A*CioD101A*CioD101A*CioD101A*CioD101A*CioD101A*CioD101A*CioD101A*CioD101A*CioD101A*CioD101A*CioD101A*CioD101A*Ci                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | D070*       |       |                                      |                                                                                                                                                                                         |      |          | .     |                                                                        |  |  |  |

| D080I/O ports0.6VIOL = 8 mA, VDD = 5V<br>IOL = 6 mA, VDD = 3.3V<br>IOL = 1.8 mA, VDD = 1.8VD090VOHOutput High Voltage <sup>(4)</sup> VIOH = 3.5 mA, VDD = 5V<br>IOH = 3 mA, VDD = 5V<br>IOH = 3 mA, VDD = 5V<br>IOH = 3 mA, VDD = 3.3V<br>IOH = 1 mA, VDD = 3.3V<br>IOH = 1 mA, VDD = 1.8VD101*COSC2OSC2 pin15pFIn XT, HS and LP modes whe<br>external clock is used to drive<br>OSC1D101A*CioAll I/O pins50pF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |             |       | <b>A</b> (4)                         | 25                                                                                                                                                                                      | 140  | 300      | μA    | VDD = 5.0V, VPIN = VSS                                                 |  |  |  |