Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 128 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 11x8b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 28-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf722at-i-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 DEVICE OVERVIEW

The PIC16(L)F722A/723A devices are covered by this data sheet. They are available in 28-pin packages. Figure 1-1 shows a block diagram of the PIC16(L)F722A/723A devices. Table 1-1 shows the pinout descriptions.

#### FIGURE 2-3:

# PIC16(L)F722A SPECIAL FUNCTION REGISTERS

| Indirect addr.(*)  | 00h | Indirect addr. <sup>(*)</sup>              | 80h       | Indirect addr. <sup>(*)</sup> | 100h | Indirect addr.(*)   | 180h |

|--------------------|-----|--------------------------------------------|-----------|-------------------------------|------|---------------------|------|

| TMR0               | 01h | OPTION                                     | 81h       | TMR0                          | 101h | OPTION              | 181h |

| PCL                | 02h | PCL                                        | 82h       | PCL                           | 102h | PCL                 | 182h |

| STATUS             | 03h | STATUS                                     | 83h       | STATUS                        | 103h | STATUS              | 183h |

| FSR                | 04h | FSR                                        | 84h       | FSR                           | 104h | FSR                 | 184h |

| PORTA              | 05h | TRISA                                      | 85h       |                               | 105h | ANSELA              | 185h |

| PORTB              | 06h | TRISB                                      | 86h       |                               | 106h | ANSELB              | 186h |

| PORTC              | 07h | TRISC                                      | 87h       |                               | 107h |                     | 187h |

|                    | 08h |                                            | 88h       | CPSCON0                       | 108h |                     | 188h |

| PORTE              | 09h | TRISE                                      | 89h       | CPSCON1                       | 109h |                     | 189h |

| PCLATH             | 0Ah | PCLATH                                     | 8Ah       | PCLATH                        | 10Ah | PCLATH              | 18Ah |

| INTCON             | 0Bh | INTCON                                     | 8Bh       | INTCON                        | 10Bh | INTCON              | 18Bh |

| PIR1               | 0Ch | PIE1                                       | 8Ch       | PMDATL                        | 10Ch | PMCON1              | 18Ch |

| PIR2               | 0Dh | PIE2                                       | 8Dh       | PMADRL                        | 10Dh | Reserved            | 18Dh |

| TMR1L              | 0Eh | PCON                                       | 8Eh       | PMDATH                        | 10Eh | Reserved            | 18Eh |

| TMR1H              | 0Fh | T1GCON                                     | 8Fh       | PMADRH                        | 10Fh | Reserved            | 18Fh |

| T1CON              | 10h | OSCCON                                     | 90h       |                               | 110h |                     | 190h |

| TMR2               | 11h | OSCTUNE                                    | 91h       |                               | 111h |                     | 191h |

| T2CON              | 12h | PR2                                        | 92h       |                               | 112h |                     | 192h |

| SSPBUF             | 13h | SSPADD/SSPMSK                              | 93h       |                               | 113h |                     | 193h |

| SSPCON             | 14h | SSPSTAT                                    | 94h       |                               | 114h |                     | 194h |

| CCPR1L             | 15h | WPUB                                       | 95h       |                               | 115h |                     | 195h |

| CCPR1H             | 16h | IOCB                                       | 96h       |                               | 116h |                     | 196h |

| CCP1CON            | 17h |                                            | 97h       |                               | 117h |                     | 197h |

| RCSTA              | 18h | TXSTA                                      | 98h       |                               | 118h |                     | 198h |

| TXREG              | 19h | SPBRG                                      | 99h       |                               | 119h |                     | 199h |

| RCREG              | 1Ah |                                            | 9Ah       |                               | 11Ah |                     | 19Ah |

| CCPR2L             | 1Bh |                                            | 9Bh       |                               | 11Bh |                     | 19Bh |

| CCPR2H             | 1Ch | APFCON                                     | 9Ch       |                               | 11Ch |                     | 19Ch |

| CCP2CON            | 1Dh | FVRCON                                     | 9Dh       |                               | 11Dh |                     | 19Dh |

| ADRES              | 1Eh |                                            | 9Eh       |                               | 11Eh |                     | 19Eh |

| ADCON0             | 1Fh | ADCON1                                     | 9Fh       |                               | 11Fh |                     | 19Fh |

|                    | 20h |                                            | A0h       |                               | 120h |                     | 1A0h |

| General<br>Purpose |     | General<br>Purpose<br>Register<br>32 Bytes | BFh       |                               |      |                     |      |

| Register           |     |                                            | C0h       |                               |      |                     |      |

| 96 Bytes           |     |                                            | EFh       |                               | 16Fh |                     | 1EFh |

| -                  |     |                                            | F0h       |                               | 170h |                     | 1F0h |

|                    |     | Accesses<br>70h-7Fh                        |           | Accesses<br>70h-7Fh           |      | Accesses<br>70h-7Fh |      |

|                    | 7Fh |                                            | FFh       |                               | 17Fh |                     | 1FFh |

| Bank 0             |     | Bank 1                                     |           | Bank 2                        |      | Bank 3              |      |

|                    |     | nted data memory loc<br>cal register.      | ations, I | read as '0'.                  |      |                     |      |

#### 4.5.1 INTCON REGISTER

The INTCON register is a readable and writable register, which contains the various enable and flag bits for TMR0 register overflow, PORTB change and external RB0/INT/SEG0 pin interrupts.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 4-1: INTCON: INTERRUPT CONTROL REGISTER

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0               | R/W-0               | R/W-0 | R/W-x |

|-------|-------|-------|-------|---------------------|---------------------|-------|-------|

| GIE   | PEIE  | TOIE  | INTE  | RBIE <sup>(1)</sup> | T0IF <sup>(2)</sup> | INTF  | RBIF  |

| bit 7 |       |       |       |                     |                     |       | bit 0 |

|       |       |       |       |                     |                     |       |       |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7        | GIE: Global Interrupt Enable bit                                                                                            |

|--------------|-----------------------------------------------------------------------------------------------------------------------------|

|              | 1 = Enables all unmasked interrupts                                                                                         |

|              | 0 = Disables all interrupts                                                                                                 |

| bit 6        | PEIE: Peripheral Interrupt Enable bit                                                                                       |

|              | 1 = Enables all unmasked peripheral interrupts<br>0 = Disables all peripheral interrupts                                    |

| L:1. F       |                                                                                                                             |

| bit 5        | <b>TolE:</b> Timer0 Overflow Interrupt Enable bit<br>1 = Enables the Timer0 interrupt                                       |

|              | 0 = Disables the Timer0 interrupt                                                                                           |

| bit 4        | INTE: RB0/INT External Interrupt Enable bit                                                                                 |

|              | 1 = Enables the RB0/INT external interrupt                                                                                  |

|              | 0 = Disables the RB0/INT external interrupt                                                                                 |

| bit 3        | RBIE: PORTB Change Interrupt Enable bit <sup>(1)</sup>                                                                      |

|              | 1 = Enables the PORTB change interrupt                                                                                      |

|              | 0 = Disables the PORTB change interrupt                                                                                     |

| bit 2        | <b>T0IF:</b> Timer0 Overflow Interrupt Flag bit <sup>(2)</sup>                                                              |

|              | 1 = TMR0 register has overflowed (must be cleared in software)                                                              |

|              | 0 = TMR0 register did not overflow                                                                                          |

| bit 1        | INTF: RB0/INT External Interrupt Flag bit<br>1 = The RB0/INT external interrupt occurred (must be cleared in software)      |

|              | 0 = The RBO/INT external interrupt did not occur                                                                            |

| bit 0        | <b>RBIF:</b> PORTB Change Interrupt Flag bit                                                                                |

| bit 0        | <ul> <li>1 = When at least one of the PORTB general purpose I/O pins changed state (must be cleared in software)</li> </ul> |

|              | 0 = None of the PORTB general purpose I/O pins have changed state                                                           |

| <b>N</b> 4 4 |                                                                                                                             |

| Note 1:      | The appropriate bits in the IOCB register must also be set.                                                                 |

- **Note 1:** The appropriate bits in the IOCB register must also be set.

- 2: T0IF bit is set when Timer0 rolls over. Timer0 is unchanged on Reset and should be initialized before clearing T0IF bit.

#### 6.2.1 ANSELA REGISTER

The ANSELA register (Register 6-4) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELA bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELA bits has no affect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

#### REGISTER 6-4: ANSELA: PORTA ANALOG SELECT REGISTER

'1' = Bit is set

| U-0                               | U-0 | R/W-1 | R/W-1        | R/W-1            | R/W-1    | R/W-1 | R/W-1 |

|-----------------------------------|-----|-------|--------------|------------------|----------|-------|-------|

| —                                 | —   | ANSA5 | ANSA4        | ANSA3            | ANSA2    | ANSA1 | ANSA0 |

| bit 7                             |     |       |              |                  |          |       | bit 0 |

|                                   |     |       |              |                  |          |       |       |

| Legend:                           |     |       |              |                  |          |       |       |

| R = Readable bit W = Writable bit |     | bit   | U = Unimpler | mented bit, read | l as '0' |       |       |

'0' = Bit is cleared

bit 7-6 Unimplemented: Read as '0'

-n = Value at POR

bit 5-0 **ANSA<5:0>**: Analog Select between Analog or Digital Function on pins RA<5:0>, respectively 0 = Digital I/O. Pin is assigned to port or digital special function. 1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

x = Bit is unknown

# PIC16(L)F722A/723A

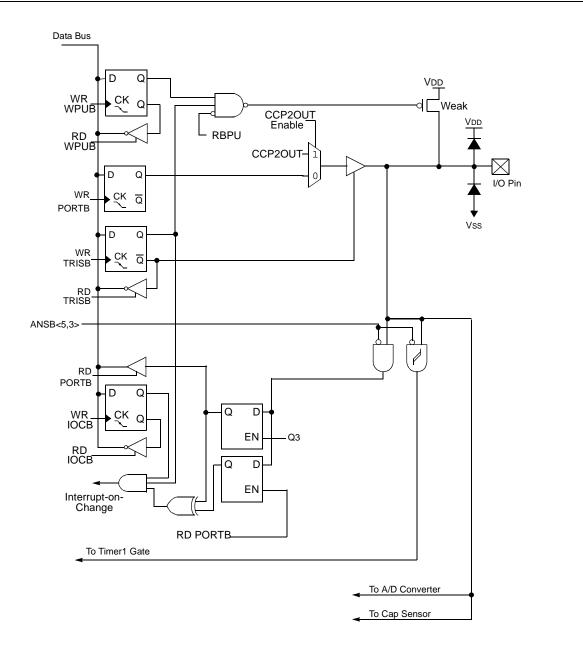

# FIGURE 6-10: BLOCK DIAGRAM OF RB5

# 6.4 PORTC and TRISC Registers

PORTC is a 8-bit wide, bidirectional port. The corresponding data direction register is TRISC (Register 6-11). Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 6-3 shows how to initialize PORTC.

Reading the PORTC register (Register 6-10) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch.

The TRISC register (Register 6-11) controls the PORTC pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISC register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

#### EXAMPLE 6-3: INITIALIZING PORTC

| BANKSEL PORTC  | ;                          |

|----------------|----------------------------|

| CLRF PORTC     | ;Init PORTC                |

| BANKSEL TRISC  | i                          |

| MOVLW B'000011 | 00' ;Set RC<3:2> as inputs |

| MOVWF TRISC    | ;and set RC<7:4,1:0>       |

|                | ;as outputs                |

|                |                            |

The location of the CCP2 function is controlled by the CCP2SEL bit in the APFCON register (refer to Register 6-1).

#### REGISTER 6-10: PORTC: PORTC REGISTER

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| RC7   | RC6   | RC5   | RC4   | RC3   | RC2   | RC1   | RC0   |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 RC<7:0>: PORTC General Purpose I/O Pin bits

1 = Port pin is > VIH 0 = Port pin is < VIL

#### REGISTER 6-11: TRISC: PORTC TRI-STATE REGISTER

| R/W-1  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| TRISC7 | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-0 TRISC<7:0>: PORTC Tri-State Control bits

1 = PORTC pin configured as an input (tri-stated)

0 = PORTC pin configured as an output

| TABLE 6-4: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTC |

|------------|--------------------------------------------|

|            |                                            |

| Name    | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0   | Register<br>on Page |

|---------|---------|---------|---------|---------|---------|--------|--------|---------|---------------------|

| APFCON  | —       | _       | _       | _       | —       | —      | SSSEL  | CCP2SEL | 42                  |

| CCP1CON | —       | _       | DC1B1   | DC1B0   | CCP1M3  | CCP1M2 | CCP1M1 | CCP1M0  | 115                 |

| CCP2CON | —       | —       | DC2B1   | DC2B0   | CCP2M3  | CCP2M2 | CCP2M1 | CCP2M0  | 115                 |

| PORTC   | RC7     | RC6     | RC5     | RC4     | RC3     | RC2    | RC1    | RC0     | 62                  |

| RCSTA   | SPEN    | RX9     | SREN    | CREN    | ADDEN   | FERR   | OERR   | RX9D    | 134                 |

| SSPCON  | WCOL    | SSPOV   | SSPEN   | CKP     | SSPM3   | SSPM2  | SSPM1  | SSPM0   | 152                 |

| SSPSTAT | SMP     | CKE     | D/Ā     | Р       | S       | R/W    | UA     | BF      | 153                 |

| T1CON   | TMR1CS1 | TMR1CS0 | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | —      | TMR10N  | 103                 |

| TXSTA   | CSRC    | TX9     | TXEN    | SYNC    | —       | BRGH   | TRMT   | TX9D    | 133                 |

| TRISC   | TRISC7  | TRISC6  | TRISC5  | TRISC4  | TRISC3  | TRISC2 | TRISC1 | TRISC0  | 62                  |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTC.

# 7.4 Oscillator Control

The Oscillator Control (OSCCON) register (Figure 7-1) displays the status and allows frequency selection of the internal oscillator (INTOSC) system clock. The OSCCON register contains the following bits:

- Frequency selection bits (IRCF)

- Status Locked bits (ICSL)

- Status Stable bits (ICSS)

#### REGISTER 7-1: OSCCON: OSCILLATOR CONTROL REGISTER

| U-0     | U-0 | R/W-1 | R/W-0 | R-q  | R-q  | U-0 | U-0   |

|---------|-----|-------|-------|------|------|-----|-------|

|         | —   | IRCF1 | IRCF0 | ICSL | ICSS |     | _     |

| bit 7   |     |       |       |      |      |     | bit 0 |

|         |     |       |       |      |      |     |       |

| Legend: |     |       |       |      |      |     |       |

| R = Readable bit       | W = Writable bit | U = Unimplemented bit | , read as '0'      |  |

|------------------------|------------------|-----------------------|--------------------|--|

| -n = Value at POR      | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |  |

| q = Value depends on c | ondition         |                       |                    |  |

| bit 7-6 | Unimplemented: Read as '0'                                                               |

|---------|------------------------------------------------------------------------------------------|

| bit 5-4 | IRCF<1:0>: Internal Oscillator Frequency Select bits                                     |

|         | <u>When PLLEN = 1 (16 MHz INTOSC)</u>                                                    |

|         | 11 <b>= 16 MHz</b>                                                                       |

|         | 10 = 8 MHz (POR value)                                                                   |

|         | 01 = 4  MHz                                                                              |

|         | 00 = 2 MHz                                                                               |

|         | $\frac{\text{When PLLEN} = 0 (500 \text{ kHz INTOSC})}{11 - 500 \text{ kHz}}$            |

|         | 11 = 500 kHz                                                                             |

|         | 10 = 250 kHz (POR value)<br>01 = 125 kHz                                                 |

|         | 01 = 125  kHz<br>00 = 62.5  kHz                                                          |

| h it 0  |                                                                                          |

| bit 3   | ICSL: Internal Clock Oscillator Status Locked bit (2% Stable)                            |

|         | 1 = 16 MHz/500 kHz Internal Oscillator (HFIOSC) is in lock                               |

|         | 0 = 16 MHz/500 kHz Internal Oscillator (HFIOSC) has not yet locked                       |

| bit 2   | ICSS: Internal Clock Oscillator Status Stable bit (0.5% Stable)                          |

|         | 1 = 16 MHz/500 kHz Internal Oscillator (HFIOSC) has stabilized to its maximum accuracy   |

|         | 0 = 16 MHz/500 kHz Internal Oscillator (HFIOSC) has not yet reached its maximum accuracy |

| bit 1-0 | Unimplemented: Read as '0'                                                               |

|         |                                                                                          |

| U-0          | R/W-0         | R/W-0            | R/W-0           | U-0              | U-0             | R/W-0           | R/W-0  |

|--------------|---------------|------------------|-----------------|------------------|-----------------|-----------------|--------|

| _            | ADCS2         | ADCS1            | ADCS0           | _                | _               | ADREF1          | ADREF0 |

| bit 7        |               | ·                |                 |                  |                 |                 | bit C  |

|              |               |                  |                 |                  |                 |                 |        |

| Legend:      |               |                  |                 |                  |                 |                 |        |

| R = Readal   | ble bit       | W = Writable     | bit             | U = Unimpler     | mented bit, rea | d as '0'        |        |

| -n = Value a | at POR        | '1' = Bit is set |                 | '0' = Bit is cle | ared            | x = Bit is unkr | nown   |

|              |               |                  |                 |                  |                 |                 |        |

| bit 7        | Unimplemen    | ted: Read as '   | 0'              |                  |                 |                 |        |

| bit 6-4      | ADCS<2:0>:    | A/D Conversio    | n Clock Select  | t bits           |                 |                 |        |

|              | 000 = Fosc/2  | _                |                 |                  |                 |                 |        |

|              | 001 = Fosc/8  | -                |                 |                  |                 |                 |        |

|              | 010 = Fosc/3  |                  | rom a dadicata  | ed RC oscillator | r)              |                 |        |

|              | 100 = FRC (C) |                  |                 |                  | )               |                 |        |

|              | 101 = Fosc/1  | -                |                 |                  |                 |                 |        |

|              | 110 = Fosc/6  | 64               |                 |                  |                 |                 |        |

|              | 111 = FRC (C  | lock supplied f  | rom a dedicate  | ed RC oscillator | r)              |                 |        |

| bit 3-2      | Unimplemen    | ted: Read as '   | 0'              |                  |                 |                 |        |

| bit 1-0      | ADREF<1:0>    | : Voltage Refe   | rence Configui  | ration bits      |                 |                 |        |

|              | 0x = VREF is  | connected to \   | /DD             |                  |                 |                 |        |

|              |               | connected to e   |                 |                  |                 |                 |        |

|              | 11 = VREF is  | connected to i   | nternal Fixed V | /oltage Referer  | nce             |                 |        |

#### REGISTER 9-2: ADCON1: A/D CONTROL REGISTER 1

#### REGISTER 9-3: ADRES: ADC RESULT REGISTER

| R/W-x  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| ADRES7 | ADRES6 | ADRES5 | ADRES4 | ADRES3 | ADRES2 | ADRES1 | ADRES0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 7-0 **ADRES<7:0>**: ADC Result Register bits 8-bit conversion result.

|         |         | •••••  |        |             |             |        |             |        |                     |

|---------|---------|--------|--------|-------------|-------------|--------|-------------|--------|---------------------|

| Name    | Bit 7   | Bit 6  | Bit 5  | Bit 4       | Bit 3       | Bit 2  | Bit 1       | Bit 0  | Register<br>on Page |

| ADCON0  |         |        | CHS3   | CHS2        | CHS1        | CHS0   | GO/<br>DONE | ADON   | 85                  |

| ADCON1  | _       | ADCS2  | ADCS1  | ADCS0       | —           | —      | ADREF1      | ADREF0 | 86                  |

| ANSELA  |         |        | ANSA5  | ANSA4       | ANSA3       | ANSA2  | ANSA1       | ANSA0  | 44                  |

| ANSELB  | _       | —      | ANSB5  | ANSB4       | ANSB3       | ANSB2  | ANSB1       | ANSB0  | 53                  |

| ADRES   |         |        | A/[    | D Result Re | gister Byte |        |             |        | 86                  |

| CCP2CON | _       | _      | DC2B1  | DC2B0       | CCP2M3      | CCP2M2 | CCP2M1      | CCP2M0 | 115                 |

| FVRCON  | FVRRDY  | FVREN  | _      | —           | —           | —      | ADFVR1      | ADFVR0 | 90                  |

| INTCON  | GIE     | PEIE   | TOIE   | INTE        | RBIE        | T0IF   | INTF        | RBIF   | 36                  |

| PIE1    | TMR1GIE | ADIE   | RCIE   | TXIE        | SSPIE       | CCP1IE | TMR2IE      | TMR1IE | 37                  |

| PIR1    | TMR1GIF | ADIF   | RCIF   | TXIF        | SSPIF       | CCP1IF | TMR2IF      | TMR1IF | 39                  |

| TRISA   | TRISA7  | TRISA6 | TRISA5 | TRISA4      | TRISA3      | TRISA2 | TRISA1      | TRISA0 | 43                  |

| TRISB   | TRISB7  | TRISB6 | TRISB5 | TRISB4      | TRISB3      | TRISB2 | TRISB1      | TRISB0 | 52                  |

### TABLE 9-2: SUMMARY OF ASSOCIATED ADC REGISTERS

**Legend:** x = unknown, u = unchanged, - = unimplemented read as '0', <math>q = value depends on condition. Shaded cells are not used for ADC module.

PIC16(L)F722A/723A

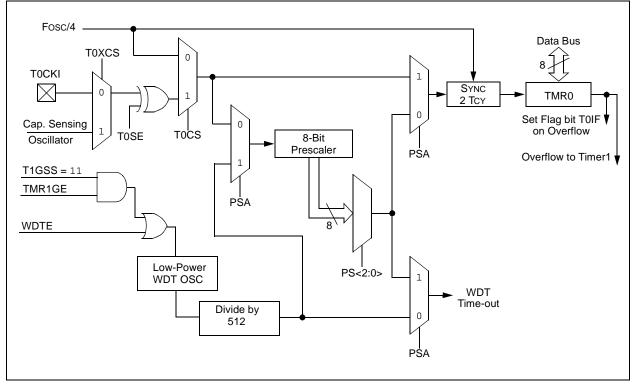

# 11.0 TIMER0 MODULE

The Timer0 module is an 8-bit timer/counter with the following features:

- 8-bit timer/counter register (TMR0)

- 8-bit prescaler (shared with Watchdog Timer)

- Programmable internal or external clock source

- · Programmable external clock edge selection

- Interrupt on overflow

- TMR0 can be used to gate Timer1

Figure 11-1 is a block diagram of the Timer0 module.

# 11.1 Timer0 Operation

The Timer0 module can be used as either an 8-bit timer or an 8-bit counter.

#### 11.1.1 8-BIT TIMER MODE

The Timer0 module will increment every instruction cycle, if used without a prescaler. 8-Bit Timer mode is selected by clearing the T0CS bit of the OPTION register.

When TMR0 is written, the increment is inhibited for two instruction cycles immediately following the write.

Note: The value written to the TMR0 register can be adjusted, in order to account for the two instruction cycle delay when TMR0 is written.

#### 11.1.2 8-BIT COUNTER MODE

In 8-Bit Counter mode, the Timer0 module will increment on every rising or falling edge of the T0CKI pin or the Capacitive Sensing Oscillator (CPSOSC) signal.

8-Bit Counter mode using the T0CKI pin is selected by setting the T0CS bit in the OPTION register to '1' and resetting the T0XCS bit in the CPSCON0 register to '0'.

8-Bit Counter Mode using the Capacitive Sensing Oscillator (CPSOSC) signal is selected by setting the TOCS bit in the OPTION register to '1' and setting the T0XCS bit in the CPSCON0 register to '1'.

The rising or falling transition of the incrementing edge for either input source is determined by the T0SE bit in the OPTION register.

#### FIGURE 11-1: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

# PIC16(L)F722A/723A

| FIGURE 12-6:   | TIMER1 GATE SINGLE-PU                  | ILSE MODE |                                                               |

|----------------|----------------------------------------|-----------|---------------------------------------------------------------|

|                |                                        |           |                                                               |

| TMR1GE         |                                        |           |                                                               |

| T1GPOL         |                                        |           |                                                               |

| T1GSPM         |                                        |           |                                                               |

| T1GGO/<br>DONE | Set by software<br>Counting enabled on |           | Cleared by hardware on<br>falling edge of T1GVAL              |

| T1G_IN         | rising edge of T1G                     |           |                                                               |

| T1CKI          |                                        |           |                                                               |

| T1GVAL         |                                        |           |                                                               |

| TIMER1         | N                                      | N + 1     | N + 2                                                         |

| TMR1GIF        | — Cleared by software                  |           | <ul> <li>Set by hardware on falling edge of T1GVAL</li> </ul> |

# 16.3 AUSART Synchronous Mode

Synchronous serial communications are typically used in systems with a single master and one or more slaves. The master device contains the necessary circuitry for baud rate generation and supplies the clock for all devices in the system. Slave devices can take advantage of the master clock by eliminating the internal clock generation circuitry.

There are two signal lines in Synchronous mode: a bidirectional data line and a clock line. Slaves use the external clock supplied by the master to shift the serial data into and out of their respective receive and transmit shift registers. Since the data line is bidirectional, synchronous operation is half-duplex only. Half-duplex refers to the fact that master and slave devices can receive and transmit data but not both simultaneously. The AUSART can operate as either a master or slave device.

Start and Stop bits are not used in synchronous transmissions.

#### 16.3.1 SYNCHRONOUS MASTER MODE

The following bits are used to configure the AUSART for Synchronous Master operation:

- SYNC = 1

- CSRC = 1

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TXSTA register configures the device for synchronous operation. Setting the CSRC bit of the TXSTA register configures the device as a master. Clearing the SREN and CREN bits of the RCSTA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RCSTA register enables the AUSART.

#### 16.3.1.1 Master Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a master transmits the clock on the TX/ CK line. The TX/CK pin output driver is automatically enabled when the AUSART is configured for synchronous transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One clock cycle is generated for each data bit. Only as many clock cycles are generated as there are data bits.

#### 16.3.1.2 Synchronous Master Transmission

Data is transferred out of the device on the RX/DT pin. The RX/DT and TX/CK pin output drivers are automatically enabled when the AUSART is configured for synchronous master transmit operation.

A transmission is initiated by writing a character to the TXREG register. If the TSR still contains all or part of a previous character, the new character data is held in the TXREG until the last bit of the previous character has been transmitted. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TXREG is immediately transferred to the TSR. The transmission of the character commences immediately following the transfer of the data to the TSR from the TXREG.

Each data bit changes on the leading edge of the master clock and remains valid until the subsequent leading clock edge.

Note: The TSR register is not mapped in data memory, so it is not available to the user.

16.3.1.3 Synchronous Master Transmission Setup:

- Initialize the SPBRG register and the BRGH bit to achieve the desired baud rate (refer to Section 16.2 "AUSART Baud Rate Generator (BRG)").

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Disable Receive mode by clearing bits SREN and CREN.

- 4. Enable Transmit mode by setting the TXEN bit.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. If interrupts are desired, set the TXIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded in the TX9D bit.

- 8. Start transmission by loading data to the TXREG register.

#### 17.1.2 SLAVE MODE

For any SPI device acting as a slave, the data is transmitted and received as external clock pulses appear on SCK pin. This external clock must meet the minimum high and low times as specified in the electrical specifications.

#### 17.1.2.1 Slave Mode Operation

The SSP consists of a transmit/receive shift register (SSPSR) and a buffer register (SSPBUF). The SSPSR shifts the data in and out of the device, MSb first. The SSPBUF holds the data that was written to the SSPSR until the received data is ready.

The slave has no control as to when data will be clocked in or out of the device. All data that is to be transmitted, to a master or another slave, must be loaded into the SSPBUF register before the first clock pulse is received.

Once eight bits of data have been received:

- · Received byte is moved to the SSPBUF register

- BF bit of the SSPSTAT register is set

- SSPIF bit of the PIR1 register is set

Any write to the SSPBUF register during transmission/ reception of data will be ignored and the Write Collision Detect bit, WCOL of the SSPCON register, will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPBUF register completed successfully.

The user's firmware must read SSPBUF, clearing the BF flag, or the SSPOV bit of the SSPCON register will be set with the reception of the next byte and communication will be disabled.

A SPI module transmits and receives at the same time, occasionally causing dummy data to be transmitted/ received. It is up to the user to determine which data is to be used and what can be discarded.

#### 17.1.2.2 Enabling Slave I/O

To enable the serial port, the SSPEN bit of the SSPCON register must be set. If a Slave mode of operation is selected in the SSPM bits of the SSPCON register, the SDI, SDO and SCK pins will be assigned as serial port pins.

For these pins to function as serial port pins, they must have their corresponding data direction bits set or cleared in the associated TRIS register as follows:

- · SDI configured as input

- · SDO configured as output

- · SCK configured as input

Optionally, a fourth pin, Slave Select  $(\overline{SS})$  may be used in Slave mode. Slave Select may be configured to operate on one of the following pins via the SSSEL bit in the APFCON register.

- RA5/AN4/SS

- RA0/AN0/SS

Upon selection of a Slave Select pin, the appropriate bits must be set in the ANSELA and TRISA registers. Slave Select must be set as an input by setting the corresponding bit in TRISA, and digital I/O must be enabled on the SS pin by clearing the corresponding bit of the ANSELA register.

#### 17.1.2.3 Slave Mode Setup

When initializing the SSP module to SPI Slave mode, compatibility must be ensured with the master device. This is done by programming the appropriate control bits of the SSPCON and SSPSTAT registers. These control bits allow the following to be specified:

- · SCK as clock input

- Idle state of SCK (CKP bit)

- Data input sample phase (SMP bit)

- Output data on rising/falling edge of SCK (CKE bit)

Figure 17-4 and Figure 17-5 show example waveforms of Slave mode operation.

#### REGISTER 18-1: PMCON1: PROGRAM MEMORY CONTROL 1 REGISTER

| R-1      | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/S-0 |

|----------|-----|-----|-----|-----|-----|-----|-------|

| Reserved | —   | —I  | —   | —   | —   | —   | RD    |

| bit 7    |     |     |     |     |     |     | bit 0 |

|          |     |     |     |     |     |     |       |

| Legend:           |                  | S = Setable bit, cleared in ha | ardware            |

|-------------------|------------------|--------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read    | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared           | x = Bit is unknown |

| bit 7 <b>Reserved:</b> Read as '1'. Maintain this bit set. |

|------------------------------------------------------------|

| bit 7 <b>Reserved:</b> Read as '1'. Maintain this bit set. |

bit 6-1 Unimplemented: Read as '0'

bit 0 RD: Read Control bit

1 = Initiates an program memory read (The RD is cleared in hardware; the RD bit can only be set (not cleared) in software).

0 = Does not initiate a program memory read

#### REGISTER 18-2: PMDATH: PROGRAM MEMORY DATA HIGH REGISTER

| U-0      | U-0 | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|----------|-----|-------|-------|-------|-------|-------|-------|

|          | —   | PMD13 | PMD12 | PMD11 | PMD10 | PMD9  | PMD8  |

| bit 7    |     |       |       |       |       |       | bit 0 |

|          |     |       |       |       |       |       |       |

| l egend: |     |       |       |       |       |       |       |

| Legenu.                           |                  |                                    |                    |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **PMD<13:8>:** The value of the program memory word pointed to by PMADRH and PMADRL after a Program Memory Read command.

#### REGISTER 18-3: PMDATL: PROGRAM MEMORY DATA LOW REGISTER

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| PMD7  | PMD6  | PMD5  | PMD4  | PMD3  | PMD2  | PMD1  | PMD0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-0 **PMD<7:0>:** The value of the program memory word pointed to by PMADRH and PMADRL after a Program Memory Read command.

# 19.2 Wake-up Using Interrupts

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs before the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT prescaler and postscaler (if enabled) will not be cleared, the TO bit will not be set and the PD bit will not be cleared.

- If the interrupt occurs **during or after** the execution of a SLEEP instruction, the device will immediately wake-up from Sleep. The SLEEP instruction will be completely executed before the wake-up. Therefore, the WDT and WDT prescaler and postscaler (if enabled) will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction.

# FIGURE 19-1: WAKE-UP FROM SLEEP THROUGH INTERRUPT

| ; Q1  Q2  Q3   Q4; Q1  Q2 Q3  <br>OSC1 <sup>(1)</sup> /~~~/~/~/~/_/ |              | Q1  Q2  Q3   Q4         | Q1 Q2 Q3 Q4;     | Q1 Q2 Q3 Q4; | Q1 Q2 Q3 Q4; |

|---------------------------------------------------------------------|--------------|-------------------------|------------------|--------------|--------------|

| CLKOUT(4)                                                           |              | /\_                     | /                |              |              |

| INT pin                                                             |              |                         |                  |              | <u>'</u>     |

| INTF flag<br>(INTCON reg.)                                          |              | Interrupt Latency       | y <sup>(3)</sup> |              |              |

| GIE bit<br>(INTCON reg.)                                            | Processor in | · · · · · · · · · · · · |                  |              | ;<br>;_      |

| Instruction Flow<br>PC X PC X PC + 1                                | X PC + 2     | X PC + 2 X              | PC + 2           | 0004h        | 0005h        |

| Instruction { Inst(PC) = Sleep Inst(PC + 1                          | 1)           | Inst(PC + 2)            | 1                | Inst(0004h)  | Inst(0005h)  |

| Instruction { Inst(PC - 1) Sleep                                    |              | Inst(PC + 1)            | Dummy Cycle      | Dummy Cycle  | Inst(0004h)  |

|                                                                     |              |                         |                  |              |              |

Note 1: XT, HS or LP Oscillator mode assumed.

2: TOST = 1024 TOSC (drawing not to scale). This delay does not apply to EC and RC Oscillator modes.

3: GIE = 1 assumed. In this case after wake-up, the processor jumps to 0004h. If GIE = 0, execution will continue in-line.

4: CLKOUT is not available in XT, HS, LP or EC Oscillator modes, but shown here for timing reference.

| Name   | Bit 7   | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Register on<br>Page |

|--------|---------|-------|-------|-------|-------|--------|--------|--------|---------------------|

| IOCB   | IOCB7   | IOCB6 | IOCB5 | IOCB4 | IOCB3 | IOCB2  | IOCB1  | IOCB0  | 53                  |

| INTCON | GIE     | PEIE  | TOIE  | INTE  | RBIE  | T0IF   | INTF   | RBIF   | 36                  |

| PIE1   | TMR1GIE | ADIE  | RCIE  | TXIE  | SSPIE | CCP1IE | TMR2IE | TMR1IE | 37                  |

| PIE2   | —       | —     | —     | —     | —     | _      | —      | CCP2IE | 38                  |

| PIR1   | TMR1GIF | ADIF  | RCIF  | TXIF  | SSPIF | CCP1IF | TMR2IF | TMR1IF | 39                  |

| PIR2   | —       | —     | —     | —     | —     | _      | —      | CCP2IF | 40                  |

#### TABLE 19-1: SUMMARY OF REGISTERS ASSOCIATED WITH POWER-DOWN MODE

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used in Power-Down mode.

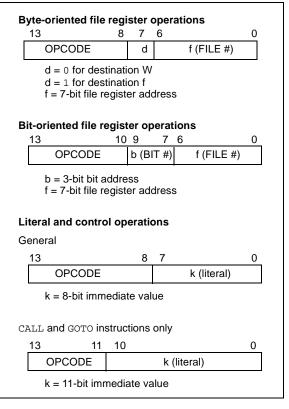

# 21.0 INSTRUCTION SET SUMMARY

The PIC16(L)F722A/723A instruction set is highly orthogonal and is comprised of three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

Each PIC16 instruction is a 14-bit word divided into an **opcode**, which specifies the instruction type and one or more **operands**, which further specify the operation of the instruction. The formats for each of the categories is presented in Figure 21-1, while the various opcode fields are summarized in Table 21-1.

Table 21-2 lists the instructions recognized by the MPASM<sup>TM</sup> assembler.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator, which selects the bit affected by the operation, while 'f' represents the address of the file in which the bit is located.

For **literal and control** operations, 'k' represents an 8bit or 11-bit constant, or literal value.

One instruction cycle consists of four oscillator periods; for an oscillator frequency of 4 MHz, this gives a nominal instruction execution time of 1  $\mu$ s. All instructions are executed within a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of an instruction. When this occurs, the execution takes two instruction cycles, with the second cycle executed as a NOP.

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

# 21.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

For example, a CLRF PORTB instruction will read PORTB, clear all the data bits, then write the result back to PORTB. This example would have the unintended consequence of clearing the condition that set the RBIF flag.

#### TABLE 21-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                     |  |  |  |  |  |  |  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                            |  |  |  |  |  |  |  |

| W     | Working register (accumulator)                                                                                                                                                  |  |  |  |  |  |  |  |

| b     | Bit address within an 8-bit file register                                                                                                                                       |  |  |  |  |  |  |  |

| k     | Literal field, constant data or label                                                                                                                                           |  |  |  |  |  |  |  |

| x     | Don't care location (= 0 or 1).<br>The assembler will generate code with $x = 0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |  |  |  |  |  |  |  |

| d     | Destination select; $d = 0$ : store result in W,<br>d = 1: store result in file register f.<br>Default is $d = 1$ .                                                             |  |  |  |  |  |  |  |

| PC    | Program Counter                                                                                                                                                                 |  |  |  |  |  |  |  |

| TO    | Time-out bit                                                                                                                                                                    |  |  |  |  |  |  |  |

| С     | Carry bit                                                                                                                                                                       |  |  |  |  |  |  |  |

| DC    | Digit carry bit                                                                                                                                                                 |  |  |  |  |  |  |  |

| Z     | Zero bit                                                                                                                                                                        |  |  |  |  |  |  |  |

| PD    | Power-down bit                                                                                                                                                                  |  |  |  |  |  |  |  |

#### FIGURE 21-1: GENERAL FORMAT FOR INSTRUCTIONS

© 2010-2016 Microchip Technology Inc.

# 22.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

### 22.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

# 22.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

# 22.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

#### 22.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

# TABLE 23-4:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER,<br/>AND BROWN-OUT RESET PARAMETERS

| Standard Operating Conditions (unless otherwise stated)<br>Operating Temperature -40°C $\leq$ TA $\leq$ +125°C |        |                                                             |              |            |              |          |                                                |  |

|----------------------------------------------------------------------------------------------------------------|--------|-------------------------------------------------------------|--------------|------------|--------------|----------|------------------------------------------------|--|

| Param<br>No.                                                                                                   | Sym.   | Characteristic                                              | Min.         | Тур†       | Max.         | Units    | Conditions                                     |  |

| 30                                                                                                             | ТмсL   | MCLR Pulse Width (low)                                      | 2<br>5       | _          |              | μS<br>μS | VDD = 3.3-5V, -40°C to +85°C<br>VDD = 3.3-5V   |  |

| 31                                                                                                             | TWDTLP | Low Power Watchdog Timer Time-<br>out Period (No Prescaler) | 10           | 18         | 27           | ms       | Vdd = 3.3V-5V                                  |  |

| 32                                                                                                             | Tost   | Oscillator Start-up Timer Period <sup>(1), (2)</sup>        | _            | 1024       | _            | Tosc     | (Note 3)                                       |  |

| 33*                                                                                                            | TPWRT  | Power-up Timer Period, $\overline{PWRTE} = 0$               | 40           | 65         | 140          | ms       |                                                |  |

| 34*                                                                                                            | Tioz   | I/O high-impedance from MCLR Low or Watchdog Timer Reset    | _            | —          | 2.0          | μS       |                                                |  |

| 35                                                                                                             | VBOR   | Brown-out Reset Voltage                                     | 2.38<br>1.80 | 2.5<br>1.9 | 2.73<br>2.11 | V        | BORV=2.5V<br>BORV=1.9V                         |  |

| 36*                                                                                                            | VHYST  | Brown-out Reset Hysteresis                                  | 0            | 25         | 50           | mV       | -40°C to +85°C                                 |  |

| 37*                                                                                                            | TBORDC | Brown-out Reset DC Response<br>Time                         | 1            | 3          | 5<br>10      | μS       | $VDD \le VBOR$ , -40°C to +85°C $VDD \le VBOR$ |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- **Note 1:** Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to the OSC1 pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

- 2: By design.

- **3:** Period of the slower clock.

- 4: To ensure these voltage tolerances, VDD and VSS must be capacitively decoupled as close to the device as possible. 0.1  $\mu$ F and 0.01  $\mu$ F values in parallel are recommended.

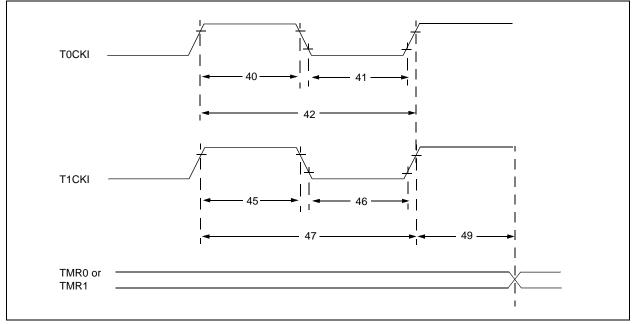

#### FIGURE 23-10: TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

# 24.0 DC AND AC CHARACTERISTICS GRAPHS AND CHARTS

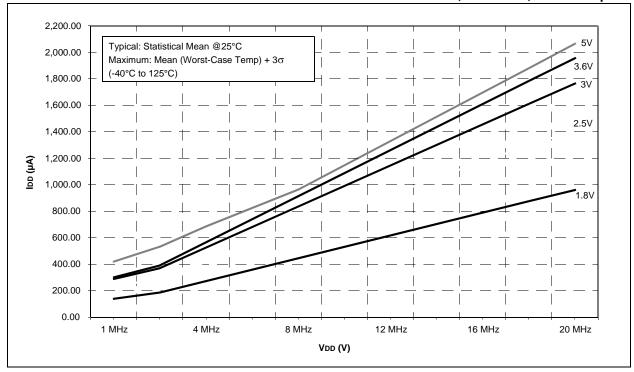

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25 °C. "Maximum" or "minimum" represents (mean + 3 $\sigma$ ) or (mean - 3 $\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over the whole temperature range.

#### FIGURE 24-1: PIC16F722A/723A MAXIMUM IDD vs. Fosc OVER VDD, EC MODE, VCAP = 0.1µF