Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 7KB (4K x 14)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 192 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 11x8b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 28-UQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf723a-i-mv |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

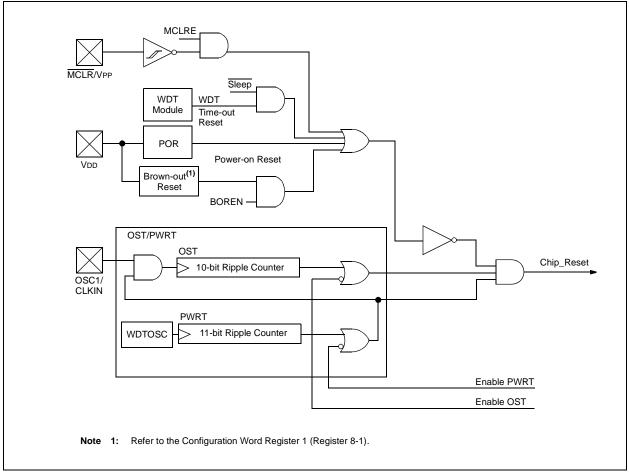

## 3.0 RESETS

The PIC16(L)F722A/723A differentiates between various kinds of Reset:

- a) Power-on Reset (POR)

- b) WDT Reset during normal operation

- c) WDT Reset during Sleep

- d) MCLR Reset during normal operation

- e) MCLR Reset during Sleep

- f) Brown-out Reset (BOR)

Some registers are not affected in any Reset condition; their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on:

- Power-on Reset (POR)

- MCLR Reset

- MCLR Reset during Sleep

- WDT Reset

- Brown-out Reset (BOR)

Most registers are not affected by a WDT wake-up since this is viewed as the resumption of normal operation. TO and PD bits are set or cleared differently in different Reset situations, as indicated in Table 3-3. These bits are used in software to determine the nature of the Reset.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 3-1.

The MCLR Reset path has a noise filter to detect and ignore small pulses. See **Section 23.0** "**Electrical Specifications**" for pulse width specifications.

### FIGURE 3-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

### 3.6 Time-out Sequence

On power-up, the time-out sequence is as follows: first, PWRT time out is invoked after POR has expired, then OST is activated after the PWRT time out has expired. The total time out will vary based on oscillator configuration and  $\overrightarrow{PWRTE}$  bit status. For example, in EC mode with  $\overrightarrow{PWRTE}$  bit = 1 ( $\overrightarrow{PWRT}$  disabled), there will be no time-out at all. Figure 3-4, Figure 3-5 and Figure 3-6 depict time-out sequences.

Since the time outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then, bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (see Figure 3-5). This is useful for testing purposes or to synchronize more than one PIC16(L)F722A/723A device operating in parallel.

Table 3-3 shows the Reset conditions for some special registers.

### 3.7 Power Control (PCON) Register

The Power Control (PCON) register has two Status bits to indicate what type of Reset that last occurred.

Bit 0 is  $\overrightarrow{BOR}$  (Brown-out Reset).  $\overrightarrow{BOR}$  is unknown on Power-on Reset. It must then be set by the user and checked on subsequent Resets to see if  $\overrightarrow{BOR} = 0$ , indicating that a brown-out has occurred. The  $\overrightarrow{BOR}$ Status bit is a "don't care" and is not necessarily predictable if the brown-out circuit is disabled (BOREN<1:0> = 00 in the Configuration Word register).

Bit 1 is POR (Power-on Reset). It is a '0' on Power-on Reset and unaffected otherwise. The user must write a '1' to this bit following a Power-on Reset. On a subsequent Reset, if POR is '0', it will indicate that a Power-on Reset has occurred (i.e., VDD may have gone too low).

For more information, see Section 3.5 "Brown-Out Reset (BOR)".

| Oscillator Configuration  | Powe                   | er-up       | Brown-o                | Wake-up from     |             |

|---------------------------|------------------------|-------------|------------------------|------------------|-------------|

| Oscillator Configuration  | <b>PWRTE</b> = 0       | PWRTE = 1   | <b>PWRTE</b> = 0       | <b>PWRTE</b> = 1 | Sleep       |

| XT, HS, LP <sup>(1)</sup> | TPWRT + 1024 •<br>Tosc | 1024 • Tosc | TPWRT + 1024 •<br>Tosc | 1024 • Tosc      | 1024 • Tosc |

| RC, EC, INTOSC            | TPWRT                  |             | TPWRT                  | _                | —           |

### TABLE 3-2: TIME OUT IN VARIOUS SITUATIONS

Note 1: LP mode with T1OSC disabled.

### TABLE 3-3: RESET BITS AND THEIR SIGNIFICANCE

| POR | BOR | то | PD | Condition                          |

|-----|-----|----|----|------------------------------------|

| 0   | u   | 1  | 1  | Power-on Reset                     |

| 1   | 0   | 1  | 1  | Brown-out Reset                    |

| u   | u   | 0  | u  | WDT Reset                          |

| u   | u   | 0  | 0  | WDT Wake-up                        |

| u   | u   | u  | u  | MCLR Reset during normal operation |

| u   | u   | 1  | 0  | MCLR Reset during Sleep            |

**Legend:** u = unchanged, x = unknown

| IADLE 5-4. | INITIALIZATION CONDITION FOR REGISTERS (CONTINUED) |                                                   |                          |                                                  |  |  |  |  |  |  |

|------------|----------------------------------------------------|---------------------------------------------------|--------------------------|--------------------------------------------------|--|--|--|--|--|--|

| Register   | Address                                            | Power-on Reset/<br>Brown-out Reset <sup>(1)</sup> | MCLR Reset/<br>WDT Reset | Wake-up from Sleep through<br>Interrupt/Time out |  |  |  |  |  |  |

| PIE1       | 8Ch                                                | 0000 0000                                         | 0000 0000                | սսսս սսսս                                        |  |  |  |  |  |  |

| PIE2       | 8Dh                                                | 0                                                 | 0                        | u                                                |  |  |  |  |  |  |

| PCON       | 8Eh                                                | dd                                                | uu <sup>(1,5)</sup>      | uu                                               |  |  |  |  |  |  |

| T1GCON     | 8Fh                                                | 0000 0x00                                         | uuuu uxuu                | uuuu uxuu                                        |  |  |  |  |  |  |

| OSCCON     | 90h                                                | 10 qq                                             | 10 qq                    | uu qq                                            |  |  |  |  |  |  |

| OSCTUNE    | 91h                                                | 00 0000                                           | uu uuuu                  | uu uuuu                                          |  |  |  |  |  |  |

| PR2        | 92h                                                | 1111 1111                                         | 1111 1111                | uuuu uuuu                                        |  |  |  |  |  |  |

| SSPADD     | 93h                                                | 0000 0000                                         | 0000 0000                | uuuu uuuu                                        |  |  |  |  |  |  |

| SSPMSK     | 93h                                                | 1111 1111                                         | 1111 1111                | uuuu uuuu                                        |  |  |  |  |  |  |

| SSPSTAT    | 94h                                                | 0000 0000                                         | 0000 0000                | uuuu uuuu                                        |  |  |  |  |  |  |

| WPUB       | 95h                                                | 1111 1111                                         | 1111 1111                | uuuu uuuu                                        |  |  |  |  |  |  |

| IOCB       | 96h                                                | 0000 0000                                         | 0000 0000                | uuuu uuuu                                        |  |  |  |  |  |  |

| TXSTA      | 98h                                                | 0000 -010                                         | 0000 -010                | uuuu -uuu                                        |  |  |  |  |  |  |

| SPBRG      | 99h                                                | 0000 0000                                         | 0000 0000                | uuuu uuuu                                        |  |  |  |  |  |  |

| APFCON     | 9Ch                                                | 00                                                | 00                       |                                                  |  |  |  |  |  |  |

| FVRCON     | 9Dh                                                | d00000                                            | d00000                   | uuuuuu                                           |  |  |  |  |  |  |

| ADCON1     | 9Fh                                                | -00000                                            | -00000                   | -uuuuu                                           |  |  |  |  |  |  |

| CPSCON0    | 108h                                               | 0 0000                                            | 0 0000                   | u uuuu                                           |  |  |  |  |  |  |

| CPSCON1    | 109h                                               | 0000                                              | 0000                     | uuuu                                             |  |  |  |  |  |  |

| PMDATL     | 10Ch                                               | xxxx xxxx                                         | XXXX XXXX                | uuuu uuuu                                        |  |  |  |  |  |  |

| PMADRL     | 10Dh                                               | xxxx xxxx                                         | XXXX XXXX                | սսսս սսսս                                        |  |  |  |  |  |  |

| PMDATH     | 10Eh                                               | xx xxxx                                           | xx xxxx                  | uu uuuu                                          |  |  |  |  |  |  |

| PMADRH     | 10Fh                                               | x xxxx                                            | x xxxx                   | u uuuu                                           |  |  |  |  |  |  |

| ANSELA     | 185h                                               | 11 1111                                           | 11 1111                  | uu uuuu                                          |  |  |  |  |  |  |

| ANSELB     | 186h                                               | 11 1111                                           | 11 1111                  | uu uuuu                                          |  |  |  |  |  |  |

| PMCON1     | 18Ch                                               | 10                                                | 10                       | uu                                               |  |  |  |  |  |  |

| TABLE 3-4: | INITIALIZATION CONDITION FOR REGISTERS ( | CONTINUED) |  |

|------------|------------------------------------------|------------|--|

| IADLL J-4. | INTIALIZATION CONDITION FOR REGISTERS (  | CONTINUED) |  |

$\label{eq:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:logend:loge$

**Note 1:** If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2: One or more bits in INTCON and/or PIR1 and PIR2 will be affected (to cause wake-up).

3: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

4: See Table 3-5 for Reset value for specific condition.

5: If Reset was due to brown-out, then bit 0 = 0. All other Resets will cause bit 0 = u.

### 6.4 PORTC and TRISC Registers

PORTC is a 8-bit wide, bidirectional port. The corresponding data direction register is TRISC (Register 6-11). Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 6-3 shows how to initialize PORTC.

Reading the PORTC register (Register 6-10) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch.

The TRISC register (Register 6-11) controls the PORTC pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISC register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

### EXAMPLE 6-3: INITIALIZING PORTC

| BANKSEL PORTC  | ;                          |

|----------------|----------------------------|

| CLRF PORTC     | ;Init PORTC                |

| BANKSEL TRISC  | i                          |

| MOVLW B'000011 | 00' ;Set RC<3:2> as inputs |

| MOVWF TRISC    | ;and set RC<7:4,1:0>       |

|                | ;as outputs                |

|                |                            |

The location of the CCP2 function is controlled by the CCP2SEL bit in the APFCON register (refer to Register 6-1).

### REGISTER 6-10: PORTC: PORTC REGISTER

| R/W-x | R/W-x | R/W-x              | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|-------|-------|--------------------|-------|-------|-------|-------|-------|

| RC7   | RC6   | C6 RC5 RC4 RC3 RC2 |       | RC1   | RC0   |       |       |

| bit 7 |       |                    |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 RC<7:0>: PORTC General Purpose I/O Pin bits

1 = Port pin is > VIH 0 = Port pin is < VIL

### REGISTER 6-11: TRISC: PORTC TRI-STATE REGISTER

| R/W-1  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| TRISC7 | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-0 TRISC<7:0>: PORTC Tri-State Control bits

1 = PORTC pin configured as an input (tri-stated)

0 = PORTC pin configured as an output

### 14.5 Software Control

The software portion of the capacitive sensing module is required to determine the change in frequency of the capacitive sensing oscillator. This is accomplished by the following:

- Setting a fixed-time base to acquire counts on Timer0 or Timer1

- Establishing the nominal frequency for the capacitive sensing oscillator

- Establishing the reduced frequency for the capacitive sensing oscillator due to an additional capacitive load

- Set the frequency threshold

### 14.5.1 NOMINAL FREQUENCY (NO CAPACITIVE LOAD)

To determine the nominal frequency of the capacitive sensing oscillator:

- Remove any extra capacitive load on the selected CPSx pin

- At the start of the fixed-time base, clear the timer resource

- At the end of the fixed-time base, save the value in the timer resource

The value of the timer resource is the number of oscillations of the capacitive sensing oscillator for the given time base. The frequency of the capacitive sensing oscillator is equal to the number of counts on in the timer divided by the period of the fixed-time base.

### 14.5.2 REDUCED FREQUENCY (ADDITIONAL CAPACITIVE LOAD)

The extra capacitive load will cause the frequency of the capacitive sensing oscillator to decrease. To determine the reduced frequency of the capacitive sensing oscillator:

- Add a typical capacitive load on the selected CPSx pin

- Use the same fixed-time base as the nominal frequency measurement

- At the start of the fixed-time base, clear the timer resource

- At the end of the fixed-time base, save the value in the timer resource

The value of the timer resource is the number of oscillations of the capacitive sensing oscillator with an additional capacitive load. The frequency of the capacitive sensing oscillator is equal to the number of counts on in the timer divided by the period of the fixedtime base. This frequency should be less than the value obtained during the nominal frequency measurement.

### 14.5.3 FREQUENCY THRESHOLD

The frequency threshold should be placed midway between the value of nominal frequency and the reduced frequency of the capacitive sensing oscillator. Refer to Application Note *AN1103, Software Handling for Capacitive Sensing* (DS01103) for more detailed information the software required for capacitive sensing module.

**Note:** For more information on general capacitive sensing refer to Application Notes:

- •AN1101, Introduction to Capacitive Sensing (DS01101)

- •AN1102, Layout and Physical Design Guidelines for Capacitive Sensing (DS01102)

### 14.6 Operation During Sleep

The capacitive sensing oscillator will continue to run as long as the module is enabled, independent of the part being in Sleep. In order for the software to determine if a frequency change has occurred, the part must be awake. However, the part does not have to be awake when the timer resource is acquiring counts. One way to acquire the Timer1 counts while in Sleep is to have Timer1 gated with the overflow of the Watchdog Timer. This can be accomplished using the following steps:

- 1. Configure the Watchdog Time-out overflow as the Timer1's gate source T1GSS<1:0> = 11.

- 2. Set Timer1 gate to toggle mode by setting the T1GTM bit of the T1GCON register.

- 3. Set the TMR1GE bit of the T1GCON register.

- 4. Set TMR1ON bit of the T1CON register.

- 5. Enable capacitive sensing module with the appropriate current settings and pin selection.

- 6. Clear Timer1.

- 7. Put the part to Sleep.

- 8. On the first WDT overflow, the capacitive sensing oscillator will begin to increment Timer1. Then put the part to Sleep.

- 9. On the second WDT overflow Timer1 will stop incrementing. Then run the software routine to determine if a frequency change has occurred.

Refer to Section 12.0 "Timer1 Module with Gate Control" for additional information.

- Note 1: When using the WDT to set the interval on Timer1, any other source that wakes the part up early will cause the WDT overflow to be delayed, affecting the value captured by Timer1.

- 2: Timer0 does not operate when in Sleep, and therefore cannot be used for capacitive sense measurements in Sleep.

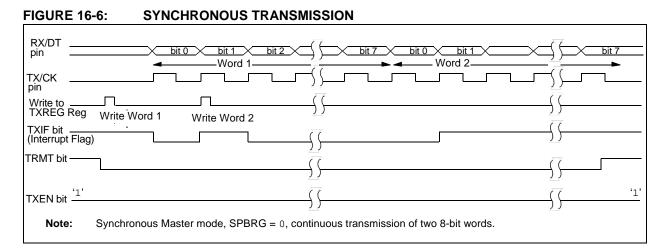

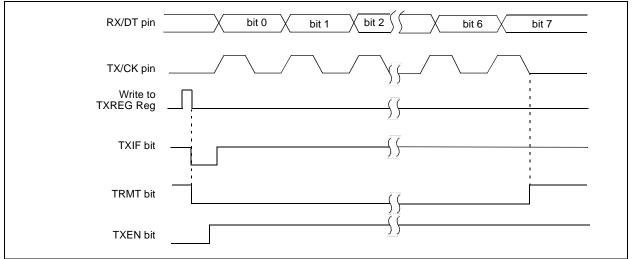

### FIGURE 16-7: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

### TABLE 16-6: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Name   | Bit 7                             | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-----------------------------------|--------|--------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE                               | PEIE   | TOIE   | INTE   | RBIE   | T0IF   | INTF   | RBIF   | 0000 000x            | 0000 000x                       |

| PIE1   | TMR1GIE                           | ADIE   | RCIE   | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| PIR1   | TMR1GIF                           | ADIF   | RCIF   | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| RCSTA  | SPEN                              | RX9    | SREN   | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 0000 000x            | 0000 000x                       |

| SPBRG  | BRG7                              | BRG6   | BRG5   | BRG4   | BRG3   | BRG2   | BRG1   | BRG0   | 0000 0000            | 0000 0000                       |

| TRISC  | TRISC7                            | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 1111 1111            | 1111 1111                       |

| TXREG  | REG AUSART Transmit Data Register |        |        |        |        |        |        |        | 0000 0000            | 0000 0000                       |

| TXSTA  | CSRC                              | TX9    | TXEN   | SYNC   | _      | BRGH   | TRMT   | TX9D   | 0000 -010            | 0000 -010                       |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for synchronous master transmission.

### 16.3.1.4 Synchronous Master Reception

Data is received at the RX/DT pin. The RX/DT pin output driver is automatically disabled when the AUSART is configured for synchronous master receive operation.

In Synchronous mode, reception is enabled by setting either the Single Receive Enable bit (SREN of the RCSTA register) or the Continuous Receive Enable bit (CREN of the RCSTA register).

When SREN is set and CREN is clear, only as many clock cycles are generated as there are data bits in a single character. The SREN bit is automatically cleared at the completion of one character. When CREN is set, clocks are continuously generated until CREN is cleared. If CREN is cleared in the middle of a character the CK clock stops immediately and the partial character is discarded. If SREN and CREN are both set, then SREN is cleared at the completion of the first character and CREN takes precedence.

To initiate reception, set either SREN or CREN. Data is sampled at the RX/DT pin on the trailing edge of the TX/CK clock pin and is shifted into the Receive Shift Register (RSR). When a complete character is received into the RSR, the RCIF bit of the PIR1 register is set and the character is automatically transferred to the two character receive FIFO. The Least Significant eight bits of the top character in the receive FIFO are available in RCREG. The RCIF bit remains set as long as there are un-read characters in the receive FIFO.

### 16.3.1.5 Slave Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a slave receives the clock on the TX/CK line. The TX/ CK pin output driver is automatically disabled when the device is configured for synchronous slave transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One data bit is transferred for each clock cycle. Only as many clock cycles should be received as there are data bits.

### 16.3.1.6 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before RCREG is read to access the FIFO. When this happens the OERR bit of the RCSTA register is set. Previous data in the FIFO will not be overwritten. The two characters in the FIFO buffer can be read, however, no additional characters will be received until the error is cleared. The OERR bit can only be cleared by clearing the overrun condition. If the overrun error occurred when the SREN bit is set and CREN is clear then the error is cleared by reading RCREG. If the overrun occurred when the CREN bit is set then the error condition is cleared by either clearing the CREN bit of the RCSTA register.

### 16.3.1.7 Receiving 9-bit Characters

The AUSART supports 9-bit character reception. When the RX9 bit of the RCSTA register is set, the AUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RCSTA register is the ninth, and Most Significant, data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RCREG.

Address detection in Synchronous modes is not supported, therefore the ADDEN bit of the RCSTA register must be cleared.

# 16.3.1.8 Synchronous Master Reception Setup:

- 1. Initialize the SPBRG register for the appropriate baud rate. Set or clear the BRGH bit, as required, to achieve the desired baud rate.

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Ensure bits CREN and SREN are clear.

- 4. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit reception is desired, set bit RX9.

- 6. Verify address detection is disabled by clearing the ADDEN bit of the RCSTA register.

- 7. Start reception by setting the SREN bit or for continuous reception, set the CREN bit.

- Interrupt flag bit RCIF of the PIR1 register will be set when reception of a character is complete. An interrupt will be generated if the RCIE interrupt enable bit of the PIE1 register was set.

- 9. Read the RCSTA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 10. Read the 8-bit received data by reading the RCREG register.

- 11. If an overrun error occurs, clear the error by either clearing the CREN bit of the RCSTA register or by clearing the SPEN bit, which resets the AUSART.

| FIGURE 16-8:            | SYNCHRONOUS RECEPTION (MASTER MODE, SREN)                                          |     |

|-------------------------|------------------------------------------------------------------------------------|-----|

| RX/DT<br>pin            | bit 0 bit 1 bit 2 bit 3 bit 4 bit 5 bit 6 bit 7                                    |     |

| TX/CK pin               |                                                                                    |     |

| Write to<br>bit SREN    |                                                                                    |     |

| SREN bit                | l                                                                                  |     |

| CREN bit <u>'</u> 0'    |                                                                                    | ʻ0' |

| RCIF bit<br>(Interrupt) |                                                                                    |     |

| Read<br>RCREG           |                                                                                    |     |

| Note: Timing d          | iagram demonstrates Synchronous Master mode with bit SREN = 1 and bit BRGH = $0$ . |     |

| Name   | Bit 7    | Bit 6       | Bit 5      | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|----------|-------------|------------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE      | PEIE        | TOIE       | INTE   | RBIE   | T0IF   | INTF   | RBIF   | 0000 000x            | 0000 000x                       |

| PIE1   | TMR1GIE  | ADIE        | RCIE       | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| PIR1   | TMR1GIF  | ADIF        | RCIF       | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| RCREG  | AUSART R | eceive Data | a Register |        |        |        |        |        | 0000 0000            | 0000 0000                       |

| RCSTA  | SPEN     | RX9         | SREN       | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 0000 000x            | 0000 000x                       |

| TRISC  | TRISC7   | TRISC6      | TRISC5     | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 1111 1111            | 1111 1111                       |

| TXSTA  | CSRC     | TX9         | TXEN       | SYNC   | —      | BRGH   | TRMT   | TX9D   | 0000 -010            | 0000 -010                       |

### TABLE 16-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for synchronous master reception.

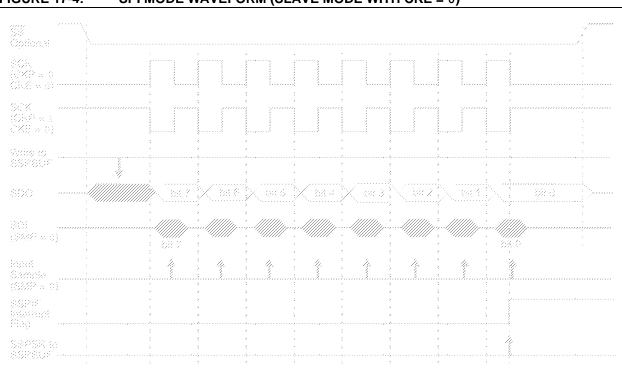

### FIGURE 17-4: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 0)

#### SS SCK (CKP = 0 $\dot{C}KE = 1)$ SCK (CKP = 1 CKE = 1) Write to SSPBUF bit 6 bit 5 bit 4 bit 2 bit 1 bit 0 SDO bit '7 bit 3 ï SDI (SMP = 0)I bit 0 bit 7 Input Sample (SMP = 0)SSPIF Interrupt Flag SSPSR to SSPBUF 1 . i . . . .

### FIGURE 17-5: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

### REGISTER 18-1: PMCON1: PROGRAM MEMORY CONTROL 1 REGISTER

| R-1      | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/S-0 |

|----------|-----|-----|-----|-----|-----|-----|-------|

| Reserved | —   | —I  | —   | —   | —   | —   | RD    |

| bit 7    |     |     |     |     |     |     | bit 0 |

|          |     |     |     |     |     |     |       |

| Legend:           |                  | S = Setable bit, cleared in hardware |                    |  |  |  |

|-------------------|------------------|--------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read          | 1 as '0'           |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                 | x = Bit is unknown |  |  |  |

| bit 7 <b>Reserved:</b> Read as '1'. Maintain this bit set. |

|------------------------------------------------------------|

| bit 7 <b>Reserved:</b> Read as '1'. Maintain this bit set. |

bit 6-1 Unimplemented: Read as '0'

bit 0 RD: Read Control bit

1 = Initiates an program memory read (The RD is cleared in hardware; the RD bit can only be set (not cleared) in software).

0 = Does not initiate a program memory read

### REGISTER 18-2: PMDATH: PROGRAM MEMORY DATA HIGH REGISTER

| U-0      | U-0 | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|----------|-----|-------|-------|-------|-------|-------|-------|

| —        | —   | PMD13 | PMD12 | PMD11 | PMD10 | PMD9  | PMD8  |

| bit 7    |     |       |       |       |       |       | bit 0 |

|          |     |       |       |       |       |       |       |

| l egend. |     |       |       |       |       |       |       |

| Legenu.           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **PMD<13:8>:** The value of the program memory word pointed to by PMADRH and PMADRL after a Program Memory Read command.

### REGISTER 18-3: PMDATL: PROGRAM MEMORY DATA LOW REGISTER

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| PMD7  | PMD6  | PMD5  | PMD4  | PMD3  | PMD2  | PMD1  | PMD0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-0 **PMD<7:0>:** The value of the program memory word pointed to by PMADRH and PMADRL after a Program Memory Read command.

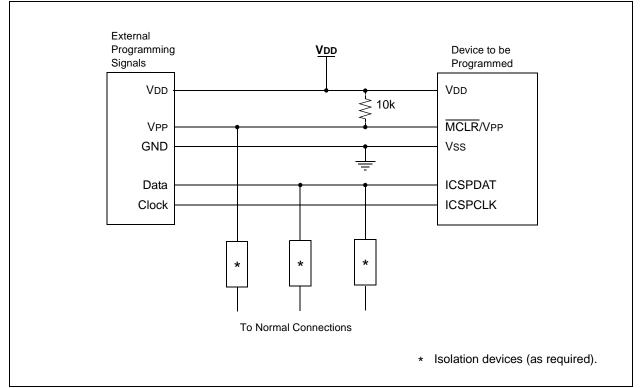

## 20.0 IN-CIRCUIT SERIAL PROGRAMMING<sup>™</sup> (ICSP<sup>™</sup>)

ICSP<sup>™</sup> programming allows customers to manufacture circuit boards with unprogrammed devices. Programming can be done after the assembly process allowing the device to be programmed with the most recent firmware or a custom firmware. Five pins are needed for ICSP<sup>™</sup> programming:

- ICSPCLK

- ICSPDAT

- MCLR/VPP

- VDD

- Vss

The device is placed into Program/Verify mode by holding the ICSPCLK and ICSPDAT pins low then raising the voltage on MCLR/VPP from 0v to VPP. In Program/Verify mode the Program Memory, User IDs and the Configuration Words are programmed through serial communications. The ICSPDAT pin is a bidirectional I/O used for transferring the serial data and the ISCPCLK pin is the clock input. For more information on ICSP<sup>TM</sup> refer to the "PIC16(L)F72X Memory Programming Specification" (DS41332).

**Note:** The ICD 2 produces a VPP voltage greater than the maximum VPP specification of the PIC16(L)F722A/723A. When using this programmer, an external circuit, such as the AC164112 MPLAB ICD 2 VPP voltage limiter, is required to keep the VPP voltage within the device specifications.

### FIGURE 20-1: TYPICAL CONNECTION FOR ICSP™ PROGRAMMING

| PIC16LF         | 722A/723 | A                                                         | $\begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for extended} \end{array}$ |                                                      |                          |                  |                                                                                                                                                                                                                                                                  |  |  |

|-----------------|----------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PIC16F722A/723A |          |                                                           |                                                                                                                                                                                                                                                            | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                          |                  |                                                                                                                                                                                                                                                                  |  |  |

| Param.<br>No.   | Sym.     | Characteristic                                            | Min.                                                                                                                                                                                                                                                       | Тур†                                                 | Max.                     | Units            | Conditions                                                                                                                                                                                                                                                       |  |  |

| D001            | Vdd      | Supply Voltage                                            |                                                                                                                                                                                                                                                            |                                                      |                          |                  |                                                                                                                                                                                                                                                                  |  |  |

|                 |          | PIC16LF722A/723A                                          | 1.8<br>1.8<br>2.3<br>2.5                                                                                                                                                                                                                                   |                                                      | 3.6<br>3.6<br>3.6<br>3.6 | V<br>V<br>V<br>V | Fosc $\leq$ 16 MHz: HFINTOSC, EC<br>Fosc $\leq$ 4 MHz<br>Fosc $\leq$ 20 MHz, EC<br>Fosc $\leq$ 20 MHz, HS                                                                                                                                                        |  |  |

| D001            |          | PIC16F722A/723A                                           | 1.8<br>1.8<br>2.3<br>2.5                                                                                                                                                                                                                                   |                                                      | 5.5<br>5.5<br>5.5<br>5.5 | V<br>V<br>V<br>V | Fosc $\leq$ 16 MHz: HFINTOSC, EC<br>Fosc $\leq$ 4 MHz<br>Fosc $\leq$ 20 MHz, EC<br>Fosc $\leq$ 20 MHz, HS                                                                                                                                                        |  |  |

| D002*           | Vdr      | RAM Data Retention Voltage <sup>(1)</sup>                 |                                                                                                                                                                                                                                                            |                                                      |                          |                  |                                                                                                                                                                                                                                                                  |  |  |

|                 |          | PIC16LF722A/723A                                          | 1.5                                                                                                                                                                                                                                                        |                                                      | —                        | V                | Device in Sleep mode                                                                                                                                                                                                                                             |  |  |

| D002*           |          | PIC16F722A/723A                                           | 1.7                                                                                                                                                                                                                                                        | —                                                    | _                        | V                | Device in Sleep mode                                                                                                                                                                                                                                             |  |  |

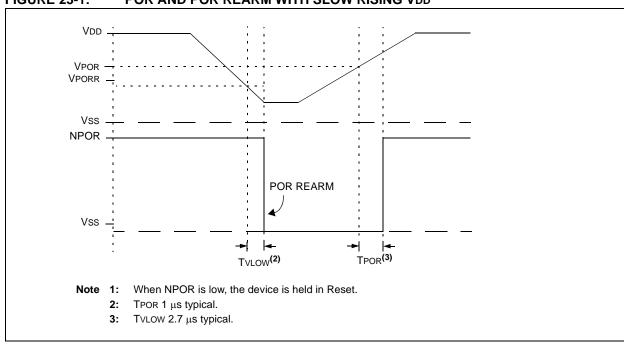

|                 | VPOR*    | Power-on Reset Release Voltage                            |                                                                                                                                                                                                                                                            | 1.6                                                  | _                        | V                |                                                                                                                                                                                                                                                                  |  |  |

|                 | VPORR*   | Power-on Reset Rearm Voltage                              |                                                                                                                                                                                                                                                            |                                                      |                          |                  |                                                                                                                                                                                                                                                                  |  |  |

|                 |          | PIC16LF722A/723A                                          |                                                                                                                                                                                                                                                            | 0.8                                                  | —                        | V                | Device in Sleep mode                                                                                                                                                                                                                                             |  |  |

|                 |          | PIC16F722A/723A                                           | _                                                                                                                                                                                                                                                          | 1.7                                                  |                          | V                | Device in Sleep mode                                                                                                                                                                                                                                             |  |  |

| D003            | Vfvr     | Fixed Voltage Reference Voltage,<br>Initial Accuracy      | -5.5<br>-5.5<br>-5.5                                                                                                                                                                                                                                       | <br> <br>                                            | 5.5<br>5.5<br>5.5        | %<br>%<br>%      | $ \begin{array}{l} {\sf VFVR} = 1.024{\sf V},  {\sf VDD} \geq 2.5{\sf V} \\ {\sf VFVR} = 2.048{\sf V},  {\sf VDD} \geq 2.5{\sf V} \\ {\sf VFVR} = 4.096{\sf V},  {\sf VDD} \geq 4.75{\sf V}; \\ {\sf -40} \leq {\sf TA} \leq 85^{\circ}{\sf C} \end{array} $     |  |  |

|                 |          |                                                           | -6<br>-6<br>-6                                                                                                                                                                                                                                             |                                                      | 6<br>6<br>6              | %<br>%<br>%      | $ \begin{array}{l} V{\sf FVR} = 1.024{\sf V}, \ {\sf VDD} \geq 2.5{\sf V} \\ {\sf VFVR} = 2.048{\sf V}, \ {\sf VDD} \geq 2.5{\sf V} \\ {\sf VFVR} = 4.096{\sf V}, \ {\sf VDD} \geq 4.75{\sf V}; \\ {\sf -40} \leq {\sf TA} \leq 125^{\circ}{\sf C} \end{array} $ |  |  |

| D004*           | SVDD     | VDD Rise Rate to ensure internal<br>Power-on Reset signal | 0.05                                                                                                                                                                                                                                                       |                                                      | —                        | V/ms             | See Section 3.2 "Power-on Reset (POR)" for details.                                                                                                                                                                                                              |  |  |

## 23.1 DC Characteristics: PIC16(L)F722A/723A-I/E (Industrial, Extended)

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

### FIGURE 23-1: POR AND POR REARM WITH SLOW RISING VDD

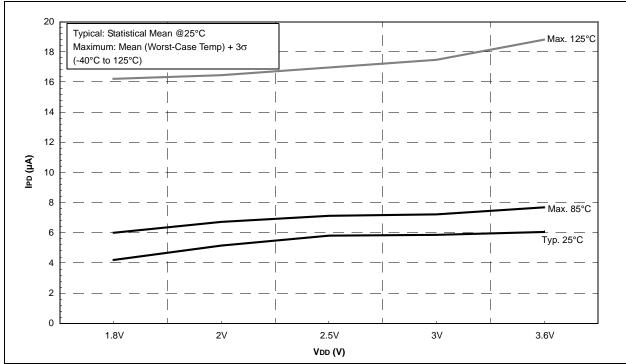

## 23.3 DC Characteristics: PIC16(L)F722A/723A-I/E (Power-Down) (Continued)

| PIC16LF722A/723A |                         |                      |      | r <b>d Opera</b> t<br>ng temper |        | -40°C ≤                                                                                                                        | TA ≤ +85° | n <b>erwise stated)</b><br>²C for industrial<br>5°C for extended |  |

|------------------|-------------------------|----------------------|------|---------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------|-----------|------------------------------------------------------------------|--|

| PIC16F722A/723A  |                         |                      |      | rd Operating temper             |        | ditions (unless otherwise stated)<br>-40°C $\leq$ TA $\leq$ +85°C for industrial<br>-40°C $\leq$ TA $\leq$ +125°C for extended |           |                                                                  |  |

| Param            | Device Characteristics  | Min.                 | Тур† | Max.                            | Max.   | Units                                                                                                                          |           | Conditions                                                       |  |

| No.              |                         |                      |      | +85°C                           | +125°C |                                                                                                                                | VDD       | Note                                                             |  |

|                  | Power-down Base Current | (IPD) <sup>(2)</sup> |      | -                               |        |                                                                                                                                | -         |                                                                  |  |

| D027             |                         |                      | 0.06 | 0.7                             | 5.0    | μΑ                                                                                                                             | 1.8       | A/D Current (Note 1, Note 4), no                                 |  |

|                  |                         | —                    | 0.08 | 1.0                             | 5.5    | μΑ                                                                                                                             | 3.0       | conversion in progress                                           |  |

| D027             |                         |                      | 6    | 10.7                            | 18     | μΑ                                                                                                                             | 1.8       | A/D Current (Note 1, Note 4), no                                 |  |

|                  |                         |                      | 7    | 10.6                            | 20     | μΑ                                                                                                                             | 3.0       | conversion in progress                                           |  |

|                  |                         | —                    | 7.2  | 11.9                            | 22     | μΑ                                                                                                                             | 5.0       |                                                                  |  |

| D027A            |                         |                      | 250  | 400                             | —      | μΑ                                                                                                                             | 1.8       | A/D Current (Note 1, Note 4),                                    |  |

|                  |                         | —                    | 250  | 400                             | —      | μΑ                                                                                                                             | 3.0       | conversion in progress                                           |  |

| D027A            |                         |                      | 280  | 430                             | —      | μΑ                                                                                                                             | 1.8       | A/D Current (Note 1, Note 4,                                     |  |

|                  |                         |                      | 280  | 430                             | —      | μΑ                                                                                                                             | 3.0       | Note 5), conversion in progress                                  |  |

|                  |                         | —                    | 280  | 430                             | —      | μΑ                                                                                                                             | 5.0       |                                                                  |  |

| D028             |                         | —                    | 2.2  | 3.2                             | 14.4   | μA                                                                                                                             | 1.8       | Cap Sense Low Power                                              |  |

|                  |                         | —                    | 3.3  | 4.4                             | 15.6   | μA                                                                                                                             | 3.0       | Oscillator mode                                                  |  |

| D028             |                         | _                    | 6.5  | 13                              | 21     | μΑ                                                                                                                             | 1.8       | Cap Sense Low Power                                              |  |

|                  |                         | —                    | 8    | 14                              | 23     | μΑ                                                                                                                             | 3.0       | Oscillator mode                                                  |  |

|                  |                         | —                    | 8    | 14                              | 25     | μΑ                                                                                                                             | 5.0       |                                                                  |  |

| D028A            |                         |                      | 4.2  | 6                               | 17     | μA                                                                                                                             | 1.8       | Cap Sense Medium Power                                           |  |

|                  |                         | —                    | 6    | 7                               | 18     | μA                                                                                                                             | 3.0       | Oscillator mode                                                  |  |

| D028A            |                         |                      | 8.5  | 15.5                            | 23     | μA                                                                                                                             | 1.8       | Cap Sense Medium Power                                           |  |

|                  |                         | _                    | 11   | 17                              | 24     | μΑ                                                                                                                             | 3.0       | Oscillator mode                                                  |  |

|                  |                         | _                    | 11   | 18                              | 27     | μA                                                                                                                             | 5.0       |                                                                  |  |

| D028B            |                         | _                    | 12   | 14                              | 25     | μA                                                                                                                             | 1.8       | Cap Sense High Power                                             |  |

|                  |                         |                      | 32   | 35                              | 44     | μA                                                                                                                             | 3.0       | Oscillator mode                                                  |  |

| D028B            |                         | _                    | 16   | 20                              | 31     | μA                                                                                                                             | 1.8       | Cap Sense High Power                                             |  |

|                  |                         | _                    | 36   | 41                              | 50     | μA                                                                                                                             | 3.0       | Oscillator mode                                                  |  |

|                  |                         |                      | 42   | 49                              | 58     | μΑ                                                                                                                             | 5.0       | ]                                                                |  |

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral △ current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD.

3: Fixed Voltage Reference is automatically enabled whenever the BOR is enabled.

4: A/D oscillator source is FRC.

5: 0.1  $\mu$ F capacitor on VCAP (RA0).

|                 | DC CI | HARACTERISTICS                       |                   | •    | $-40^{\circ}C \le TA$ | ≤ +85°C | otherwise stated)<br>c for industrial<br>C for extended                    |

|-----------------|-------|--------------------------------------|-------------------|------|-----------------------|---------|----------------------------------------------------------------------------|

| Param<br>No.    | Sym.  | Characteristic                       | Min.              | Тур† | Max.                  | Units   | Conditions                                                                 |

|                 | VIL   | Input Low Voltage                    |                   |      |                       |         |                                                                            |

|                 |       | I/O PORT:                            |                   |      |                       |         |                                                                            |

| D030            |       | with TTL buffer                      | —                 | _    | 0.8                   | V       | $4.5V \leq V\text{DD} \leq 5.5V$                                           |

| D030A           |       |                                      | —                 |      | 0.15 Vdd              | V       | $1.8V \le V\text{DD} \le 4.5V$                                             |

| D031            |       | with Schmitt Trigger buffer          | —                 | _    | 0.2 Vdd               | V       | $2.0V \le V\text{DD} \le 5.5V$                                             |

|                 |       | with I <sup>2</sup> C levels         | —                 |      | 0.3 Vdd               | V       |                                                                            |

| D032            |       | MCLR, OSC1 (RC mode) <sup>(1)</sup>  | —                 | _    | 0.2 Vdd               | V       |                                                                            |

| D033A           |       | OSC1 (HS mode)                       |                   | _    | 0.3 Vdd               | V       |                                                                            |

|                 | VIH   | Input High Voltage                   |                   |      |                       |         |                                                                            |

|                 |       | I/O ports:                           |                   | _    |                       |         |                                                                            |

| D040            |       | with TTL buffer                      | 2.0               | _    | _                     | V       | $4.5V \leq V\text{DD} \leq 5.5V$                                           |

| D040A           |       |                                      | 0.25 VDD +<br>0.8 | —    | -                     | V       | $1.8V \leq V\text{DD} \leq 4.5V$                                           |

| D041            |       | with Schmitt Trigger buffer          | 0.8 Vdd           | _    | —                     | V       | $2.0V \le V\text{DD} \le 5.5V$                                             |

|                 |       | with I <sup>2</sup> C levels         | 0.7 Vdd           | _    | —                     | V       |                                                                            |

| D042            |       | MCLR                                 | 0.8 Vdd           |      | _                     | V       |                                                                            |

| D043A           |       | OSC1 (HS mode)                       | 0.7 Vdd           |      | _                     | V       |                                                                            |

| D043B           |       | OSC1 (RC mode)                       | 0.9 Vdd           |      | _                     | V       | (Note 1)                                                                   |

|                 | lı∟   | Input Leakage Current <sup>(2)</sup> |                   |      |                       |         |                                                                            |

| D060            |       | I/O ports                            | —                 | ± 5  | ± 125                 | nA      | Vss $\leq$ VPIN $\leq$ VDD, Pin at high-impedance, 85°C                    |

|                 |       |                                      |                   | ± 5  | ± 1000                | nA      | 125°C                                                                      |

| D061            |       | MCLR <sup>(3)</sup>                  | —                 | ± 50 | ± 200                 | nA      | $VSS \le VPIN \le VDD, 85^{\circ}C$                                        |

|                 | IPUR  | PORTB Weak Pull-up Current           |                   |      | _                     | _       |                                                                            |

| D070*           |       |                                      | 25                | 100  | 200                   |         | VDD = 3.3V, VPIN = VSS                                                     |

|                 |       |                                      | 25                | 140  | 300                   | μΑ      | VDD = 5.0V, VPIN = VSS                                                     |

|                 | Vol   | Output Low Voltage <sup>(4)</sup>    | г – т             |      | 1                     | 1       |                                                                            |

| D080            |       | I/O ports                            | _                 | _    | 0.6                   | v       | IOL = 8 mA, VDD = 5V<br>IOL = 6 mA, VDD = 3.3V<br>IOL = 1.8 mA, VDD = 1.8V |

|                 | Voн   | Output High Voltage <sup>(4)</sup>   |                   |      |                       |         |                                                                            |

| D090            |       | I/O ports                            | Vdd - 0.7         | _    | _                     | V       | IOH = 3.5 mA, VDD = 5V<br>IOH = 3 mA, VDD = 3.3V<br>IOH = 1 mA, VDD = 1.8V |

|                 |       | Capacitive Loading Specs on          | Output Pins       |      | 1                     | 1       | I , -                                                                      |

| Ì               | 1     | OSC2 pin                             | _                 | _    | 15                    | pF      | In XT, HS and LP modes when                                                |

| D101*           | COSC2 | 0002 pm                              |                   |      |                       |         | external clock is used to drive OSC1                                       |

| D101*<br>D101A* | COSC2 | All I/O pins                         | _                 | _    | 50                    | pF      |                                                                            |

### 23.4 DC Characteristics: PIC16(L)F722A/723A-I/E

**Legend:** TBD = To Be Determined

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

**2:** Negative current is defined as current sourced by the pin.

3: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

**4:** Including OSC2 in CLKOUT mode.

### 23.5 Thermal Considerations

|              |           | Conditions (unless otherwise stated) re $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |       |                                                          |

|--------------|-----------|---------------------------------------------------------------------------------|------|-------|----------------------------------------------------------|

| Param<br>No. | Sym.      | Characteristic                                                                  | Тур. | Units | Conditions                                               |

| TH01         | θJA       | Thermal Resistance Junction to Ambient                                          | 60.0 | °C/W  | 28-pin SPDIP package                                     |

|              |           |                                                                                 | 69.7 | °C/W  | 28-pin SOIC package                                      |

|              |           |                                                                                 | 71.0 | °C/W  | 28-pin SSOP package                                      |

|              |           |                                                                                 | 52.5 | °C/W  | 28-pin UQFN 4x4mm package                                |

|              |           |                                                                                 | 30.0 | °C/W  | 28-pin QFN 6x6mm package                                 |

| TH02         | θJC       | Thermal Resistance Junction to Case                                             | 29.0 | °C/W  | 28-pin SPDIP package                                     |

|              |           |                                                                                 | 18.9 | °C/W  | 28-pin SOIC package                                      |

|              |           |                                                                                 | 24.0 | °C/W  | 28-pin SSOP package                                      |

|              |           |                                                                                 | 16.7 | °C/W  | 28-pin UQFN 4x4mm package                                |

|              |           |                                                                                 | 5.0  | °C/W  | 28-pin QFN 6x6mm package                                 |

| TH03         | Тјмах     | Maximum Junction Temperature                                                    | 150  | °C    |                                                          |

| TH04         | PD        | Power Dissipation                                                               | _    | W     | PD = PINTERNAL + PI/O                                    |

| TH05         | PINTERNAL | Internal Power Dissipation                                                      | _    | W     | PINTERNAL = IDD x VDD <sup>(1)</sup>                     |

| TH06         | Pi/o      | I/O Power Dissipation                                                           | _    | W     | $PI/O = \Sigma (IOL * VOL) + \Sigma (IOH * (VDD - VOH))$ |

| TH07         | Pder      | Derated Power                                                                   | —    | W     | Pder = PDmax (Tj - Ta)/θja <sup>(2)</sup>                |

Note 1: IDD is current to run the chip alone without driving any load on the output pins.

2: TA = Ambient Temperature

**3:** T<sub>J</sub> = Junction Temperature

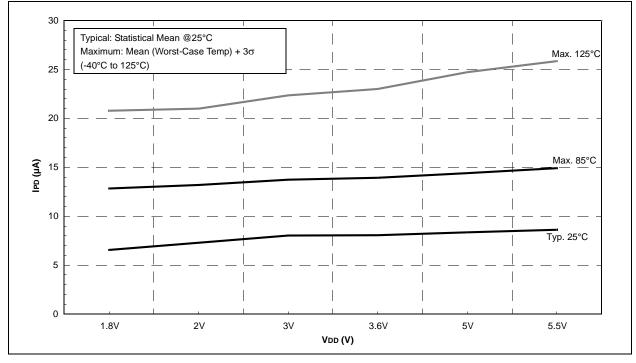

### FIGURE 24-38: PIC16LF722A/723A CAP SENSE MEDIUM POWER IPD vs. VDD

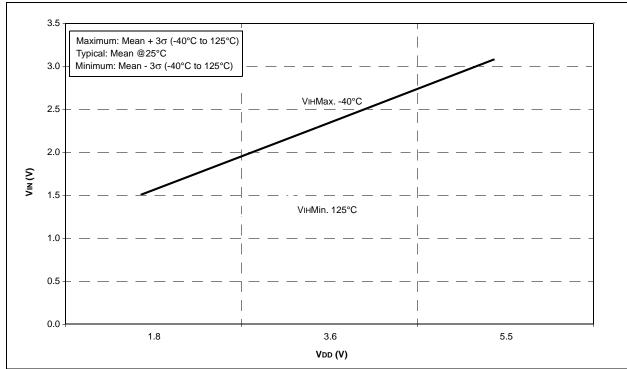

FIGURE 24-50: SCHMITT TRIGGER INPUT THRESHOLD VIN vs. VDD OVER TEMPERATURE

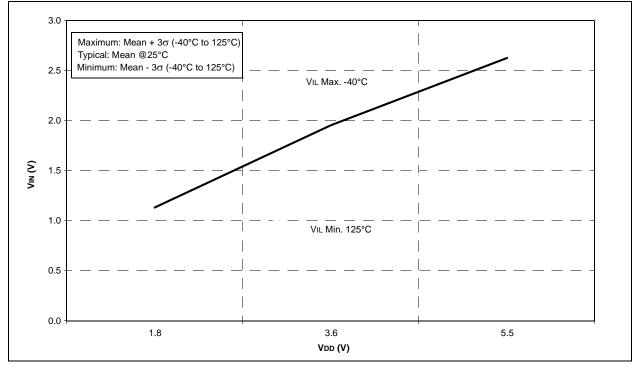

FIGURE 24-51: SCHMITT TRIGGER INPUT THRESHOLD VIN vs. VDD OVER TEMPERATURE

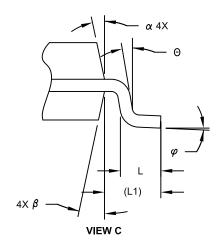

### 28-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                    |    | MILLIMETERS |     |      |

|--------------------------|----|-------------|-----|------|

| Dimension Limits         |    | MIN         | NOM | MAX  |

| Number of Pins           | N  | 28          |     |      |

| Pitch                    | е  | 1.27 BSC    |     |      |

| Overall Height           | A  | -           | -   | 2.65 |

| Molded Package Thickness | A2 | 2.05        | -   | -    |

| Standoff §               | A1 | 0.10        | -   | 0.30 |

| Overall Width            | E  | 10.30 BSC   |     |      |

| Molded Package Width     | E1 | 7.50 BSC    |     |      |

| Overall Length           | D  | 17.90 BSC   |     |      |

| Chamfer (Optional)       | h  | 0.25        | -   | 0.75 |

| Foot Length              | L  | 0.40        | -   | 1.27 |

| Footprint                | L1 | 1.40 REF    |     |      |

| Lead Angle               | Θ  | 0°          | -   | -    |

| Foot Angle               | φ  | 0°          | -   | 8°   |

| Lead Thickness           | С  | 0.18        | -   | 0.33 |

| Lead Width               | b  | 0.31        | -   | 0.51 |

| Mold Draft Angle Top     | α  | 5°          | -   | 15°  |

| Mold Draft Angle Bottom  | β  | 5°          | -   | 15°  |

### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- Dimensioning and tolerancing per ASME Y14.5M BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing C04-052C Sheet 2 of 2