Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 25                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                |                                                                             |

| RAM Size                   | 192 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 11x8b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 28-UQFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf723at-i-mv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16(L)F722A/723A

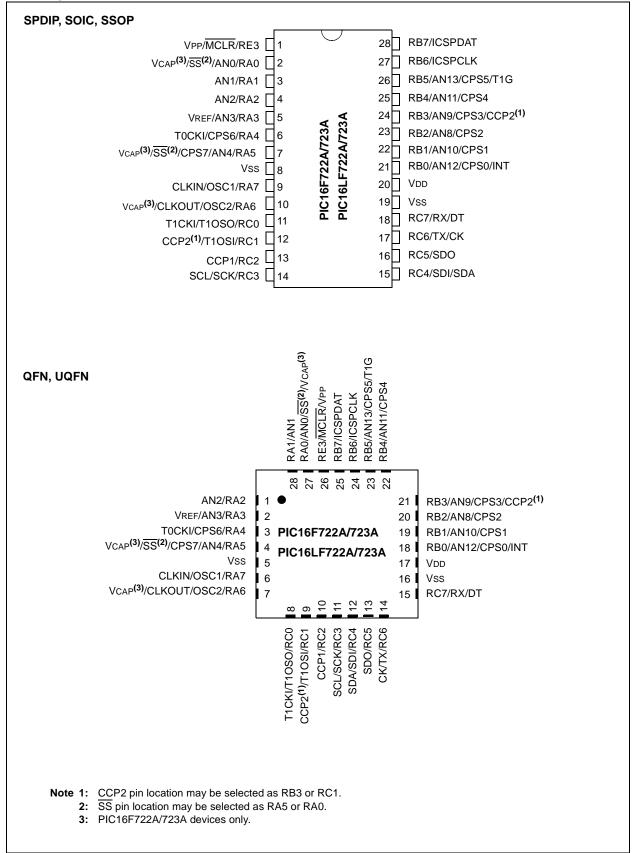

### Pin Diagrams - 28-PIN SPDIP/SOIC/SSOP/QFN/UQFN (PIC16(L)F722A/723A)

#### FIGURE 2-3:

## PIC16(L)F722A SPECIAL FUNCTION REGISTERS

| Indirect addr.(*)  | 00h | Indirect addr. <sup>(*)</sup>              | 80h       | Indirect addr. <sup>(*)</sup> | 100h | Indirect addr.(*)   | 180h |

|--------------------|-----|--------------------------------------------|-----------|-------------------------------|------|---------------------|------|

| TMR0               | 01h | OPTION                                     | 81h       | TMR0                          | 101h | OPTION              | 181h |

| PCL                | 02h | PCL                                        | 82h       | PCL                           | 102h | PCL                 | 182h |

| STATUS             | 03h | STATUS                                     | 83h       | STATUS                        | 103h | STATUS              | 183h |

| FSR                | 04h | FSR                                        | 84h       | FSR                           | 104h | FSR                 | 184h |

| PORTA              | 05h | TRISA                                      | 85h       |                               | 105h | ANSELA              | 185h |

| PORTB              | 06h | TRISB                                      | 86h       |                               | 106h | ANSELB              | 186h |

| PORTC              | 07h | TRISC                                      | 87h       |                               | 107h |                     | 187h |

|                    | 08h |                                            | 88h       | CPSCON0                       | 108h |                     | 188h |

| PORTE              | 09h | TRISE                                      | 89h       | CPSCON1                       | 109h |                     | 189h |

| PCLATH             | 0Ah | PCLATH                                     | 8Ah       | PCLATH                        | 10Ah | PCLATH              | 18Ah |

| INTCON             | 0Bh | INTCON                                     | 8Bh       | INTCON                        | 10Bh | INTCON              | 18Bh |

| PIR1               | 0Ch | PIE1                                       | 8Ch       | PMDATL                        | 10Ch | PMCON1              | 18Ch |

| PIR2               | 0Dh | PIE2                                       | 8Dh       | PMADRL                        | 10Dh | Reserved            | 18Dh |

| TMR1L              | 0Eh | PCON                                       | 8Eh       | PMDATH                        | 10Eh | Reserved            | 18Eh |

| TMR1H              | 0Fh | T1GCON                                     | 8Fh       | PMADRH                        | 10Fh | Reserved            | 18Fh |

| T1CON              | 10h | OSCCON                                     | 90h       |                               | 110h |                     | 190h |

| TMR2               | 11h | OSCTUNE                                    | 91h       |                               | 111h |                     | 191h |

| T2CON              | 12h | PR2                                        | 92h       |                               | 112h |                     | 192h |

| SSPBUF             | 13h | SSPADD/SSPMSK                              | 93h       |                               | 113h |                     | 193h |

| SSPCON             | 14h | SSPSTAT                                    | 94h       |                               | 114h |                     | 194h |

| CCPR1L             | 15h | WPUB                                       | 95h       |                               | 115h |                     | 195h |

| CCPR1H             | 16h | IOCB                                       | 96h       |                               | 116h |                     | 196h |

| CCP1CON            | 17h |                                            | 97h       |                               | 117h |                     | 197h |

| RCSTA              | 18h | TXSTA                                      | 98h       |                               | 118h |                     | 198h |

| TXREG              | 19h | SPBRG                                      | 99h       |                               | 119h |                     | 199h |

| RCREG              | 1Ah |                                            | 9Ah       |                               | 11Ah |                     | 19Ah |

| CCPR2L             | 1Bh |                                            | 9Bh       |                               | 11Bh |                     | 19Bh |

| CCPR2H             | 1Ch | APFCON                                     | 9Ch       |                               | 11Ch |                     | 19Ch |

| CCP2CON            | 1Dh | FVRCON                                     | 9Dh       |                               | 11Dh |                     | 19Dh |

| ADRES              | 1Eh |                                            | 9Eh       |                               | 11Eh |                     | 19Eh |

| ADCON0             | 1Fh | ADCON1                                     | 9Fh       |                               | 11Fh |                     | 19Fh |

|                    | 20h |                                            | A0h       |                               | 120h |                     | 1A0h |

| General<br>Purpose |     | General<br>Purpose<br>Register<br>32 Bytes | BFh       |                               |      |                     |      |

| Register           |     |                                            | C0h       |                               |      |                     |      |

| 96 Bytes           |     |                                            | EFh       |                               | 16Fh |                     | 1EFh |

| -                  |     |                                            | F0h       |                               | 170h |                     | 1F0h |

|                    |     | Accesses<br>70h-7Fh                        |           | Accesses<br>70h-7Fh           |      | Accesses<br>70h-7Fh |      |

|                    | 7Fh |                                            | FFh       |                               | 17Fh |                     | 1FFh |

| Bank 0             |     | Bank 1                                     |           | Bank 2                        |      | Bank 3              |      |

|                    |     | nted data memory loc<br>cal register.      | ations, I | read as '0'.                  |      |                     |      |

| Name       | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3   | Bit 2   | Bit 1       | Bit 0   | Register<br>on Page |

|------------|--------|--------|--------|--------|---------|---------|-------------|---------|---------------------|

| ADCON0     | _      | _      | CHS3   | CHS2   | CHS1    | CHS0    | GO/<br>DONE | ADON    | 85                  |

| ADCON1     | _      | ADCS2  | ADCS1  | ADCS0  | —       | —       | ADREF1      | ADREF0  | 86                  |

| ANSELA     | _      | —      | ANSA5  | ANSA4  | ANSA3   | ANSA2   | ANSA1       | ANSA0   | 44                  |

| APFCON     | —      | —      | _      | _      | —       | —       | SSSEL       | CCP2SEL | 42                  |

| CPSCON0    | CPSON  | —      | _      | _      | CPSRNG1 | CPSRNG0 | CPSOUT      | TOXCS   | 112                 |

| CPSCON1    | _      | —      |        | _      | _       | CPSCH2  | CPSCH1      | CPSCH0  | 113                 |

| OPTION_REG | RBPU   | INTEDG | TOCS   | T0SE   | PSA     | PS2     | PS1         | PS0     | 19                  |

| PORTA      | RA7    | RA6    | RA5    | RA4    | RA3     | RA2     | RA1         | RA0     | 43                  |

| SSPCON     | WCOL   | SSPOV  | SSPEN  | CKP    | SSPM3   | SSPM2   | SSPM1       | SSPM0   | 152                 |

| TRISA      | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3  | TRISA2  | TRISA1      | TRISA0  | 43                  |

#### TABLE 6-1: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

**Legend:** x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

#### TABLE 6-2: SUMMARY OF CONFIGURATION WORD WITH CLOCK SOURCES

| Name                   | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|------------------------|------|---------|---------|----------|----------|----------|----------|---------|---------|---------------------|

| CONFIG2 <sup>(1)</sup> | 13:8 | _       | _       | _        | _        | _        | —        | _       | —       | 70                  |

|                        | 7:0  | _       | _       | VCAPEN1  | VCAPEN0  | WDTE     | _        | _       | —       | 78                  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

Note 1: PIC16F722A/723A only.

| R/W-x                          | R/W-x | R/W-x        | R/W-x | R/W-x        | R/W-x            | R/W-x  | R/W-x |

|--------------------------------|-------|--------------|-------|--------------|------------------|--------|-------|

| RB7                            | RB6   | RB5          | RB4   | RB3          | RB2              | RB1    | RB0   |

| bit 7                          |       |              |       |              |                  |        | bit 0 |

|                                |       |              |       |              |                  |        |       |

|                                |       |              |       |              |                  |        |       |

| Legend:                        |       |              |       |              |                  |        |       |

| <b>Legend:</b><br>R = Readable | bit   | W = Writable | bit   | U = Unimplen | nented bit, read | as '0' |       |

#### REGISTER 6-5: PORTB: PORTB REGISTER

bit 7-0 RB<7:0>: PORTB I/O Pin bits

1 = Port pin is > VIH

0 = Port pin is < VIL

#### REGISTER 6-6: TRISB: PORTB TRI-STATE REGISTER

| R/W-1  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0

**—**

TRISB<7:0>: PORTB Tri-State Control bits

1 = PORTB pin configured as an input (tri-stated)

0 = PORTB pin configured as an output

#### REGISTER 6-7: WPUB: WEAK PULL-UP PORTB REGISTER

| R/W-1 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| WPUB7 | WPUB6 | WPUB5 | WPUB4 | WPUB3 | WPUB2 | WPUB1 | WPUB0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 **WPUB<7:0>**: Weak Pull-up Register bits

1 = Pull up enabled

0 = Pull up disabled

**Note 1:** Global RBPU bit of the OPTION register must be cleared for individual pull ups to be enabled.

2: The weak pull-up device is automatically disabled if the pin is in configured as an output.

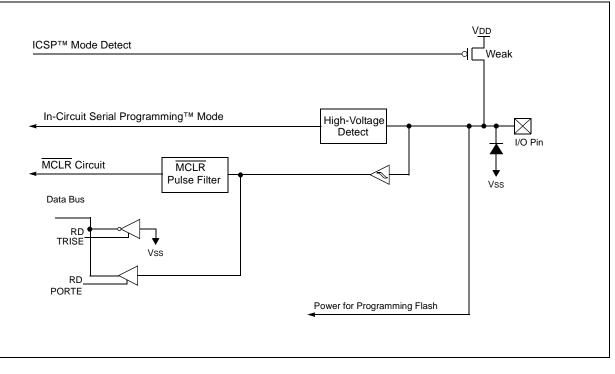

### 6.5.1 RE3/MCLR/VPP

Figure 6-21 shows the diagram for this pin. This pin is configurable to function as one of the following:

- General purpose input

- Master Clear Reset with weak pull up

- Programming voltage reference input

### FIGURE 6-21: BLOCK DIAGRAM OF RE3

## 7.5 Oscillator Tuning

The INTOSC is factory-calibrated but can be adjusted in software by writing to the OSCTUNE register (Register 7-2).

The default value of the OSCTUNE register is '0'. The value is a 6-bit two's complement number.

When the OSCTUNE register is modified, the INTOSC frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred.

#### REGISTER 7-2: OSCTUNE: OSCILLATOR TUNING REGISTER

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     |     | TUN5  | TUN4  | TUN3  | TUN2  | TUN1  | TUN0  |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 7-6 Unimplemented: Read as '0'

bit 5-0

## 7.6 External Clock Modes

#### 7.6.1 OSCILLATOR START-UP TIMER (OST)

If the oscillator module is configured for LP, XT or HS modes, the Oscillator Start-up Timer (OST) counts 1024 oscillations on the OSC1 pin before the device is released from Reset. This occurs following a Power-on Reset (POR) and when the Power-up Timer (PWRT) has expired (if configured), or a wake-up from Sleep. During this time, the program counter does not increment and program execution is suspended. The OST ensures that the oscillator circuit, using a quartz crystal resonator or ceramic resonator, has started and is providing a stable system clock to the oscillator module.

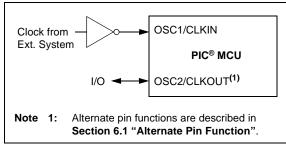

### 7.6.2 EC MODE

The External Clock (EC) mode allows an externally generated logic level as the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input and the OSC2 is available for general purpose I/O. Figure 7-2 shows the pin connections for EC mode.

The Oscillator Start-up Timer (OST) is disabled when EC mode is selected. Therefore, there is no delay in operation after a Power-on Reset (POR) or wake-up from Sleep. Because the PIC<sup>®</sup> MCU design is fully static, stopping the external clock input will have the effect of halting the device while leaving all data intact. Upon restarting the external clock, the device will resume operation as if no time had elapsed.

#### FIGURE 7-2: EXTERNAL CLOCK (EC) MODE OPERATION

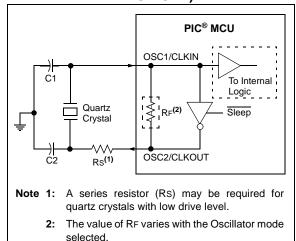

### 7.6.3 LP, XT, HS MODES

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 7-3). The mode selects a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

LP Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is best suited to drive resonators with a low drive level specification, for example, tuning fork type crystals.

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 7-3 and Figure 7-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

#### FIGURE 7-3: QUARTZ CRYSTAL OPERATION (LP, XT OR HS MODE)

Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- **2:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Applications Notes:

- AN826, Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices (DS00826)

- AN849, Basic PIC<sup>®</sup> Oscillator Design (DS00849)

- AN943, Practical PIC<sup>®</sup> Oscillator Analysis and Design (DS00943)

- AN949, Making Your Oscillator Work (DS00949)

## 15.0 CAPTURE/COMPARE/PWM (CCP) MODULE

The Capture/Compare/PWM module is a peripheral which allows the user to time and control different events. In Capture mode, the peripheral allows the timing of the duration of an event. The Compare mode allows the user to trigger an external event when a predetermined amount of time has expired. The PWM mode can generate a Pulse-Width Modulated signal of varying frequency and duty cycle.

The timer resources used by the module are shown in Table 15-1.

Additional information on CCP modules is available in the Application Note *AN594, Using the CCP Modules* (DS00594).

#### TABLE 15-1: CCP MODE – TIMER RESOURCES REQUIRED

| CCP Mode | Timer Resource |

|----------|----------------|

| Capture  | Timer1         |

| Compare  | Timer1         |

| PWM      | Timer2         |

| CCP1 Mode | CCP2 Mode | Interaction                                                                                                  |

|-----------|-----------|--------------------------------------------------------------------------------------------------------------|

| Capture   | Capture   | Same TMR1 time base                                                                                          |

| Capture   | Compare   | Same TMR1 time base <sup>(1, 2)</sup>                                                                        |

| Compare   | Compare   | Same TMR1 time base <sup>(1, 2)</sup>                                                                        |

| PWM       | PWM       | The PWMs will have the same frequency and update rate (TMR2 interrupt).<br>The rising edges will be aligned. |

| PWM       | Capture   | None                                                                                                         |

| PWM       | Compare   | None                                                                                                         |

## TABLE 15-2: INTERACTION OF TWO CCP MODULES

**Note 1:** If CCP2 is configured as a Special Event Trigger, CCP1 will clear Timer1, affecting the value captured on the CCP2 pin.

2: If CCP1 is in Capture mode and CCP2 is configured as a Special Event Trigger, CCP2 will clear Timer1, affecting the value captured on the CCP1 pin.

| Note: | CCPRx   | and      | CCPx     | throughout  | this |

|-------|---------|----------|----------|-------------|------|

|       | documer | nt refer | to CCP   | R1 or CCPR2 | and  |

|       | CCP1 or | CCP2     | , respec | tively.     |      |

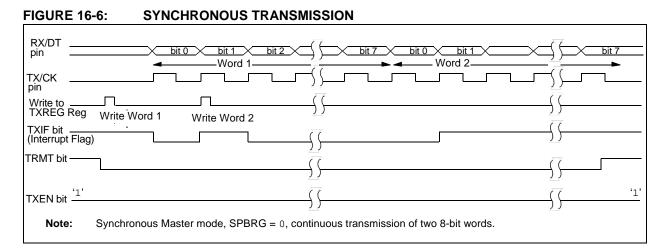

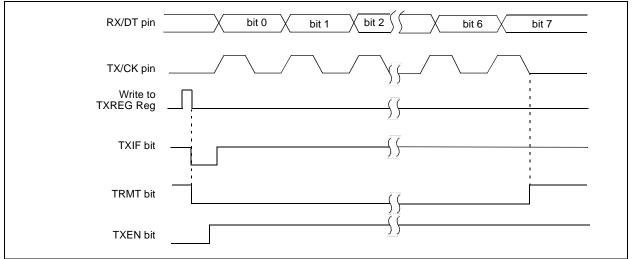

### FIGURE 16-7: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

#### TABLE 16-6: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Name   | Bit 7    | Bit 6       | Bit 5      | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|----------|-------------|------------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE      | PEIE        | TOIE       | INTE   | RBIE   | T0IF   | INTF   | RBIF   | 0000 000x            | 0000 000x                       |

| PIE1   | TMR1GIE  | ADIE        | RCIE       | TXIE   | SSPIE  | CCP1IE | TMR2IE | TMR1IE | 0000 0000            | 0000 0000                       |

| PIR1   | TMR1GIF  | ADIF        | RCIF       | TXIF   | SSPIF  | CCP1IF | TMR2IF | TMR1IF | 0000 0000            | 0000 0000                       |

| RCSTA  | SPEN     | RX9         | SREN       | CREN   | ADDEN  | FERR   | OERR   | RX9D   | 0000 000x            | 0000 000x                       |

| SPBRG  | BRG7     | BRG6        | BRG5       | BRG4   | BRG3   | BRG2   | BRG1   | BRG0   | 0000 0000            | 0000 0000                       |

| TRISC  | TRISC7   | TRISC6      | TRISC5     | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 1111 1111            | 1111 1111                       |

| TXREG  | AUSART T | ransmit Dat | a Register |        |        |        |        |        | 0000 0000            | 0000 0000                       |

| TXSTA  | CSRC     | TX9         | TXEN       | SYNC   | _      | BRGH   | TRMT   | TX9D   | 0000 -010            | 0000 -010                       |

Legend: x = unknown, - = unimplemented read as '0'. Shaded cells are not used for synchronous master transmission.

# PIC16(L)F722A/723A

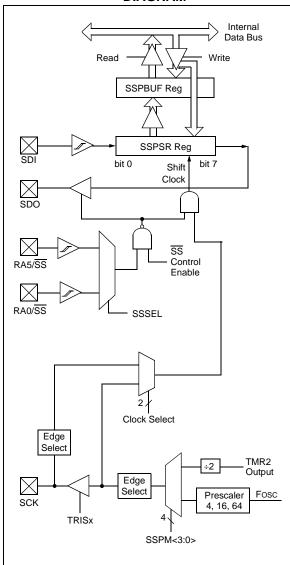

FIGURE 17-2: SPI MODE BLOCK DIAGRAM

#### 17.1.1 MASTER MODE

In Master mode, data transfer can be initiated at any time because the master controls the SCK line. Master mode determines when the slave (Figure 17-1, Processor 2) transmits data via control of the SCK line.

#### 17.1.1.1 Master Mode Operation

The SSP consists of a transmit/receive shift register (SSPSR) and a buffer register (SSPBUF). The SSPSR register shifts the data in and out of the device, MSb first. The SSPBUF register holds the data that is written out of the master until the received data is ready. Once the eight bits of data have been received, the byte is moved to the SSPBUF register. The Buffer Full Status bit, BF of the SSPSTAT register, and the SSP Interrupt Flag bit, SSPIF of the PIR1 register, are then set.

Any write to the SSPBUF register during transmission/ reception of data will be ignored and the Write Collision Detect bit, WCOL of the SSPCON register, will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPBUF register completed successfully.

When the application software is expecting to receive valid data, the SSPBUF should be read before the next byte of data is written to the SSPBUF. The BF bit of the SSPSTAT register is set when SSPBUF has been loaded with the received data (transmission is complete). When the SSPBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. The SSP interrupt may be used to determine when the transmission/reception is complete and the SSPBUF must be read and/or written. If interrupts are not used, then software polling can be done to ensure that a write collision does not occur. Example 17-1 shows the loading of the SSPBUF (SSPSR) for data transmission.

Note: The SSPSR is not directly readable or writable and can only be accessed by addressing the SSPBUF register.

### 17.1.1.2 Enabling Master I/O

To enable the serial port, the SSPEN bit of the SSPCON register, must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, re-initialize the SSPCON register and then set the SSPEN bit. If a Master mode of operation is selected in the SSPM bits of the SSPCON register, the SDI, SDO and SCK pins will be assigned as serial port pins.

For these pins to function as serial port pins, they must have their corresponding data direction bits set or cleared in the associated TRIS register as follows:

- SDI configured as input

- SDO configured as output

- SCK configured as output

#### 17.1.1.3 Master Mode Setup

In Master mode, the data is transmitted/received as soon as the SSPBUF register is loaded with a byte value. If the master is only going to receive, SDO output could be disabled (programmed and used as an input). The SSPSR register will continue to shift in the signal present on the SDI pin at the programmed clock rate.

When initializing SPI Master mode operation, several options need to be specified. This is accomplished by programming the appropriate control bits in the SSPCON and SSPSTAT registers. These control bits allow the following to be specified:

- SCK as clock output

- Idle state of SCK (CKP bit)

- Data input sample phase (SMP bit)

- Output data on rising/falling edge of SCK (CKE bit)

- · Clock bit rate

In Master mode, the SPI clock rate (bit rate) is user selectable to be one of the following:

- Fosc/4 (or TCY)

- Fosc/16 (or 4 TCY)

- Fosc/64 (or 16 TCY)

- (Timer2 output)/2

This allows a maximum data rate of 5 Mbps (at Fosc = 20 MHz).

Figure 17-3 shows the waveforms for Master mode. The clock polarity is selected by appropriately programming the CKP bit of the SSPCON register. When the CKE bit is set, the SDO data is valid before there is a clock edge on SCK. The sample time of the input data is shown based on the state of the SMP bit and can occur at the middle or end of the data output time. The time when the SSPBUF is loaded with the received data is shown.

#### 17.1.1.4 Sleep in Master Mode

In Master mode, all module clocks are halted and the transmission/reception will remain in their current state, paused, until the device wakes from Sleep. After the device wakes up from Sleep, the module will continue to transmit/receive data.

#### REGISTER 18-1: PMCON1: PROGRAM MEMORY CONTROL 1 REGISTER

| R-1      | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/S-0 |

|----------|-----|-----|-----|-----|-----|-----|-------|

| Reserved | —   | —I  | —   | —   | —   | —   | RD    |

| bit 7    |     |     |     |     |     |     | bit 0 |

|          |     |     |     |     |     |     |       |

| Legend:           |                  | S = Setable bit, cleared in ha | ardware            |

|-------------------|------------------|--------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read    | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared           | x = Bit is unknown |

| bit 7 <b>Reserved:</b> Read as '1'. Maintain this bit set. |

|------------------------------------------------------------|

| bit 7 <b>Reserved:</b> Read as '1'. Maintain this bit set. |

bit 6-1 Unimplemented: Read as '0'

bit 0 RD: Read Control bit

1 = Initiates an program memory read (The RD is cleared in hardware; the RD bit can only be set (not cleared) in software).

0 = Does not initiate a program memory read

#### REGISTER 18-2: PMDATH: PROGRAM MEMORY DATA HIGH REGISTER

| U-0      | U-0 | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|----------|-----|-------|-------|-------|-------|-------|-------|

| —        | —   | PMD13 | PMD12 | PMD11 | PMD10 | PMD9  | PMD8  |

| bit 7    |     |       |       |       |       |       | bit 0 |

|          |     |       |       |       |       |       |       |

| l egend. |     |       |       |       |       |       |       |

| Legenu.           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **PMD<13:8>:** The value of the program memory word pointed to by PMADRH and PMADRL after a Program Memory Read command.

### REGISTER 18-3: PMDATL: PROGRAM MEMORY DATA LOW REGISTER

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| PMD7  | PMD6  | PMD5  | PMD4  | PMD3  | PMD2  | PMD1  | PMD0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 7-0 **PMD<7:0>:** The value of the program memory word pointed to by PMADRH and PMADRL after a Program Memory Read command.

## 23.3 DC Characteristics: PIC16(L)F722A/723A-I/E (Power-Down)

| PIC16LF722A/723A<br>PIC16F722A/723A |                         |          |      | rd Operation<br>ng temper                                                                                                       |                | -40°C ≤ | TA ≤ +85° | nerwise stated)<br>C for industrial<br>5°C for extended |

|-------------------------------------|-------------------------|----------|------|---------------------------------------------------------------------------------------------------------------------------------|----------------|---------|-----------|---------------------------------------------------------|

|                                     |                         |          |      | perating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |                |         |           |                                                         |

| Param<br>No.                        | Device Characteristics  | Min.     | Тур† | Max.<br>+85°C                                                                                                                   | Max.<br>+125°C | Units   |           | Conditions                                              |

|                                     | Power-down Base Current | (Ipp)(2) |      |                                                                                                                                 |                |         | VDD       | Note                                                    |

| D020                                | Fower-down base current | (IPD)( / | 0.02 | 0.7                                                                                                                             | 3.9            | μA      | 1.8       | WDT, BOR, FVR, and T1OSC                                |

| 0020                                |                         |          | 0.02 | 1.0                                                                                                                             | 4.3            | μΑ      | 3.0       | disabled, all Peripherals Inactive                      |

| D020                                |                         |          | 4.3  | 10.2                                                                                                                            | 17             | μΑ      | 1.8       | WDT, BOR, FVR, and T1OSC                                |

| 2020                                |                         |          | 5    | 10.5                                                                                                                            | 18             | μΑ      | 3.0       | disabled, all Peripherals Inactive                      |

|                                     |                         |          | 5.5  | 11.8                                                                                                                            | 21             | μA      | 5.0       |                                                         |

| D021                                |                         | _        | 0.5  | 1.7                                                                                                                             | 4.1            | μA      | 1.8       | LPWDT Current (Note 1)                                  |

|                                     |                         | _        | 0.8  | 2.5                                                                                                                             | 4.8            | μA      | 3.0       |                                                         |

| D021                                |                         | _        | 6    | 13.5                                                                                                                            | 16.4           | μA      | 1.8       | LPWDT Current (Note 1)                                  |

|                                     |                         |          | 6.5  | 14.5                                                                                                                            | 16.8           | μA      | 3.0       |                                                         |

|                                     |                         |          | 7.5  | 16                                                                                                                              | 18.7           | μA      | 5.0       |                                                         |

| D021A                               |                         | _        | 8.5  | 14                                                                                                                              | 19             | μΑ      | 1.8       | FVR current (Note 1. Note 3)                            |

|                                     |                         | _        | 8.5  | 14                                                                                                                              | 20             | μA      | 3.0       |                                                         |

| D021A                               |                         | _        | 23   | 44                                                                                                                              | 48             | μA      | 1.8       | FVR current (Note 1, Note 3,                            |

|                                     |                         |          | 25   | 45                                                                                                                              | 55             | μΑ      | 3.0       | Note 5)                                                 |

|                                     |                         |          | 26   | 60                                                                                                                              | 70             | μA      | 5.0       |                                                         |

| D022                                |                         | _        | —    | _                                                                                                                               | _              | μΑ      | 1.8       | BOR Current (Note 1, Note 3)                            |

|                                     |                         | —        | 7.5  | 12                                                                                                                              | 22             | μΑ      | 3.0       |                                                         |

| D022                                |                         | —        | —    | —                                                                                                                               | —              | μA      | 1.8       | BOR Current (Note 1, Note 3, Note 5)                    |

|                                     |                         |          | 23   | 42                                                                                                                              | 49             | μA      | 3.0       |                                                         |

|                                     |                         | —        | 25   | 46                                                                                                                              | 50             | μA      | 5.0       |                                                         |

| D026                                |                         | _        | 0.6  | 2                                                                                                                               |                | μA      | 1.8       | T1OSC Current (Note 1)                                  |

|                                     |                         | _        | 1.8  | 3.0                                                                                                                             | _              | μΑ      | 3.0       |                                                         |

| D026                                |                         |          | 4.5  | 11.1                                                                                                                            | _              | μΑ      | 1.8       | T1OSC Current (Note 1)                                  |

|                                     |                         |          | 6    | 12.5                                                                                                                            | —              | μΑ      | 3.0       | -                                                       |

|                                     |                         | —        | 7    | 13.5                                                                                                                            | —              | μA      | 5.0       |                                                         |

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral ∆ current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD.

3: Fixed Voltage Reference is automatically enabled whenever the BOR is enabled.

4: A/D oscillator source is FRC.

5: 0.1 μF capacitor on VCAP (RA0).

|                 | DC CI | HARACTERISTICS                       |                   | •    | $-40^{\circ}C \le TA$ | ≤ +85°C | otherwise stated)<br>c for industrial<br>C for extended                    |

|-----------------|-------|--------------------------------------|-------------------|------|-----------------------|---------|----------------------------------------------------------------------------|

| Param<br>No.    | Sym.  | Characteristic                       | Min.              | Тур† | Max.                  | Units   | Conditions                                                                 |

|                 | VIL   | Input Low Voltage                    |                   |      |                       |         |                                                                            |

|                 |       | I/O PORT:                            |                   |      |                       |         |                                                                            |

| D030            |       | with TTL buffer                      | —                 | _    | 0.8                   | V       | $4.5V \leq V\text{DD} \leq 5.5V$                                           |

| D030A           |       |                                      | —                 |      | 0.15 Vdd              | V       | $1.8V \le V\text{DD} \le 4.5V$                                             |

| D031            |       | with Schmitt Trigger buffer          | —                 | _    | 0.2 Vdd               | V       | $2.0V \le V\text{DD} \le 5.5V$                                             |

|                 |       | with I <sup>2</sup> C levels         | —                 |      | 0.3 Vdd               | V       |                                                                            |

| D032            |       | MCLR, OSC1 (RC mode) <sup>(1)</sup>  | —                 | _    | 0.2 Vdd               | V       |                                                                            |

| D033A           |       | OSC1 (HS mode)                       |                   | _    | 0.3 Vdd               | V       |                                                                            |

|                 | VIH   | Input High Voltage                   |                   |      |                       |         |                                                                            |

|                 |       | I/O ports:                           |                   | _    |                       |         |                                                                            |

| D040            |       | with TTL buffer                      | 2.0               | _    | _                     | V       | $4.5V \leq V\text{DD} \leq 5.5V$                                           |

| D040A           |       |                                      | 0.25 VDD +<br>0.8 | —    | -                     | V       | $1.8V \leq V\text{DD} \leq 4.5V$                                           |

| D041            |       | with Schmitt Trigger buffer          | 0.8 Vdd           | _    | —                     | V       | $2.0V \le V\text{DD} \le 5.5V$                                             |

|                 |       | with I <sup>2</sup> C levels         | 0.7 Vdd           | _    | —                     | V       |                                                                            |

| D042            |       | MCLR                                 | 0.8 Vdd           |      | _                     | V       |                                                                            |

| D043A           |       | OSC1 (HS mode)                       | 0.7 Vdd           |      | _                     | V       |                                                                            |

| D043B           |       | OSC1 (RC mode)                       | 0.9 Vdd           |      | _                     | V       | (Note 1)                                                                   |

|                 | lı∟   | Input Leakage Current <sup>(2)</sup> |                   |      |                       |         |                                                                            |

| D060            |       | I/O ports                            | —                 | ± 5  | ± 125                 | nA      | $Vss \le VPIN \le VDD$ , Pin at high-impedance, 85°C                       |

|                 |       |                                      |                   | ± 5  | ± 1000                | nA      | 125°C                                                                      |

| D061            |       | MCLR <sup>(3)</sup>                  | —                 | ± 50 | ± 200                 | nA      | $Vss \le Vpin \le Vdd, 85^{\circ}C$                                        |

|                 | IPUR  | PORTB Weak Pull-up Current           |                   |      | _                     | _       |                                                                            |

| D070*           |       |                                      | 25                | 100  | 200                   |         | VDD = 3.3V, VPIN = VSS                                                     |

|                 |       |                                      | 25                | 140  | 300                   | μΑ      | VDD = 5.0V, VPIN = VSS                                                     |

|                 | Vol   | Output Low Voltage <sup>(4)</sup>    | г – т             |      | 1                     | 1       |                                                                            |

| D080            |       | I/O ports                            | _                 | _    | 0.6                   | v       | IOL = 8 mA, VDD = 5V<br>IOL = 6 mA, VDD = 3.3V<br>IOL = 1.8 mA, VDD = 1.8V |

|                 | Voh   | Output High Voltage <sup>(4)</sup>   |                   |      |                       |         |                                                                            |

| D090            |       | I/O ports                            | Vdd - 0.7         | _    | _                     | V       | IOH = 3.5 mA, VDD = 5V<br>IOH = 3 mA, VDD = 3.3V<br>IOH = 1 mA, VDD = 1.8V |

|                 |       | Capacitive Loading Specs on          | Output Pins       |      | 1                     | 1       | I , -                                                                      |

| Ì               | 1     | OSC2 pin                             | _                 | _    | 15                    | pF      | In XT, HS and LP modes when                                                |

| D101*           | COSC2 | 0002 pm                              |                   |      |                       |         | external clock is used to drive OSC1                                       |

| D101*<br>D101A* | COSC2 | All I/O pins                         | _                 | _    | 50                    | pF      |                                                                            |

## 23.4 DC Characteristics: PIC16(L)F722A/723A-I/E

**Legend:** TBD = To Be Determined

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

**2:** Negative current is defined as current sourced by the pin.

3: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

**4:** Including OSC2 in CLKOUT mode.

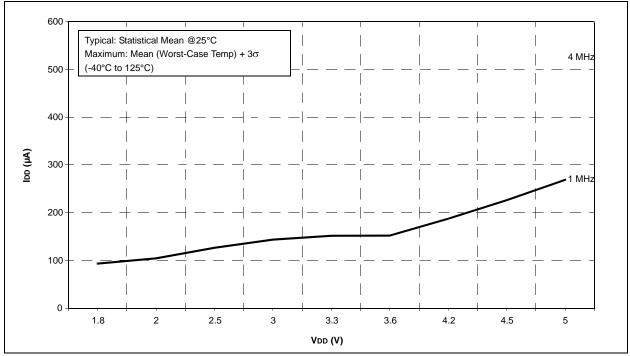

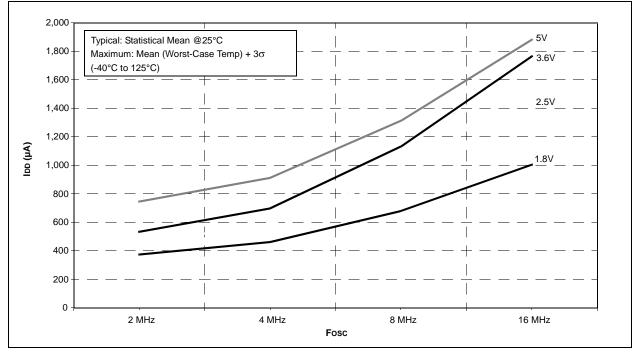

#### FIGURE 24-4: PIC16LF722A/723A TYPICAL IDD vs. Fosc OVER VDD, EC MODE

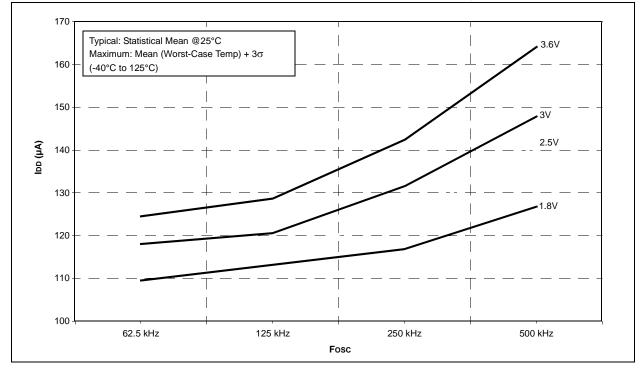

#### FIGURE 24-20: PIC16LF722A/723A MAXIMUM IDD vs. Fosc OVER VDD, INTOSC MODE

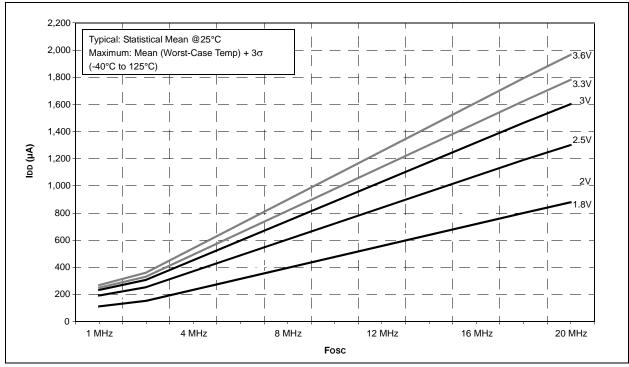

FIGURE 24-21: PIC16F722A/723A MAXIMUM IDD vs. Fosc OVER VDD, INTOSC MODE, VCAP = 0.1µF

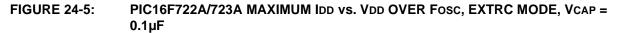

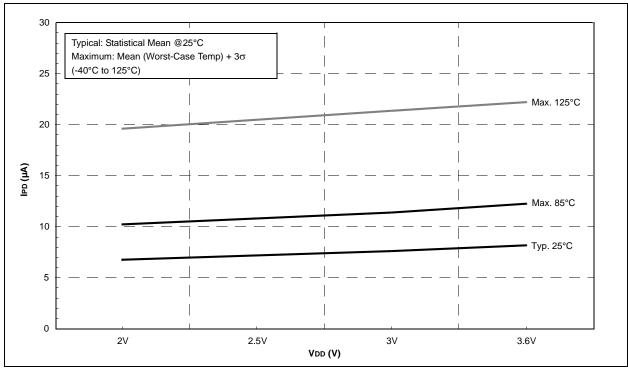

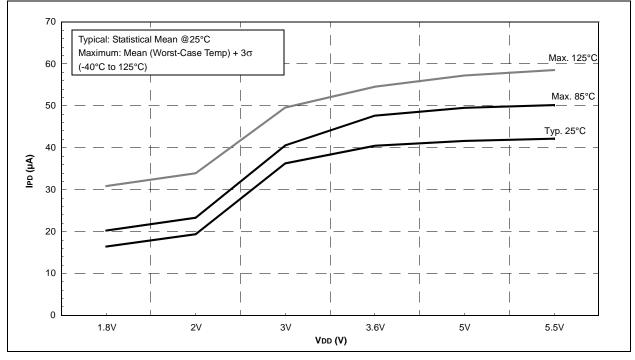

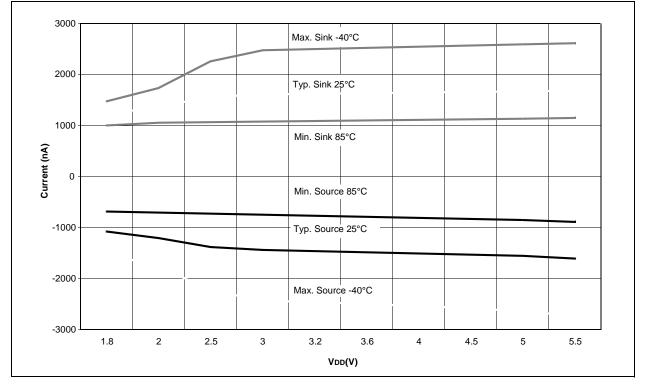

FIGURE 24-34: PIC16LF722A/723A BOR IPD vs. VDD

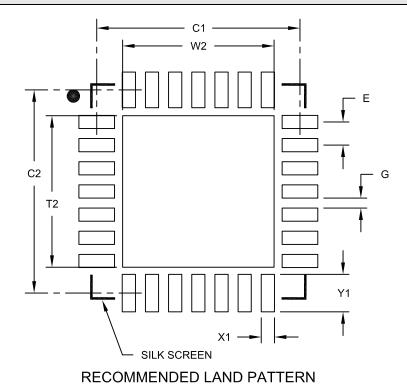

## 28-Lead Plastic Quad Flat, No Lead Package (ML) – 6x6 mm Body [QFN] with 0.55 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                      |    | MILLIMETERS |          |      |

|----------------------------|----|-------------|----------|------|

| Dimension Limits           |    | MIN         | NOM      | MAX  |

| Contact Pitch              | E  |             | 0.65 BSC |      |

| Optional Center Pad Width  | W2 |             |          | 4.25 |

| Optional Center Pad Length | T2 |             |          | 4.25 |

| Contact Pad Spacing        | C1 |             | 5.70     |      |

| Contact Pad Spacing        | C2 |             | 5.70     |      |

| Contact Pad Width (X28)    | X1 |             |          | 0.37 |

| Contact Pad Length (X28)   | Y1 |             |          | 1.00 |

| Distance Between Pads      | G  | 0.20        |          |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2105A

## **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.<br>Device Tap   | [X] <sup>(1)</sup> X     XXX       I     I     I       De and Reel Temperature     Package     Pattern       Option     Range | Examples:<br>a) PIC16F722A-E/SP 301 = Extended<br>Temp., SPDIP package, QTP pattern<br>#301                                                                                                                                                                                   |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device:                  | PIC16F722A, PIC16LF722A<br>PIC16F723A, PIC16LF723A                                                                            | <ul> <li>b) PIC16F722A-I/SO = Industrial Temp.,<br/>SOIC package</li> </ul>                                                                                                                                                                                                   |

| Tape and Reel<br>Option: | Blank= Standard packaging (tube or tray)<br>T = Tape and Reel <sup>(1)</sup>                                                  |                                                                                                                                                                                                                                                                               |

| Temperature<br>Range:    | I = $-40^{\circ}$ C to+85°C (Industrial)<br>E = $-40^{\circ}$ C to+125°C (Extended)                                           |                                                                                                                                                                                                                                                                               |

| Package:                 | MV = UQFN<br>ML = QFN<br>SO = SOIC<br>SP = SPDIP<br>SS = SSOP                                                                 | Note 1: Tape and Reel identifier only<br>appears in the catalog part number<br>description. This identifier is used for<br>ordering purposes and is not printed<br>on the device package. Check with<br>your Microchip Sales Office for<br>package availability with the Tape |

| Pattern:                 | 3-Digit Pattern Code for QTP (blank otherwise)                                                                                | and Reel option.                                                                                                                                                                                                                                                              |