Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                       |

|--------------------------------|-----------------------------------------------------------------------|

| Product Status                 | Obsolete                                                              |

| Number of LABs/CLBs            | -                                                                     |

| Number of Logic Elements/Cells | 6400                                                                  |

| Total RAM Bits                 | -                                                                     |

| Number of I/O                  | 120                                                                   |

| Number of Gates                | 30000                                                                 |

| Voltage - Supply               | 4.75V ~ 5.25V                                                         |

| Mounting Type                  | Surface Mount                                                         |

| Operating Temperature          | 0°C ~ 70°C (TC)                                                       |

| Package / Case                 | 144-LQFP                                                              |

| Supplier Device Package        | 144-LQFP (20x20)                                                      |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microchip-technology/at6010a-4ac |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Devices range in size from 4,000 to 30,000 usable gates, and 1024 to 6400 registers. Pin locations are consistent throughout the AT6000 Series for easy design migration. High-I/O versions are available for the lower gate count devices.

AT6000 Series FPGAs utilize a reliable 0.6  $\mu m$  single-poly, double-metal CMOS process and are 100% factory-tested.

Atmel's PC- and workstation-based Integrated Development System is used to create AT6000 Series designs. Multiple design entry methods are supported.

The Atmel architecture was developed to provide the highest levels of performance, functional density and design flexibility in an FPGA. The cells in the Atmel array are small, very efficient and contain the most important and most commonly used logic and wiring functions. The cell's small size leads to arrays with large numbers of cells, greatly multiplying the functionality in each cell. A simple, high-speed busing network provides fast, efficient communication over medium and long distances.

### The Symmetrical Array

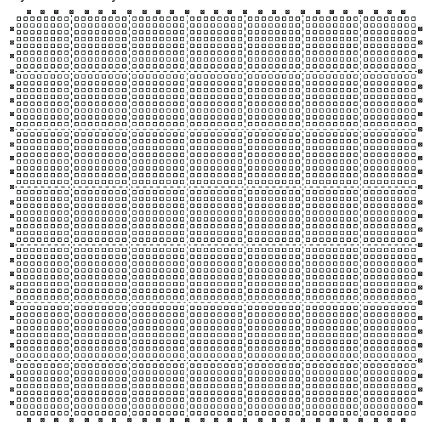

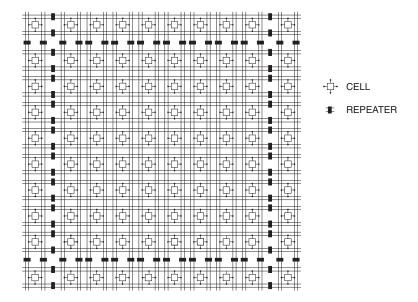

At the heart of the Atmel architecture is a symmetrical array of identical cells (Figure 1). The array is continuous and completely uninterrupted from one edge to the other, except for bus *repeaters* spaced every eight cells (Figure 2).

In addition to logic and storage, cells can also be used as wires to connect functions together over short distances and are useful for routing in tight spaces.

### The Busing Network

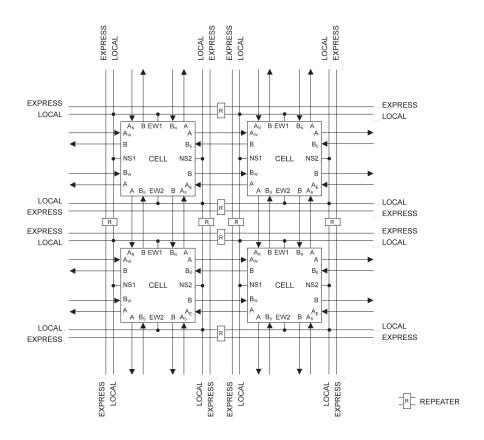

There are two kinds of buses: local and express (see Figures 2 and 3).

Local buses are the link between the array of cells and the busing network. There are two local buses – North-South 1 and 2 (NS1 and NS2) – for every column of cells, and two local buses – East-West 1 and 2 (EW1 and EW2) – for every row of cells. In a sector (an 8 x 8 array of cells enclosed by repeaters) each local bus is connected to every cell in its column or row, thus providing every cell in the array with read/write access to two North-South and two East-West buses.

Figure 1. Symmetrical Array Surrounded by I/O

Figure 2. Busing Network (one sector)

Figure 3. Cell-to-cell and Bus-to-bus Connections

Each cell, in addition, provides the ability to route a signal on a 90° turn between the NS1 bus and EW1 bus and between the NS2 bus and EW2 bus.

Express buses are not connected directly to cells, and thus provide higher speeds. They are the fastest way to cover long, straight-line distances within the array.

Each express bus is paired with a local bus, so there are two express buses for every column and two express buses for every row of cells.

Connective units, called repeaters, spaced every eight cells, divide each bus, both local and express, into segments spanning eight cells. Repeaters are aligned in rows and columns thereby partitioning the array into 8 x 8 sectors of cells. Each repeater is associated with a local/express pair, and on each side of the repeater are connections to a local-bus segment and an express-bus segment. The repeater can be programmed to provide any one of twenty-one connecting functions. These functions are symmetric with respect to both the two repeater sides and the two types of buses.

Among the functions provided are the ability to:

- Isolate bus segments from one another

- · Connect two local-bus segments

- Connect two express-bus segments

- Implement a local/express transfer

In all of these cases, each connection provides signal regeneration and is thus unidirectional. For bidirectional connections, the basic repeater function for the NS2 and EW2 repeaters is augmented with a special programmable connection allowing bidirectional communication between local-bus segments. This option is primarily used to implement long, tristate buses.

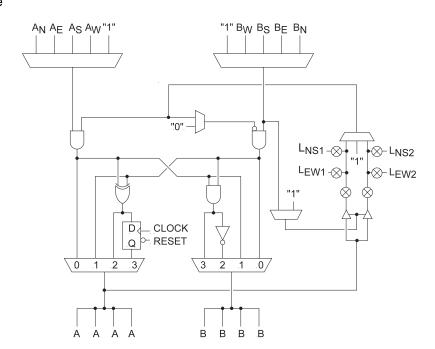

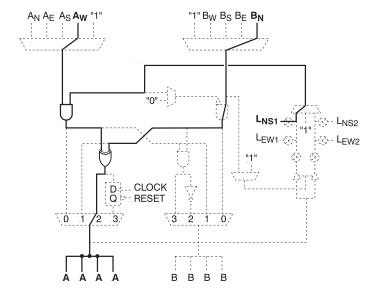

#### The Cell Structure

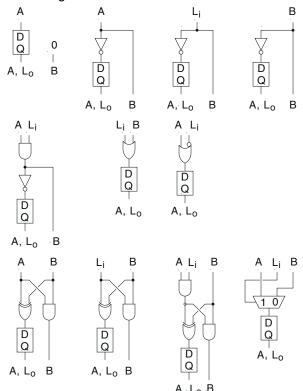

The Atmel cell (Figure 4) is simple and small and yet can be programmed to perform all the logic and wiring functions needed to implement any digital circuit. Its four sides are functionally identical, so each cell is completely symmetrical.

Read/write access to the four local buses – NS1, EW1, NS2 and EW2 – is controlled, in part, by four bidirectional pass gates connected directly to the buses. To read a local bus, the pass gate for that bus is turned on and the three-input multiplexer is set accordingly. To write to a local bus, the pass gate for that bus and the pass gate for the associated tristate driver are both turned on. The two-input multiplexer supplying the control signal to the drivers permits either: (1) active drive, or (2) dynamic tristating controlled by the B input. Turning between  $L_{\rm NS1}$  and  $L_{\rm EW1}$  or between  $L_{\rm NS2}$  and  $L_{\rm EW2}$  is accomplished by turning on the two associated pass gates. The operations of reading, writing and turning are subject to the restriction that each bus can be involved in no more than a **single** operation.

Figure 4. Cell Structure

## AT6000(LV) Series

In addition to the four local-bus connections, a cell receives two inputs and provides two outputs to each of its North (N), South (S), East (E) and West (W) neighbors. These inputs and outputs are divided into two classes: "A" and "B". There is an A input and a B input from each neighboring cell and an A output and a B output driving all four neighbors. Between cells, an A output is always connected to an A input and a B output to a B input.

Within the cell, the four A inputs and the four B inputs enter two separate, independently configurable multiplexers. Cell flexibility is enhanced by allowing each multiplexer to select also the logical constant "1". The two multiplexer outputs enter the two upstream AND gates.

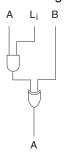

Downstream from these two AND gates are an Exclusive-OR (XOR) gate, a register, an AND gate, an inverter and two four-input multiplexers producing the A and B outputs. These multiplexers are controlled in tandem (unlike the A and B input multiplexers) and determine the function of the cell.

- In State 0 corresponding to the "0" inputs of the multiplexers – the output of the left-hand upstream AND gate is connected to the cell's A output, and the output of the right-hand upstream AND gate is connected to the cell's B output.

- In State 1 corresponding to the "1" inputs of the multiplexers – the output of the left-hand upstream AND gate is connected to the cell's B output, the output of the right-hand upstream AND gate is connected to the cell's A output.

- In State 2 corresponding to the "2" inputs of the multiplexers – the XOR of the outputs from the two upstream AND gates is provided to the cell's A output, while the NAND of these two outputs is provided to the cell's B output.

In State 3 – corresponding to the "3" inputs of the

multiplexers – the XOR function of State 2 is provided to

the D input of a D-type flip-flop, the Q output of which is

connected to the cell's A output. Clock and

asynchronous reset signals are supplied externally as

described later. The AND of the outputs from the two

upstream AND gates is provided to the cell's B output.

### **Logic States**

The Atmel cell implements a rich and powerful set of logic functions, stemming from 44 logical cell states which permutate into 72 physical states. Some states use both A and B inputs. Other states are created by selecting the "1" input on either or both of the input multiplexers.

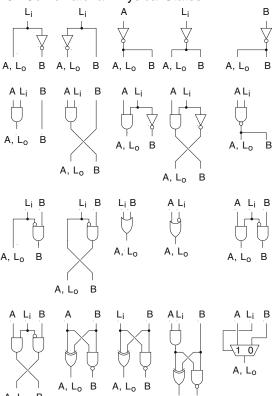

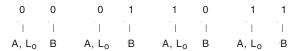

There are 28 combinatorial primitives created from the cell's tristate capabilities and the 20 physical states represented in Figure 5. Five logical primitives are derived from the physical constants shown in Figure 7. More complex functions are created by using cells in combination.

A two-input AND feeding an XOR (Figure 8) is produced using a single cell (Figure 9). A two-to-one multiplexer selects the logical constant "0" and feeds it to the right-hand AND gate. The AND gate acts as a feed-through, letting the B input pass through to the XOR. The three-to-one multiplexer on the right side selects the local-bus input, LNS1, and passes it to the left-hand AND gate. The A and LNS1 signals are the inputs to the AND gate. The output of the AND gate feeds into the XOR, producing the logic state (A•L) XOR B.

Figure 5. Combinatorial Physical States

Figure 7. Physical Constants

Figure 8. Two-input AND Feeding XOR

Figure 6. Register States

Figure 9. Cell Configuration (A•L) XOR B

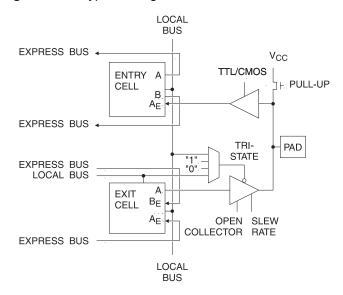

Figure 11. A-type I/O Logic

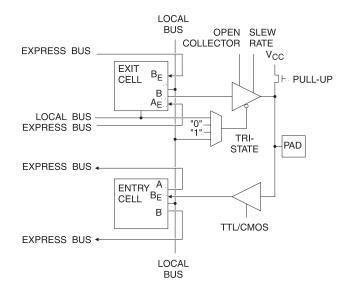

Figure 12. B-type I/O Logic

#### **TTL/CMOS Inputs**

A user-configurable bit determines the threshold level – TTL or CMOS – of the input buffer.

#### **Open Collector/Tristate Outputs**

A user-configurable bit which enables or disables the active pull-up of the output device.

#### **Slew Rate Control**

A user-configurable bit controls the slew rate – fast or slow – of the output buffer. A slow slew rate, which reduces noise and ground bounce, is recommended for outputs that are not speed-critical. Fast and slow slew rates have the same DC-current sinking capabilities, but the rate at which each allows the output devices to reach full drive differs.

#### Pull-up

A user-configurable bit controls the pull-up transistor in the I/O pin. It's primary function is to provide a logical "1" to unused input pins. When on, it is approximately equivalent to a 25K resistor to  $V_{\rm CC}$ .

#### **Enable Select**

User-configurable bits determine the output-enable for the output driver. The output driver can be static – always on or always off – or dynamically controlled by a signal generated in the array. Four options are available from the array: (1) the control is low and always driving; (2) the control is high and never driving; (3) the control is connected to a vertical local bus associated with the output cell; or (4) the control is connected to a horizontal local bus associated with the output cell. On power-up, the user I/Os are configured as inputs with pull-up resistors.

In addition to the functionality provided by the I/O logic, the entrance and exit cells provide the ability to register both inputs and outputs. Also, these perimeter cells (unlike interior cells) are connected directly to express buses: the edge-facing A and B outputs of the entrance cell are connected to express buses, as are the edge-facing A and B inputs of the exit cell. These buses are perpendicular to the edge, and provide a rapid means of bringing I/O signals to and from the array interior and the opposite edge of the chip.

### **Chip Configuration**

The Integrated Development System generates the SRAM bit pattern required to configure a AT6000 Series device. A PC parallel port, microprocessor, EPROM or serial configuration memory can be used to download configuration patterns.

Users select from several configuration modes. Many factors, including board area, configuration speed and the number of designs implemented in parallel can influence the user's final choice.

Configuration is controlled by dedicated configuration pins and dual-function pins that double as I/O pins when the device is in operation. The number of dual-function pins required for each mode varies.

## **Pinout Assignment (Continued)**

|                       |                       |                | Left Side      | (Top to Bo                | ttom)       |                            |             |                            |                            |                            |

|-----------------------|-----------------------|----------------|----------------|---------------------------|-------------|----------------------------|-------------|----------------------------|----------------------------|----------------------------|

| AT6002 <sup>(3)</sup> | AT6003 <sup>(3)</sup> | AT6005         | AT6010         | 84 <sup>(3)</sup><br>PLCC | 100<br>VQFP | 132 <sup>(3)</sup><br>PQFP | 144<br>TQFP | 180 <sup>(3)</sup><br>CPGA | 208 <sup>(3)</sup><br>PQFP | 240 <sup>(3)</sup><br>PQFP |

| I/O10(A) or D5        | I/O12(A) or D5        | I/O11(A) or D5 | I/O22(A) or D5 | 24                        | 15          | 36                         | 21          | K4                         | 30                         | 34                         |

| VDD                   | VDD                   | VDD            | VDD            | 25                        | 16          | 37                         | 22          | PWR <sup>(1</sup>          | 31                         | 35                         |

| vcc                   | vcc                   | vcc            | vcc            | 26                        | 17          | 38                         | 23          | PWR <sup>(1</sup>          | 32                         | 36                         |

| I/O9(B)               | I/O11(B)              | I/O10(A)       | I/O21(A)       | -                         | -           | 39                         | 24          | J3                         | 33                         | 37                         |

| -                     | -                     | -              | I/O20(B)       | -                         | -           | -                          | -           | -                          | 34                         | 38                         |

| I/O8(A) or D4         | I/O10(A) or D4        | I/O9(A) or D4  | I/O19(A) or D4 | 27                        | 18          | 40                         | 25          | K3                         | 35                         | 39                         |

| I/O7(B)               | I/O9(B)               | I/O8(A)        | I/O18(A)       | -                         | 19          | 41                         | 26          | L3                         | 36                         | 40                         |

| -                     | -                     | -              | I/O17(A)       | -                         | -           | -                          | -           | МЗ                         | 37                         | 41                         |

| -                     | -                     | -              | I/O16(B)       | -                         | -           | -                          | -           | -                          | -                          | 42                         |

| I/O6(A) or D3         | I/O8(A) or D3         | I/O7(A) or D3  | I/O15(A) or D3 | 28                        | 20          | 42                         | 27          | N3                         | 38                         | 43                         |

| -                     | I/O7(B)               | I/O6(A)        | I/O14(A)       | -                         | -           | 43                         | 28          | J2                         | 39                         | 44                         |

| -                     | -                     | -              | I/O13(A)       | -                         | -           | -                          | -           | K2                         | 40                         | 45                         |

| GND                   | GND                   | GND            | GND            | -                         | -           | 44                         | 29          | GND <sup>(2)</sup>         | 41                         | 46                         |

| -                     | -                     | -              | vss            | -                         | -           | -                          | -           | GND <sup>(2)</sup>         | 42                         | 47                         |

| -                     | -                     | -              | I/O12(B)       | -                         | -           | -                          | -           | -                          | -                          | 48                         |

| I/O5(A) or D2         | I/O6(A) or D2         | I/O5(A) or D2  | I/O11(A) or D2 | 29                        | 21          | 45                         | 30          | M2                         | 43                         | 49                         |

| I/O4(B)               | I/O5(B)               | I/O4(A)        | I/O10(A)       | -                         | 22          | 46                         | 31          | N2                         | 44                         | 50                         |

| -                     | -                     | -              | I/O9(A)        | -                         | -           | -                          | -           | P2                         | 45                         | 51                         |

| -                     | -                     | -              | I/O8(B)        | -                         | -           | -                          | -           | -                          | -                          | 52                         |

| I/O3(A) or D1         | I/O4(A) or D1         | I/O3(A) or D1  | I/O7(A) or D1  | 30                        | 23          | 47                         | 32          | J1                         | 46                         | 53                         |

| I/O2(B)               | I/O3(A)               | I/O2(A)        | I/O6(A)        | -                         | -           | 48                         | 33          | K1                         | 47                         | 54                         |

| -                     | -                     | -              | I/O5(A)        | -                         | -           | -                          | -           | L1                         | 48                         | 55                         |

| -                     | -                     | -              | I/O4(B)        | -                         | -           | -                          | -           | -                          | -                          | 56                         |

| -                     | I/O2(B)               | -              | I/O3(A)        | -                         | -           | -                          | 34          | M1                         | 49                         | 57                         |

| I/O1(A) or D0         | I/O1(A) or D0         | I/O1(A) or D0  | I/O2(A) or D0  | 31                        | 24          | 49                         | 35          | N1                         | 50                         | 58                         |

| -                     | -                     | -              | I/O1(A)        | -                         | -           | -                          | -           | P1                         | 51                         | 59                         |

| CCLK                  | CCLK                  | CCLK           | CCLK           | 32                        | 25          | 50                         | 36          | R1                         | 52                         | 60                         |

Notes: 1. PWR = Pins connected to power plane = F1, E4/E5, L2, R4, K15, L12, E14, A12.

3. Obsolete. Not recommended for new design.

<sup>2.</sup> GND = Pins connected to ground plane = L4, M4, N9, N10, E12, D12, C7, C6.

## **Pinout Assignment**

|                       |                       |                       | Bottom S              | ide (Left to              | Right)      |                            |             |                            |                            |                            |

|-----------------------|-----------------------|-----------------------|-----------------------|---------------------------|-------------|----------------------------|-------------|----------------------------|----------------------------|----------------------------|

| AT6002 <sup>(3)</sup> | AT6003 <sup>(3)</sup> | AT6005                | AT6010                | 84 <sup>(3)</sup><br>PLCC | 100<br>VQFP | 132 <sup>(3)</sup><br>PQFP | 144<br>TQFP | 180 <sup>(3)</sup><br>CPGA | 208 <sup>(3)</sup><br>PQFP | 240 <sup>(3)</sup><br>PQFP |

| CON                   | CON                   | CON                   | CON                   | 33                        | 26          | 51                         | 37          | M5                         | 53                         | 61                         |

| -                     | -                     | -                     | I/O204(A)             | -                         | -           | -                          | -           | M6                         | 54                         | 62                         |

| I/O96(A)              | I/O120(A)             | I/O108(A)             | I/O203(A)             | 34                        | 27          | 52                         | 38          | M7                         | 55                         | 63                         |

| -                     | I/O119(B)             | -                     | I/O202(A)             | -                         | -           | -                          | 39          | R2                         | 56                         | 64                         |

| -                     | -                     | -                     | I/O201(B)             | -                         | -           | -                          | -           | -                          | -                          | 65                         |

| -                     | -                     | -                     | vcc                   | -                         | -           | -                          | -           | PWR <sup>(1)</sup>         | 57                         | 66                         |

| -                     | -                     | -                     | I/O200(A)             | -                         | -           | -                          | -           | R3                         | 58                         | 67                         |

| -                     | -                     | -                     | GND                   | -                         | -           | -                          | -           | GND <sup>(2)</sup>         | 59                         | 68                         |

| -                     | I/O118(A)             | I/O107(A)             | I/O199(A)             | -                         | -           | 53                         | 40          | R5                         | 60                         | 69                         |

| I/O95(A) or<br>CSOUT  | I/O117(A) or<br>CSOUT | I/O106(A) or<br>CSOUT | I/O198(A) or<br>CSOUT | 35                        | 28          | 54                         | 41          | R6                         | 61                         | 70                         |

| -                     | -                     | -                     | I/O197(B)             | -                         | -           | -                          | -           | -                          | -                          | 71                         |

| -                     | -                     | -                     | I/O196(A)             | -                         | -           | -                          | -           | R7                         | 62                         | 72                         |

| I/O94(B)              | I/O116(A)             | I/O105(A)             | I/O195(A)             | -                         | -           | 55                         | 42          | P3                         | 63                         | 73                         |

| I/O93(A)              | I/O115(A)             | I/O104(A)             | I/O194(A)             | 36                        | 29          | 56                         | 43          | P4                         | 64                         | 74                         |

| -                     | -                     | -                     | I/O193(B)             | -                         | -           | -                          | -           | -                          | -                          | 75                         |

| -                     | -                     | -                     | I/O192(A)             | -                         | -           | -                          | -           | P5                         | 65                         | 76                         |

| I/O92(B)              | I/O114(B)             | I/O103(A)             | I/O191(A)             | -                         | 30          | 57                         | 44          | P6                         | 66                         | 77                         |

| I/O91(A) or<br>CHECK  | I/O113(A) or<br>CHECK | I/O102(A) or<br>CHECK | I/O190(A) or<br>CHECK | 37                        | 31          | 58                         | 45          | P7                         | 67                         | 78                         |

| -                     | -                     | -                     | I/O189(B)             | -                         | -           | -                          | -           | -                          | -                          | 79                         |

| I/O90(B)              | I/O112(B)             | I/O101(A)             | I/O188(A)             | -                         | -           | 59                         | 46          | N4                         | 68                         | 80                         |

| I/O89(A) or<br>ERR    | I/O111(A) or<br>ERR   | I/O100(A) or<br>ERR   | I/O187(A) or ERR      | 38                        | 32          | 60                         | 47          | N5                         | 69                         | 81                         |

| I/O88(B)              | I/O110(B)             | I/O99(A)              | I/O186(A)             | -                         | 33          | 61                         | 48          | N6                         | 70                         | 82                         |

| -                     | -                     | -                     | I/O185(B)             | -                         | -           | -                          | -           | -                          | 71                         | 83                         |

| I/O87(A)              | I/O109(A)             | I/O98(A)              | I/O184(A)             | 39                        | 34          | 62                         | 49          | N7                         | 72                         | 84                         |

| -                     | I/O108(B)             | I/O97(A)              | I/O183(A)             | -                         | -           | 63                         | 50          | M8                         | 73                         | 85                         |

| GND                   | GND                   | GND                   | GND                   | 40                        | 35          | 64                         | 51          | GND <sup>(2)</sup>         | 74                         | 86                         |

| I/O86(A)              | I/O107(A)             | I/O96(A)              | I/O182(A)             | 41                        | 36          | 65                         | 52          | M9                         | 75                         | 87                         |

| -                     | -                     | -                     | I/O181(B)             | -                         | -           | -                          | -           | -                          | 76                         | 88                         |

| -                     | I/O106(B)             | -                     | I/O180(A)             | -                         | -           | -                          | 53          | M10                        | 77                         | 89                         |

| I/O85(A)              | I/O105(A)             | I/O95(A)              | I/O179(A)             | 42                        | 37          | 66                         | 54          | M11                        | 78                         | 90                         |

| CS                    | CS                    | CS                    | CS                    | 43                        | 38          | 67                         | 55          | L8                         | 79                         | 91                         |

| I/O84(B)              | I/O104(A)             | I/O94(A)              | I/O178(A)             | 44                        | 39          | 68                         | 56          | M12                        | 80                         | 92                         |

Notes: 1. PWR = Pins connected to power plane = F1, E4/E5, L2, R4, K15, L12, E14, A12.

<sup>3.</sup> Obsolete. Not recommended for new design.

<sup>2.</sup> GND = Pins connected to ground plane = L4, M4, N9, N10, E12, D12, C7, C6.

## **Pinout Assignment**

|                       |                       |          | Right Sid | le (Bottom to             | о Тор)      |                            |             |                            |                            |                            |

|-----------------------|-----------------------|----------|-----------|---------------------------|-------------|----------------------------|-------------|----------------------------|----------------------------|----------------------------|

| AT6002 <sup>(5)</sup> | AT6003 <sup>(5)</sup> | AT6005   | AT6010    | 84 <sup>(5)</sup><br>PLCC | 100<br>VQFP | 132 <sup>(5)</sup><br>PQFP | 144<br>TQFP | 180 <sup>(5)</sup><br>CPGA | 208 <sup>(5)</sup><br>PQFP | 240 <sup>(5)</sup><br>PQFP |

| -                     | -                     | -        | I/O153(A) | -                         | -           | -                          | -           | P15                        | 105                        | 121                        |

| I/O72(A)              | I/O90(A)              | I/O81(A) | I/O152(A) | 54                        | 51          | 84                         | 73          | N15                        | 106                        | 122                        |

| -                     | I/O89(B)              | I/O80(A) | I/O151(A) | -                         | -           | 85 <sup>(3)</sup>          | 74          | M15                        | 107                        | 123                        |

| -                     | -                     | -        | I/O150(B) | -                         | -           | -                          | -           | -                          | -                          | 124                        |

| -                     | -                     | -        | vcc       | -                         | -           | -                          | -           | PWR <sup>(1</sup>          | 108                        | 125                        |

| -                     | -                     | -        | I/O149(A) | -                         | -           | -                          | -           | L15                        | 109                        | 126                        |

| -                     | -                     | -        | GND       | -                         | -           | -                          | -           | GND <sup>(2)</sup>         | 110                        | 127                        |

| -                     | I/O88(A)              | -        | I/O148(A) | -                         | -           | 85 <sup>(4)</sup>          | 75          | J15                        | 111                        | 128                        |

| I/O71(A)              | I/O87(A)              | I/O79(A) | I/O147(A) | 55                        | 52          | 86                         | 76          | H15                        | 112                        | 129                        |

| -                     | -                     | -        | I/O146(B) | -                         | -           | -                          | -           | -                          | -                          | 130                        |

| -                     | -                     | -        | I/O145(A) | -                         | -           | -                          | -           | N14                        | 113                        | 131                        |

| I/O70(B)              | I/O86(A)              | I/O78(A) | I/O144(A) | -                         | -           | 87                         | 77          | M14                        | 114                        | 132                        |

| I/O69(A)              | I/O85(A)              | I/O77(A) | I/O143(A) | 56                        | 53          | 88                         | 78          | L14                        | 115                        | 133                        |

| -                     | -                     | -        | I/O142(B) | -                         | -           | -                          | -           | -                          | -                          | 134                        |

| -                     | -                     | -        | I/O141(A) | -                         | -           | -                          | -           | K14                        | 116                        | 135                        |

| I/O68(B)              | I/O84(B)              | I/O76(A) | I/O140(A) | -                         | 54          | 89                         | 79          | J14                        | 117                        | 136                        |

| I/O67(A)              | I/O83(A)              | I/O75(A) | I/O139(A) | 57                        | 55          | 90                         | 80          | H14                        | 118                        | 137                        |

| -                     | -                     | -        | I/O138B   | -                         | -           | -                          | -           | -                          | -                          | 138                        |

| I/O66(B)              | I/O82(B)              | I/O74(A) | I/O137(A) | -                         | -           | 91                         | 81          | M13                        | 119                        | 139                        |

| I/O65(A)              | I/O81(A)              | I/O73(A) | I/O136(A) | 58                        | 56          | 92                         | 82          | L13                        | 120                        | 140                        |

| I/O64(B)              | I/O80(B)              | I/O72(A) | I/O135(A) | -                         | 57          | 93                         | 83          | K13                        | 121                        | 141                        |

| -                     | -                     | -        | I/O134(B) | -                         | -           | -                          | -           | -                          | 122                        | 142                        |

| I/O63(A)              | I/O79(A)              | I/O71(A  | I/O133(A) | 59                        | 58          | 94                         | 84          | J13                        | 123                        | 143                        |

| -                     | I/O78(B)              | I/O70(A) | I/O132(A) | -                         | -           | 95                         | 85          | H13                        | 124                        | 144                        |

| GND                   | GND                   | GND      | GND       | 60                        | 59          | 96                         | 86          | GND <sup>(2)</sup>         | 125                        | 145                        |

| VSS                   | VSS                   | VSS      | VSS       | 61                        | 60          | 97                         | 87          | GND <sup>(2)</sup>         | 126                        | 146                        |

| I/O62(A)              | I/O77(A)              | I/O69(A) | I/O131(A) | 62                        | 61          | 98                         | 88          | K12                        | 127                        | 147                        |

| -                     | -                     | -        | I/O130(B) | -                         | -           | -                          | -           | -                          | 128                        | 148                        |

| -                     | I/O76(B)              | -        | I/O129(A) | -                         | -           | -                          | 89          | J12                        | 129                        | 149                        |

| I/O61(A)              | I/O75(A)              | I/O68(A) | I/O128(A) | 63                        | 62          | 99                         | 90          | H12                        | 130                        | 150                        |

| I/O60(B)              | I/O74(A)              | I/O67(A) | I/O127(A) | 64                        | 63          | 100                        | 91          | H11                        | 131                        | 151                        |

| -                     | -                     | -        | I/O126(B) | -                         | -           | -                          | -           | -                          | 132                        | 152                        |

Notes: 1. PWR = Pins connected to power plane = F1, E4/E5, L2, R4, K15, L12, E14, A12.

5. Obsolete. Not recommended for new design.

<sup>2.</sup> GND = Pins connected to ground plane = L4, M4, N9, N10, E12, D12, C7, C6.

<sup>3. 85 =</sup> Pin 85 on AT6005.

<sup>4. 85 =</sup> Pin 85 on AT6003 and AT6010.

## **Pinout Assignment (Continued)**

|                       |                       |                    | Top Side           | e (Right to               | Left)       |                            |             |                            |                            |                            |

|-----------------------|-----------------------|--------------------|--------------------|---------------------------|-------------|----------------------------|-------------|----------------------------|----------------------------|----------------------------|

| AT6002 <sup>(3)</sup> | AT6003 <sup>(3)</sup> | AT6005             | AT6010             | 84 <sup>(3)</sup><br>PLCC | 100<br>VQFP | 132 <sup>(3)</sup><br>PQFP | 144<br>TQFP | 180 <sup>(3)</sup><br>CPGA | 208 <sup>(3)</sup><br>PQFP | 240 <sup>(3)</sup><br>PQFP |

| -                     | -                     | -                  | I/O75(B)           | -                         | -           | -                          | -           | -                          | 185                        | 213                        |

| I/O35(A) or<br>A14    | I/O43(A) or<br>A14    | I/O39(A) or<br>A14 | I/O74(A) or<br>A14 | 3                         | 90          | 3                          | 129         | C8                         | 186                        | 214                        |

| -                     | -                     | -                  | VDD                | -                         | -           | -                          | -           | PWR <sup>(1</sup>          | 187                        | 215                        |

| vcc                   | vcc                   | vcc                | vcc                | 4                         | 91          | 4                          | 130         | PWR <sup>(1</sup>          | 188                        | 216                        |

| I/O34(A) or<br>A13    | I/O42(A) or<br>A13    | I/O38(A) or<br>A13 | I/O73(A) or<br>A13 | 5                         | 92          | 5                          | 131         | C5                         | 189                        | 217                        |

| I/O33(B)              | I/O41(B)              | I/O37(A)           | I/O72(A)           | -                         | -           | 6                          | 132         | C4                         | 190                        | 218                        |

| -                     | -                     | -                  | I/O71(B)           | -                         | -           | -                          | -           | -                          | 191                        | 219                        |

| I/O32(A) or<br>A12    | I/O40(A) or<br>A12    | I/O36(A) or<br>A12 | I/O70(A) or<br>A12 | 6                         | 93          | 7                          | 133         | С3                         | 192                        | 220                        |

| I/O31(B)              | I/O39(B)              | I/O35(A)           | I/O69(A)           | -                         | 94          | 8                          | 134         | B8                         | 193                        | 221                        |

| -                     | -                     | -                  | I/O68(A)           | -                         | -           | -                          | -           | В7                         | 194                        | 222                        |

| -                     | -                     | -                  | I/O67(B)           | -                         | -           | -                          | -           | -                          | -                          | 223                        |

| I/O30(A) or<br>A11    | I/O38(A) or<br>A11    | I/O34(A) or<br>A11 | I/O66(A) or<br>A11 | 7                         | 95          | 9                          | 135         | В6                         | 195                        | 224                        |

| -                     | I/O37(B)              | I/O33(A)           | I/O65(A)           | -                         | -           | 10                         | 136         | B5                         | 196                        | 225                        |

| -                     | -                     | -                  | I/O64(A)           | -                         | -           | -                          | -           | B4                         | 197                        | 226                        |

| GND                   | GND                   | GND                | GND                | -                         | -           | 11                         | 137         | GND <sup>(2)</sup>         | 198                        | 227                        |

| -                     | -                     | -                  | I/O63(B)           | -                         | -           | -                          | -           | -                          | -                          | 228                        |

| I/O29(A) or<br>A10    | I/O36(A) or<br>A10    | I/O32(A) or<br>A10 | I/O62(A) or<br>A10 | 8                         | 96          | 12                         | 138         | В3                         | 199                        | 229                        |

| I/O28(B)              | I/O35(B)              | I/O31(A)           | I/O61(A)           | -                         | 97          | 13                         | 139         | B2                         | 200                        | 230                        |

| -                     | -                     | -                  | I/O60(A)           | -                         | -           | -                          | -           | A8                         | 201                        | 231                        |

| -                     | -                     | -                  | I/O59(B)           | -                         | -           | -                          | -           | -                          | -                          | 232                        |

| I/O27(A) or A9        | I/O34(A) or A9        | I/O30(A) or A9     | I/O58(A) or A9     | 9                         | 98          | 14                         | 140         | A7                         | 202                        | 233                        |

| I/O26(B)              | I/O33(A)              | I/O29(A)           | I/O57(A)           | -                         | -           | 15                         | 141         | A6                         | 203                        | 234                        |

| -                     | -                     | -                  | I/O56(A)           | -                         | -           | -                          | -           | A5                         | 204                        | 235                        |

| -                     | -                     | -                  | I/O55(B)           | -                         | -           | -                          | -           | -                          | -                          | 236                        |

| -                     | I/O32(B)              | -                  | I/O54(A)           | -                         | -           | -                          | 142         | A4                         | 205                        | 237                        |

| I/O25(A) or A8        | I/O31(A) or A8        | I/O28(A) or A8     | I/O53(A) or A8     | 10                        | 99          | 16                         | 143         | АЗ                         | 206                        | 238                        |

| -                     | -                     | -                  | I/O52(A)           | -                         | -           | -                          | -           | A2                         | -207                       | 239                        |

| MO                    | MO                    | MO                 | MO                 | 11                        | 100         | 17                         | 144         | A1                         | 208                        | 240                        |

Notes: 1. PWR = Pins connected to power plane = F1, E4/E5, L2, R4, K15, L12, E14, A12.

3. Obsolete. Not recommended for new design.

<sup>2.</sup> GND = Pins connected to ground plane = L4, M4, N9, N10, E12, D12, C7, C6.

### **AC Timing Characteristics – 5V Operation**

Delays are based on fixed load. Loads for each type of device are described in the notes. Delays are in nanoseconds. Worst case:  $V_{CC} = 4.75V$  to 5.25V. Temperature = 0°C to 70°C.

| Cell Function                 | Parameter                            | From        | То      | Load<br>Definition <sup>(7)</sup> | -1  | -2  | -4   | Units |

|-------------------------------|--------------------------------------|-------------|---------|-----------------------------------|-----|-----|------|-------|

| Wire <sup>(4)</sup>           | t <sub>PD</sub> (max) <sup>(4)</sup> | A, B, L     | A, B    | 1                                 | 0.8 | 1.2 | 1.8  | ns    |

| NAND                          | t <sub>PD</sub> (max)                | A, B, L     | В       | 1                                 | 1.6 | 2.2 | 3.2  | ns    |

| XOR                           | t <sub>PD</sub> (max)                | A, B, L     | Α       | 1                                 | 1.8 | 2.4 | 4.0  | ns    |

| AND                           | t <sub>PD</sub> (max)                | A, B, L     | В       | 1                                 | 1.7 | 2.2 | 3.2  | ns    |

| MILIV                         | h (mm)                               | A, B        | Α       | 1                                 | 1.7 | 2.3 | 4.0  | ns    |

| MUX                           | t <sub>PD</sub> (max)                | L           | Α       | 1                                 | 2.1 | 3.0 | 4.9  | ns    |

| D-Flip-flop <sup>(5)</sup>    | t <sub>setup</sub> (min)             | A, B, L     | CLK     | -                                 | 1.5 | 2.0 | 3.0  | ns    |

| D-Flip-flop <sup>(5)</sup>    | t <sub>hold</sub> (min)              | CLK         | A, B, L | -                                 | 0   | 0   | 0    | ns    |

| D-Flip-flop                   | t <sub>PD</sub> (max)                | CLK         | Α       | 1                                 | 1.5 | 2.0 | 3.0  | ns    |

| Bus Driver                    | t <sub>PD</sub> (max)                | А           | L       | 2                                 | 2.0 | 2.6 | 4.0  | ns    |

| Damastar                      | h (m.n.)                             | L, E        | E       | 3                                 | 1.3 | 1.6 | 2.3  | ns    |

| Repeater                      | t <sub>PD</sub> (max)                | L, E        | L       | 2                                 | 1.7 | 2.1 | 3.0  | ns    |

| Column Clock                  | t <sub>PD</sub> (max)                | GCLK, A, ES | CLK     | 3                                 | 1.8 | 2.4 | 3.0  | ns    |

| Column Reset                  | t <sub>PD</sub> (max)                | GRES, A, EN | RES     | 3                                 | 1.8 | 2.4 | 3.0  | ns    |

| Clock Buffer <sup>(5)</sup>   | t <sub>PD</sub> (max)                | CLOCK PIN   | GCLK    | -                                 | 1.6 | 2.0 | 2.9  | ns    |

| Reset Buffer <sup>(5)</sup>   | t <sub>PD</sub> (max)                | RESET PIN   | GRES    | -                                 | 1.5 | 1.9 | 2.8  | ns    |

| TTL Input <sup>(1)</sup>      | t <sub>PD</sub> (max)                | I/O         | Α       | 3                                 | 1.0 | 1.2 | 1.5  | ns    |

| CMOS Input <sup>(2)</sup>     | t <sub>PD</sub> (max)                | I/O         | Α       | 3                                 | 1.3 | 1.4 | 2.3  | ns    |

| Fast Output <sup>(3)</sup>    | t <sub>PD</sub> (max)                | А           | I/O PIN | 4                                 | 3.3 | 3.5 | 6.0  | ns    |

| Slow Output <sup>(3)</sup>    | t <sub>PD</sub> (max)                | А           | I/O PIN | 4                                 | 7.5 | 8.0 | 12.0 | ns    |

| Output Disable <sup>(5)</sup> | t <sub>PXZ</sub> (max)               | L           | I/O PIN | 4                                 | 3.1 | 3.3 | 5.5  | ns    |

| Fast Enable <sup>(3)(5)</sup> | t <sub>PXZ</sub> (max)               | L           | I/O PIN | 4                                 | 3.8 | 4.0 | 6.5  | ns    |

| Slow Enable <sup>(3)(5)</sup> | t <sub>PXZ</sub> (max)               | L           | I/O PIN | 4                                 | 8.2 | 8.5 | 12.5 | ns    |

| Device                      | Cell Types                                   | Outputs | I <sub>CC</sub> (max) |

|-----------------------------|----------------------------------------------|---------|-----------------------|

| Cell <sup>(6)</sup>         | Wire, XWire, Half-adder, Flip-flop           | A, B    | 4.5 μA/MHz            |

| Bus <sup>(6)</sup>          | Wire, XWire, Half-adder, Flip-flop, Repeater | L       | 2.5 μA/MHz            |

| Column Clock <sup>(6)</sup> | Column Clock Driver                          | CLK     | 40 μA/MHz             |

Notes:

- 1. TTL buffer delays are measured from a  $V_{IH}$  of 1.5V at the pad to the internal  $V_{IH}$  at A. The input buffer load is constant.

- 2. CMOS buffer delays are measured from a  $V_{IH}$  of 1/2  $V_{CC}$  at the apd to the internal  $V_{IH}$  at A. The input buffer load is constant.

- 3. Buffer delay is to a pad voltage of 1.5V with one output switching.

- 4. Max specifications are the average of mas  $t_{PDLH}$  and  $t_{PDHL}$ .

- 5. Parameter based on characterization and simulation; not tested in production

- 6. Exact power calculation is available in an Atmel application note.

- 7. Load Definition: 1 = Load of one A or B input; 2 = Load of one L input; 3 = Constant Load; 4 = Tester Load of 50 pF.

# AC Timing Characteristics – 3.3V Operation (8)

Delays are based on fixed load. Loads for each type of device are described in the notes. Delays are in nanoseconds. Worst case:  $V_{CC} = 3.0V$  to 3.6V. Temperature = 0°C to 70°C.

| Cell Function                 | Parameter                            | From        | То      | Load<br>Definition <sup>(7)</sup> | -4   | Units |

|-------------------------------|--------------------------------------|-------------|---------|-----------------------------------|------|-------|

| Wire <sup>(4)</sup>           | t <sub>PD</sub> (max) <sup>(4)</sup> | A, B, L     | A, B    | 1                                 | 1.8  | ns    |

| NAND                          | t <sub>PD</sub> (max)                | A, B, L     | В       | 1                                 | 3.2  | ns    |

| XOR                           | t <sub>PD</sub> (max)                | A, B, L     | Α       | 1                                 | 4.0  | ns    |

| AND                           | t <sub>PD</sub> (max)                | A, B, L     | В       | 1                                 | 3.2  | ns    |

| MUX                           | t (may)                              | A, B        | Α       | 1                                 | 4.0  | ns    |

| WOX                           | t <sub>PD</sub> (max)                | L           | Α       | 1                                 | 4.9  | ns    |

| D-Flip-flop <sup>(5)</sup>    | t <sub>setup</sub> (min)             | A, B, L     | CLK     | -                                 | 3.0  | ns    |

| D-Flip-flop <sup>(5)</sup>    | t <sub>hold</sub> (min)              | CLK         | A, B, L | -                                 | 0    | ns    |

| D-Flip-flop                   | t <sub>PD</sub> (max)                | CLK         | Α       | 1                                 | 3.0  | ns    |

| Bus Driver                    | t <sub>PD</sub> (max)                | A           | L       | 2                                 | 4.0  | ns    |

| Danastar                      | t (may)                              | L, E        | E       | 3                                 | 2.3  | ns    |

| Repeater                      | t <sub>PD</sub> (max)                | L, E        | L       | 2                                 | 3.0  | ns    |

| Column Clock                  | t <sub>PD</sub> (max)                | GCLK, A, ES | CLK     | 3                                 | 3.0  | ns    |

| Column Reset                  | t <sub>PD</sub> (max)                | GRES, A, EN | RES     | 3                                 | 3.0  | ns    |

| Clock Buffer <sup>(5)</sup>   | t <sub>PD</sub> (max)                | CLOCK PIN   | GCLK    | 4                                 | 2.9  | ns    |

| Reset Buffer <sup>(5)</sup>   | t <sub>PD</sub> (max)                | RESET PIN   | GRES    | 5                                 | 2.8  | ns    |

| TTL Input <sup>(1)</sup>      | t <sub>PD</sub> (max)                | I/O         | А       | 3                                 | 1.5  | ns    |

| CMOS Input <sup>(2)</sup>     | t <sub>PD</sub> (max)                | I/O         | А       | 3                                 | 2.3  | ns    |

| Fast Output <sup>(3)</sup>    | t <sub>PD</sub> (max)                | A           | I/O PIN | 6                                 | 6.0  | ns    |

| Slow Output <sup>(3)</sup>    | t <sub>PD</sub> (max)                | A           | I/O PIN | 6                                 | 12.0 | ns    |

| Output Disable <sup>(5)</sup> | t <sub>PXZ</sub> (max)               | L           | I/O PIN | 6                                 | 5.5  | ns    |

| Fast Enable <sup>(3)(5)</sup> | t <sub>PXZ</sub> (max)               | L           | I/O PIN | 6                                 | 6.5  | ns    |

| Slow Enable <sup>(3)(5)</sup> | t <sub>PXZ</sub> (max)               | L           | I/O PIN | 6                                 | 12.5 | ns    |

| Device                      | Cell Types                                   | Outputs | I <sub>CC</sub> (max) |

|-----------------------------|----------------------------------------------|---------|-----------------------|

| Cell <sup>(6)</sup>         | Wire, XWire, Half-adder, Flip-flop           | A, B    | 2.3 μA/MHz            |

| Bus <sup>(6)</sup>          | Wire, XWire, Half-adder, Flip-flop, Repeater | L       | 1.3 μA/MHz            |

| Column Clock <sup>(6)</sup> | Column Clock Driver                          | CLK     | 20 μA/MHz             |

Notes

- 1. TTL buffer delays are measured from a  $V_{IH}$  of 1.5V at the pad to the internal  $V_{IH}$  at A. The input buffer load is constant.

- 2. CMOS buffer delays are measured from a  $V_{IH}$  of 1/2  $V_{CC}$  at the apd to the internal  $V_{IH}$  at A. The input buffer load is constant.

- 3. Buffer delay is to a pad voltage of 1.5V with one output switching.

- 4. Max specifications are the average of mas  $t_{PDLH}$  and  $t_{PDHL}$ .

- 5. Parameter based on characterization and simulation; not tested in production

- 6. Exact power calculation is available in an Atmel application note.

- 7. Load Definition: 1 = Load of one A or B input; 2 = Load of one L input; 3 = Constant Load; 4 = Load of 28 Clock Columns; 5 = Load of 28 Reset Columns; 6 = Tester Load of 50 pF.

- 8. Obsolete. Not recommended for new design.

### **Absolute Maximum Ratings\***

| Supply Voltage (V <sub>CC</sub> )0.5V to + 7.0V                    |

|--------------------------------------------------------------------|

| DC Input Voltage (V <sub>IN</sub> )0.5V to V <sub>CC</sub> + 0.5V  |

| DC Output Voltage (V <sub>ON</sub> )0.5V to V <sub>CC</sub> + 0.5V |

| Storage Temperature Range (TSTG)65 °C to +150 °C                   |

| Power Dissipation (PD)1500 mW                                      |

| Lead Temperature (T <sub>L</sub> ) (Soldering, 10 sec.)260°C       |

| ESD (R <sub>ZAP</sub> = 1.5K, C <sub>ZAP</sub> = 100 pF)2000V      |

\*NOTICE:

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress rating only and functional operation of the device at these or any other conditions beyond those listed under operating conditions is not implied. Exposure to Absolute Maximum Rating conditions for extended periods of time may affect device reliability.

## DC and AC Operating Rage – 5V Operation

|                                |                              | AT6002-2/4 <sup>(1)</sup> AT6003-2/4 <sup>(1)</sup> AT6005-2/4 <sup>(1)</sup> AT6010-2/4 <sup>(1)</sup> Commercial <sup>(1)</sup> | AT6002-2/4 <sup>(1)</sup><br>AT6003-2/4 <sup>(1)</sup><br>AT6005-2/4<br>AT6010-2/4<br>Industrial | AT6002-2/4 <sup>(1)</sup><br>AT6003-2/4 <sup>(1)</sup><br>AT6005-2/4 <sup>(1)</sup><br>AT6010-2/4 <sup>(1)</sup><br>Military <sup>(1)</sup> |  |

|--------------------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|

| Operating Temperature (Case)   |                              | 0°C - 70°C                                                                                                                        | -40°C - 85°C                                                                                     | -55°C - 125°C                                                                                                                               |  |

| V <sub>CC</sub> Power Supply   | V <sub>CC</sub> Power Supply |                                                                                                                                   | 5V ± 10%                                                                                         | 5V ± 10%                                                                                                                                    |  |

| Input Voltage Level            | High (V <sub>IHT</sub> )     | 2.0V - V <sub>CC</sub>                                                                                                            | 2.0V - V <sub>CC</sub>                                                                           | 2.0V - V <sub>CC</sub>                                                                                                                      |  |

| (TTL)                          | Low (V <sub>ILT</sub> )      | 0V - 0.8V                                                                                                                         | 0V - 0.8V                                                                                        | 0V - 0.8V                                                                                                                                   |  |

| Input Voltage Level            | High (V <sub>IHC</sub> )     | 70% - 100% V <sub>CC</sub>                                                                                                        | 70% - 100% V <sub>CC</sub>                                                                       | 70% - 100% V <sub>CC</sub>                                                                                                                  |  |

| (CMOS)                         | Low (V <sub>ILC</sub> )      | 0 - 30% V <sub>CC</sub>                                                                                                           | 0 - 30% V <sub>CC</sub>                                                                          | 0 - 30% V <sub>CC</sub>                                                                                                                     |  |

| Input Signal Transition Time ( | (T <sub>IN</sub> )           | 50 ns (max)                                                                                                                       | 50 ns (max)                                                                                      | 50 ns (max)                                                                                                                                 |  |

## DC and AC Operating Rage – 3.3V Operation(1)

|                              |                          | AT6002-2/4 <sup>(1)</sup> , AT6003-2/4 <sup>(1)</sup><br>AT6005-2/4 <sup>(1)</sup> , AT6010-2/4 <sup>(1)</sup><br>Commercial |  |  |

|------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|

| Operating Temperature (Case) |                          | 0°C - 70°C                                                                                                                   |  |  |

| V <sub>CC</sub> Power Supply |                          | 3.3V ± 5%                                                                                                                    |  |  |

| Input Voltage Level          | High (V <sub>IHT</sub> ) | 2.0V - V <sub>CC</sub>                                                                                                       |  |  |

| (TTL)                        | Low (V <sub>ILT</sub> )  | 0V - 0.8V                                                                                                                    |  |  |

| Input Voltage Level          | High (V <sub>IHC</sub> ) | 70% - 100% V <sub>CC</sub>                                                                                                   |  |  |

| (CMOS)                       | Low (V <sub>ILC</sub> )  | 0 - 30% V <sub>CC</sub>                                                                                                      |  |  |

| Input Signal Transition Time | (T <sub>IN</sub> )       | 50 ns (max)                                                                                                                  |  |  |

Note: 1. Obsolete. Not recommended for new design.

# **DC Characteristics – 5V Operation**

| Symbol           | Parameter                     | Conditions                                         | Conditions                                    |                     | Max                 | Units |

|------------------|-------------------------------|----------------------------------------------------|-----------------------------------------------|---------------------|---------------------|-------|

| V                | Liber level brook Veltere     | 0                                                  | CMOS                                          | 70% V <sub>CC</sub> | V <sub>CC</sub>     | V     |

| V <sub>IH</sub>  | High-level Input Voltage      | Commercial                                         | TTL                                           | 2.0                 | V <sub>CC</sub>     | V     |

| V                | Low lovel loout Voltage       | Commoraial                                         | CMOS                                          | 0                   | 30% V <sub>CC</sub> | V     |

| V <sub>IL</sub>  | Low-level Input Voltage       | Commercial                                         | TTL                                           | 0                   | 0.8                 | ٧     |

| V                | Lligh level Output Veltage    | Commoraial                                         | I <sub>OH</sub> = -4 mA, V <sub>CC</sub> min  | 3.9                 |                     | V     |

| V <sub>OH</sub>  | High-level Output Voltage     | Commercial                                         | I <sub>OH</sub> = -16 mA, V <sub>CC</sub> min | 3.0                 |                     | V     |

| V                | Low-level Output Voltage      | Commercial                                         | I <sub>OL</sub> = 4 mA, V <sub>CC</sub> min   |                     | 0.4                 | V     |

| V <sub>OL</sub>  |                               |                                                    | I <sub>OL</sub> = 16 mA, V <sub>CC</sub> min  |                     | 0.5                 | ٧     |

|                  | High-level Tristate           | V V (may)                                          |                                               |                     | 10                  |       |

| l <sub>OZH</sub> | Output Leakage Current        | $V_O = V_{CC}$ (max)                               |                                               | 10                  | μΑ                  |       |

|                  | High-level Tristate           | Without Pull-up, $V_O = V_{SS}$                    |                                               | -10                 |                     | μΑ    |

| l <sub>OZL</sub> | Output Leakage Current        | With Pull-up, $V_0 = V$                            | With Pull-up, $V_O = V_{SS}$                  |                     |                     | μΑ    |

| I <sub>IH</sub>  | High-level Input Current      | $V_{IN} = V_{CC}$ (max)                            |                                               |                     | 10                  | μΑ    |

|                  | Lauria da val la must Current | Without Pull-up, V <sub>IN</sub> = V <sub>SS</sub> |                                               | -10                 |                     | μΑ    |

| l <sub>IL</sub>  | Low-level Input Current       | With Pull-up, V <sub>IN</sub> = V <sub>SS</sub>    |                                               | -500                |                     | μΑ    |

| I <sub>cc</sub>  | Power Consumption             | Without Internal Oscillator (Standby)              |                                               |                     | 500                 | μΑ    |

| C <sub>IN</sub>  | Input Capacitance             | All Pins                                           |                                               |                     | 10                  | pF    |

| Note: | 1. | Obsolete. Not recommended for new design. |

|-------|----|-------------------------------------------|

|       |    | Obcoloto: Not recommended for new deelgm  |

# DC Characteristics – 3.3V Operation<sup>(2)</sup>

| Symbol                         | Parameter                 | Conditions                                         | Conditions                                   |                     | Max                 | Units |

|--------------------------------|---------------------------|----------------------------------------------------|----------------------------------------------|---------------------|---------------------|-------|

| V                              | Library Laurent Vallage   | 0                                                  | CMOS                                         | 70% V <sub>CC</sub> | V <sub>CC</sub>     | V     |

| V <sub>IH</sub>                | High-level Input Voltage  | Commercial                                         | TTL                                          | 2.0                 | V <sub>CC</sub>     | V     |

| V                              | Low lovel lanut Voltage   | Commoraial                                         | CMOS                                         | 0                   | 30% V <sub>CC</sub> | V     |

| V <sub>IL</sub>                | Low-level Input Voltage   | Commercial                                         | TTL                                          | 0                   | 0.8                 | V     |

| M                              | High lavel Output Valtage | Commonatel                                         | I <sub>OH</sub> = -2 mA, V <sub>CC</sub> min | 2.4                 |                     | V     |

| V <sub>OH</sub>                | High-level Output Voltage | Commercial                                         | I <sub>OH</sub> = -6 mA, V <sub>CC</sub> min | 2.0                 |                     | V     |

| M                              | Low-level Output Voltage  | Commercial                                         | I <sub>OL</sub> = +2 mA, V <sub>CC</sub> min |                     | 0.4                 | V     |

| V <sub>OL</sub>                |                           |                                                    | I <sub>OL</sub> = +6 mA, V <sub>CC</sub> min |                     | 0.5                 | V     |

|                                | High-level Tristate       |                                                    |                                              | 10                  |                     |       |

| l <sub>OZH</sub>               | Output Leakage Current    | $V_0 = V_{CC}$ (max)                               |                                              | 10                  | μA                  |       |

|                                | High-level Tristate       | Without Pull-up, $V_O = V_{SS}$                    |                                              | -10                 |                     | μA    |

| I <sub>OZL</sub>               | Output Leakage Current    | With Pull-up, $V_0 = V$                            | With Pull-up, $V_O = V_{SS}$                 |                     |                     | μA    |

| I <sub>IH</sub>                | High-level Input Current  | $V_{IN} = V_{CC}$ (max)                            |                                              |                     | 10                  | μΑ    |

| I <sub>IL</sub>                |                           | Without Pull-up, V <sub>IN</sub> = V <sub>SS</sub> |                                              | -10                 |                     | μΑ    |

|                                | Low-level Input Current   | With Pull-up, V <sub>IN</sub> = V <sub>SS</sub>    |                                              | -500                |                     | μΑ    |

| I <sub>cc</sub>                | Power Consumption         | Without Internal Oscillator (Standby)              |                                              |                     | 200                 | μΑ    |

| C <sub>IN</sub> <sup>(1)</sup> | Input Capacitance         | All Pins                                           |                                              |                     | 10                  | pF    |

Notes: 1. Parameter based on characterization and simulation; it is not tested in production.

2. Obsolete. Not recommended for new design.

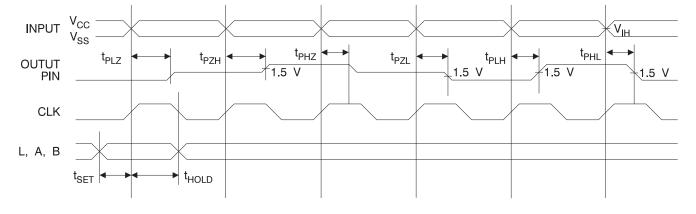

## **Device Timing: During Operation**

# Ordering Information – AT6003<sup>(1)</sup>

| Usable | Speed      |               |         |                 |

|--------|------------|---------------|---------|-----------------|

| Gates  | Grade (ns) | Ordering Code | Package | Operation Range |

| 9,000  | 2          | AT6003-2AC    | 100A    | 5V Commercial   |

|        |            | AT6003A-2AC   | 144A    | (0°C to 70°C)   |

|        |            | AT6003-2JC    | 84J     |                 |

|        |            | AT6003-2QC    | 132Q    |                 |

|        |            | AT6003-2AI    | 100A    | Industrial      |

|        |            | AT6003A-2AI   | 144A    | (-40°C to 85°C) |

|        |            | AT6003-2JI    | 84J     |                 |

|        |            | AT6003-2QI    | 132Q    |                 |

| 9,000  | 4          | AT6003-4AC    | 100A    | 5V Commercial   |

|        |            | AT6003A-4AC   | 144A    | (0°C to 70°C)   |

|        |            | AT6003-4JC    | 84J     |                 |

|        |            | AT6003-4QC    | 132Q    |                 |

|        |            | AT6003LV-4AC  | 100A    | 3.3V Commercial |

|        |            | AT6003ALV-4AC | 144A    | (0°C to 70°C)   |

|        |            | AT6003LV-4JC  | 84J     |                 |

|        |            | AT6003LV-4QC  | 132Q    |                 |

|        |            | AT6003-4AI    | 100A    | 5V Industrial   |

|        |            | AT6003A-4AI   | 144A    | (-40°C to 85°C) |

|        |            | AT6003-4JI    | 84J     |                 |

|        |            | AT6003-4QI    | 132Q    |                 |

Note: 1. Obsolete. Not recommended for new design.

|      | Package Type                                                            |  |  |  |

|------|-------------------------------------------------------------------------|--|--|--|

| 84J  | 84-lead, Plastic J-leaded Chip Carrier (PLCC)                           |  |  |  |

| 100A | 100-lead, Very Thin (1.0 mm) Plastic Gull-Wing Quad Flat Package (VQFP) |  |  |  |

| 132Q | Q 132-lead, Bumpered Plastic Gull-Wing Quad Flat Package (BQFP)         |  |  |  |

| 144A | 144-lead, Thin (1.4 mm) Plastic Gull-Wing Quad Flat Package (TQFP)      |  |  |  |

| 208Q | 208Q 208-lead, Plastic Gull-Wing Quad Flat Package (PQFP)               |  |  |  |

| 240Q | 240-lead, Plastic Gull-Wing Quad Flat Package (PQFP)                    |  |  |  |

# **Ordering Information – AT6005**

| Usable<br>Gates | Speed<br>Grade (ns) | Ordering Code | Package | Operation Range           |

|-----------------|---------------------|---------------|---------|---------------------------|

| 15,000          | 2                   | AT6005-2AU    | 100A    | 5V Industrial Temperature |

|                 |                     |               |         | (-40°C to 85°C)           |

| 15,000          | 2                   | AT6005-2AC    | 100A    | 5V Commercial             |