# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                           |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 168MHz                                                                    |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT         |

| Number of I/O              | 82                                                                        |

| Program Memory Size        | 1MB (1M x 8)                                                              |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 192K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                     |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 100-LQFP                                                                  |

| Supplier Device Package    | 100-LQFP (14x14)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f405vgt6     |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Perip                           | herals           | STM32F405RG | STM32F405OG | STM32F405VG | STM32F405ZG        | STM32F405OE           | STM32F407Vx | STM32F407Zx    | STM32F407I          |  |  |  |

|---------------------------------|------------------|-------------|-------------|-------------|--------------------|-----------------------|-------------|----------------|---------------------|--|--|--|

|                                 | SPI / I2S        |             |             |             | 3/2 (full du       | uplex) <sup>(2)</sup> | 1           | 1              |                     |  |  |  |

|                                 | l <sup>2</sup> C |             |             |             | 3                  |                       |             |                |                     |  |  |  |

|                                 | USART/<br>UART   |             |             |             | 4/2                | 4/2                   |             |                |                     |  |  |  |

| Communi<br>cation<br>interfaces | USB<br>OTG FS    |             |             |             | Yes                | 5                     |             | 16 24<br>05 °C |                     |  |  |  |

| interfaceo                      | USB<br>OTG HS    |             |             |             | Yes                | 3                     |             |                |                     |  |  |  |

|                                 | CAN              |             |             |             | 2                  |                       |             |                |                     |  |  |  |

|                                 | SDIO             |             | Yes         |             |                    |                       |             |                |                     |  |  |  |

| Camera in                       | terface          |             | Ν           | 0           |                    |                       |             | Yes            |                     |  |  |  |

| GPIOs                           |                  | 51          | 72          | 82          | 114                | 72                    | 82          | 114            | 140                 |  |  |  |

| 12-bit ADC                      |                  |             |             |             | 3                  |                       |             |                |                     |  |  |  |

| Number of                       | channels         | 16          | 13          | 16          | 24                 | 13                    | 16          | 24             | 24                  |  |  |  |

| 12-bit DAC<br>Number of         |                  |             |             |             | Yes<br>2           |                       |             |                |                     |  |  |  |

| Maximum<br>frequency            | CPU              |             |             |             | 168 N              | ЛНz                   |             |                |                     |  |  |  |

| Operating                       | voltage          |             |             |             | 1.8 to 3.          | 6 V <sup>(3)</sup>    |             |                |                     |  |  |  |

| Operating                       |                  |             |             | Ambient te  | mperatures: -40    | to +85 °C /–40 to     | +105 °C     |                |                     |  |  |  |

| temperatu                       | res              |             |             | Jur         | iction temperature | e: –40 to + 125 °C    | ;           |                | 24<br>UFBGA17       |  |  |  |

| Package                         |                  | LQFP64      | WLCSP90     | LQFP100     | LQFP144            | WLCSP90               | LQFP100     | LQFP144        | UFBGA176<br>LQFP176 |  |  |  |

Т. Select. Bank2 can only support a 16- or 8-bit NAND Flash memory using the NCE2 Chip Select. The interrupt line cannot be used since Port G is not available in this package.

2. The SPI2 and SPI3 interfaces give the flexibility to work in an exclusive way in either the SPI mode or the  $I^2S$  audio mode.

V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V is obtained when the device operates in reduced temperature range, and with the use of an external power supply supervisor (refer to Section : Internal reset OFF). 3.

## 2.2.1 ARM<sup>®</sup> Cortex<sup>®</sup>-M4 core with FPU and embedded Flash and SRAM

The ARM Cortex-M4 processor with FPU is the latest generation of ARM processors for embedded systems. It was developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced response to interrupts.

The ARM Cortex-M4 32-bit RISC processor with FPU features exceptional code-efficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices.

The processor supports a set of DSP instructions which allow efficient signal processing and complex algorithm execution.

Its single precision FPU (floating point unit) speeds up software development by using metalanguage development tools, while avoiding saturation.

The STM32F405xx and STM32F407xx family is compatible with all ARM tools and software.

*Figure 5* shows the general block diagram of the STM32F40xxx family.

Note: Cortex-M4 with FPU is binary compatible with Cortex-M3.

## 2.2.2 Adaptive real-time memory accelerator (ART Accelerator<sup>™</sup>)

The ART Accelerator<sup>™</sup> is a memory accelerator which is optimized for STM32 industrystandard ARM<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU processors. It balances the inherent performance advantage of the ARM Cortex-M4 with FPU over Flash memory technologies, which normally requires the processor to wait for the Flash memory at higher frequencies.

To release the processor full 210 DMIPS performance at this frequency, the accelerator implements an instruction prefetch queue and branch cache, which increases program execution speed from the 128-bit Flash memory. Based on CoreMark benchmark, the performance achieved thanks to the ART accelerator is equivalent to 0 wait state program execution from Flash memory at a CPU frequency up to 168 MHz.

## 2.2.3 Memory protection unit

The memory protection unit (MPU) is used to manage the CPU accesses to memory to prevent one task to accidentally corrupt the memory or resources used by any other active task. This memory area is organized into up to 8 protected areas that can in turn be divided up into 8 subareas. The protection area sizes are between 32 bytes and the whole 4 gigabytes of addressable memory.

The MPU is especially helpful for applications where some critical or certified code has to be protected against the misbehavior of other tasks. It is usually managed by an RTOS (real-time operating system). If a program accesses a memory location that is prohibited by the MPU, the RTOS can detect it and take action. In an RTOS environment, the kernel can dynamically update the MPU area setting, based on the process to be executed.

The MPU is optional and can be bypassed for applications that do not need it.

## 2.2.4 Embedded Flash memory

The STM32F40xxx devices embed a Flash memory of 512 Kbytes or 1 Mbytes available for storing programs and data.

DocID022152 Rev 8

## 2.2.5 CRC (cyclic redundancy check) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code from a 32-bit data word and a fixed generator polynomial.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a software signature during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

## 2.2.6 Embedded SRAM

All STM32F40xxx products embed:

Up to 192 Kbytes of system SRAM including 64 Kbytes of CCM (core coupled memory) data RAM

RAM memory is accessed (read/write) at CPU clock speed with 0 wait states.

4 Kbytes of backup SRAM

This area is accessible only from the CPU. Its content is protected against possible unwanted write accesses, and is retained in Standby or VBAT mode.

## 2.2.7 Multi-AHB bus matrix

The 32-bit multi-AHB bus matrix interconnects all the masters (CPU, DMAs, Ethernet, USB HS) and the slaves (Flash memory, RAM, FSMC, AHB and APB peripherals) and ensures a seamless and efficient operation even when several high-speed peripherals work simultaneously.

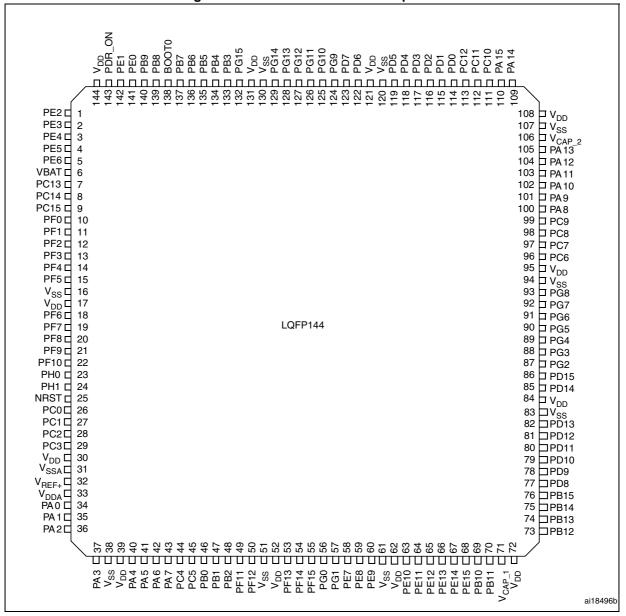

Figure 14. STM32F40xxx LQFP144 pinout

1. The above figure shows the package top view.

|        | F       | Pin r   | numb    | er       |         |                                                      |          |                 |            |                                                          |                                    |

|--------|---------|---------|---------|----------|---------|------------------------------------------------------|----------|-----------------|------------|----------------------------------------------------------|------------------------------------|

| LQFP64 | WLCSP90 | LQFP100 | LQFP144 | UFBGA176 | LQFP176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes      | Alternate functions                                      | Additional<br>functions            |

| -      | -       | 1       | 1       | A2       | 1       | PE2                                                  | I/O      | FT              | -          | TRACECLK/ FSMC_A23 /<br>ETH_MII_TXD3 /<br>EVENTOUT       | -                                  |

| -      | -       | 2       | 2       | A1       | 2       | PE3                                                  | I/O      | FT              | -          | TRACED0/FSMC_A19 /<br>EVENTOUT                           | -                                  |

| -      | -       | 3       | 3       | B1       | 3       | PE4                                                  | I/O      | FT              | -          | TRACED1/FSMC_A20 /<br>DCMI_D4/ EVENTOUT                  | -                                  |

| -      | -       | 4       | 4       | B2       | 4       | PE5                                                  | I/O      | FT              | -          | TRACED2 / FSMC_A21 /<br>TIM9_CH1 / DCMI_D6 /<br>EVENTOUT | -                                  |

| -      | -       | 5       | 5       | В3       | 5       | PE6                                                  | I/O      | FT              | -          | TRACED3 / FSMC_A22 /<br>TIM9_CH2 / DCMI_D7 /<br>EVENTOUT | -                                  |

| 1      | A10     | 6       | 6       | C1       | 6       | V <sub>BAT</sub>                                     | S        | -               | -          | -                                                        | -                                  |

| -      | -       | -       | -       | D2       | 7       | PI8                                                  | I/O      | FT              | (2)(<br>3) | EVENTOUT                                                 | RTC_TAMP1,<br>RTC_TAMP2,<br>RTC_TS |

| 2      | A9      | 7       | 7       | D1       | 8       | PC13                                                 | I/O      | FT              | (2)<br>(3) | EVENTOUT                                                 | RTC_OUT,<br>RTC_TAMP1,<br>RTC_TS   |

| 3      | B10     | 8       | 8       | E1       | 9       | PC14/OSC32_IN<br>(PC14)                              | I/O      | FT              | (2)(<br>3) | EVENTOUT                                                 | OSC32_IN <sup>(4)</sup>            |

| 4      | B9      | 9       | 9       | F1       | 10      | PC15/<br>OSC32_OUT<br>(PC15)                         | I/O      | FT              | (2)(<br>3) | EVENTOUT                                                 | OSC32_OUT <sup>(4)</sup>           |

| -      | -       | -       | -       | D3       | 11      | PI9                                                  | I/O      | FT              | -          | CAN1_RX / EVENTOUT                                       | -                                  |

| -      | -       | -       | -       | E3       | 12      | PI10                                                 | I/O      | FT              | -          | ETH_MII_RX_ER /<br>EVENTOUT                              | -                                  |

| -      | -       | -       | -       | E4       | 13      | PI11                                                 | I/O      | FT              | -          | OTG_HS_ULPI_DIR /<br>EVENTOUT                            | -                                  |

| -      | -       | -       | I       | F2       | 14      | V <sub>SS</sub>                                      | S        | I               | -          | -                                                        | -                                  |

| -      | -       | -       | -       | F3       | 15      | V <sub>DD</sub>                                      | S        | I               | -          | -                                                        | -                                  |

| -      | -       | -       | 10      | E2       | 16      | PF0                                                  | I/O      | FT              | -          | FSMC_A0 / I2C2_SDA /<br>EVENTOUT                         | -                                  |

Table 7. STM32F40xxx pin and ball definitions

|        |      |                |                        |           |                  |               | Table                          | 9. Alterr            | nate funct             | ion ma             | pping                     |                    |                                           |                      |                |      |          |

|--------|------|----------------|------------------------|-----------|------------------|---------------|--------------------------------|----------------------|------------------------|--------------------|---------------------------|--------------------|-------------------------------------------|----------------------|----------------|------|----------|

|        |      | AF0            | AF1                    | AF2       | AF3              | AF4           | AF5                            | AF6                  | AF7                    | AF8                | AF9                       | AF10               | AF11                                      | AF12                 | AF13           |      |          |

| Po     | ort  | SYS            | TIM1/2                 | TIM3/4/5  | TIM8/9/10<br>/11 | I2C1/2/3      | SPI1/SPI2/<br>I2S2/I2S2e<br>xt | SPI3/I2Sext<br>/I2S3 | USART1/2/3/<br>I2S3ext | UART4/5/<br>USART6 | CAN1/2<br>TIM12/13/<br>14 | OTG_FS/<br>OTG_HS  | ETH                                       | FSMC/SDIO<br>/OTG_FS | DCMI           | AF14 | AF15     |

|        | PA0  | -              | TIM2_CH1_<br>ETR       | TIM 5_CH1 | TIM8_ETR         | -             | -                              | -                    | USART2_CTS             | UART4_TX           | -                         | -                  | ETH_MII_CRS                               | -                    | -              | -    | EVENTOUT |

|        | PA1  | -              | TIM2_CH2               | TIM5_CH2  | -                | -             | -                              | -                    | USART2_RTS             | UART4_RX           | -                         | -                  | ETH_MII<br>_RX_CLK<br>ETH_RMIIREF<br>_CLK | -                    | -              | -    | EVENTOUT |

|        | PA2  | -              | TIM2_CH3               | TIM5_CH3  | TIM9_CH1         | -             | -                              | -                    | USART2_TX              | -                  | -                         | -                  | ETH_MDIO                                  | -                    | -              | -    | EVENTOUT |

|        | PA3  | -              | TIM2_CH4               | TIM5_CH4  | TIM9_CH2         | -             | -                              | -                    | USART2_RX              | -                  | -                         | OTG_HS_ULPI_<br>D0 | ETH _MII_COL                              | -                    | -              | -    | EVENTOUT |

|        | PA4  | -              | -                      | -         | -                | -             | SPI1_NSS                       | SPI3_NSS<br>I2S3_WS  | USART2_CK              | -                  | -                         | -                  | -                                         | OTG_HS_SOF           | DCMI_<br>HSYNC | -    | EVENTOUT |

|        | PA5  | -              | TIM2_CH1_<br>ETR       | -         | TIM8_CH1N        | -             | SPI1_SCK                       | -                    | -                      | -                  | -                         | OTG_HS_ULPI_<br>CK | -                                         | -                    | -              | -    | EVENTOUT |

|        | PA6  | -              | TIM1_BKIN              | TIM3_CH1  | TIM8_BKIN        | -             | SPI1_MISO                      | -                    | -                      | -                  | TIM13_CH1                 | -                  | -                                         | -                    | DCMI_PIXCK     | -    | EVENTOUT |

| Port A | PA7  | -              | TIM1_CH1N              | TIM3_CH2  | TIM8_CH1N        | -             | SPI1_MOSI                      | -                    | -                      | -                  | TIM14_CH1                 | -                  | ETH_MII_RX_DV<br>ETH_RMII<br>_CRS_DV      | -                    | -              | -    | EVENTOUT |

|        | PA8  | MCO1           | TIM1_CH1               | -         | -                | I2C3_SCL      | -                              | -                    | USART1_CK              | -                  | -                         | OTG_FS_SOF         | -                                         | -                    | -              | -    | EVENTOUT |

|        | PA9  | -              | TIM1_CH2               | -         | -                | I2C3_<br>SMBA | -                              | -                    | USART1_TX              | -                  | -                         | -                  | -                                         | -                    | DCMI_D0        | -    | EVENTOUT |

|        | PA10 | -              | TIM1_CH3               | -         | -                | -             | -                              | -                    | USART1_RX              | -                  | -                         | OTG_FS_ID          | -                                         | -                    | DCMI_D1        | -    | EVENTOUT |

|        | PA11 | -              | TIM1_CH4               | -         | -                | -             | -                              | -                    | USART1_CTS             | -                  | CAN1_RX                   | OTG_FS_DM          | -                                         | -                    | -              | -    | EVENTOUT |

|        | PA12 | -              | TIM1_ETR               | -         | -                | -             | -                              | -                    | USART1_RTS             | -                  | CAN1_TX                   | OTG_FS_DP          | -                                         | -                    | -              | -    | EVENTOUT |

|        | PA13 | JTMS-<br>SWDIO | -                      | -         | -                | -             | -                              | -                    | -                      | -                  | -                         | -                  | -                                         | -                    | -              | -    | EVENTOUT |

|        | PA14 | JTCK-<br>SWCLK | -                      | -         | -                | -             | -                              | -                    | -                      | -                  | -                         | -                  | -                                         | -                    | -              | -    | EVENTOUT |

|        | PA15 | JTDI           | TIM 2_CH1<br>TIM 2_ETR | -         | -                | -             | SPI1_NSS                       | SPI3_NSS/<br>I2S3_WS | -                      | -                  | -                         | -                  | -                                         | -                    | -              | -    | EVENTOUT |

DocID022152 Rev 8

5

62/202

STM32F405xx, STM32F407xx

Pinouts and pin description

65/202

DocID022152 Rev 8

|        |      |     |        |          |                  |          |                                |                      |                        |                    | (00                       | ,                 |      |                        |          |      |          |

|--------|------|-----|--------|----------|------------------|----------|--------------------------------|----------------------|------------------------|--------------------|---------------------------|-------------------|------|------------------------|----------|------|----------|

|        |      | AF0 | AF1    | AF2      | AF3              | AF4      | AF5                            | AF6                  | AF7                    | AF8                | AF9                       | AF10              | AF11 | AF12                   | AF13     |      |          |

| Po     | ort  | SYS | TIM1/2 | TIM3/4/5 | TIM8/9/10<br>/11 | I2C1/2/3 | SPI1/SPI2/<br>I2S2/I2S2e<br>xt | SPI3/I2Sext<br>/I2S3 | USART1/2/3/<br>I2S3ext | UART4/5/<br>USART6 | CAN1/2<br>TIM12/13/<br>14 | OTG_FS/<br>OTG_HS | ЕТН  | FSMC/SDIO<br>/OTG_FS   | DCMI     | AF14 | AF15     |

|        | PD0  | -   | -      | -        | -                | -        | -                              | -                    | -                      | -                  | CAN1_RX                   | -                 | -    | FSMC_D2                | -        | -    | EVENTOUT |

|        | PD1  | -   | -      | -        | -                | -        | -                              | -                    | -                      | -                  | CAN1_TX                   | -                 | -    | FSMC_D3                | -        | -    | EVENTOUT |

|        | PD2  | -   | -      | TIM3_ETR | -                | -        | -                              | -                    | -                      | UART5_RX           | -                         | -                 | -    | SDIO_CMD               | DCMI_D11 | -    | EVENTOUT |

|        | PD3  | -   | -      | -        | -                | -        | -                              | -                    | USART2_CTS             | -                  | -                         | -                 | -    | FSMC_CLK               | -        | -    | EVENTOUT |

|        | PD4  | -   | -      | -        | -                | -        | -                              | -                    | USART2_RTS             | -                  | -                         | -                 | -    | FSMC_NOE               | -        | -    | EVENTOUT |

|        | PD5  | -   | -      | -        | -                | -        | -                              | -                    | USART2_TX              | -                  | -                         | -                 | -    | FSMC_NWE               | -        | -    | EVENTOUT |

|        | PD6  | -   | -      | -        | -                | -        | -                              | -                    | USART2_RX              | -                  | -                         | -                 | -    | FSMC_NWAIT             | -        | -    | EVENTOUT |

| Port D | PD7  | -   | -      | -        | -                | -        | -                              | -                    | USART2_CK              | -                  | -                         | -                 | -    | FSMC_NE1/<br>FSMC_NCE2 | -        | -    | EVENTOUT |

|        | PD8  | -   | -      | -        | -                | -        | -                              | -                    | USART3_TX              | -                  | -                         | -                 | -    | FSMC_D13               | -        | -    | EVENTOUT |

|        | PD9  | -   | -      | -        | -                | -        | -                              | -                    | USART3_RX              | -                  | -                         | -                 | -    | FSMC_D14               | -        | -    | EVENTOUT |

|        | PD10 | -   | -      | -        | -                | -        | -                              | -                    | USART3_CK              | -                  | -                         | -                 | -    | FSMC_D15               | -        | -    | EVENTOUT |

|        | PD11 | -   | -      | -        | -                | -        | -                              | -                    | USART3_CTS             | -                  | -                         | -                 | -    | FSMC_A16               | -        | -    | EVENTOUT |

|        | PD12 | -   | -      | TIM4_CH1 | -                | -        | -                              | -                    | USART3_RTS             | -                  | -                         | -                 | -    | FSMC_A17               | -        | -    | EVENTOUT |

|        | PD13 | -   | -      | TIM4_CH2 | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A18               | -        | -    | EVENTOUT |

|        | PD14 | -   | -      | TIM4_CH3 | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_D0                | -        | -    | EVENTOUT |

|        | PD15 | -   | -      | TIM4_CH4 | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_D1                | -        | -    | EVENTOUT |

#### Table 9. Alternate function mapping (continued)

577

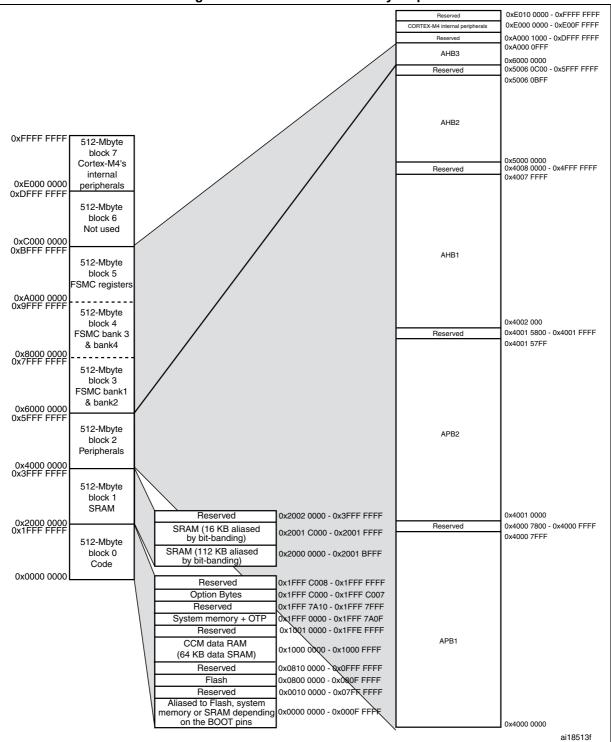

# 4 Memory mapping

The memory map is shown in *Figure 18*.

DocID022152 Rev 8

| Bus  | Boundary address          | Peripheral          |

|------|---------------------------|---------------------|

|      | 0x4000 7800 - 0x4000 7FFF | Reserved            |

|      | 0x4000 7400 - 0x4000 77FF | DAC                 |

|      | 0x4000 7000 - 0x4000 73FF | PWR                 |

|      | 0x4000 6C00 - 0x4000 6FFF | Reserved            |

|      | 0x4000 6800 - 0x4000 6BFF | CAN2                |

|      | 0x4000 6400 - 0x4000 67FF | CAN1                |

|      | 0x4000 6000 - 0x4000 63FF | Reserved            |

|      | 0x4000 5C00 - 0x4000 5FFF | I2C3                |

|      | 0x4000 5800 - 0x4000 5BFF | I2C2                |

|      | 0x4000 5400 - 0x4000 57FF | I2C1                |

|      | 0x4000 5000 - 0x4000 53FF | UART5               |

|      | 0x4000 4C00 - 0x4000 4FFF | UART4               |

|      | 0x4000 4800 - 0x4000 4BFF | USART3              |

|      | 0x4000 4400 - 0x4000 47FF | USART2              |

|      | 0x4000 4000 - 0x4000 43FF | I2S3ext             |

| APB1 | 0x4000 3C00 - 0x4000 3FFF | SPI3 / I2S3         |

|      | 0x4000 3800 - 0x4000 3BFF | SPI2 / I2S2         |

|      | 0x4000 3400 - 0x4000 37FF | I2S2ext             |

|      | 0x4000 3000 - 0x4000 33FF | IWDG                |

|      | 0x4000 2C00 - 0x4000 2FFF | WWDG                |

|      | 0x4000 2800 - 0x4000 2BFF | RTC & BKP Registers |

|      | 0x4000 2400 - 0x4000 27FF | Reserved            |

|      | 0x4000 2000 - 0x4000 23FF | TIM14               |

|      | 0x4000 1C00 - 0x4000 1FFF | TIM13               |

|      | 0x4000 1800 - 0x4000 1BFF | TIM12               |

|      | 0x4000 1400 - 0x4000 17FF | TIM7                |

|      | 0x4000 1000 - 0x4000 13FF | TIM6                |

|      | 0x4000 0C00 - 0x4000 0FFF | TIM5                |

|      | 0x4000 0800 - 0x4000 0BFF | TIM4                |

|      | 0x4000 0400 - 0x4000 07FF | TIM3                |

|      | 0x4000 0000 - 0x4000 03FF | TIM2                |

Table 10. register boundary addresses (continued)

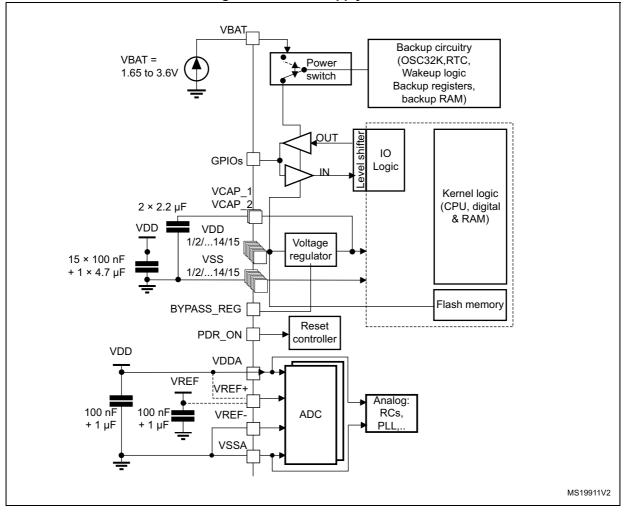

## 5.1.6 Power supply scheme

#### Figure 21. Power supply scheme

1. Each power supply pair must be decoupled with filtering ceramic capacitors as shown above. These capacitors must be placed as close as possible to, or below, the appropriate pins on the underside of the PCB to ensure the good functionality of the device.

- 2. To connect BYPASS\_REG and PDR\_ON pins, refer to Section 2.2.16: Voltage regulator and Table 2.2.15: Power supply supervisor.

- 3. The two 2.2  $\mu F$  ceramic capacitors should be replaced by two 100 nF decoupling capacitors when the voltage regulator is OFF.

- 4. The 4.7  $\mu F$  ceramic capacitor must be connected to one of the  $V_{DD}$  pin.

- 5.  $V_{DDA}=V_{DD}$  and  $V_{SSA}=V_{SS}$ .

| Operating<br>power<br>supply<br>range            | ADC<br>operation                     | Maximum<br>Flash<br>memory<br>access<br>frequency<br>with no wait<br>state<br>(f <sub>Flashmax</sub> ) | Maximum Flash<br>memory access<br>frequency<br>with wait<br>states <sup>(1) (2)</sup> | I/O operation                                                                                  | Clock output<br>Frequency on<br>I/O pins                                                                                                                                                                                                              | Possible<br>Flash<br>memory<br>operations        |

|--------------------------------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| V <sub>DD</sub> =1.8 to<br>2.1 V <sup>(3)</sup>  | Conversion<br>time up to<br>1.2 Msps | 20 MHz <sup>(4)</sup>                                                                                  | 160 MHz with 7<br>wait states                                                         | <ul> <li>Degraded<br/>speed<br/>performance</li> <li>No I/O<br/>compensation</li> </ul>        | up to 30 MHz                                                                                                                                                                                                                                          | 8-bit erase<br>and program<br>operations<br>only |

| V <sub>DD</sub> = 2.1 to<br>2.4 V                | Conversion<br>time up to<br>1.2 Msps | 22 MHz                                                                                                 | 168 MHz with 7<br>wait states                                                         | <ul> <li>Degraded<br/>speed<br/>performance</li> <li>No I/O<br/>compensation</li> </ul>        | up to 30 MHz                                                                                                                                                                                                                                          | 16-bit erase<br>and program<br>operations        |

| V <sub>DD</sub> = 2.4 to<br>2.7 V                | Conversion<br>time up to<br>2.4 Msps | 24 MHz                                                                                                 | 168 MHz with 6<br>wait states                                                         | <ul> <li>Degraded<br/>speed<br/>performance</li> <li>I/O<br/>compensation<br/>works</li> </ul> | up to 48 MHz                                                                                                                                                                                                                                          | 16-bit erase<br>and program<br>operations        |

| V <sub>DD</sub> = 2.7 to<br>3.6 V <sup>(5)</sup> | Conversion<br>time up to<br>2.4 Msps | 30 MHz                                                                                                 | 168 MHz with 5<br>wait states                                                         | <ul> <li>Full-speed<br/>operation</li> <li>I/O<br/>compensation<br/>works</li> </ul>           | $\begin{array}{l} - \text{ up to} \\ 60 \text{ MHz} \\ \text{when } \text{V}_{\text{DD}} = \\ 3.0 \text{ to } 3.6 \text{ V} \\ - \text{ up to} \\ 48 \text{ MHz} \\ \text{when } \text{V}_{\text{DD}} = \\ 2.7 \text{ to } 3.0 \text{ V} \end{array}$ | 32-bit erase<br>and program<br>operations        |

Table 15. Limitations depending on the operating power supply range

1. It applies only when code executed from Flash memory access, when code executed from RAM, no wait state is required.

2. Thanks to the ART accelerator and the 128-bit Flash memory, the number of wait states given here does not impact the execution speed from Flash memory since the ART accelerator allows to achieve a performance equivalent to 0 wait state program execution.

3. V<sub>DD</sub>/VDDA minimum value of 1.7 V is obtained when the device operates in reduced temperature range, and with the use of an external power supply supervisor (refer to *Section : Internal reset OFF*).

4. Prefetch is not available. Refer to AN3430 application note for details on how to adjust performance and power.

5. The voltage range for OTG USB FS can drop down to 2.7 V. However it is degraded between 2.7 and 3 V.

|                        |                     | I <sub>DD</sub> (1       |                           |        |

|------------------------|---------------------|--------------------------|---------------------------|--------|

| Perip                  | heral               | Scale1<br>(up t 168 MHz) | Scale2<br>(up to 144 MHz) | Unit   |

|                        | SDIO                | 7.08                     | 7.92                      |        |

|                        | TIM1                | 16.79                    | 15.51                     |        |

|                        | TIM8                | 17.88                    | 16.53                     |        |

|                        | TIM9                | 7.64                     | 7.28                      |        |

|                        | TIM10               | 4.89                     | 4.82                      |        |

|                        | TIM11               | 5.19                     | 4.82                      |        |

| APB2<br>(up to 84 MHz) | ADC1 <sup>(5)</sup> | 4.67                     | 4.58                      | µA/MHz |

| (up to 04 mil2)        | ADC2 <sup>(5)</sup> | 4.67                     | 4.58                      |        |

|                        | ADC3 <sup>(5)</sup> | 4.43                     | 4.44                      | •      |

|                        | SPI1                | 1.32                     | 1.39                      |        |

|                        | USART1              | 3.51                     | 3.72                      |        |

|                        | USART6              | 3.55                     | 3.75                      | ]      |

|                        | SYSCFG              | 0.74                     | 0.56                      | ]      |

Table 28. Peripheral current consumption (continued)

1. When the I/O compensation cell is ON, I<sub>DD</sub> typical value increases by 0.22 mA.

2. The BusMatrix is automatically active when at least one master is ON.

- 3. To enable an I2S peripheral, first set the I2SMOD bit and then the I2SE bit in the SPI\_I2SCFGR register.

- 4. When the DAC is ON and EN1/2 bits are set in DAC\_CR register, add an additional power consumption of 0.8 mA per DAC channel for the analog part.

- When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.6 mA per ADC for the analog part.

## 5.3.7 Wakeup time from low-power mode

The wakeup times given in *Table 29* is measured on a wakeup phase with a 16 MHz HSI RC oscillator. The clock source used to wake up the device depends from the current operating mode:

- Stop or Standby mode: the clock source is the RC oscillator

- Sleep mode: the clock source is the clock that was set before entering Sleep mode.

All timings are derived from tests performed under ambient temperature and V<sub>DD</sub> supply voltage conditions summarized in *Table 14*.

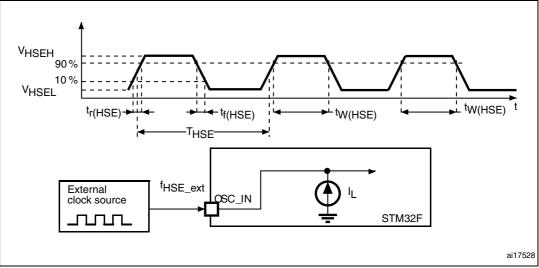

#### Low-speed external user clock generated from an external source

The characteristics given in *Table 31* result from tests performed using an low-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 14*.

| Symbol                                     | Parameter                                              | Conditions                       | Min                | Тур    | Max                | Unit |

|--------------------------------------------|--------------------------------------------------------|----------------------------------|--------------------|--------|--------------------|------|

| f <sub>LSE_ext</sub>                       | User External clock source<br>frequency <sup>(1)</sup> |                                  | -                  | 32.768 | 1000               | kHz  |

| V <sub>LSEH</sub>                          | OSC32_IN input pin high level voltage                  |                                  | 0.7V <sub>DD</sub> | -      | V <sub>DD</sub>    | V    |

| V <sub>LSEL</sub>                          | OSC32_IN input pin low level voltage                   | -                                | V <sub>SS</sub>    | -      | 0.3V <sub>DD</sub> |      |

| t <sub>w(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN high or low time <sup>(1)</sup>               |                                  | 450                | -      | -                  | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN rise or fall time <sup>(1)</sup>              |                                  | -                  | -      | 50                 | 115  |

| C <sub>in(LSE)</sub>                       | OSC32_IN input capacitance <sup>(1)</sup>              | -                                | -                  | 5      | -                  | pF   |

| DuCy <sub>(LSE)</sub>                      | Duty cycle                                             | -                                | 30                 | -      | 70                 | %    |

| ١L                                         | OSC32_IN Input leakage current                         | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -                  | -      | ±1                 | μA   |

| Table 31. Low-speed external user clock characteristics |

|---------------------------------------------------------|

|---------------------------------------------------------|

1. Guaranteed by design.

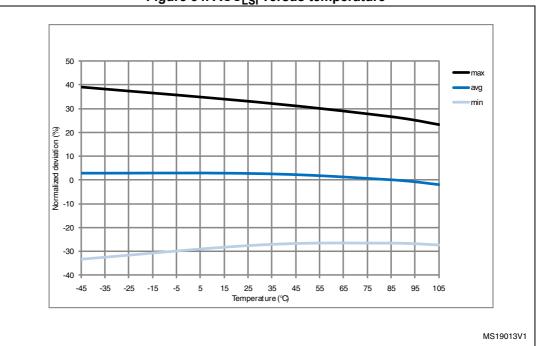

Figure 34. ACC<sub>LSI</sub> versus temperature

# 5.3.10 PLL characteristics

The parameters given in *Table 36* and *Table 37* are derived from tests performed under temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

| Symbol                  | Parameter                             | Conditions         | Min                 | Тур | Max  | Unit |

|-------------------------|---------------------------------------|--------------------|---------------------|-----|------|------|

| f <sub>PLL_IN</sub>     | PLL input clock <sup>(1)</sup>        | -                  | 0.95 <sup>(2)</sup> | 1   | 2.10 | MHz  |

| f <sub>PLL_OUT</sub>    | PLL multiplier output clock           | -                  | 24                  | -   | 168  | MHz  |

| f <sub>PLL48_</sub> OUT | 48 MHz PLL multiplier output<br>clock | -                  | -                   | 48  | 75   | MHz  |

| f <sub>VCO_OUT</sub>    | PLL VCO output                        | -                  | 100                 | -   | 432  | MHz  |

| t                       | PLL lock time                         | VCO freq = 100 MHz | 75                  | -   | 200  | 116  |

| t <sub>lock</sub>       |                                       | VCO freq = 432 MHz | 100                 | -   | 300  | μs   |

Table 36. Main PLL characteristics

| Symbol                          | Parameter                                        | Conditions                   | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit |

|---------------------------------|--------------------------------------------------|------------------------------|--------------------|-----|--------------------|------|

| t <sub>prog</sub>               | Double word programming                          |                              | -                  | 16  | 100 <sup>(2)</sup> | μs   |

| t <sub>ERASE16KB</sub>          | Sector (16 KB) erase time                        | T <sub>A</sub> = 0 to +40 °C | -                  | 230 | -                  |      |

| t <sub>ERASE64KB</sub>          | Sector (64 KB) erase time                        | V <sub>DD</sub> = 3.3 V      | -                  | 490 | -                  | ms   |

| t <sub>ERASE128KB</sub>         | Sector (128 KB) erase time                       | V <sub>PP</sub> = 8.5 V      | -                  | 875 | -                  |      |

| t <sub>ME</sub>                 | Mass erase time                                  |                              | -                  | 6.9 | -                  | S    |

| V <sub>prog</sub>               | Programming voltage                              | -                            | 2.7                | -   | 3.6                | V    |

| V <sub>PP</sub>                 | V <sub>PP</sub> voltage range                    | -                            | 7                  | -   | 9                  | V    |

| I <sub>PP</sub>                 | Minimum current sunk on the $V_{\rm PP}$ pin     | -                            | 10                 | -   | -                  | mA   |

| t <sub>VPP</sub> <sup>(3)</sup> | Cumulative time during which $V_{PP}$ is applied | -                            | -                  | -   | 1                  | hour |

| Table 41. Flash memor | y programming with V <sub>PP</sub> |

|-----------------------|------------------------------------|

|-----------------------|------------------------------------|

1. Guaranteed by design.

2. The maximum programming time is measured after 100K erase operations.

3.  $V_{PP}$  should only be connected during programming/erasing.

| Symbol                          | Parameter                                          | Parameter Conditions Value Min <sup>(1)</sup>                                           |       | Unit    |

|---------------------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------|-------|---------|

| N <sub>END</sub>                | Endurance                                          | $T_A = -40$ to +85 °C (6 suffix versions)<br>$T_A = -40$ to +105 °C (7 suffix versions) | 10    | kcycles |

|                                 |                                                    | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C                                       | 30    |         |

| t <sub>RET</sub> Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C | 10                                                                                      | Years |         |

|                                 |                                                    | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 55 °C                                     | 20    |         |

#### Table 42. Flash memory endurance and data retention

1. Guaranteed by characterization.

2. Cycling performed over the whole temperature range.

#### 5.3.13 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

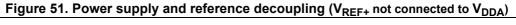

#### General PCB design guidelines

Power supply decoupling should be performed as shown in *Figure 51* or *Figure 52*, depending on whether  $V_{REF+}$  is connected to  $V_{DDA}$  or not. The 10 nF capacitors should be ceramic (good quality). They should be placed them as close as possible to the chip.

1.  $V_{REF+}$  and  $V_{REF-}$  inputs are both available on UFBGA176.  $V_{REF+}$  is also available on LQFP100, LQFP144, and LQFP176. When  $V_{REF+}$  and  $V_{REF-}$  are not available, they are internally connected to  $V_{DDA}$  and  $V_{SSA}$ .

| Symbol                             | Parameter                                                                                                                                                          | Min | Тур | Мах  | Unit | Comments                                                                                                                                                                         |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Offset <sup>(4)</sup>              | Offset error<br>(difference between<br>measured value at Code<br>(0x800) and the ideal value<br>= V <sub>REF+</sub> /2)                                            | -   | -   | ±10  | mV   | Given for the DAC in 12-bit configuration                                                                                                                                        |

|                                    |                                                                                                                                                                    | -   | -   | ±3   | LSB  | Given for the DAC in 10-bit at $V_{REF+}$ = 3.6 V                                                                                                                                |

|                                    |                                                                                                                                                                    | -   | -   | ±12  | LSB  | Given for the DAC in 12-bit at $V_{REF+}$ = 3.6 V                                                                                                                                |

| Gain<br>error <sup>(4)</sup>       | Gain error                                                                                                                                                         | -   | -   | ±0.5 | %    | Given for the DAC in 12-bit configuration                                                                                                                                        |

| tsettling <sup>(4)</sup>           | Settling time (full scale: for a<br>10-bit input code transition<br>between the lowest and the<br>highest input codes when<br>DAC_OUT reaches final<br>value ±4LSB | -   | 3   | 6    | μs   | $C_{LOAD} \le 50 \text{ pF},$<br>$R_{LOAD} \ge 5 \text{ k}\Omega$                                                                                                                |

| THD <sup>(4)</sup>                 | Total Harmonic Distortion<br>Buffer ON                                                                                                                             | -   | -   | -    | dB   | $\begin{array}{l} C_{LOAD} \leq 50 \text{ pF}, \\ R_{LOAD} \geq 5  k\Omega \end{array}$                                                                                          |

| Update<br>rate <sup>(2)</sup>      | Max frequency for a correct<br>DAC_OUT change when<br>small variation in the input<br>code (from code i to i+1LSB)                                                 | -   | -   | 1    | MS/s | $C_{LOAD} \le 50 \text{ pF},$<br>$R_{LOAD} \ge 5 \text{ k}\Omega$                                                                                                                |

| t <sub>WAKEUP</sub> <sup>(4)</sup> | Wakeup time from off state<br>(Setting the ENx bit in the<br>DAC Control register)                                                                                 | -   | 6.5 | 10   | μs   | $\label{eq:loss} \begin{array}{l} C_{LOAD} \leq 50 \text{ pF}, \ R_{LOAD} \geq 5 \ k\Omega \\ \text{input code between lowest and} \\ \text{highest possible ones.} \end{array}$ |

| PSRR+ <sup>(2)</sup>               | Power supply rejection ratio<br>(to V <sub>DDA</sub> ) (static DC<br>measurement)                                                                                  | -   | -67 | -40  | dB   | No R <sub>LOAD</sub> , C <sub>LOAD</sub> = 50 pF                                                                                                                                 |

V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V is obtained when the device operates in reduced temperature range, and with the use of an external power supply supervisor (refer to Section : Internal reset OFF).

2. Guaranteed by design.

3. The quiescent mode corresponds to a state where the DAC maintains a stable output level to ensure that no dynamic consumption occurs.

4. Guaranteed by characterization.

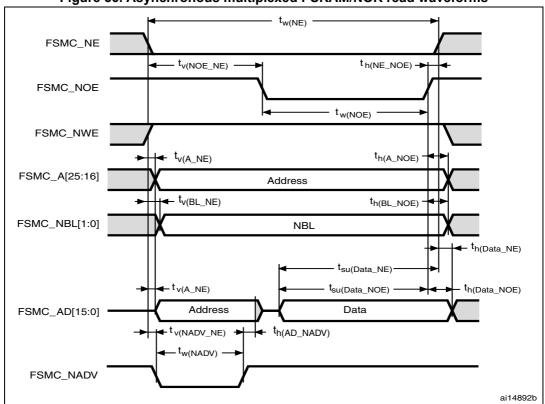

Figure 56. Asynchronous multiplexed PSRAM/NOR read waveforms

## Table 77. Asynchronous multiplexed PSRAM/NOR read timings<sup>(1)(2)</sup>

| Symbol                    | Parameter                                                                     | Min                     | Мах                     | Unit |

|---------------------------|-------------------------------------------------------------------------------|-------------------------|-------------------------|------|

| t <sub>w(NE)</sub>        | FSMC_NE low time                                                              | 3T <sub>HCLK</sub> –1   | 3T <sub>HCLK</sub> +1   | ns   |

| t <sub>v(NOE_NE)</sub>    | FSMC_NEx low to FSMC_NOE low                                                  | 2T <sub>HCLK</sub> -0.5 | 2T <sub>HCLK</sub> +0.5 | ns   |

| t <sub>w(NOE)</sub>       | FSMC_NOE low time                                                             | T <sub>HCLK</sub> –1    | T <sub>HCLK</sub> +1    | ns   |

| t <sub>h(NE_NOE)</sub>    | FSMC_NOE high to FSMC_NE high hold time                                       | 0                       | -                       | ns   |

| t <sub>v(A_NE)</sub>      | FSMC_NEx low to FSMC_A valid                                                  | -                       | 3                       | ns   |

| t <sub>v(NADV_NE)</sub>   | FSMC_NEx low to FSMC_NADV low                                                 | 1                       | 2                       | ns   |

| t <sub>w(NADV)</sub>      | (NADV) FSMC_NADV low time                                                     |                         | T <sub>HCLK</sub> +1    | ns   |

| t <sub>h(AD_NADV)</sub>   | t <sub>h(AD_NADV)</sub> FSMC_AD(adress) valid hold time after FSMC_NADV high) |                         | -                       | ns   |

| t <sub>h(A_NOE)</sub>     | (A_NOE) Address hold time after FSMC_NOE high                                 |                         | -                       | ns   |

| t <sub>h(BL_NOE)</sub>    | t <sub>h(BL_NOE)</sub> FSMC_BL time after FSMC_NOE high                       |                         | -                       | ns   |

| t <sub>v(BL_NE)</sub>     | FSMC_NEx low to FSMC_BL valid                                                 | -                       | 2                       | ns   |

| t <sub>su(Data_NE)</sub>  | su(Data_NE) Data to FSMC_NEx high setup time                                  |                         | -                       | ns   |

| t <sub>su(Data_NOE)</sub> | u(Data_NOE) Data to FSMC_NOE high setup time                                  |                         | -                       | ns   |

| t <sub>h(Data_NE)</sub>   | Data hold time after FSMC_NEx high                                            | 0                       | -                       | ns   |

| t <sub>h(Data_NOE)</sub>  | _NOE) Data hold time after FSMC_NOE high                                      |                         | -                       | ns   |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization.

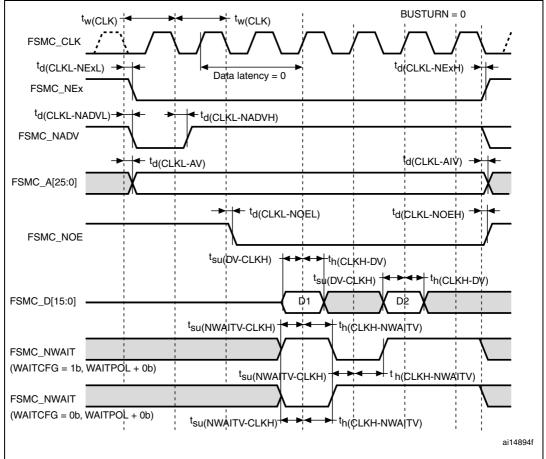

| Symbol                          | Parameter                             | Min | Max | Unit |

|---------------------------------|---------------------------------------|-----|-----|------|

| t <sub>d(CLKL-NBLH)</sub>       | FSMC_CLK low to FSMC_NBL high         | 0   | -   | ns   |

| t <sub>su(NWAIT-</sub><br>CLKH) | FSMC_NWAIT valid before FSMC_CLK high | 4   | -   | ns   |

| t <sub>h(CLKH-NWAIT)</sub>      | FSMC_NWAIT valid after FSMC_CLK high  | 0   | -   | ns   |

Table 80. Synchronous multiplexed PSRAM write timings<sup>(1)(2)</sup> (continued)

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization.

## Figure 60. Synchronous non-multiplexed NOR/PSRAM read timings

| Dimension      | Recommended values                            |  |  |  |

|----------------|-----------------------------------------------|--|--|--|

| Pitch          | 0.4 mm                                        |  |  |  |

| Dpad           | 260 μm max. (circular)<br>220 μm recommended  |  |  |  |

| Dsm            | 300 µm min. (for 260 µm diameter pad)         |  |  |  |

| PCB pad design | Non-solder mask defined via underbump allowed |  |  |  |

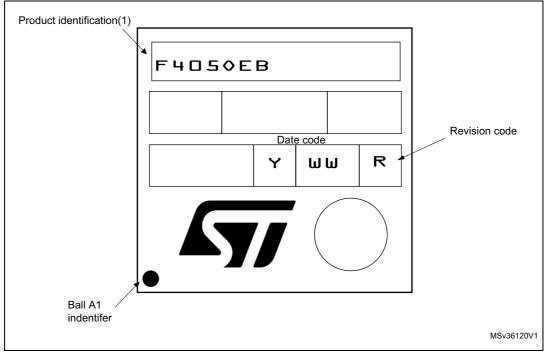

#### **Device marking for WLCSP90**

The following figure gives an example of topside marking and ball A1 position identifier location.

Other optional marking or inset/upset marks, which depend on supply chain operations, are not indicated below.

Figure 77. WLCSP90 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.