#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                  |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                           |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 168MHz                                                                    |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT         |

| Number of I/O              | 114                                                                       |

| Program Memory Size        | 1MB (1M x 8)                                                              |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 192K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                     |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 144-LQFP                                                                  |

| Supplier Device Package    | 144-LQFP (20x20)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f405zgt6j    |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- 8- to 14-bit parallel camera interface up to 54 Mbytes/s

- 96-bit unique ID

- RTC: subsecond accuracy, hardware calendar

- True random number generator

- CRC calculation unit

## Table 1. Device summary

| Reference   | Part number                                                                     |

|-------------|---------------------------------------------------------------------------------|

| STM32F405xx | STM32F405RG, STM32F405VG, STM32F405ZG, STM32F405OG, STM32F405OE                 |

| STM32F407xx | STM32F407VG, STM32F407IG, STM32F407ZG,<br>STM32F407VE, STM32F407ZE, STM32F407IE |

clock entry is available when necessary (for example if an indirectly used external oscillator fails).

Several prescalers allow the configuration of the three AHB buses, the high-speed APB (APB2) and the low-speed APB (APB1) domains. The maximum frequency of the three AHB buses is 168 MHz while the maximum frequency of the high-speed APB domains is 84 MHz. The maximum allowed frequency of the low-speed APB domain is 42 MHz.

The devices embed a dedicated PLL (PLLI2S) which allows to achieve audio class performance. In this case, the  $I^2S$  master clock can generate all standard sampling frequencies from 8 kHz to 192 kHz.

### 2.2.13 Boot modes

At startup, boot pins are used to select one out of three boot options:

- Boot from user Flash

- Boot from system memory

- Boot from embedded SRAM

The boot loader is located in system memory. It is used to reprogram the Flash memory by using USART1 (PA9/PA10), USART3 (PC10/PC11 or PB10/PB11), CAN2 (PB5/PB13), USB OTG FS in Device mode (PA11/PA12) through DFU (device firmware upgrade).

#### 2.2.14 **Power supply schemes**

- V<sub>DD</sub> = 1.8 to 3.6 V: external power supply for I/Os and the internal regulator (when enabled), provided externally through V<sub>DD</sub> pins.

- V<sub>SSA</sub>, V<sub>DDA</sub> = 1.8 to 3.6 V: external analog power supplies for ADC, DAC, Reset blocks, RCs and PLL. V<sub>DDA</sub> and V<sub>SSA</sub> must be connected to V<sub>DD</sub> and V<sub>SS</sub>, respectively.

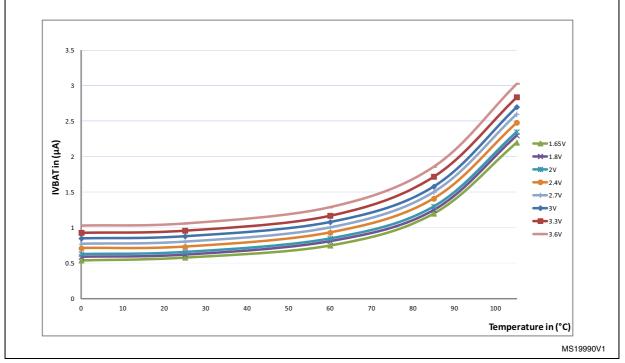

- V<sub>BAT</sub> = 1.65 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

Refer to Figure 21: Power supply scheme for more details.

Note:  $V_{DD}/V_{DDA}$  minimum value of 1.7 V is obtained when the device operates in reduced temperature range, and with the use of an external power supply supervisor (refer to Section : Internal reset OFF).

Refer to Table 2 in order to identify the packages supporting this option.

## 2.2.15 **Power supply supervisor**

#### Internal reset ON

On packages embedding the PDR\_ON pin, the power supply supervisor is enabled by holding PDR\_ON high. On all other packages, the power supply supervisor is always enabled.

The device has an integrated power-on reset (POR) / power-down reset (PDR) circuitry coupled with a Brownout reset (BOR) circuitry. At power-on, POR/PDR is always active and ensures proper operation starting from 1.8 V. After the 1.8 V POR threshold level is reached, the option byte loading process starts, either to confirm or modify default BOR threshold levels, or to disable BOR permanently. Three BOR thresholds are available through option bytes. The device remains in reset mode when V<sub>DD</sub> is below a specified threshold, V<sub>POR/PDR</sub> or V<sub>BOR</sub>, without the need for an external reset circuit.

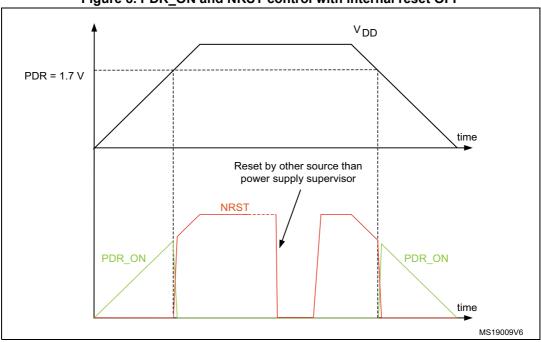

Figure 8. PDR\_ON and NRST control with internal reset OFF

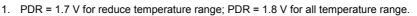

## 2.2.16 Voltage regulator

The regulator has four operating modes:

- Regulator ON

- Main regulator mode (MR)

- Low-power regulator (LPR)

- Power-down

- Regulator OFF

#### **Regulator ON**

On packages embedding the BYPASS\_REG pin, the regulator is enabled by holding BYPASS\_REG low. On all other packages, the regulator is always enabled.

There are three power modes configured by software when regulator is ON:

- MR is used in the nominal regulation mode (With different voltage scaling in Run) In Main regulator mode (MR mode), different voltage scaling are provided to reach the best compromise between maximum frequency and dynamic power consumption. Refer to *Table 14: General operating conditions*.

- LPR is used in the Stop modes

The LP regulator mode is configured by software when entering Stop mode.

- Power-down is used in Standby mode.

- The Power-down mode is activated only when entering in Standby mode. The regulator output is in high impedance and the kernel circuitry is powered down, inducing zero consumption. The contents of the registers and SRAM are lost)

Two external ceramic capacitors should be connected on V<sub>CAP\_1</sub> & V<sub>CAP\_2</sub> pin. Refer to *Figure 21: Power supply scheme* and *Figure 16: VCAP\_1/VCAP\_2 operating conditions*.

All packages have regulator ON feature.

#### **Regulator OFF**

This feature is available only on packages featuring the BYPASS\_REG pin. The regulator is disabled by holding BYPASS\_REG high. The regulator OFF mode allows to supply externally a  $V_{12}$  voltage source through  $V_{CAP_1}$  and  $V_{CAP_2}$  pins.

Since the internal voltage scaling is not manage internally, the external voltage value must be aligned with the targeted maximum frequency. Refer to *Table 14: General operating conditions*.

The two 2.2  $\mu\text{F}$  ceramic capacitors should be replaced by two 100 nF decoupling capacitors.

Refer to Figure 21: Power supply scheme

When the regulator is OFF, there is no more internal monitoring on  $V_{12}$ . An external power supply supervisor should be used to monitor the  $V_{12}$  of the logic power domain. PA0 pin should be used for this purpose, and act as power-on reset on  $V_{12}$  power domain.

In regulator OFF mode the following features are no more supported:

- PA0 cannot be used as a GPIO pin since it allows to reset a part of the V<sub>12</sub> logic power domain which is not reset by the NRST pin.

- As long as PA0 is kept low, the debug mode cannot be used under power-on reset. As a consequence, PA0 and NRST pins must be managed separately if the debug connection under reset or pre-reset is required.

- The standby mode is not available

#### Figure 9. Regulator OFF

## 2.2.31 Universal serial bus on-the-go high-speed (OTG\_HS)

The STM32F405xx and STM32F407xx devices embed a USB OTG high-speed (up to 480 Mb/s) device/host/OTG peripheral. The USB OTG HS supports both full-speed and high-speed operations. It integrates the transceivers for full-speed operation (12 MB/s) and features a UTMI low-pin interface (ULPI) for high-speed operation (480 MB/s). When using the USB OTG HS in HS mode, an external PHY device connected to the ULPI is required.

The USB OTG HS peripheral is compliant with the USB 2.0 specification and with the OTG 1.0 specification. It has software-configurable endpoint setting and supports suspend/resume. The USB OTG full-speed controller requires a dedicated 48 MHz clock that is generated by a PLL connected to the HSE oscillator.

The major features are:

- Combined Rx and Tx FIFO size of 1 Kbit × 35 with dynamic FIFO sizing

- Supports the session request protocol (SRP) and host negotiation protocol (HNP)

- 6 bidirectional endpoints

- 12 host channels with periodic OUT support

- Internal FS OTG PHY support

- External HS or HS OTG operation supporting ULPI in SDR mode. The OTG PHY is connected to the microcontroller ULPI port through 12 signals. It can be clocked using the 60 MHz output.

- Internal USB DMA

- HNP/SNP/IP inside (no need for any external resistor)

- for OTG/Host modes, a power switch is needed in case bus-powered devices are connected

## 2.2.32 Digital camera interface (DCMI)

The camera interface is *not* available in STM32F405xx devices.

STM32F407xx products embed a camera interface that can connect with camera modules and CMOS sensors through an 8-bit to 14-bit parallel interface, to receive video data. The camera interface can sustain a data transfer rate up to 54 Mbyte/s at 54 MHz. It features:

- Programmable polarity for the input pixel clock and synchronization signals

- Parallel data communication can be 8-, 10-, 12- or 14-bit

- Supports 8-bit progressive video monochrome or raw bayer format, YCbCr 4:2:2 progressive video, RGB 565 progressive video or compressed data (like JPEG)

- Supports continuous mode or snapshot (a single frame) mode

- Capability to automatically crop the image

## 2.2.33 Random number generator (RNG)

All STM32F405xx and STM32F407xx products embed an RNG that delivers 32-bit random numbers generated by an integrated analog circuit.

## 2.2.34 General-purpose input/outputs (GPIOs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain, with or without pull-up or pull-down), as input (floating, with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog

|        | I       | Pin r   | numb    |          |         |                                                      |          |                 |       | definitions (continued)                                                          |                         |

|--------|---------|---------|---------|----------|---------|------------------------------------------------------|----------|-----------------|-------|----------------------------------------------------------------------------------|-------------------------|

| LQFP64 | WLCSP90 | LQFP100 | LQFP144 | UFBGA176 | LQFP176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes | Alternate functions                                                              | Additional<br>functions |

| -      | -       | 60      | 82      | M15      | 101     | PD13                                                 | I/O      | FT              | -     | FSMC_A18/TIM4_CH2/<br>EVENTOUT                                                   | -                       |

| -      | -       | -       | 83      | -        | 102     | V <sub>SS</sub>                                      | S        |                 | -     | -                                                                                | -                       |

| -      | -       | -       | 84      | J13      | 103     | V <sub>DD</sub>                                      | S        |                 | -     | -                                                                                | -                       |

| -      | F2      | 61      | 85      | M14      | 104     | PD14                                                 | I/O      | FT              | -     | FSMC_D0/TIM4_CH3/<br>EVENTOUT/ EVENTOUT                                          | -                       |

| -      | F1      | 62      | 86      | L14      | 105     | PD15                                                 | I/O      | FT              | -     | FSMC_D1/TIM4_CH4/<br>EVENTOUT                                                    | -                       |

| -      | -       | -       | 87      | L15      | 106     | PG2                                                  | I/O      | FT              | -     | FSMC_A12/ EVENTOUT                                                               | -                       |

| -      | -       | -       | 88      | K15      | 107     | PG3                                                  | I/O      | FT              | -     | FSMC_A13/ EVENTOUT                                                               | -                       |

| -      | -       | -       | 89      | K14      | 108     | PG4                                                  | I/O      | FT              | -     | FSMC_A14/ EVENTOUT                                                               | -                       |

| -      | -       | -       | 90      | K13      | 109     | PG5                                                  | I/O      | FT              | -     | FSMC_A15/ EVENTOUT                                                               | -                       |

| -      | -       | -       | 91      | J15      | 110     | PG6                                                  | I/O      | FT              | -     | FSMC_INT2/ EVENTOUT                                                              | -                       |

| -      | -       | -       | 92      | J14      | 111     | PG7                                                  | I/O      | FT              | -     | FSMC_INT3/USART6_CK/<br>EVENTOUT                                                 | -                       |

| -      | -       | -       | 93      | H14      | 112     | PG8                                                  | I/O      | FT              | -     | USART6_RTS /<br>ETH_PPS_OUT/<br>EVENTOUT                                         | -                       |

| -      | -       | -       | 94      | G12      | 113     | V <sub>SS</sub>                                      | S        |                 | -     | -                                                                                | -                       |

| -      | -       | -       | 95      | H13      | 114     | V <sub>DD</sub>                                      | S        |                 | -     | -                                                                                | -                       |

| 37     | F3      | 63      | 96      | H15      | 115     | PC6                                                  | I/O      | FT              | -     | I2S2_MCK /<br>TIM8_CH1/SDIO_D6 /<br>USART6_TX /<br>DCMI_D0/TIM3_CH1/<br>EVENTOUT | -                       |

| 38     | E1      | 64      | 97      | G15      | 116     | PC7                                                  | I/O      | FT              | -     | I2S3_MCK /<br>TIM8_CH2/SDIO_D7 /<br>USART6_RX /<br>DCMI_D1/TIM3_CH2/<br>EVENTOUT | -                       |

| 39     | E2      | 65      | 98      | G14      | 117     | PC8                                                  | I/O      | FT              | -     | TIM8_CH3/SDIO_D0<br>/TIM3_CH3/ USART6_CK /<br>DCMI_D2/ EVENTOUT                  | -                       |

Table 7. STM32F40xxx pin and ball definitions (continued)

|        |      |     |        |          |                  | Tab      | Die 9. Alt                     | ernate it            | inction m              | apping             | (contin                   | uea)              |                                       |                              |          |      |          |

|--------|------|-----|--------|----------|------------------|----------|--------------------------------|----------------------|------------------------|--------------------|---------------------------|-------------------|---------------------------------------|------------------------------|----------|------|----------|

|        |      | AF0 | AF1    | AF2      | AF3              | AF4      | AF5                            | AF6                  | AF7                    | AF8                | AF9                       | AF10              | AF11                                  | AF12                         | AF13     |      |          |

| P      | ort  | SYS | TIM1/2 | TIM3/4/5 | TIM8/9/10<br>/11 | I2C1/2/3 | SPI1/SPI2/<br>I2S2/I2S2e<br>xt | SPI3/I2Sext<br>/I2S3 | USART1/2/3/<br>I2S3ext | UART4/5/<br>USART6 | CAN1/2<br>TIM12/13/<br>14 | OTG_FS/<br>OTG_HS | ETH                                   | FSMC/SDIO<br>/OTG_FS         | DCMI     | AF14 | AF15     |

|        | PG0  | -   | -      | -        | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | -                                     | FSMC_A10                     | -        | -    | EVENTOUT |

|        | PG1  | -   | -      | -        | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | -                                     | FSMC_A11                     | -        | -    | EVENTOUT |

|        | PG2  | -   | -      | -        | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | -                                     | FSMC_A12                     | -        | -    | EVENTOUT |

|        | PG3  | -   | -      | -        | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | -                                     | FSMC_A13                     | -        | -    | EVENTOUT |

|        | PG4  | -   | -      | -        | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | -                                     | FSMC_A14                     | -        | -    | EVENTOUT |

|        | PG5  | -   | -      | -        | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | -                                     | FSMC_A15                     | -        | -    | EVENTOUT |

|        | PG6  | -   | -      | -        | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | -                                     | FSMC_INT2                    | -        | -    | EVENTOUT |

|        | PG7  | -   | -      | -        | -                | -        | -                              | -                    | -                      | USART6_CK          | -                         | -                 | -                                     | FSMC_INT3                    | -        | -    | EVENTOUT |

|        | PG8  | -   | -      | -        | -                | -        | -                              | -                    | -                      | USART6_<br>RTS     | -                         | -                 | ETH_PPS_OUT                           | -                            | -        | -    | EVENTOUT |

| Port G | PG9  | -   | -      | -        | -                | -        | -                              | -                    | -                      | USART6_RX          | -                         | -                 | -                                     | FSMC_NE2/<br>FSMC_NCE3       | -        | -    | EVENTOUT |

|        | PG10 | -   | -      | -        | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | -                                     | FSMC_<br>NCE4_1/<br>FSMC_NE3 | -        | -    | EVENTOUT |

|        | PG11 | -   | -      | -        | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | ETH _MII_TX_EN<br>ETH _RMII_<br>TX_EN | FSMC_NCE4_<br>2              | -        | -    | EVENTOUT |

|        | PG12 | -   | -      | -        | -                | -        | -                              | -                    | -                      | USART6_<br>RTS     | -                         | -                 | -                                     | FSMC_NE4                     | -        | -    | EVENTOUT |

|        | PG13 | -   | -      | -        | -                | -        | -                              | -                    | -                      | UART6_CTS          | -                         | -                 | ETH _MII_TXD0<br>ETH _RMII_TXD0       | FSMC_A24                     | -        | -    | EVENTOUT |

|        | PG14 | -   | -      | -        | -                | -        | -                              | -                    | -                      | USART6_TX          | -                         | -                 | ETH_MII_TXD1<br>ETH_RMII_TXD1         | FSMC_A25                     | -        | -    | EVENTOUT |

|        | PG15 | -   | -      | -        | -                | -        | -                              | -                    | -                      | USART6_<br>CTS     | -                         | -                 | -                                     | -                            | DCMI_D13 | -    | EVENTOUT |

#### Table 9. Alternate function mapping (continued)

DocID022152 Rev 8

57

68/202

STM32F405xx, STM32F407xx

Pinouts and pin description

|                 |                   |                                                                            |                       | Тур                       | Ма                        | x <sup>(2)</sup>           |      |

|-----------------|-------------------|----------------------------------------------------------------------------|-----------------------|---------------------------|---------------------------|----------------------------|------|

| Symbol          | Parameter         | Conditions                                                                 | fhclk                 | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |

|                 |                   |                                                                            | 168 MHz               | 87                        | 102                       | 109                        |      |

|                 |                   |                                                                            | 144 MHz               | 67                        | 80                        | 86                         |      |

|                 |                   |                                                                            | 120 MHz               | 56                        | 69                        | 75                         |      |

|                 |                   |                                                                            | 90 MHz                | 44                        | 56                        | 62                         |      |

|                 |                   | - (2)                                                                      | 60 MHz                | 30                        | 42                        | 49                         |      |

|                 |                   | External clock <sup>(3)</sup> , all peripherals enabled <sup>(4)(5)</sup>  | 30 MHz                | 16                        | 28                        | 35                         |      |

|                 |                   |                                                                            | 25 MHz                | 12                        | 24                        | 31                         |      |

|                 |                   |                                                                            | 16 MHz <sup>(6)</sup> | 9                         | 20                        | 28                         | mA   |

|                 |                   |                                                                            | 8 MHz                 | 5                         | 17                        | 24                         |      |

|                 |                   |                                                                            | 4 MHz                 | 3                         | 15                        | 22                         |      |

|                 | Supply current in |                                                                            | 2 MHz                 | 2                         | 14                        | 21                         |      |

| I <sub>DD</sub> | Run mode          |                                                                            | 168 MHz               | 40                        | 54                        | 61                         |      |

|                 |                   |                                                                            | 144 MHz               | 31                        | 43                        | 50                         |      |

|                 |                   |                                                                            | 120 MHz               | 26                        | 38                        | 45                         |      |

|                 |                   |                                                                            | 90 MHz                | 20                        | 32                        | 39                         |      |

|                 |                   | - (2)                                                                      | 60 MHz                | 14                        | 26                        | 33                         |      |

|                 |                   | External clock <sup>(3)</sup> , all peripherals disabled <sup>(4)(5)</sup> | 30 MHz                | 8                         | 20                        | 27                         |      |

|                 |                   |                                                                            | 25 MHz                | 6                         | 18                        | 25                         |      |

|                 |                   |                                                                            | 16 MHz <sup>(6)</sup> | 5                         | 16                        | 24                         |      |

|                 |                   |                                                                            | 8 MHz                 | 3                         | 15                        | 22                         |      |

|                 |                   |                                                                            | 4 MHz                 | 2                         | 14                        | 21                         |      |

|                 |                   |                                                                            | 2 MHz                 | 2                         | 14                        | 21                         |      |

# Table 20. Typical and maximum current consumption in Run mode, code with data processing running from Flash memory (ART accelerator enabled) or RAM <sup>(1)</sup>

1. Code and data processing running from SRAM1 using boot pins.

2. Guaranteed by characterization, tested in production at V<sub>DD</sub> max and f<sub>HCLK</sub> max with peripherals enabled.

3. External clock is 4 MHz and PLL is on when  $f_{HCLK}$  > 25 MHz.

4. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.6 mA per ADC for the analog part.

5. When analog peripheral blocks such as ADCs, DACs, HSE, LSE, HSI, or LSI are ON, an additional power consumption should be considered.

6. In this case HCLK = system clock/2.

|                          |                                       |                                                  |                                | Тур                         |                                | Ма                        |      |    |

|--------------------------|---------------------------------------|--------------------------------------------------|--------------------------------|-----------------------------|--------------------------------|---------------------------|------|----|

| Symbol                   | Parameter                             | Conditions                                       | г                              | -<br>A = 25 °               | С                              | T <sub>A</sub> =<br>85 °C | Unit |    |

|                          |                                       |                                                  | V <sub>BAT</sub><br>=<br>1.8 V | V <sub>BAT</sub> =<br>2.4 V | V <sub>BAT</sub><br>=<br>3.3 V | V <sub>BAT</sub> = 3.6 V  |      |    |

|                          | Pookup                                | Backup SRAM ON, low-speed oscillator and RTC ON  | 1.29                           | 1.42                        | 1.68                           | 6                         | 11   |    |

| I <sub>DD_VBA</sub><br>T | Backup<br>domain<br>supply<br>current | Backup SRAM OFF, low-speed oscillator and RTC ON | 0.62                           | 0.73                        | 0.96                           | 3                         | 5    | μA |

|                          |                                       | Backup SRAM ON, RTC OFF                          | 0.79                           | 0.81                        | 0.86                           | 5                         | 10   |    |

|                          |                                       | Backup SRAM OFF, RTC OFF                         | 0.10                           | 0.10                        | 0.10                           | 2                         | 4    |    |

| Table 25. Typical and maximum current consumptions in V <sub>BAT</sub> mode |

|-----------------------------------------------------------------------------|

|-----------------------------------------------------------------------------|

1. Guaranteed by characterization.

| Symbol | Parameter     | Conditions <sup>(1)</sup>                                  | l/O toggling<br>frequency (f <sub>SW</sub> ) | Тур  | Unit |

|--------|---------------|------------------------------------------------------------|----------------------------------------------|------|------|

|        |               |                                                            | 2 MHz                                        | 0.02 |      |

|        |               | $V_{DD} = 3.3 V^{(2)}$                                     | 8 MHz                                        | 0.14 | -    |

|        |               | $C = C_{INT}$                                              | 25 MHz                                       | 0.51 |      |

|        |               |                                                            | 50 MHz                                       | 0.86 |      |

|        |               |                                                            | 60 MHz                                       | 1.30 |      |

|        |               |                                                            | 2 MHz                                        | 0.10 |      |

|        |               | V <sub>DD</sub> = 3.3 V                                    | 8 MHz                                        | 0.38 |      |

|        |               | C <sub>EXT</sub> = 0 pF                                    | 25 MHz                                       | 1.18 |      |

|        |               | $C = C_{INT} + C_{EXT} + C_S$                              | 50 MHz                                       | 2.47 | mA   |

|        |               |                                                            | 60 MHz                                       | 2.86 |      |

|        |               |                                                            | 2 MHz                                        | 0.17 |      |

|        | I/O switching | V <sub>DD</sub> = 3.3 V                                    | 8 MHz                                        | 0.66 |      |

| IDDIO  | current       | $C_{EXT} = 10 \text{ pF}$<br>$C = C_{INT} + C_{EXT} + C_S$ | 25 MHz                                       | 1.70 |      |

|        |               |                                                            | 50 MHz                                       | 2.65 |      |

|        |               |                                                            | 60 MHz                                       | 3.48 |      |

|        |               |                                                            | 2 MHz                                        | 0.23 |      |

|        |               | V <sub>DD</sub> = 3.3 V                                    | 8 MHz                                        | 0.95 |      |

|        |               | C <sub>EXT</sub> = 22 pF                                   | 25 MHz                                       | 3.20 |      |

|        |               | $C = C_{INT} + C_{EXT} + C_S$                              | 50 MHz                                       | 4.69 |      |

|        |               |                                                            | 60 MHz                                       | 8.06 |      |

|        |               |                                                            | 2 MHz                                        | 0.30 | 1    |

|        |               | V <sub>DD</sub> = 3.3 V                                    | 8 MHz                                        | 1.22 |      |

|        |               | C <sub>EXT</sub> = 33 pF                                   | 25 MHz                                       | 3.90 | -    |

|        |               | $C = C_{INT} + C_{EXT} + C_S$                              | 50 MHz                                       | 8.82 |      |

|        |               |                                                            | 60 MHz                                       | _(3) |      |

1.  $C_S$  is the PCB board capacitance including the pad pin.  $C_S$  = 7 pF (estimated value).

2. This test is performed by cutting the LQFP package pin (pad removal).

3. At 60 MHz, C maximum load is specified 30 pF.

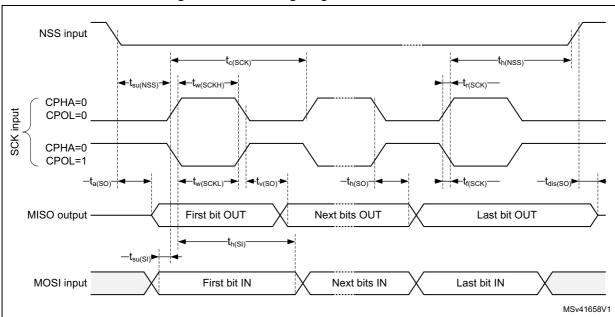

Figure 39. SPI timing diagram - slave mode and CPHA = 0

| Symbol                      | Parameter                                      | Min                | Мах | Unit |

|-----------------------------|------------------------------------------------|--------------------|-----|------|

| t <sub>w(CLK)</sub>         | FSMC_CLK period                                | 2T <sub>HCLK</sub> | -   | ns   |

| t <sub>d(CLKL-NExL)</sub>   | FSMC_CLK low to FSMC_NEx low (x=02)            | -                  | 0   | ns   |

| t <sub>d(CLKL-NExH)</sub>   | FSMC_CLK low to FSMC_NEx high (x= 02)          | 2                  | -   | ns   |

| t <sub>d(CLKL-NADVL)</sub>  | FSMC_CLK low to FSMC_NADV low                  | -                  | 2   | ns   |

| t <sub>d(CLKL-NADVH)</sub>  | FSMC_CLK low to FSMC_NADV high                 | 2                  | -   | ns   |

| t <sub>d(CLKL-AV)</sub>     | FSMC_CLK low to FSMC_Ax valid (x=1625)         | -                  | 0   | ns   |

| t <sub>d(CLKL-AIV)</sub>    | FSMC_CLK low to FSMC_Ax invalid (x=1625)       | 0                  | -   | ns   |

| t <sub>d(CLKL-NOEL)</sub>   | FSMC_CLK low to FSMC_NOE low                   | -                  | 0   | ns   |

| t <sub>d(CLKL-NOEH)</sub>   | FSMC_CLK low to FSMC_NOE high                  | 2                  | -   | ns   |

| t <sub>d(CLKL-ADV)</sub>    | FSMC_CLK low to FSMC_AD[15:0] valid            | -                  | 4.5 | ns   |

| t <sub>d(CLKL-ADIV)</sub>   | FSMC_CLK low to FSMC_AD[15:0] invalid          | 0                  | -   | ns   |

| t <sub>su(ADV-CLKH)</sub>   | FSMC_A/D[15:0] valid data before FSMC_CLK high | 6                  | -   | ns   |

| t <sub>h(CLKH-ADV)</sub>    | FSMC_A/D[15:0] valid data after FSMC_CLK high  | 0                  | -   | ns   |

| t <sub>su(NWAIT-CLKH)</sub> | FSMC_NWAIT valid before FSMC_CLK high          | 4                  | -   | ns   |

| t <sub>h(CLKH-NWAIT)</sub>  | FSMC_NWAIT valid after FSMC_CLK high           | 0                  | -   | ns   |

Table 79. Synchronous multiplexed NOR/PSRAM read timings<sup>(1)(2)</sup>

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization.

| Symbol                      | Parameter                                    | Min                     | Max | Unit |

|-----------------------------|----------------------------------------------|-------------------------|-----|------|

| t <sub>w(CLK)</sub>         | FSMC_CLK period                              | 2T <sub>HCLK</sub> –0.5 | -   | ns   |

| t <sub>d(CLKL-NExL)</sub>   | FSMC_CLK low to FSMC_NEx low (x=02)          | -                       | 0.5 | ns   |

| t <sub>d(CLKL-NExH)</sub>   | FSMC_CLK low to FSMC_NEx high (x= 02)        | 0                       | -   | ns   |

| t <sub>d(CLKL-NADVL)</sub>  | FSMC_CLK low to FSMC_NADV low                | -                       | 2   | ns   |

| t <sub>d(CLKL-NADVH)</sub>  | FSMC_CLK low to FSMC_NADV high               | 3                       | -   | ns   |

| t <sub>d(CLKL-AV)</sub>     | FSMC_CLK low to FSMC_Ax valid (x=1625)       | -                       | 0   | ns   |

| t <sub>d(CLKL-AIV)</sub>    | FSMC_CLK low to FSMC_Ax invalid (x=1625)     | 2                       | -   | ns   |

| t <sub>d(CLKL-NOEL)</sub>   | FSMC_CLK low to FSMC_NOE low                 | -                       | 0.5 | ns   |

| t <sub>d(CLKL-NOEH)</sub>   | FSMC_CLK low to FSMC_NOE high                | 1.5                     | -   | ns   |

| t <sub>su(DV-CLKH)</sub>    | FSMC_D[15:0] valid data before FSMC_CLK high | 6                       | -   | ns   |

| t <sub>h(CLKH-DV)</sub>     | FSMC_D[15:0] valid data after FSMC_CLK high  | 3                       | -   | ns   |

| t <sub>su(NWAIT-CLKH)</sub> | FSMC_NWAIT valid before FSMC_CLK high        | 4                       | -   | ns   |

| t <sub>h(CLKH-NWAIT)</sub>  | FSMC_NWAIT valid after FSMC_CLK high         | 0                       | -   | ns   |

Table 81. Synchronous non-multiplexed NOR/PSRAM read timings<sup>(1)(2)</sup>

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization.

# 6.2 LQFP64 package information

Figure 78. LQFP64 – 64-pin, 10 x 10 mm low-profile quad flat package outline SEATING PLANE С <[₽] 0.25 mm GAUGE PLANE ¥ Ł ¥ D k D1 L1 D3 48 33 32 49 b ШШ **1**7 64 ₿₿₿₿ ▋▋₿ Ht 8888 16 PIN 1 IDENTIFICATION 1 5W\_ME\_V3

1. Drawing is not to scale.

| Table 92. LQFP64 – 64-pin 10 x 10 mm low-profile quad flat package |

|--------------------------------------------------------------------|

| mechanical data                                                    |

| Symbol | millimeters |        |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|--------|-------|-----------------------|--------|--------|

|        | Min         | Тур    | Мах   | Min                   | Тур    | Max    |

| А      | -           | -      | 1.600 | -                     | -      | 0.0630 |

| A1     | 0.050       | -      | 0.150 | 0.0020                | -      | 0.0059 |

| A2     | 1.350       | 1.400  | 1.450 | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170       | 0.220  | 0.270 | 0.0067                | 0.0087 | 0.0106 |

| с      | 0.090       | -      | 0.200 | 0.0035                | -      | 0.0079 |

| D      | -           | 12.000 | -     | -                     | 0.4724 | -      |

| D1     | -           | 10.000 | -     | -                     | 0.3937 | -      |

| D3     | -           | 7.500  | -     | -                     | 0.2953 | -      |

| E      | -           | 12.000 | -     | -                     | 0.4724 | -      |

| E1     | -           | 10.000 | -     | -                     | 0.3937 | -      |

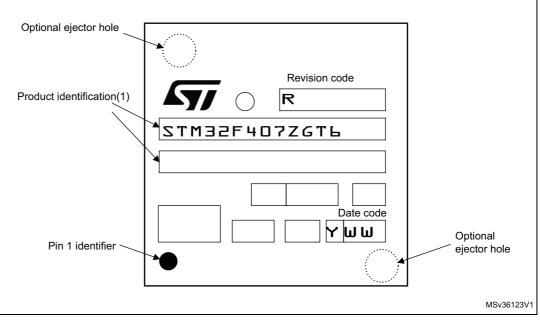

#### **Device marking for LQPF144**

The following figure gives an example of topside marking and pin 1 position identifier location.

Other optional marking or inset/upset marks, which depend on supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

## 6.7 Thermal characteristics

The maximum chip-junction temperature,  $T_{\rm J}$  max, in degrees Celsius, may be calculated using the following equation:

$T_J \max = T_A \max + (P_D \max x \Theta_{JA})$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance, in ° C/W,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

P<sub>I/O</sub> max represents the maximum power dissipation on output pins where:

$\mathsf{P}_{\mathsf{I}/\mathsf{O}} \max = \Sigma \; (\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}) + \Sigma ((\mathsf{V}_{\mathsf{DD}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual V\_{OL} / I\_{OL} and V\_{OH} / I\_{OH} of the I/Os at low and high level in the application.

| Symbol          | Parameter                                                                         | Value | Unit   |  |

|-----------------|-----------------------------------------------------------------------------------|-------|--------|--|

| Θ <sub>JA</sub> | Thermal resistance junction-ambient<br>LQFP64 - 10 × 10 mm / 0.5 mm pitch         | 46    |        |  |

|                 | Thermal resistance junction-ambient<br>LQFP100 - 14 × 14 mm / 0.5 mm pitch        | 43    | - °C/W |  |

|                 | Thermal resistance junction-ambient<br>LQFP144 - 20 × 20 mm / 0.5 mm pitch        | 40    |        |  |

|                 | <b>Thermal resistance junction-ambient</b><br>LQFP176 - 24 × 24 mm / 0.5 mm pitch | 38    |        |  |

|                 | Thermal resistance junction-ambient<br>UFBGA176 - 10× 10 mm / 0.65 mm pitch       | 39    |        |  |

|                 | Thermal resistance junction-ambient<br>WLCSP90 - 0.400 mm pitch                   | 38.1  |        |  |

| Table 98. | Package | thermal | characteristics |

|-----------|---------|---------|-----------------|

|-----------|---------|---------|-----------------|

#### **Reference document**

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org.

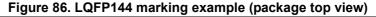

# Appendix A Application block diagrams

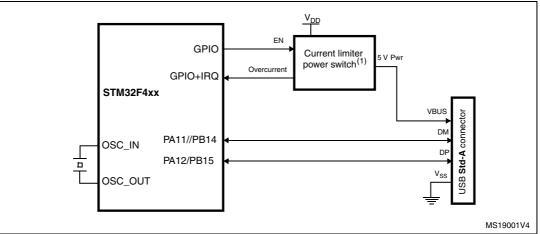

# A.1 USB OTG full speed (FS) interface solutions

Figure 93. USB controller configured as peripheral-only and used in Full speed mode

1. External voltage regulator only needed when building a  $V_{\text{BUS}}$  powered device.

2. The same application can be developed using the OTG HS in FS mode to achieve enhanced performance thanks to the large Rx/Tx FIFO and to a dedicated DMA controller.

The current limiter is required only if the application has to support a V<sub>BUS</sub> powered device. A basic power switch can be used if 5 V are available on the application board.

2. The same application can be developed using the OTG HS in FS mode to achieve enhanced performance thanks to the large Rx/Tx FIFO and to a dedicated DMA controller.

Table 100. Document revision history (continued)

| Table 100. Document revision history (continued) |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|--------------------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Date                                             | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| Date<br>04-Jun-2013                              |          | Changes           Modified Note 1 below Table 2: STM32F405xx and STM32F407xx:<br>features and peripheral counts.           Updated Figure 4 title.           Updated Note 3 below Figure 21: Power supply scheme.           Changed simplex mode into half-duplex mode in Section 2.2.25: Inter-<br>integrated sound (I2S).           Replaced DAC1_OUT and DAC2_OUT by DAC_OUT1 and<br>DAC_OUT2, respectively.           Updated pin 36 signal in Figure 15: STM32F40xxx LQFP176 pinout.           Changed pin number from F8 to D4 for PA13 pin in Table 7:<br>STM32F40xxx pin and ball definitions.           Replaced TIM2_CH1/TIM2_ETR by TIM2_CH1_ETR for PA0 and PA5<br>pins in Table 9: Alternate function mapping.           Changed system memory into System memory + OTP in Figure 18:<br>STM32F40xxx memory map.           Added Note 1 below Table 16: VCAP_1/VCAP_2 operating conditions.           Updated I <sub>DDA</sub> description in Table 74: DAC characteristics.           Removed PA9/PB13 connection to VBUS in Figure 93: USB controller<br>configured as peripheral-only and used in Full speed mode and<br>Figure 94: USB controller configured as host-only and used in full<br>speed mode.           Updated Section 2.2.15: Power supply schemes           Updated operating voltages in Table 2: STM32F405xx and<br>STM32F407xx: features and peripheral counts           Updated Section 2.2.15: Power supply schemes           Updated Section 2.2.15: Power supply schemes           Updated Section 2.2.16: Notage<br>regulator           Removed note in Section 2.2.19: Low-power modes |  |  |

|                                                  |          | Updated Table 25: Typical and maximum current consumptions in VBAT mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|                                                  |          | Deleted Table 59<br>Updated <i>Table 62: ULPI timing</i><br>Updated <i>Figure 46: Ethernet SMI timing diagram</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

Table 100. Document revision history (continued)

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2016 STMicroelectronics – All rights reserved

DocID022152 Rev 8