Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                    |

|----------------------------|-------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                        |

| Speed                      | 168MHz                                                                                    |

| Connectivity               | CANbus, DCMI, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                         |

| Number of I/O              | 140                                                                                       |

| Program Memory Size        | 512KB (512K x 8)                                                                          |

| Program Memory Type        | FLASH                                                                                     |

| EEPROM Size                | -                                                                                         |

| RAM Size                   | 192К х 8                                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                               |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                     |

| Oscillator Type            | Internal                                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                         |

| Mounting Type              | Surface Mount                                                                             |

| Package / Case             | 201-UFBGA                                                                                 |

| Supplier Device Package    | 176+25UFBGA (10x10)                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f407ieh6                     |

|                            |                                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|        |                                                                                                       | 5.3.12                                                                                                 | Memory characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 108                                                                      |

|--------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

|        |                                                                                                       | 5.3.13                                                                                                 | EMC characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 110                                                                      |

|        |                                                                                                       | 5.3.14                                                                                                 | Absolute maximum ratings (electrical sensitivity)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 112                                                                      |

|        |                                                                                                       | 5.3.15                                                                                                 | I/O current injection characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 113                                                                      |

|        |                                                                                                       | 5.3.16                                                                                                 | I/O port characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 114                                                                      |

|        |                                                                                                       | 5.3.17                                                                                                 | NRST pin characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 118                                                                      |

|        |                                                                                                       | 5.3.18                                                                                                 | TIM timer characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 119                                                                      |

|        |                                                                                                       | 5.3.19                                                                                                 | Communications interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 121                                                                      |

|        |                                                                                                       | 5.3.20                                                                                                 | CAN (controller area network) interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 133                                                                      |

|        |                                                                                                       | 5.3.21                                                                                                 | 12-bit ADC characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 133                                                                      |

|        |                                                                                                       | 5.3.22                                                                                                 | Temperature sensor characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 138                                                                      |

|        |                                                                                                       | 5.3.23                                                                                                 | V <sub>BAT</sub> monitoring characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 139                                                                      |

|        |                                                                                                       | 5.3.24                                                                                                 | Embedded reference voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 139                                                                      |

|        |                                                                                                       | 5.3.25                                                                                                 | DAC electrical characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 139                                                                      |

|        |                                                                                                       | 5.3.26                                                                                                 | FSMC characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 142                                                                      |

|        |                                                                                                       | 5.3.27                                                                                                 | Camera interface (DCMI) timing specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 161                                                                      |

|        |                                                                                                       | 5.3.28                                                                                                 | SD/SDIO MMC card host interface (SDIO) characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 162                                                                      |

|        |                                                                                                       | 5.3.29                                                                                                 | RTC characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 163                                                                      |

|        |                                                                                                       |                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                          |

| 6      | Packa                                                                                                 | ige info                                                                                               | rmation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 64                                                                       |

| 6      | <b>Packa</b><br>6.1                                                                                   |                                                                                                        | rmation   1     90 package information   1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                          |

| 6      |                                                                                                       | WLCSP                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 164                                                                      |

| 6      | 6.1                                                                                                   | WLCSP<br>LQFP64                                                                                        | 90 package information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 164<br>167                                                               |

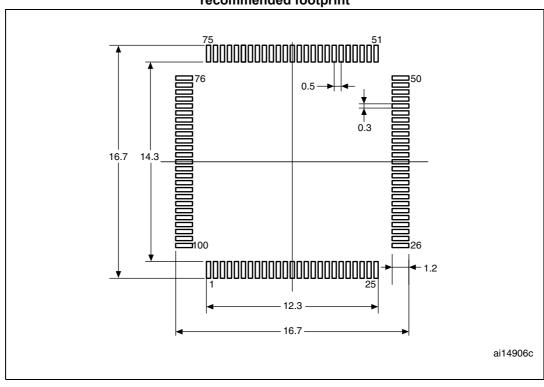

| 6      | 6.1<br>6.2                                                                                            | WLCSP<br>LQFP64<br>LQPF10                                                                              | 90 package information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 164<br>167<br>170                                                        |

| 6      | 6.1<br>6.2<br>6.3                                                                                     | WLCSP<br>LQFP64<br>LQPF10<br>LQFP14                                                                    | 90 package information 1<br>package information 1<br>0 package information 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 164<br>167<br>170<br>173                                                 |

| 6      | 6.1<br>6.2<br>6.3<br>6.4                                                                              | WLCSP<br>LQFP64<br>LQPF10<br>LQFP14<br>UFBGA                                                           | 90 package information    1      • package information    1      • 0 package information    1      • 4 package information    1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 164<br>167<br>170<br>173<br>177                                          |

| 6      | 6.1<br>6.2<br>6.3<br>6.4<br>6.5                                                                       | WLCSP<br>LQFP64<br>LQPF10<br>LQFP14<br>UFBGA<br>LQFP17                                                 | 90 package information    1      • package information    1      •0 package information    1      •4 package information    1      •176+25 package information    1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 164<br>167<br>170<br>173<br>177<br>180                                   |

| 6<br>7 | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> <li>6.7</li> </ul> | WLCSP<br>LQFP64<br>LQPF10<br>LQFP14<br>UFBGA<br>LQFP17<br>Therma                                       | 90 package information    1      • package information    1      •0 package information    1      •4 package information    1      •176+25 package information    1      •6 package information    1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 164<br>167<br>170<br>173<br>177<br>180<br>184                            |

| 7      | 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br><b>Part n</b>                                        | WLCSP<br>LQFP64<br>LQPF10<br>LQFP14<br>UFBGA<br>LQFP17<br>Therma                                       | 90 package information    1      • package information    1      • 0 package information    1      • 4 package information    1      • 176+25 package information    1      • 6 package information    1      • 6 package information    1      • 6 package information    1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 164<br>167<br>170<br>173<br>177<br>180<br>184                            |

| 7      | 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br><b>Part n</b>                                        | WLCSP<br>LQFP64<br>LQFP14<br>UFBGA<br>LQFP17<br>Therma                                                 | 90 package information       1         9 package information       1         10 package information       1         14 package information       1         176+25 package information       1         176 package information       1         16 package information       1         176 hackage information       1         177 hackage information       1         178 hackage information       1         178 hackage information       1         178 hackage informating       1 | 164<br>167<br>170<br>173<br>177<br>180<br>184<br>185                     |

| 7      | 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br><b>Part n</b><br><b>x A Ag</b><br>A.1                | WLCSP<br>LQFP64<br>LQFP14<br>UFBGA<br>LQFP17<br>Therma                                                 | 90 package information       1         9 package information       1         10 package information       1         14 package information       1         176+25 package information       1         16 package information       1         176+25 package information       1         16 package information       1         16 package information       1         176 package information       1         16 package information       1         176 characteristics       1         176 full speed (FS) interface solutions       1                                                                                                                                                                                                                                                                                                                                                                                                     | 164<br>167<br>170<br>173<br>177<br>180<br>184<br><b>85</b><br>186        |

| 7      | 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br><b>Part n</b><br>A.1<br>A.2                          | WLCSP<br>LQFP64<br>LQFP10<br>LQFP14<br>UFBGA<br>LQFP17<br>Therma<br><b>Dumberi</b><br>USB 01<br>USB 01 | 90 package information       1         9 package information       1         90 package information       1         90 package information       1         90 package information       1         90 package information       1         176+25 package information       1         176 package information       1         16 package information       1         16 package information       1         176 package information       1         16 package information       1         176 characteristics       1         177 ng       1         176 full speed (FS) interface solutions       1         176 high speed (HS) interface solutions       1                                                                                                                                                                                                                                                                                  | 164<br>167<br>170<br>173<br>177<br>180<br>184<br><b>85</b><br>186<br>186 |

| 7      | 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br><b>Part n</b><br><b>x A Ag</b><br>A.1                | WLCSP<br>LQFP64<br>LQFP10<br>LQFP14<br>UFBGA<br>LQFP17<br>Therma<br><b>Dumberi</b><br>USB 01<br>USB 01 | 90 package information       1         9 package information       1         10 package information       1         14 package information       1         176+25 package information       1         16 package information       1         176+25 package information       1         16 package information       1         16 package information       1         176 package information       1         16 package information       1         176 characteristics       1         176 full speed (FS) interface solutions       1                                                                                                                                                                                                                                                                                                                                                                                                     | 164<br>167<br>170<br>173<br>177<br>180<br>184<br><b>85</b><br>186<br>186 |

## 1 Introduction

This datasheet provides the description of the STM32F405xx and STM32F407xx lines of microcontrollers. For more details on the whole STMicroelectronics STM32<sup>™</sup> family, please refer to Section 2.1: Full compatibility throughout the family.

The STM32F405xx and STM32F407xx datasheet should be read in conjunction with the STM32F4xx reference manual which is available from the STMicroelectronics website *www.st.com*.

For information on the Cortex<sup>®</sup>-M4 core, please refer to the Cortex<sup>®</sup>-M4 programming manual (PM0214) available from *www.st.com*.

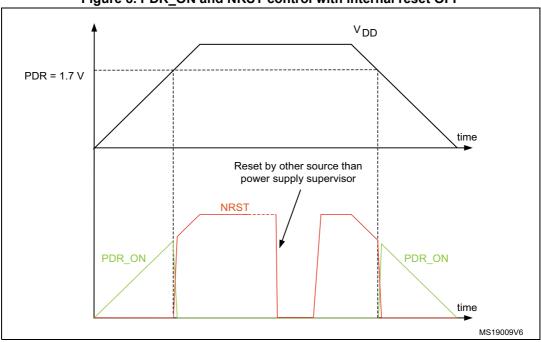

Figure 8. PDR\_ON and NRST control with internal reset OFF

#### 2.2.16 Voltage regulator

The regulator has four operating modes:

- Regulator ON

- Main regulator mode (MR)

- Low-power regulator (LPR)

- Power-down

- Regulator OFF

#### **Regulator ON**

On packages embedding the BYPASS\_REG pin, the regulator is enabled by holding BYPASS\_REG low. On all other packages, the regulator is always enabled.

There are three power modes configured by software when regulator is ON:

- MR is used in the nominal regulation mode (With different voltage scaling in Run) In Main regulator mode (MR mode), different voltage scaling are provided to reach the best compromise between maximum frequency and dynamic power consumption. Refer to *Table 14: General operating conditions*.

- LPR is used in the Stop modes

The LP regulator mode is configured by software when entering Stop mode.

- Power-down is used in Standby mode.

- The Power-down mode is activated only when entering in Standby mode. The regulator output is in high impedance and the kernel circuitry is powered down, inducing zero consumption. The contents of the registers and SRAM are lost)

|        | F       | Pin r   | numb    | er       | -       |                                                      |               |          |   |                                       |                         |

|--------|---------|---------|---------|----------|---------|------------------------------------------------------|---------------|----------|---|---------------------------------------|-------------------------|

| LQFP64 | WLCSP90 | LQFP100 | LQFP144 | UFBGA176 | LQFP176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type      | 2        |   | Alternate functions                   | Additional<br>functions |

| -      | A8      | -       | 143     | C6       | 171     | PDR_ON                                               | PDR_ON I FT - |          | - | -                                     | -                       |

| 64     | A1      | 10<br>0 | 144     | C5       | 172     | V <sub>DD</sub>                                      |               | -        | - | -                                     | -                       |

| -      | -       | -       | -       | D4       | 173     | Pl4                                                  | I/O           | FT       | - | TIM8_BKIN / DCMI_D5/<br>EVENTOUT      | -                       |

| -      | -       | -       | -       | C4       | 174     | PI5                                                  | I/O           | //O FT - |   | TIM8_CH1 /<br>DCMI_VSYNC/<br>EVENTOUT | -                       |

| -      | -       | -       | -       | C3       | 175     | Pl6                                                  | I/O           | I/O FT - |   | TIM8_CH2 / DCMI_D6/<br>EVENTOUT       | -                       |

| -      | -       | -       | -       | C2       | 176     | PI7                                                  | I/O           | FT       | - | TIM8_CH3 / DCMI_D7/<br>EVENTOUT       | -                       |

Table 7. STM32F40xxx pin and ball definitions (continued)

1. Function availability depends on the chosen device.

PC13, PC14, PC15 and PI8 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 and PI8 in output mode is limited:

The speed should not exceed 2 MHz with a maximum load of 30 pF.

- These I/Os must not be used as a current source (e.g. to drive an LED).

3. Main function after the first backup domain power-up. Later on, it depends on the contents of the RTC registers even after reset (because these registers are not reset by the main reset). For details on how to manage these I/Os, refer to the RTC register description sections in the STM32F4xx reference manual, available from the STMicroelectronics website: www.st.com.

4. FT = 5 V tolerant except when in analog mode or oscillator mode (for PC14, PC15, PH0 and PH1).

If the device is delivered in an UFBGA176 or WLCSP90 and the BYPASS\_REG pin is set to VDD (Regulator off/internal reset ON mode), then PA0 is used as an internal Reset (active low). 5.

|                     |    |                    |               | WLCSP90     |                        |     |

|---------------------|----|--------------------|---------------|-------------|------------------------|-----|

| Pins <sup>(1)</sup> | CF | NOR/PSRAM/<br>SRAM | NOR/PSRAM Mux | NAND 16 bit | LQFP100 <sup>(2)</sup> | (2) |

| PE2                 | -  | A23                | A23           | -           | Yes                    | -   |

| PE3                 | -  | A19                | A19           | -           | Yes                    | -   |

| PE4                 | -  | A20                | A20           | -           | Yes                    | -   |

| PE5                 | -  | A21                | A21           | -           | Yes                    | -   |

| PE6                 | -  | A22                | A22           | -           | Yes                    | -   |

| PF0                 | A0 | A0                 | -             | -           | -                      | -   |

Table 8. FSMC pin definition

| Pins <sup>(1)</sup> | CF    | NOR/PSRAM/<br>SRAM | NOR/PSRAM Mux | NAND 16 bit | LQFP100 <sup>(2)</sup> | WLCSP90<br>(2) |

|---------------------|-------|--------------------|---------------|-------------|------------------------|----------------|

| PF1                 | A1    | A1                 | -             | -           | -                      | -              |

| PF2                 | A2    | A2                 | -             | -           | -                      | -              |

| PF3                 | A3    | A3                 | -             | -           | -                      | -              |

| PF4                 | A4    | A4                 | -             | -           | -                      | -              |

| PF5                 | A5    | A5                 | -             | -           | -                      | -              |

| PF6                 | NIORD | -                  | -             | -           | -                      | -              |

| PF7                 | NREG  | -                  | -             | -           | -                      | -              |

| PF8                 | NIOWR | -                  | -             | -           | -                      | -              |

| PF9                 | CD    | -                  | -             | -           | -                      | -              |

| PF10                | INTR  | -                  | -             | -           | -                      | -              |

| PF12                | A6    | A6                 | -             | -           | -                      | -              |

| PF13                | A7    | A7                 | -             | -           | -                      | -              |

| PF14                | A8    | A8                 | -             | -           | -                      | -              |

| PF15                | A9    | A9                 | -             | -           | -                      | -              |

| PG0                 | A10   | A10                | -             | -           | -                      | -              |

| PG1                 |       | A11                | -             | -           | -                      | -              |

| PE7                 | D4    | D4                 | DA4           | D4          | Yes                    | Yes            |

| PE8                 | D5    | D5                 | DA5           | D5          | Yes                    | Yes            |

| PE9                 | D6    | D6                 | DA6           | D6          | Yes                    | Yes            |

| PE10                | D7    | D7                 | DA7           | D7          | Yes                    | Yes            |

| PE11                | D8    | D8                 | DA8           | D8          | Yes                    | Yes            |

| PE12                | D9    | D9                 | DA9           | D9          | Yes                    | Yes            |

| PE13                | D10   | D10                | DA10          | D10         | Yes                    | Yes            |

| PE14                | D11   | D11                | DA11          | D11         | Yes                    | Yes            |

| PE15                | D12   | D12                | DA12          | D12         | Yes                    | Yes            |

| PD8                 | D13   | D13                | DA13          | D13         | Yes                    | Yes            |

| PD9                 | D14   | D14                | DA14          | D14         | Yes                    | Yes            |

| PD10                | D15   | D15                | DA15          | D15         | Yes                    | Yes            |

| PD11                | -     | A16                | A16           | CLE         | Yes                    | Yes            |

| PD12                | -     | A17                | A17           | ALE         | Yes                    | Yes            |

| PD13                | -     | A18                | A18           | -           | Yes                    | -              |

| PD14                | D0    | D0                 | DA0           | D0          | Yes                    | Yes            |

| PD15                | D1    | D1                 | DA1           | D1          | Yes                    | Yes            |

| Table 8. FSM | C pin definition | n (continued) |

|--------------|------------------|---------------|

|--------------|------------------|---------------|

|--|

DocID022152 Rev 8

|        |      | AF0          | AF1       | AF2      | AF3              | AF4      | AF5                            | AF6                  | AF7                    | AF8                | AF9                       | AF10              | AF11          | AF12                 | AF13    |      |          |

|--------|------|--------------|-----------|----------|------------------|----------|--------------------------------|----------------------|------------------------|--------------------|---------------------------|-------------------|---------------|----------------------|---------|------|----------|

| P      | ort  | SYS          | TIM1/2    | TIM3/4/5 | TIM8/9/10<br>/11 | I2C1/2/3 | SPI1/SPI2/<br>I2S2/I2S2e<br>xt | SPI3/I2Sext<br>/I2S3 | USART1/2/3/<br>I2S3ext | UART4/5/<br>USART6 | CAN1/2<br>TIM12/13/<br>14 | OTG_FS/<br>OTG_HS | ETH           | FSMC/SDIO<br>/OTG_FS | DCMI    | AF14 | AF15     |

|        | PE0  | -            | -         | TIM4_ETR | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | -             | FSMC_NBL0            | DCMI_D2 | -    | EVENTOUT |

|        | PE1  | -            | -         | -        | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | -             | FSMC_NBL1            | DCMI_D3 | -    | EVENTOUT |

|        | PE2  | TRACECL<br>K | -         | -        | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | ETH _MII_TXD3 | FSMC_A23             | -       | -    | EVENTOUT |

|        | PE3  | TRACED0      | -         | -        | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | -             | FSMC_A19             | -       | -    | EVENTOUT |

|        | PE4  | TRACED1      | -         | -        | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | -             | FSMC_A20             | DCMI_D4 | -    | EVENTOUT |

|        | PE5  | TRACED2      | -         | -        | TIM9_CH1         | -        | -                              | -                    | -                      | -                  | -                         | -                 | -             | FSMC_A21             | DCMI_D6 | -    | EVENTOUT |

|        | PE6  | TRACED3      | -         | -        | TIM9_CH2         | -        | -                              | -                    | -                      | -                  | -                         | -                 | -             | FSMC_A22             | DCMI_D7 | -    | EVENTOUT |

| Port E | PE7  | -            | TIM1_ETR  | -        | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | -             | FSMC_D4              | -       | -    | EVENTOUT |

|        | PE8  | -            | TIM1_CH1N | -        | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | -             | FSMC_D5              | -       | -    | EVENTOUT |

|        | PE9  | -            | TIM1_CH1  | -        | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | -             | FSMC_D6              | -       | -    | EVENTOUT |

|        | PE10 | -            | TIM1_CH2N | -        | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | -             | FSMC_D7              | -       | -    | EVENTOUT |

|        | PE11 | -            | TIM1_CH2  | -        | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | -             | FSMC_D8              | -       | -    | EVENTOUT |

|        | PE12 | -            | TIM1_CH3N | -        | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | -             | FSMC_D9              | -       | -    | EVENTOUT |

|        | PE13 | -            | TIM1_CH3  | -        | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | -             | FSMC_D10             | -       | -    | EVENTOUT |

|        | PE14 | -            | TIM1_CH4  | -        | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | -             | FSMC_D11             | -       | -    | EVENTOUT |

|        | PE15 | -            | TIM1_BKIN | ÷        | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | -             | FSMC_D12             | -       | -    | EVENTOUT |

Table 9. Alternate function mapping (continued)

| Bus  | Boundary address          | Peripheral               |

|------|---------------------------|--------------------------|

|      | 0x4004 0000 - 0x4007 FFFF | USB OTG HS               |

|      | 0x4002 9400 - 0x4003 FFFF | Reserved                 |

|      | 0x4002 9000 - 0x4002 93FF |                          |

|      | 0x4002 8C00 - 0x4002 8FFF |                          |

|      | 0x4002 8800 - 0x4002 8BFF | ETHERNET MAC             |

|      | 0x4002 8400 - 0x4002 87FF |                          |

|      | 0x4002 8000 - 0x4002 83FF |                          |

|      | 0x4002 6800 - 0x4002 7FFF | Reserved                 |

|      | 0x4002 6400 - 0x4002 67FF | DMA2                     |

|      | 0x4002 6000 - 0x4002 63FF | DMA1                     |

|      | 0x4002 5000 - 0x4002 5FFF | Reserved                 |

|      | 0x4002 4000 - 0x4002 4FFF | BKPSRAM                  |

| AHB1 | 0x4002 3C00 - 0x4002 3FFF | Flash interface register |

| АПВТ | 0x4002 3800 - 0x4002 3BFF | RCC                      |

|      | 0x4002 3400 - 0x4002 37FF | Reserved                 |

|      | 0x4002 3000 - 0x4002 33FF | CRC                      |

|      | 0x4002 2400 - 0x4002 2FFF | Reserved                 |

|      | 0x4002 2000 - 0x4002 23FF | GPIOI                    |

|      | 0x4002 1C00 - 0x4002 1FFF | GPIOH                    |

|      | 0x4002 1800 - 0x4002 1BFF | GPIOG                    |

|      | 0x4002 1400 - 0x4002 17FF | GPIOF                    |

|      | 0x4002 1000 - 0x4002 13FF | GPIOE                    |

|      | 0x4002 0C00 - 0x4002 0FFF | GPIOD                    |

|      | 0x4002 0800 - 0x4002 0BFF | GPIOC                    |

|      | 0x4002 0400 - 0x4002 07FF | GPIOB                    |

|      | 0x4002 0000 - 0x4002 03FF | GPIOA                    |

|      | 0x4001 5800- 0x4001 FFFF  | Reserved                 |

Table 10. register boundary addresses (continued)

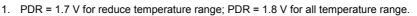

#### 5.1.6 Power supply scheme

#### Figure 21. Power supply scheme

1. Each power supply pair must be decoupled with filtering ceramic capacitors as shown above. These capacitors must be placed as close as possible to, or below, the appropriate pins on the underside of the PCB to ensure the good functionality of the device.

- 2. To connect BYPASS\_REG and PDR\_ON pins, refer to Section 2.2.16: Voltage regulator and Table 2.2.15: Power supply supervisor.

- 3. The two 2.2  $\mu F$  ceramic capacitors should be replaced by two 100 nF decoupling capacitors when the voltage regulator is OFF.

- 4. The 4.7  $\mu F$  ceramic capacitor must be connected to one of the  $V_{DD}$  pin.

- 5.  $V_{DDA}=V_{DD}$  and  $V_{SSA}=V_{SS}$ .

| Symbol                                  | Parameter                                                                          | Conditions                                                                                | Min  | Тур  | Max  | Unit |

|-----------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------|------|------|------|

| N                                       | Brownout level 2                                                                   | Falling edge                                                                              | 2.44 | 2.50 | 2.56 | V    |

| V <sub>BOR2</sub>                       | threshold                                                                          | Rising edge                                                                               | 2.53 | 2.59 | 2.63 | V    |

| M                                       | Brownout level 3                                                                   | Falling edge                                                                              | 2.75 | 2.83 | 2.56 | V    |

| V <sub>BOR3</sub>                       | threshold                                                                          | Rising edge                                                                               | 2.85 | 2.92 | 2.97 | V    |

| V <sub>BORhyst</sub> <sup>(1)</sup>     | BOR hysteresis                                                                     | -                                                                                         | -    | 100  | -    | mV   |

| T <sub>RSTTEMPO</sub> <sup>(1)(2)</sup> | Reset temporization                                                                | -                                                                                         | 0.5  | 1.5  | 3.0  | ms   |

| I <sub>RUSH</sub> <sup>(1)</sup>        | InRush current on<br>voltage regulator<br>power-on (POR or<br>wakeup from Standby) | -                                                                                         | -    | 160  | 200  | mA   |

| E <sub>RUSH</sub> <sup>(1)</sup>        | InRush energy on<br>voltage regulator<br>power-on (POR or<br>wakeup from Standby)  | V <sub>DD</sub> = 1.8 V, T <sub>A</sub> = 105 °C,<br>I <sub>RUSH</sub> = 171 mA for 31 μs | -    | -    | 5.4  | μC   |

Table 19. Embedded reset and power control block characteristics (continued)

1. Guaranteed by design.

2. The reset temporization is measured from the power-on (POR reset or wakeup from  $V_{BAT}$ ) to the instant when first instruction is read by the user application code.

#### 5.3.6 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 22: Current consumption measurement scheme*.

All Run mode current consumption measurements given in this section are performed using a CoreMark-compliant code.

#### Typical and maximum current consumption

The MCU is placed under the following conditions:

- At startup, all I/O pins are configured as analog inputs by firmware.

- All peripherals are disabled except if it is explicitly mentioned.

- The Flash memory access time is adjusted to f<sub>HCLK</sub> frequency (0 wait state from 0 to 30 MHz, 1 wait state from 30 to 60 MHz, 2 wait states from 60 to 90 MHz, 3 wait states from 90 to 120 MHz, 4 wait states from 120 to 150 MHz, and 5 wait states from 150 to 168 MHz).

- When the peripherals are enabled HCLK is the system clock, f<sub>PCLK1</sub> = f<sub>HCLK</sub>/4, and f<sub>PCLK2</sub> = f<sub>HCLK</sub>/2, except is explicitly mentioned.

- The maximum values are obtained for  $V_{DD}$  = 3.6 V and maximum ambient temperature (T<sub>A</sub>), and the typical values for T<sub>A</sub>= 25 °C and V<sub>DD</sub> = 3.3 V unless otherwise specified.

#### Additional current consumption

The MCU is placed under the following conditions:

- All I/O pins are configured in analog mode.

- The Flash memory access time is adjusted to f<sub>HCLK</sub> frequency.

- The voltage scaling is adjusted to f<sub>HCLK</sub> frequency as follows:

- Scale 2 for f<sub>HCLK</sub> ≤ 144 MHz

- Scale 1 for 144 MHz <  $f_{HCLK} \le 168$  MHz.

- The system clock is HCLK,  $f_{PCLK1} = f_{HCLK}/4$ , and  $f_{PCLK2} = f_{HCLK}/2$ .

- The HSE crystal clock frequency is 25 MHz.

- T<sub>A</sub>= 25 °C.

# Table 26. Typical current consumption in Run mode, code with data processing running from Flash memory, regulator ON (ART accelerator enabled except prefetch), $V_{DD} = 1.8 V^{(1)}$

| Symbol | Parameter                     | Conditions                 | f <sub>HCLK</sub> (MHz) | Typ. at T <sub>A</sub> =<br>25 °C | Unit |  |

|--------|-------------------------------|----------------------------|-------------------------|-----------------------------------|------|--|

|        |                               |                            | 160                     | 36.2                              |      |  |

|        |                               |                            | 144                     | 29.3                              |      |  |

|        |                               |                            | 120                     | 24.7                              |      |  |

| IDD    | Supply current in<br>Run mode | All peripheral<br>disabled | 90                      | 19.3                              | mA   |  |

|        |                               |                            | 60                      | 13.4                              |      |  |

|        |                               |                            | 30                      | 7.7                               |      |  |

|        |                               |                            | 25                      | 6.0                               |      |  |

1. When peripherals are enabled, the power consumption corresponding to the analog part of the peripherals (such as ADC or DAC) is not included.

#### I/O system current consumption

The current consumption of the I/O system has two components: static and dynamic.

I/O static current consumption

All the I/Os used as inputs with pull-up generate current consumption when the pin is externally held low. The value of this current consumption can be simply computed by using the pull-up/pull-down resistors values given in *Table 48: I/O static characteristics*.

For the output pins, any external pull-down or external load must also be considered to estimate the current consumption.

Additional I/O current consumption is due to I/Os configured as inputs if an intermediate voltage level is externally applied. This current consumption is caused by the input Schmitt trigger circuits used to discriminate the input value. Unless this specific configuration is required by the application, this supply current consumption can be avoided by configuring these I/Os in analog mode. This is notably the case of ADC input pins which should be configured as analog inputs.

**Caution:** Any floating input pin can also settle to an intermediate voltage level or switch inadvertently, as a result of external electromagnetic noise. To avoid current consumption related to

DocID022152 Rev 8

floating pins, they must either be configured in analog mode, or forced internally to a definite digital value. This can be done either by using pull-up/down resistors or by configuring the pins in output mode.

I/O dynamic current consumption

In addition to the internal peripheral current consumption measured previously (see *Table 28: Peripheral current consumption*), the I/Os used by an application also contribute to the current consumption. When an I/O pin switches, it uses the current from the MCU supply voltage to supply the I/O pin circuitry and to charge/discharge the capacitive load (internal or external) connected to the pin:

$$I_{SW} = V_{DD} \times f_{SW} \times C$$

where

${\rm I}_{\rm SW}$  is the current sunk by a switching I/O to charge/discharge the capacitive load

$V_{DD}$  is the MCU supply voltage

$f_{\mbox{SW}}$  is the I/O switching frequency

C is the total capacitance seen by the I/O pin: C =  $C_{INT}$ +  $C_{EXT}$

The test pin is configured in push-pull output mode and is toggled by software at a fixed frequency.

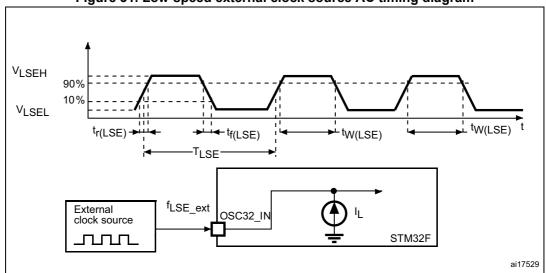

Figure 31. Low-speed external clock source AC timing diagram

#### High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 4 to 26 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 32*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter                               | Conditions                    | Min | Тур | Max | Unit   |

|-------------------------------------|-----------------------------------------|-------------------------------|-----|-----|-----|--------|

| f <sub>OSC_IN</sub>                 | Oscillator frequency                    | -                             | 4   | -   | 26  | MHz    |

| R <sub>F</sub>                      | Feedback resistor                       | -                             | -   | 200 | -   | kΩ     |

| G <sub>m</sub>                      | Oscillator transconductance             | Statup                        | 5   | -   | -   | mA/V   |

| G <sub>mcritmax</sub>               | Maximum critical crystal G <sub>m</sub> | Startup                       | -   | -   | 1   | THAV V |

| t <sub>SU(HSE)</sub> <sup>(2)</sup> | Startup time                            | $V_{\text{DD}}$ is stabilized | -   | 2   | -   | ms     |

| Table 32. HSE 4-26 MHz oscillator characteristics <sup>(1)</sup> | Table 32. HSE 4-26 | 6 MHz oscillator | characteristics <sup>(1)</sup> |

|------------------------------------------------------------------|--------------------|------------------|--------------------------------|

|------------------------------------------------------------------|--------------------|------------------|--------------------------------|

1. Guaranteed by design.