Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                    |

|----------------------------|-------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                        |

| Speed                      | 168MHz                                                                                    |

| Connectivity               | CANbus, DCMI, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                         |

| Number of I/O              | 140                                                                                       |

| Program Memory Size        | 512KB (512K x 8)                                                                          |

| Program Memory Type        | FLASH                                                                                     |

| EEPROM Size                | -                                                                                         |

| RAM Size                   | 192К х 8                                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                               |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                     |

| Oscillator Type            | Internal                                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                         |

| Mounting Type              | Surface Mount                                                                             |

| Package / Case             | 201-UFBGA                                                                                 |

| Supplier Device Package    | 176+25UFBGA (10x10)                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f407ieh6tr                   |

|                            |                                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| recommended footprint                                                        | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| UFBGA176+25 ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ball grid array package outline                                              | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| UFBGA176+25 - 201-ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ball grid array recommended footprint                                        | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| UFBGA176+25 marking example (package top view)1                              | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| LQFP176 - 176-pin, 24 x 24 mm low profile quad flat package outline          | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| LQFP176 - 176-pin, 24 x 24 mm low profile quad flat recommended footprint 18 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| LQFP176 marking example (package top view)18                                 | 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| USB controller configured as peripheral-only and used                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| in Full speed mode                                                           | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| USB controller configured as host-only and used in full speed mode           | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| USB controller configured in dual mode and used in full speed mode           | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| USB controller configured as peripheral, host, or dual-mode                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| and used in high speed mode                                                  | 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| MII mode using a 25 MHz crystal                                              | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RMII with a 50 MHz oscillator                                                | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

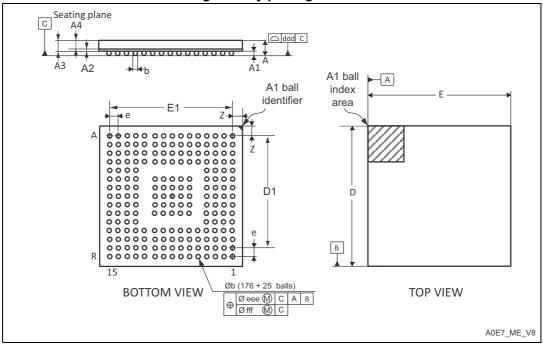

| RMII with a 25 MHz crystal and PHY with PLL19                                | 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                              | ball grid array package outline11UFBGA176+25 - 201-ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch11ball grid array recommended footprint11UFBGA176+25 marking example (package top view)11LQFP176 - 176-pin, 24 x 24 mm low profile quad flat package outline14LQFP176 - 176-pin, 24 x 24 mm low profile quad flat recommended footprint.16LQFP176 marking example (package top view)16USB controller configured as peripheral-only and used16in Full speed mode16USB controller configured as host-only and used in full speed mode16USB controller configured as peripheral, host, or dual-mode16and used in high speed mode16MII mode using a 25 MHz crystal16RMII with a 50 MHz oscillator16 |

# 1 Introduction

This datasheet provides the description of the STM32F405xx and STM32F407xx lines of microcontrollers. For more details on the whole STMicroelectronics STM32<sup>™</sup> family, please refer to Section 2.1: Full compatibility throughout the family.

The STM32F405xx and STM32F407xx datasheet should be read in conjunction with the STM32F4xx reference manual which is available from the STMicroelectronics website *www.st.com*.

For information on the Cortex<sup>®</sup>-M4 core, please refer to the Cortex<sup>®</sup>-M4 programming manual (PM0214) available from *www.st.com*.

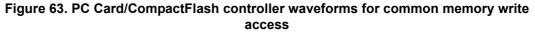

|                     |        |                    | FSMC          |             |                        | M/ 00000       |

|---------------------|--------|--------------------|---------------|-------------|------------------------|----------------|

| Pins <sup>(1)</sup> | CF     | NOR/PSRAM/<br>SRAM | NOR/PSRAM Mux | NAND 16 bit | LQFP100 <sup>(2)</sup> | WLCSP90<br>(2) |

| PG2                 | -      | A12                | -             | -           | -                      | -              |

| PG3                 | -      | A13                | -             | -           | -                      | -              |

| PG4                 | -      | A14                | -             | -           | -                      | -              |

| PG5                 | -      | A15                | -             | -           | -                      | -              |

| PG6                 | -      | -                  | -             | INT2        | -                      | -              |

| PG7                 | -      | -                  | -             | INT3        | -                      | -              |

| PD0                 | D2     | D2                 | DA2           | D2          | Yes                    | Yes            |

| PD1                 | D3     | D3                 | DA3           | D3          | Yes                    | Yes            |

| PD3                 | -      | CLK                | CLK           | -           | Yes                    | -              |

| PD4                 | NOE    | NOE                | NOE           | NOE         | Yes                    | Yes            |

| PD5                 | NWE    | NWE                | NWE           | NWE         | Yes                    | Yes            |

| PD6                 | NWAIT  | NWAIT              | NWAIT         | NWAIT       | Yes                    | Yes            |

| PD7                 | -      | NE1                | NE1           | NCE2        | Yes                    | Yes            |

| PG9                 | -      | NE2                | NE2           | NCE3        | -                      | -              |

| PG10                | NCE4_1 | NE3                | NE3           | -           | -                      | -              |

| PG11                | NCE4_2 | -                  | -             | -           | -                      | -              |

| PG12                | -      | NE4                | NE4           | -           | -                      | -              |

| PG13                | -      | A24                | A24           | -           | -                      | -              |

| PG14                | -      | A25                | A25           | -           | -                      | -              |

| PB7                 | -      | NADV               | NADV          | -           | Yes                    | Yes            |

| PE0                 | -      | NBL0               | NBL0          | -           | Yes                    | -              |

| PE1                 | -      | NBL1               | NBL1          | -           | Yes                    | -              |

Table 8. FSMC pin definition (continued)

1. Full FSMC features are available on LQFP144, LQFP176, and UFBGA176. The features available on smaller packages are given in the dedicated package column.

2. Ports F and G are not available in devices delivered in 100-pin packages.

|        | Table 9. Alternate function mapping |                |                        |           |                  |               |                                |                      |                        |                    |                           |                    |                                           |                      |                |      |          |

|--------|-------------------------------------|----------------|------------------------|-----------|------------------|---------------|--------------------------------|----------------------|------------------------|--------------------|---------------------------|--------------------|-------------------------------------------|----------------------|----------------|------|----------|

|        |                                     | AF0            | AF1                    | AF2       | AF3              | AF4           | AF5                            | AF6                  | AF7                    | AF8                | AF9                       | AF10               | AF11                                      | AF12                 | AF13           |      |          |

| Po     | ort                                 | SYS            | TIM1/2                 | TIM3/4/5  | TIM8/9/10<br>/11 | I2C1/2/3      | SPI1/SPI2/<br>I2S2/I2S2e<br>xt | SPI3/I2Sext<br>/I2S3 | USART1/2/3/<br>I2S3ext | UART4/5/<br>USART6 | CAN1/2<br>TIM12/13/<br>14 | OTG_FS/<br>OTG_HS  | ETH                                       | FSMC/SDIO<br>/OTG_FS | DCMI           | AF14 | AF15     |

|        | PA0                                 | -              | TIM2_CH1_<br>ETR       | TIM 5_CH1 | TIM8_ETR         | -             | -                              | -                    | USART2_CTS             | UART4_TX           | -                         | -                  | ETH_MII_CRS                               | -                    | -              | -    | EVENTOUT |

|        | PA1                                 | -              | TIM2_CH2               | TIM5_CH2  | -                | -             | -                              | -                    | USART2_RTS             | UART4_RX           | -                         | -                  | ETH_MII<br>_RX_CLK<br>ETH_RMIIREF<br>_CLK | -                    | -              | -    | EVENTOUT |

|        | PA2                                 | -              | TIM2_CH3               | TIM5_CH3  | TIM9_CH1         | -             | -                              | -                    | USART2_TX              | -                  | -                         | -                  | ETH_MDIO                                  | -                    | -              | -    | EVENTOUT |

|        | PA3                                 | -              | TIM2_CH4               | TIM5_CH4  | TIM9_CH2         | -             | -                              | -                    | USART2_RX              | -                  | -                         | OTG_HS_ULPI_<br>D0 | ETH _MII_COL                              | -                    | -              | -    | EVENTOUT |

|        | PA4                                 | -              | -                      | -         | -                | -             | SPI1_NSS                       | SPI3_NSS<br>I2S3_WS  | USART2_CK              | -                  | -                         | -                  | -                                         | OTG_HS_SOF           | DCMI_<br>HSYNC | -    | EVENTOUT |

|        | PA5                                 | -              | TIM2_CH1_<br>ETR       | -         | TIM8_CH1N        | -             | SPI1_SCK                       | -                    | -                      | -                  | -                         | OTG_HS_ULPI_<br>CK | -                                         | -                    | -              | -    | EVENTOUT |

|        | PA6                                 | -              | TIM1_BKIN              | TIM3_CH1  | TIM8_BKIN        | -             | SPI1_MISO                      | -                    | -                      | -                  | TIM13_CH1                 | -                  | -                                         | -                    | DCMI_PIXCK     | -    | EVENTOUT |

| Port A | PA7                                 | -              | TIM1_CH1N              | TIM3_CH2  | TIM8_CH1N        | -             | SPI1_MOSI                      | -                    | -                      | -                  | TIM14_CH1                 | -                  | ETH_MII_RX_DV<br>ETH_RMII<br>_CRS_DV      | -                    | -              | -    | EVENTOUT |

|        | PA8                                 | MCO1           | TIM1_CH1               | -         | -                | I2C3_SCL      | -                              | -                    | USART1_CK              | -                  | -                         | OTG_FS_SOF         | -                                         | -                    | -              | -    | EVENTOUT |

|        | PA9                                 | -              | TIM1_CH2               | -         | -                | I2C3_<br>SMBA | -                              | -                    | USART1_TX              | -                  | -                         | -                  | -                                         | -                    | DCMI_D0        | -    | EVENTOUT |

|        | PA10                                | -              | TIM1_CH3               | -         | -                | -             | -                              | -                    | USART1_RX              | -                  | -                         | OTG_FS_ID          | -                                         | -                    | DCMI_D1        | -    | EVENTOUT |

|        | PA11                                | -              | TIM1_CH4               | -         | -                | -             | -                              | -                    | USART1_CTS             | -                  | CAN1_RX                   | OTG_FS_DM          | -                                         | -                    | -              | -    | EVENTOUT |

|        | PA12                                | -              | TIM1_ETR               | -         | -                | -             | -                              | -                    | USART1_RTS             | -                  | CAN1_TX                   | OTG_FS_DP          | -                                         | -                    | -              | -    | EVENTOUT |

|        | PA13                                | JTMS-<br>SWDIO | -                      | -         | -                | -             | -                              | -                    | -                      | -                  | -                         | -                  | -                                         | -                    | -              | -    | EVENTOUT |

|        | PA14                                | JTCK-<br>SWCLK | -                      | -         | -                | -             | -                              | -                    | -                      | -                  | -                         | -                  | -                                         | -                    | -              | -    | EVENTOUT |

|        | PA15                                | JTDI           | TIM 2_CH1<br>TIM 2_ETR | -         | -                | -             | SPI1_NSS                       | SPI3_NSS/<br>I2S3_WS | -                      | -                  | -                         | -                  | -                                         | -                    | -              | -    | EVENTOUT |

DocID022152 Rev 8

5

62/202

STM32F405xx, STM32F407xx

Pinouts and pin description

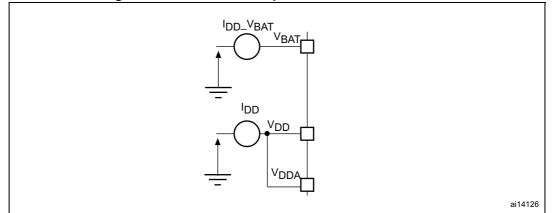

## 5.1.7 Current consumption measurement

#### Figure 22. Current consumption measurement scheme

# 5.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 11: Voltage characteristics*, *Table 12: Current characteristics*, and *Table 13: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability. Device mission profile (application conditions) is compliant with JEDEC JESD47 Qualification Standard, extended mission profiles are available on demand.

| Symbol                            | Ratings                                                                       | Min                                                      | Max                 | Unit |

|-----------------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------|---------------------|------|

| $V_{DD}-V_{SS}$                   | External main supply voltage (including $V_{DDA}$ , $V_{DD}$ ) <sup>(1)</sup> | -0.3                                                     | 4.0                 |      |

| V                                 | Input voltage on five-volt tolerant pin <sup>(2)</sup>                        | V <sub>SS</sub> -0.3                                     | V <sub>DD</sub> +4  | V    |

| V <sub>IN</sub>                   | Input voltage on any other pin                                                | V <sub>SS</sub> -0.3                                     | 4.0                 |      |

| ΔV <sub>DDx</sub>                 | Variations between different V <sub>DD</sub> power pins                       | -                                                        | 50                  |      |

| V <sub>SSX</sub> -V <sub>SS</sub> | Variations between all the different ground pins including $V_{REF-}$         | -                                                        | 50                  | mV   |

| V <sub>ESD(HBM)</sub>             | Electrostatic discharge voltage (human body model)                            | see Sectio<br>Absolute n<br>ratings (ele<br>sensitivity) | naximum<br>ectrical |      |

#### Table 11. Voltage characteristics

All main power (V<sub>DD</sub>, V<sub>DDA</sub>) and ground (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply, in the permitted range.

2. V<sub>IN</sub> maximum value must always be respected. Refer to *Table 12* for the values of the maximum allowed injected current.

| Symbol                                  | Parameter                                                                          | Conditions                                                                                | Min  | Тур  | Max  | Unit |

|-----------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>BOR2</sub>                       | Brownout level 2                                                                   | Falling edge                                                                              | 2.44 | 2.50 | 2.56 | V    |

|                                         | threshold                                                                          | Rising edge                                                                               | 2.53 | 2.59 | 2.63 | V    |

|                                         | Brownout level 3                                                                   | Falling edge                                                                              | 2.75 | 2.83 | 2.88 | V    |

|                                         | threshold                                                                          | Rising edge                                                                               | 2.85 | 2.92 | 2.97 | V    |

| V <sub>BORhyst</sub> <sup>(1)</sup>     | BOR hysteresis                                                                     | -                                                                                         | -    | 100  | -    | mV   |

| T <sub>RSTTEMPO</sub> <sup>(1)(2)</sup> | Reset temporization                                                                | -                                                                                         | 0.5  | 1.5  | 3.0  | ms   |

| I <sub>RUSH</sub> <sup>(1)</sup>        | InRush current on<br>voltage regulator<br>power-on (POR or<br>wakeup from Standby) | -                                                                                         | -    | 160  | 200  | mA   |

| E <sub>RUSH</sub> <sup>(1)</sup>        | InRush energy on<br>voltage regulator<br>power-on (POR or<br>wakeup from Standby)  | V <sub>DD</sub> = 1.8 V, T <sub>A</sub> = 105 °C,<br>I <sub>RUSH</sub> = 171 mA for 31 μs | -    | -    | 5.4  | μC   |

Table 19. Embedded reset and power control block characteristics (continued)

1. Guaranteed by design.

2. The reset temporization is measured from the power-on (POR reset or wakeup from  $V_{BAT}$ ) to the instant when first instruction is read by the user application code.

# 5.3.6 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 22: Current consumption measurement scheme*.

All Run mode current consumption measurements given in this section are performed using a CoreMark-compliant code.

## Typical and maximum current consumption

The MCU is placed under the following conditions:

- At startup, all I/O pins are configured as analog inputs by firmware.

- All peripherals are disabled except if it is explicitly mentioned.

- The Flash memory access time is adjusted to f<sub>HCLK</sub> frequency (0 wait state from 0 to 30 MHz, 1 wait state from 30 to 60 MHz, 2 wait states from 60 to 90 MHz, 3 wait states from 90 to 120 MHz, 4 wait states from 120 to 150 MHz, and 5 wait states from 150 to 168 MHz).

- When the peripherals are enabled HCLK is the system clock, f<sub>PCLK1</sub> = f<sub>HCLK</sub>/4, and f<sub>PCLK2</sub> = f<sub>HCLK</sub>/2, except is explicitly mentioned.

- The maximum values are obtained for  $V_{DD}$  = 3.6 V and maximum ambient temperature (T<sub>A</sub>), and the typical values for T<sub>A</sub>= 25 °C and V<sub>DD</sub> = 3.3 V unless otherwise specified.

|                 |                   |                                                                           | Typ Max <sup>(1)</sup> |                           |                           |                            |      |

|-----------------|-------------------|---------------------------------------------------------------------------|------------------------|---------------------------|---------------------------|----------------------------|------|

| Symbol          | Parameter         | Conditions                                                                | f <sub>HCLK</sub>      | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |

|                 |                   |                                                                           | 168 MHz                | 59                        | 77                        | 84                         |      |

|                 |                   |                                                                           | 144 MHz                | 46                        | 61                        | 67                         |      |

|                 |                   |                                                                           | 120 MHz                | 38                        | 53                        | 60                         |      |

|                 |                   |                                                                           | 90 MHz                 | 30                        | 44                        | 51                         |      |

|                 |                   | (2)                                                                       | 60 MHz                 | 20                        | 34                        | 41                         |      |

|                 |                   | External clock <sup>(2)</sup> ,<br>all peripherals enabled <sup>(3)</sup> | 30 MHz                 | 11                        | 24                        | 31                         |      |

|                 |                   |                                                                           | 25 MHz                 | 8                         | 21                        | 28                         |      |

|                 |                   |                                                                           | 16 MHz                 | 6                         | 18                        | 25                         |      |

|                 |                   |                                                                           | 8 MHz                  | 3                         | 16                        | 23                         | mA   |

|                 |                   |                                                                           | 4 MHz                  | 2                         | 15                        | 22                         |      |

|                 | Supply current in |                                                                           | 2 MHz                  | 2                         | 14                        | 21                         |      |

| I <sub>DD</sub> | Sleep mode        |                                                                           | 168 MHz                | 12                        | 27                        | 35                         | ШA   |

|                 |                   |                                                                           | 144 MHz                | 9                         | 22                        | 29                         |      |

|                 |                   |                                                                           | 120 MHz                | 8                         | 20                        | 28                         |      |

|                 |                   |                                                                           | 90 MHz                 | 7                         | 19                        | 26                         |      |

|                 |                   | (2)                                                                       | 60 MHz                 | 5                         | 17                        | 24                         |      |

|                 |                   | External clock <sup>(2)</sup> , all peripherals disabled                  | 30 MHz                 | 3                         | 16                        | 23                         |      |

|                 |                   |                                                                           | 25 MHz                 | 2                         | 15                        | 22                         |      |

|                 |                   |                                                                           | 16 MHz                 | 2                         | 14                        | 21                         |      |

|                 |                   |                                                                           | 8 MHz                  | 1                         | 14                        | 21                         |      |

|                 |                   |                                                                           | 4 MHz                  | 1                         | 13                        | 21                         |      |

|                 |                   |                                                                           | 2 MHz                  | 1                         | 13                        | 21                         |      |

| Table 22. Typica | al and maximum cu | rrent consumption i | n Sleep mode |

|------------------|-------------------|---------------------|--------------|

|------------------|-------------------|---------------------|--------------|

1. Guaranteed by characterization, tested in production at  $V_{DD}$  max and  $f_{HCLK}$  max with peripherals enabled.

2. External clock is 4 MHz and PLL is on when  $f_{HCLK}$  > 25 MHz.

3. Add an additional power consumption of 1.6 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is ON (ADON bit is set in the ADC\_CR2 register).

# 5.3.18 TIM timer characteristics

The parameters given in Table 52 and Table 53 are guaranteed by design.

Refer to *Section 5.3.16: I/O port characteristics* for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Symbol                 | Parameter                              | Conditions                                                     | Min    | Мах                     | Unit                 |

|------------------------|----------------------------------------|----------------------------------------------------------------|--------|-------------------------|----------------------|

|                        |                                        | AHB/APB1                                                       | 1      | -                       | t <sub>TIMxCLK</sub> |

| t <sub>res(TIM)</sub>  | Timer resolution time                  | prescaler distinct<br>from 1, f <sub>TIMxCLK</sub> =<br>84 MHz | 11.9   | -                       | ns                   |

|                        |                                        | AHB/APB1                                                       | 1      | -                       | t <sub>TIMxCLK</sub> |

|                        |                                        | prescaler = 1,<br>f <sub>TIMxCLK</sub> = 42 MHz                | 23.8   | -                       | ns                   |

| f                      | Timer external clock                   |                                                                | 0      | f <sub>TIMxCLK</sub> /2 | MHz                  |

| f <sub>EXT</sub>       | frequency on CH1 to CH4                |                                                                | 0      | 42                      | MHz                  |

| Res <sub>TIM</sub>     | Timer resolution                       |                                                                | -      | 16/32                   | bit                  |

|                        | 16-bit counter clock                   |                                                                | 1      | 65536                   | t <sub>TIMxCLK</sub> |

| t                      | period when internal clock is selected | f <sub>TIMxCLK</sub> = 84 MHz<br>APB1= 42 MHz                  | 0.0119 | 780                     | μs                   |

| <sup>t</sup> COUNTER   | 32-bit counter clock                   |                                                                | 1      | -                       | t <sub>TIMxCLK</sub> |

|                        | period when internal clock is selected |                                                                | 0.0119 | 51130563                | μs                   |

| +                      | Maximum possible count                 |                                                                | -      | 65536 × 65536           | t <sub>TIMxCLK</sub> |

| <sup>t</sup> MAX_COUNT | Maximum possible count                 |                                                                | -      | 51.1                    | S                    |

Table 52. Characteristics of TIMx connected to the APB1 domain<sup>(1)</sup>

1. TIMx is used as a general term to refer to the TIM2, TIM3, TIM4, TIM5, TIM6, TIM7, and TIM12 timers.

| 51                                                                                 |                  |                         |        |         |        |      |

|------------------------------------------------------------------------------------|------------------|-------------------------|--------|---------|--------|------|

| Parameter                                                                          |                  | Symbol                  | Min    | Nominal | Max    | Unit |

| Frequency (steady state) ±500 ppm                                                  |                  | F <sub>STEADY</sub>     | 59.97  | 60      | 60.03  | MHz  |

| Duty cycle (first transition) 8-bit ±10%                                           |                  | D <sub>START_8BIT</sub> | 40     | 50      | 60     | %    |

| Duty cycle (steady state) ±500 ppm                                                 |                  | D <sub>STEADY</sub>     | 49.975 | 50      | 50.025 | %    |

| Time to reach the steady state frequency and duty cycle after the first transition |                  | T <sub>STEADY</sub>     | -      | -       | 1.4    | ms   |

| Clock startup time after the                                                       | Peripheral       | T <sub>START_DEV</sub>  | -      | -       | 5.6    | ma   |

| de-assertion of SuspendM                                                           | Host             | T <sub>START_HOST</sub> | -      | -       | -      | ms   |

| PHY preparation time after the<br>of the input clock                               | first transition | T <sub>PREP</sub>       | -      | -       | -      | μs   |

## Table 61. USB HS clock timing parameters<sup>(1)</sup>

1. Guaranteed by design.

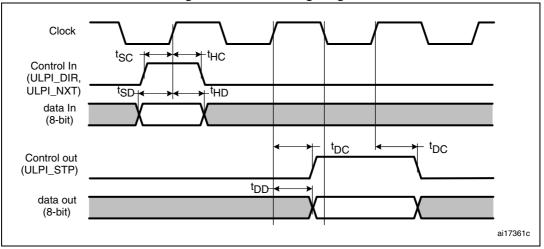

| Table 62. UL                                    | .Fi unning      |      |                      |      |

|-------------------------------------------------|-----------------|------|----------------------|------|

| Parameter                                       | Symbol          | Valu | Value <sup>(1)</sup> |      |

| Falanielei                                      | Symbol          | Min. | Max.                 | Unit |

| Control in (ULPI_DIR) setup time                | +               | -    | 2.0                  |      |

| Control in (ULPI_NXT) setup time                | t <sub>SC</sub> | -    | 1.5                  |      |

| Control in (ULPI_DIR, ULPI_NXT) hold time       | t <sub>HC</sub> | 0    | -                    |      |

| Data in setup time                              | t <sub>SD</sub> | -    | 2.0                  | ns   |

| Data in hold time                               | t <sub>HD</sub> | 0    | -                    |      |

| Control out (ULPI_STP) setup time and hold time | t <sub>DC</sub> | -    | 9.2                  |      |

| Data out available from clock rising edge       | t <sub>DD</sub> | -    | 10.7                 |      |

## Table 62. ULPI timing

1.  $V_{DD}$  = 2.7 V to 3.6 V and T<sub>A</sub> = -40 to 85 °C.

## Figure 45. ULPI timing diagram

| Symbol               | Parameter                        | Min | Тур | Max | Unit |

|----------------------|----------------------------------|-----|-----|-----|------|

| t <sub>su(RXD)</sub> | Receive data setup time          | 9   |     | -   |      |

| t <sub>ih(RXD)</sub> | Receive data hold time           | 10  |     | -   |      |

| t <sub>su(DV)</sub>  | Data valid setup time            | 9   |     | -   |      |

| t <sub>ih(DV)</sub>  | Data valid hold time             | 8   |     | -   |      |

| t <sub>su(ER)</sub>  | Error setup time                 | 6   |     | -   | – ns |

| t <sub>ih(ER)</sub>  | Error hold time                  | 8   |     | -   |      |

| t <sub>d(TXEN)</sub> | Transmit enable valid delay time | 0   | 10  | 14  |      |

| t <sub>d(TXD)</sub>  | Transmit data valid delay time   | 0   | 10  | 15  |      |

Table 66. Dynamic characteristics: Ethernet MAC signals for MII<sup>(1)</sup>

1. Guaranteed by characterization.

## 5.3.20 CAN (controller area network) interface

Refer to Section 5.3.16: I/O port characteristics for more details on the input/output alternate function characteristics (CANTX and CANRX).

# 5.3.21 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table* 67 are derived from tests performed under the ambient temperature,  $f_{PCLK2}$  frequency and  $V_{DDA}$  supply voltage conditions summarized in *Table* 14.

| Symbol                             | Parameter                               | Conditions                                           | Min                                                         | Тур | Max               | Unit               |  |

|------------------------------------|-----------------------------------------|------------------------------------------------------|-------------------------------------------------------------|-----|-------------------|--------------------|--|

| V <sub>DDA</sub>                   | Power supply                            | -                                                    | 1.8 <sup>(1)</sup>                                          | -   | 3.6               |                    |  |

| V <sub>REF+</sub>                  | Positive reference voltage              | -                                                    | 1.8 <sup>(1)(2)(3)</sup>                                    | -   | V <sub>DDA</sub>  | V <sub>DDA</sub> V |  |

| V <sub>REF-</sub>                  | Negative reference voltage              | -                                                    | -                                                           | 0   | -                 |                    |  |

| f <sub>ADC</sub>                   | ADC clock frequency                     | V <sub>DDA</sub> = 1.8 <sup>(1)(3)</sup> to<br>2.4 V | 0.6                                                         | 15  | 18                | MHz                |  |

| -                                  |                                         | $V_{DDA}$ = 2.4 to 3.6 V <sup>(3)</sup>              | 0.6                                                         | 30  | 36                | MHz                |  |

| f <sub>TRIG</sub> <sup>(4)</sup>   | External trigger frequency              | f <sub>ADC</sub> = 30 MHz,<br>12-bit resolution      | -                                                           | -   | 1764              | kHz                |  |

|                                    |                                         | -                                                    | -                                                           | -   | 17                | 1/f <sub>ADC</sub> |  |

| V <sub>AIN</sub>                   | Conversion voltage range <sup>(5)</sup> | -                                                    | 0 (V <sub>SSA</sub> or V <sub>REF-</sub><br>tied to ground) | -   | V <sub>REF+</sub> | V                  |  |

| R <sub>AIN</sub> <sup>(4)</sup>    | External input impedance                | See <i>Equation 1</i> for details                    | -                                                           | -   | 50                | кΩ                 |  |

| R <sub>ADC</sub> <sup>(4)(6)</sup> | Sampling switch resistance              | -                                                    | -                                                           | -   | 6                 | кΩ                 |  |

| C <sub>ADC</sub> <sup>(4)</sup>    | Internal sample and hold capacitor      | -                                                    | -                                                           | 4   | -                 | pF                 |  |

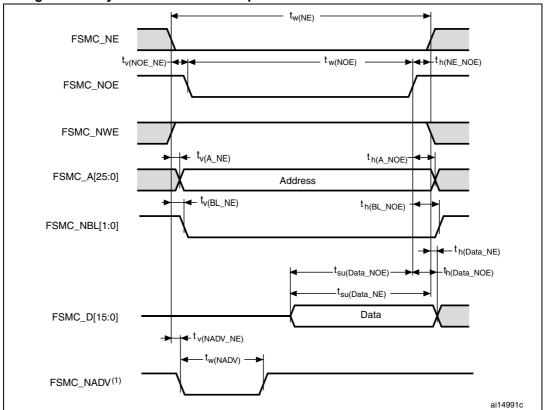

Figure 54. Asynchronous non-multiplexed SRAM/PSRAM/NOR read waveforms

1. Mode 2/B, C and D only. In Mode 1, FSMC\_NADV is not used.

## Table 75. Asynchronous non-multiplexed SRAM/PSRAM/NOR read timings<sup>(1)(2)</sup>

| Symbol                    | Parameter                               | Min                     | Max                    | Unit |

|---------------------------|-----------------------------------------|-------------------------|------------------------|------|

| t <sub>w(NE)</sub>        | FSMC_NE low time                        | 2T <sub>HCLK</sub> -0.5 | 2 T <sub>HCLK</sub> +1 | ns   |

| t <sub>v(NOE_NE)</sub>    | FSMC_NEx low to FSMC_NOE low            | 0.5                     | 3                      | ns   |

| t <sub>w(NOE)</sub>       | FSMC_NOE low time                       | 2T <sub>HCLK</sub> –2   | 2T <sub>HCLK</sub> + 2 | ns   |

| t <sub>h(NE_NOE)</sub>    | FSMC_NOE high to FSMC_NE high hold time | 0                       | -                      | ns   |

| t <sub>v(A_NE)</sub>      | FSMC_NEx low to FSMC_A valid            | -                       | 4.5                    | ns   |

| t <sub>h(A_NOE)</sub>     | Address hold time after FSMC_NOE high   | 4                       | -                      | ns   |

| t <sub>v(BL_NE)</sub>     | FSMC_NEx low to FSMC_BL valid           | -                       | 1.5                    | ns   |

| t <sub>h(BL_NOE)</sub>    | FSMC_BL hold time after FSMC_NOE high   | 0                       | -                      | ns   |

| t <sub>su(Data_NE)</sub>  | Data to FSMC_NEx high setup time        | T <sub>HCLK</sub> +4    | -                      | ns   |

| t <sub>su(Data_NOE)</sub> | Data to FSMC_NOEx high setup time       | T <sub>HCLK</sub> +4    | -                      | ns   |

| t <sub>h(Data_NOE)</sub>  | Data hold time after FSMC_NOE high      | 0                       | -                      | ns   |

| t <sub>h(Data_NE)</sub>   | Data hold time after FSMC_NEx high      | 0                       | -                      | ns   |

| t <sub>v(NADV_NE)</sub>   | FSMC_NEx low to FSMC_NADV low           | -                       | 2                      | ns   |

| t <sub>w(NADV)</sub>      | FSMC_NADV low time                      | -                       | T <sub>HCLK</sub>      | ns   |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization.

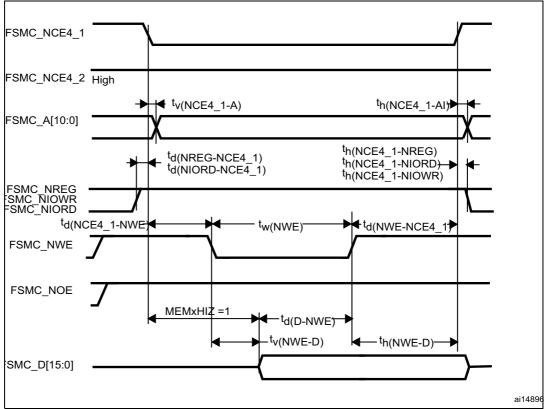

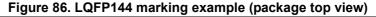

# 6.4 LQFP144 package information

Figure 84. LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat package outline

1. Drawing is not to scale.

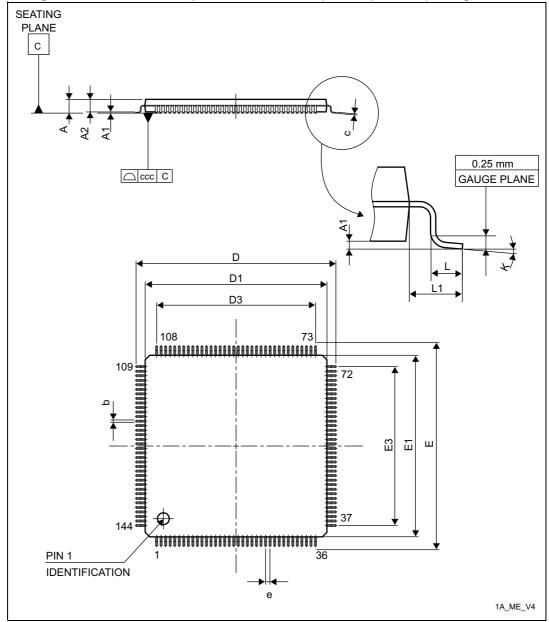

#### **Device marking for LQPF144**

The following figure gives an example of topside marking and pin 1 position identifier location.

Other optional marking or inset/upset marks, which depend on supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

# 6.5 UFBGA176+25 package information

Figure 87. UFBGA176+25 ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch ball grid array package outline

1. Drawing is not to scale.

# Table 95. UFBGA176+25 ball, 10 × 10 × 0.65 mm pitch, ultra thin fine pitchball grid array mechanical data

| Gumbal |       | millimeters | -      |        | inches <sup>(1)</sup> |        |

|--------|-------|-------------|--------|--------|-----------------------|--------|

| Symbol | Min   | Тур         | Мах    | Min    | Тур                   | Мах    |

| А      | -     | -           | 0.600  | -      | -                     | 0.0236 |

| A1     | -     | -           | 0.110  | -      | -                     | 0.0043 |

| A2     | -     | 0.130       | -      | -      | 0.0051                | -      |

| A3     | -     | 0.450       | -      | -      | 0.0177                | -      |

| A4     | -     | 0.320       | -      | -      | 0.0126                | -      |

| b      | 0.240 | 0.290       | 0.340  | 0.0094 | 0.0114                | 0.0134 |

| D      | 9.850 | 10.000      | 10.150 | 0.3878 | 0.3937                | 0.3996 |

| D1     | -     | 9.100       | -      | -      | 0.3583                | -      |

| E      | 9.850 | 10.000      | 10.150 | 0.3878 | 0.3937                | 0.3996 |

| E1     | -     | 9.100       | -      | -      | 0.3583                | -      |

| е      | -     | 0.650       | -      | -      | 0.0256                | -      |

| Z      | -     | 0.450       | -      | -      | 0.0177                | -      |

| ddd    | -     | -           | 0.080  | -      | -                     | 0.0031 |

| Table 95. UFBGA176+25 ball, 10 × 10 × 0.65 mm pitch, ultra thin fine pitch |  |

|----------------------------------------------------------------------------|--|

| ball grid array mechanical data (continued)                                |  |

| Symbol |     | millimeters |       |     | inches <sup>(1)</sup> |        |

|--------|-----|-------------|-------|-----|-----------------------|--------|

| Symbol | Min | Тур         | Max   | Min | Тур                   | Max    |

| eee    | -   | -           | 0.150 | -   | -                     | 0.0059 |

| fff    | -   | -           | 0.050 | -   | -                     | 0.0020 |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

# Figure 88. UFBGA176+25 - 201-ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch ball grid array recommended footprint

| 00000000000000000000000000000000000000            |         |

|---------------------------------------------------|---------|

|                                                   |         |

| 0000 00000 0000 <sup>+</sup> †<br>0000 00000 0000 |         |

|                                                   |         |

|                                                   |         |

|                                                   |         |

| 000000000000000000000000000000000000000           |         |

| 0000000000000                                     |         |

|                                                   |         |

| ADE                                               | 7_FP_V1 |

## Table 96. UFBGA176+2 recommended PCB design rules (0.65 mm pitch BGA)

| Dimension | Recommended values                                               |  |  |  |

|-----------|------------------------------------------------------------------|--|--|--|

| Pitch     | 0.65                                                             |  |  |  |

| Dpad      | 0.300 mm                                                         |  |  |  |

| Dsm       | 0.400 mm typ. (depends on the soldermask registration tolerance) |  |  |  |

Note:

Non solder mask defined (NSMD) pads are recommended.

4 to 6 mils solder paste screen printing process.

Stencil opening is 0.300 mm.

Stencil thickness is between 0.100 mm and 0.125 mm.

Pad trace width is 0.100 mm.

# 6.7 Thermal characteristics

The maximum chip-junction temperature,  $T_{\rm J}$  max, in degrees Celsius, may be calculated using the following equation:

$T_J \max = T_A \max + (P_D \max x \Theta_{JA})$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance, in ° C/W,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

P<sub>I/O</sub> max represents the maximum power dissipation on output pins where:

$\mathsf{P}_{\mathsf{I}/\mathsf{O}} \max = \Sigma \; (\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}) + \Sigma ((\mathsf{V}_{\mathsf{DD}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual V\_{OL} / I\_{OL} and V\_{OH} / I\_{OH} of the I/Os at low and high level in the application.

| Symbol        | Parameter                                                                         | Parameter Value Uni |      |  |  |  |

|---------------|-----------------------------------------------------------------------------------|---------------------|------|--|--|--|

|               | Thermal resistance junction-ambient<br>LQFP64 - 10 × 10 mm / 0.5 mm pitch         | 46                  |      |  |  |  |

|               | Thermal resistance junction-ambient<br>LQFP100 - 14 × 14 mm / 0.5 mm pitch        | 43                  | °C/W |  |  |  |

| 0             | Thermal resistance junction-ambient<br>LQFP144 - 20 × 20 mm / 0.5 mm pitch        | 40                  |      |  |  |  |

| $\Theta_{JA}$ | <b>Thermal resistance junction-ambient</b><br>LQFP176 - 24 × 24 mm / 0.5 mm pitch | 38                  |      |  |  |  |

|               | Thermal resistance junction-ambient<br>UFBGA176 - 10× 10 mm / 0.65 mm pitch       | 39                  |      |  |  |  |

|               | Thermal resistance junction-ambient<br>WLCSP90 - 0.400 mm pitch                   | 38.1                |      |  |  |  |

| Table 98. | Package | thermal | characteristics |

|-----------|---------|---------|-----------------|

|-----------|---------|---------|-----------------|

#### **Reference document**

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org.

# 7 Part numbering

| Example:                                                   | STM32 | F | 405 R | E | Т | 6 | xxx |

|------------------------------------------------------------|-------|---|-------|---|---|---|-----|

| Device family                                              |       |   |       |   |   |   |     |

| STM32 = ARM-based 32-bit microcontroller                   |       |   |       |   |   |   |     |

|                                                            |       |   |       |   |   |   |     |

| Product type                                               |       |   |       |   |   |   |     |

| F = general-purpose                                        |       |   |       |   |   |   |     |

|                                                            |       |   |       |   |   |   |     |

| Device subfamily                                           |       |   |       |   |   |   |     |

| 405 = STM32F40xxx, connectivity                            |       |   |       |   |   |   |     |

| 407= STM32F40xxx, connectivity, camera interface, Ethernet |       |   |       |   |   |   |     |

|                                                            |       |   |       |   |   |   |     |

| Din count                                                  |       |   |       |   |   |   |     |

| Pin count                                                  |       |   |       |   |   |   |     |

| R = 64  pins                                               |       |   |       |   |   |   |     |

| O = 90  pins                                               |       |   |       |   |   |   |     |

| V = 100 pins                                               |       |   |       |   |   |   |     |

| Z = 144  pins                                              |       |   |       |   |   |   |     |

| I = 176 pins                                               |       |   |       |   |   |   |     |

| Flash memory size                                          |       |   |       |   |   |   |     |

| E = 512 Kbytes of Flash memory                             |       |   |       |   |   |   |     |

| G = 1024 Kbytes of Flash memory                            |       |   |       |   |   |   |     |

|                                                            |       |   |       |   |   |   |     |

| Package                                                    |       |   |       |   |   |   |     |

| T = LQFP                                                   |       |   |       |   | 1 |   |     |

| H = UFBGA                                                  |       |   |       |   |   |   |     |

| Y = WLCSP                                                  |       |   |       |   |   |   |     |

|                                                            |       |   |       |   |   |   |     |

| Temperature range                                          |       |   |       |   |   |   |     |

| 6 = Industrial temperature range, -40 to 85 °C.            |       |   |       |   |   |   |     |

| 7 = Industrial temperature range, -40 to 105 °C.           |       |   |       |   |   |   |     |

| Options                                                    |       |   |       |   |   |   |     |

#### Table 99. Ordering information scheme

xxx = programmed parts

TR = tape and reel

For a list of available options (speed, package, etc.) or for further information on any aspect of this device, please contact your nearest ST sales office.

DocID022152 Rev 8

Figure 99. RMII with a 25 MHz crystal and PHY with PLL

1. f<sub>HCLK</sub> must be greater than 25 MHz.

2. The 25 MHz (PHY\_CLK) must be derived directly from the HSE oscillator, before the PLL block.

| Date          | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22-Oct-2015   | 6        | In the whole document, updated notes related to values guaranteed by design or by characterization.<br>Updated <i>Table 34: HSI oscillator characteristics</i> .<br>Changed f <sub>VCO_OUT</sub> minimum value and VCO freq to 100 MHz in<br><i>Table 36: Main PLL characteristics</i> and <i>Table 37: PLLI2S (audio PLL)</i><br><i>characteristics</i> .<br>Updated <i>Figure 39: SPI timing diagram - slave mode and CPHA = 0</i> .<br>Updated <i>Figure 53: 12-bit buffered /non-buffered DAC</i> .<br>Removed note 1 related to better performance using a restricted V <sub>DD</sub><br>range in <i>Table 68: ADC accuracy at fADC = 30 MHz</i> .<br>Upated <i>Figure 84: LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat</i><br><i>package outline</i> .<br>Updated <i>Figure 87: UFBGA176+25 ball, 10 x 10 mm, 0.65 mm pitch,</i><br><i>ultra fine pitch ball grid array package outline</i> and <i>Table 95:</i><br><i>UFBGA176+25 ball, 10 x 10 x 0.65 mm pitch, ultra thin fine pitch ball</i><br><i>grid array mechanical data</i> . |

| 16-Mar-2016 7 |          | Updated Figure 2: Compatible board design<br>STM32F10xx/STM32F2/STM32F40xxx for LQFP100 package.<br>Updated  Vssx–Vss  in Table 11: Voltage characteristics to add V <sub>REF</sub> .<br>Added V <sub>REF</sub> _in Table 67: ADC characteristics.<br>Updated Table 90: WLCSP90 - 4.223 x 3.969 mm, 0.400 mm pitch<br>wafer level chip scale package mechanical data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 09-Sep-2016   | 8        | Remove note 1 below <i>Figure 5: STM32F40xxx block diagram</i> .<br>Updated definition of stresses above maximum ratings in Section 5.2:<br><i>Absolute maximum ratings</i> .<br>Updated $t_{h(NSS)}$ in <i>Figure 39: SPI timing diagram - slave mode and</i><br><i>CPHA = 0Figure</i> and <i>Figure 40: SPI timing diagram - slave mode and</i><br><i>CPHA = 1.</i><br>Added note related to optional marking and inset/upset marks in all<br>package marking sections.<br>Updated <i>Figure 87: UFBGA176+25 ball, 10 x 10 mm, 0.65 mm pitch,</i><br><i>ultra fine pitch ball grid array package outline</i> and <i>Table 95:</i><br><i>UFBGA176+25 ball, 10 x 10 x 0.65 mm pitch, ultra thin fine pitch ball</i><br><i>grid array mechanical data.</i>                                                                                                                                                                                                                                                                                            |

Table 100. Document revision history (continued)