Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                    |

|----------------------------|-------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                        |

| Speed                      | 168MHz                                                                                    |

| Connectivity               | CANbus, DCMI, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                         |

| Number of I/O              | 140                                                                                       |

| Program Memory Size        | 512KB (512K x 8)                                                                          |

| Program Memory Type        | FLASH                                                                                     |

| EEPROM Size                | -                                                                                         |

| RAM Size                   | 192K x 8                                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                               |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                     |

| Oscillator Type            | Internal                                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                         |

| Mounting Type              | Surface Mount                                                                             |

| Package / Case             | 176-LQFP                                                                                  |

| Supplier Device Package    | 176-LQFP (24x24)                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f407iet6                     |

|                            |                                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.1 Full compatibility throughout the family

The STM32F405xx and STM32F407xx are part of the STM32F4 family. They are fully pinto-pin, software and feature compatible with the STM32F2xx devices, allowing the user to try different memory densities, peripherals, and performances (FPU, higher frequency) for a greater degree of freedom during the development cycle.

The STM32F405xx and STM32F407xx devices maintain a close compatibility with the whole STM32F10xxx family. All functional pins are pin-to-pin compatible. The STM32F405xx and STM32F407xx, however, are not drop-in replacements for the STM32F10xxx devices: the two families do not have the same power scheme, and so their power pins are different. Nonetheless, transition from the STM32F10xxx to the STM32F40xxx family remains simple as only a few pins are impacted.

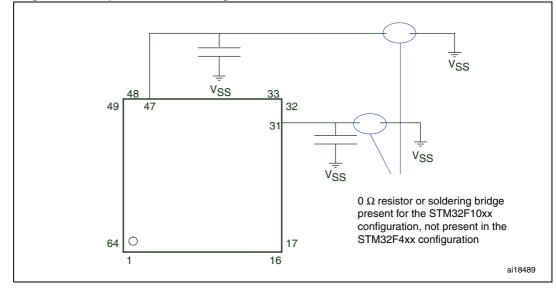

*Figure 4*, *Figure 3*, *Figure 2*, and *Figure 1* give compatible board designs between the STM32F40xxx, STM32F2, and STM32F10xxx families.

Figure 1. Compatible board design between STM32F10xx/STM32F40xxx for LQFP64

Standby mode, the SRAM and register contents are lost except for registers in the backup domain and the backup SRAM when selected.

The device exits the Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on the WKUP pin, or an RTC alarm / wakeup / tamper /time stamp event occurs.

The standby mode is not supported when the embedded voltage regulator is bypassed and the  $V_{12}$  domain is controlled by an external power.

#### 2.2.20 V<sub>BAT</sub> operation

The  $V_{BAT}$  pin allows to power the device  $V_{BAT}$  domain from an external battery, an external supercapacitor, or from  $V_{DD}$  when no external battery and an external supercapacitor are present.

$V_{BAT}$  operation is activated when  $V_{DD}$  is not present.

The V<sub>BAT</sub> pin supplies the RTC, the backup registers and the backup SRAM.

Note: When the microcontroller is supplied from  $V_{BAT}$ , external interrupts and RTC alarm/events do not exit it from  $V_{BAT}$  operation.

When PDR\_ON pin is not connected to  $V_{DD}$  (internal reset OFF), the  $V_{BAT}$  functionality is no more available and  $V_{BAT}$  pin should be connected to  $V_{DD}$ .

#### 2.2.21 Timers and watchdogs

The STM32F405xx and STM32F407xx devices include two advanced-control timers, eight general-purpose timers, two basic timers and two watchdog timers.

All timer counters can be frozen in debug mode.

*Table 4* compares the features of the advanced-control, general-purpose and basic timers.

| Timer<br>type        | Timer         | Counter<br>resolution | Counter<br>type         | Prescaler<br>factor                   | DMA<br>request<br>generation | Capture/<br>compare<br>channels | Complemen-<br>tary output | Max<br>interface<br>clock<br>(MHz) | Max<br>timer<br>clock<br>(MHz) |

|----------------------|---------------|-----------------------|-------------------------|---------------------------------------|------------------------------|---------------------------------|---------------------------|------------------------------------|--------------------------------|

| Advanceo<br>-control | TIM1,<br>TIM8 | 16-bit                | Up,<br>Down,<br>Up/down | Any integer<br>between 1<br>and 65536 | Yes                          | 4                               | Yes                       | 84                                 | 168                            |

Table 4. Timer feature comparison

#### General-purpose timers (TIMx)

There are ten synchronizable general-purpose timers embedded in the STM32F40xxx devices (see *Table 4* for differences).

• TIM2, TIM3, TIM4, TIM5

The STM32F40xxx include 4 full-featured general-purpose timers: TIM2, TIM5, TIM3, and TIM4.The TIM2 and TIM5 timers are based on a 32-bit auto-reload up/downcounter and a 16-bit prescaler. The TIM3 and TIM4 timers are based on a 16-bit prescaler.

bit auto-reload up/downcounter and a 16-bit prescaler. They all feature 4 independent channels for input capture/output compare, PWM or one-pulse mode output. This gives up to 16 input capture/output compare/PWMs on the largest packages.

The TIM2, TIM3, TIM4, TIM5 general-purpose timers can work together, or with the other general-purpose timers and the advanced-control timers TIM1 and TIM8 via the Timer Link feature for synchronization or event chaining.

Any of these general-purpose timers can be used to generate PWM outputs.

TIM2, TIM3, TIM4, TIM5 all have independent DMA request generation. They are capable of handling quadrature (incremental) encoder signals and the digital outputs from 1 to 4 hall-effect sensors.

#### • TIM9, TIM10, TIM11, TIM12, TIM13, and TIM14

These timers are based on a 16-bit auto-reload upcounter and a 16-bit prescaler. TIM10, TIM11, TIM13, and TIM14 feature one independent channel, whereas TIM9 and TIM12 have two independent channels for input capture/output compare, PWM or one-pulse mode output. They can be synchronized with the TIM2, TIM3, TIM4, TIM5 full-featured general-purpose timers. They can also be used as simple time bases.

#### Basic timers TIM6 and TIM7

These timers are mainly used for DAC trigger and waveform generation. They can also be used as a generic 16-bit time base.

TIM6 and TIM7 support independent DMA request generation.

#### Independent watchdog

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 32 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free-running timer for application timeout management. It is hardware- or software-configurable through the option bytes.

#### Window watchdog

The window watchdog is based on a 7-bit downcounter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

alternate functions. All GPIOs are high-current-capable and have speed selection to better manage internal noise, power consumption and electromagnetic emission.

The I/O configuration can be locked if needed by following a specific sequence in order to avoid spurious writing to the I/Os registers.

Fast I/O handling allowing maximum I/O toggling up to 84 MHz.

#### 2.2.35 Analog-to-digital converters (ADCs)

Three 12-bit analog-to-digital converters are embedded and each ADC shares up to 16 external channels, performing conversions in the single-shot or scan mode. In scan mode, automatic conversion is performed on a selected group of analog inputs.

Additional logic functions embedded in the ADC interface allow:

- Simultaneous sample and hold

- Interleaved sample and hold

The ADC can be served by the DMA controller. An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

To synchronize A/D conversion and timers, the ADCs could be triggered by any of TIM1, TIM2, TIM3, TIM4, TIM5, or TIM8 timer.

#### 2.2.36 Temperature sensor

The temperature sensor has to generate a voltage that varies linearly with temperature. The conversion range is between 1.8 V and 3.6 V. The temperature sensor is internally connected to the ADC1\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

As the offset of the temperature sensor varies from chip to chip due to process variation, the internal temperature sensor is mainly suitable for applications that detect temperature changes instead of absolute temperatures. If an accurate temperature reading is needed, then an external temperature sensor part should be used.

### 2.2.37 Digital-to-analog converter (DAC)

The two 12-bit buffered DAC channels can be used to convert two digital signals into two analog voltage signal outputs.

This dual digital Interface supports the following features:

- two DAC converters: one for each output channel

- 8-bit or 12-bit monotonic output

- left or right data alignment in 12-bit mode

- synchronized update capability

- noise-wave generation

- triangular-wave generation

- dual DAC channel independent or simultaneous conversions

- DMA capability for each channel

- external triggers for conversion

- input voltage reference V<sub>REF+</sub>

|   | 1     | 2    | 3    | 4              | 5   | 6      | 7    | 8    | 9    | 10     | 11   | 12   | 13     | 14   | 15       |

|---|-------|------|------|----------------|-----|--------|------|------|------|--------|------|------|--------|------|----------|

| А | PE3   | PE2  | PE1  | PE0            | PB8 | PB5    | PG14 | PG13 | PB4  | PB3    | PD7  | PC12 | PA15   | PA14 | PA13     |

| В | PE4   | PE5  | PE6  | PB9            | PB7 | PB6    | PG15 | PG12 | PG11 | PG10   | PD6  | PD0  | PC11   | PC10 | PA12     |

| с | VBAT  | PI7  | PI6  | PI5            | VDD | PDR_ON | VDD  | VDD  | VDD  | PG9    | PD5  | PD1  | PI3    | Pl2  | PA11     |

| D | PC13  | PI8  | PI9  | Pl4            | VSS | BOOT0  | VSS  | VSS  | VSS  | PD4    | PD3  | PD2  | PH15   | PI1  | PA10     |

| E | PC14  | PF0  | PI10 | PI11           |     |        |      |      |      |        |      | PH13 | PH14   | P10  | PA 9     |

| F | PC15  | VSS  | VDD  | PH2            |     | VSS    | VSS  | VSS  | VSS  | VSS    |      | VSS  | VCAP_2 | PC9  | PA 8     |

| G | PH0   | VSS  | VDD  | PH3            |     | VSS    | VSS  | VSS  | VSS  | VSS    |      | VSS  | VDD    | PC8  | PC7      |

| н | PH1   | PF2  | PF1  | PH4            |     | VSS    | VSS  | VSS  | VSS  | VSS    |      | VSS  | VDD    | PG8  | PC6      |

| J | NRST  | PF3  | PF4  | PH5            |     | VSS    | VSS  | VSS  | VSS  | VSS    |      | VDD  | VDD    | PG7  | PG6      |

| к | PF7   | PF6  | PF5  | VDD            |     | VSS    | VSS  | VSS  | VSS  | VSS    |      | PH12 | PG5    | PG4  | PG3      |

| L | PF10  | PF9  | PF8  | BYPASS_<br>REG |     |        |      |      |      |        |      | PH11 | PH10   | PD15 | PG2      |

| М | VSSA  | PC0  | PC1  | PC2            | PC3 | PB2    | PG1  | VSS  | VSS  | VCAP_1 | PH6  | PH8  | PH9    | PD14 | PD13     |

| Ν | VREF- | PA 1 | PA0  | PA4            | PC4 | PF13   | PG0  | VDD  | VDD  | VDD    | PE13 | PH7  | PD12   | PD11 | PD10     |

| Ρ | VREF+ | PA2  | PA6  | PA5            | PC5 | PF12   | PF15 | PE8  | PE9  | PE11   | PE14 | PB12 | PB13   | PD9  | PD8      |

| R | VDDA  | PA3  | PA7  | PB1            | PB0 | PF11   | PF14 | PE7  | PE10 | PE12   | PE15 | PB10 | PB11   | PB14 | PB15     |

|   |       |      |      |                |     |        |      |      |      |        |      |      |        |      | ai18497b |

Figure 16. STM32F40xxx UFBGA176 ballout

1. This figure shows the package top view.

|        | I       | Pin r   | numb    |          |         |                                                      |          |                 |       | definitions (continued)                                                          |                         |

|--------|---------|---------|---------|----------|---------|------------------------------------------------------|----------|-----------------|-------|----------------------------------------------------------------------------------|-------------------------|

| LQFP64 | WLCSP90 | LQFP100 | LQFP144 | UFBGA176 | LQFP176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes | Alternate functions                                                              | Additional<br>functions |

| -      | -       | 60      | 82      | M15      | 101     | PD13                                                 | I/O      | FT              | -     | FSMC_A18/TIM4_CH2/<br>EVENTOUT                                                   | -                       |

| -      | -       | -       | 83      | -        | 102     | V <sub>SS</sub>                                      | S        |                 | -     | -                                                                                | -                       |

| -      | -       | -       | 84      | J13      | 103     | V <sub>DD</sub>                                      | S        |                 | -     | -                                                                                | -                       |

| -      | F2      | 61      | 85      | M14      | 104     | PD14                                                 | I/O      | FT              | -     | FSMC_D0/TIM4_CH3/<br>EVENTOUT/ EVENTOUT                                          | -                       |

| -      | F1      | 62      | 86      | L14      | 105     | PD15                                                 | I/O      | FT              | -     | FSMC_D1/TIM4_CH4/<br>EVENTOUT                                                    | -                       |

| -      | -       | -       | 87      | L15      | 106     | PG2                                                  | I/O      | FT              | -     | FSMC_A12/ EVENTOUT                                                               | -                       |

| -      | -       | -       | 88      | K15      | 107     | PG3                                                  | I/O      | FT              | -     | FSMC_A13/ EVENTOUT                                                               | -                       |

| -      | -       | -       | 89      | K14      | 108     | PG4                                                  | I/O      | FT              | -     | FSMC_A14/ EVENTOUT                                                               | -                       |

| -      | -       | -       | 90      | K13      | 109     | PG5                                                  | I/O      | FT              | -     | FSMC_A15/ EVENTOUT                                                               | -                       |

| -      | -       | -       | 91      | J15      | 110     | PG6                                                  | I/O      | FT              | -     | FSMC_INT2/ EVENTOUT                                                              | -                       |

| -      | -       | -       | 92      | J14      | 111     | PG7                                                  | I/O      | FT              | -     | FSMC_INT3/USART6_CK/<br>EVENTOUT                                                 | -                       |

| -      | -       | -       | 93      | H14      | 112     | PG8                                                  | I/O      | FT              | -     | USART6_RTS /<br>ETH_PPS_OUT/<br>EVENTOUT                                         | -                       |

| -      | -       | -       | 94      | G12      | 113     | V <sub>SS</sub>                                      | S        |                 | -     | -                                                                                | -                       |

| -      | -       | -       | 95      | H13      | 114     | V <sub>DD</sub>                                      | S        |                 | -     | -                                                                                | -                       |

| 37     | F3      | 63      | 96      | H15      | 115     | PC6                                                  | I/O      | FT              | -     | I2S2_MCK /<br>TIM8_CH1/SDIO_D6 /<br>USART6_TX /<br>DCMI_D0/TIM3_CH1/<br>EVENTOUT | -                       |

| 38     | E1      | 64      | 97      | G15      | 116     | PC7                                                  | I/O      | FT              | -     | I2S3_MCK /<br>TIM8_CH2/SDIO_D7 /<br>USART6_RX /<br>DCMI_D1/TIM3_CH2/<br>EVENTOUT | -                       |

| 39     | E2      | 65      | 98      | G14      | 117     | PC8                                                  | I/O      | FT              | -     | TIM8_CH3/SDIO_D0<br>/TIM3_CH3/ USART6_CK /<br>DCMI_D2/ EVENTOUT                  | -                       |

Table 7. STM32F40xxx pin and ball definitions (continued)

| Symbol                               | Ratings                                                                 | Max.  | Unit |

|--------------------------------------|-------------------------------------------------------------------------|-------|------|

| I <sub>VDD</sub>                     |                                                                         |       |      |

| I <sub>VSS</sub>                     |                                                                         |       |      |

|                                      | Output current sunk by any I/O and control pin                          | 25    |      |

| I <sub>IO</sub>                      | Output current source by any I/Os and control pin                       | 25    | mA   |

| ı (2)                                | Injected current on five-volt tolerant I/O <sup>(3)</sup>               | -5/+0 |      |

| I <sub>INJ(PIN)</sub> <sup>(2)</sup> | Injected current on any other pin <sup>(4)</sup>                        | ±5    |      |

| $\Sigma I_{\rm INJ(PIN)}^{(4)}$      | Total injected current (sum of all I/O and control pins) <sup>(5)</sup> | ±25   |      |

#### Table 12. Current characteristics

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

2. Negative injection disturbs the analog performance of the device. See note in Section 5.3.21: 12-bit ADC characteristics.

3. Positive injection is not possible on these I/Os. A negative injection is induced by  $V_{IN} < V_{SS}$ .  $I_{INJ(PIN)}$  must never be exceeded. Refer to *Table 11* for the values of the maximum allowed input voltage.

4. A positive injection is induced by  $V_{IN}$  >  $V_{DD}$  while a negative injection is induced by  $V_{IN}$  <  $V_{SS}$ .  $I_{INJ(PIN)}$  must never be exceeded. Refer to *Table 11* for the values of the maximum allowed input voltage.

5. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values).

#### Table 13. Thermal characteristics

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | –65 to +150 | °C   |

| TJ               | Maximum junction temperature | 125         | °C   |

### 5.3 Operating conditions

### 5.3.1 General operating conditions

#### Table 14. General operating conditions

| Symbol                             | Parameter                                                  | Conditions                             | Min                | Тур | Max | Unit |  |

|------------------------------------|------------------------------------------------------------|----------------------------------------|--------------------|-----|-----|------|--|

| f                                  | Internal AHB clock frequency                               | VOS bit in PWR_CR register = $0^{(1)}$ | 0                  | -   | 144 |      |  |

| f <sub>HCLK</sub>                  | Internal AITE Clock frequency                              | VOS bit in PWR_CR register= 1          | 0                  | -   | 168 | MHz  |  |

| f <sub>PCLK1</sub>                 | Internal APB1 clock frequency                              | -                                      | 0                  | -   | 42  |      |  |

| f <sub>PCLK2</sub>                 | Internal APB2 clock frequency                              | -                                      | 0                  | -   | 84  |      |  |

| V <sub>DD</sub>                    | Standard operating voltage                                 | -                                      | 1.8 <sup>(2)</sup> | -   | 3.6 | V    |  |

| V <sub>DDA</sub> <sup>(3)(4)</sup> | Analog operating voltage<br>(ADC limited to 1.2 M samples) | Must be the same potential as          | 1.8 <sup>(2)</sup> | -   | 2.4 | V    |  |

| VDDA <sup>(O)(1)</sup>             | Analog operating voltage<br>(ADC limited to 1.4 M samples) | V <sub>DD</sub> <sup>(5)</sup>         | 2.4                | -   | 3.6 |      |  |

| V <sub>BAT</sub>                   | Backup operating voltage                                   | -                                      | 1.65               | -   | 3.6 | V    |  |

| Symbol                                  | Parameter                                                                          | Conditions                                                                                | Min  | Тур  | Max  | Unit |

|-----------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>BOR2</sub>                       | Brownout level 2                                                                   | Falling edge                                                                              | 2.44 | 2.50 | 2.56 | V    |

| VBOR2                                   | threshold                                                                          | Rising edge                                                                               | 2.53 | 2.59 | 2.63 | V    |

| V <sub>BOR3</sub>                       | Brownout level 3                                                                   | Falling edge                                                                              | 2.75 | 2.83 | 2.88 | V    |

|                                         | threshold                                                                          | Rising edge                                                                               | 2.85 | 2.92 | 2.97 | V    |

| V <sub>BORhyst</sub> <sup>(1)</sup>     | BOR hysteresis                                                                     | -                                                                                         | -    | 100  | -    | mV   |

| T <sub>RSTTEMPO</sub> <sup>(1)(2)</sup> | Reset temporization                                                                | -                                                                                         | 0.5  | 1.5  | 3.0  | ms   |

| I <sub>RUSH</sub> <sup>(1)</sup>        | InRush current on<br>voltage regulator<br>power-on (POR or<br>wakeup from Standby) | -                                                                                         | -    | 160  | 200  | mA   |

| E <sub>RUSH</sub> <sup>(1)</sup>        | InRush energy on<br>voltage regulator<br>power-on (POR or<br>wakeup from Standby)  | V <sub>DD</sub> = 1.8 V, T <sub>A</sub> = 105 °C,<br>I <sub>RUSH</sub> = 171 mA for 31 μs | -    | -    | 5.4  | μC   |

Table 19. Embedded reset and power control block characteristics (continued)

1. Guaranteed by design.

2. The reset temporization is measured from the power-on (POR reset or wakeup from  $V_{BAT}$ ) to the instant when first instruction is read by the user application code.

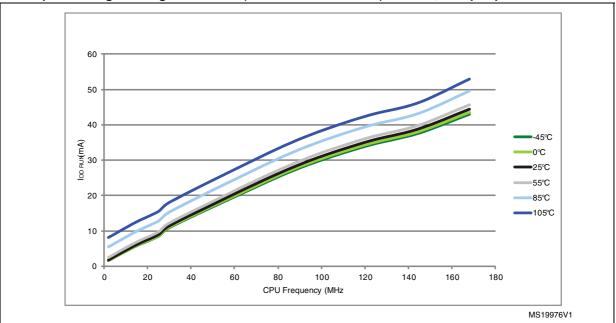

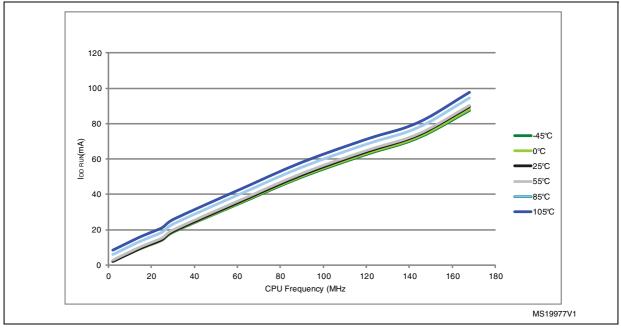

### 5.3.6 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 22: Current consumption measurement scheme*.

All Run mode current consumption measurements given in this section are performed using a CoreMark-compliant code.

#### Typical and maximum current consumption

The MCU is placed under the following conditions:

- At startup, all I/O pins are configured as analog inputs by firmware.

- All peripherals are disabled except if it is explicitly mentioned.

- The Flash memory access time is adjusted to f<sub>HCLK</sub> frequency (0 wait state from 0 to 30 MHz, 1 wait state from 30 to 60 MHz, 2 wait states from 60 to 90 MHz, 3 wait states from 90 to 120 MHz, 4 wait states from 120 to 150 MHz, and 5 wait states from 150 to 168 MHz).

- When the peripherals are enabled HCLK is the system clock, f<sub>PCLK1</sub> = f<sub>HCLK</sub>/4, and f<sub>PCLK2</sub> = f<sub>HCLK</sub>/2, except is explicitly mentioned.

- The maximum values are obtained for  $V_{DD}$  = 3.6 V and maximum ambient temperature (T<sub>A</sub>), and the typical values for T<sub>A</sub>= 25 °C and V<sub>DD</sub> = 3.3 V unless otherwise specified.

| Gumbal          | Devementer     | Conditions                                   | 4                 | Тур                    | Ма                     | ax <sup>(1)</sup>       | Unit |

|-----------------|----------------|----------------------------------------------|-------------------|------------------------|------------------------|-------------------------|------|

| Symbol          | Parameter      | Conditions                                   | f <sub>HCLK</sub> | T <sub>A</sub> = 25 °C | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Unit |

|                 |                |                                              | 168 MHz           | 93                     | 109                    | 117                     |      |

|                 |                |                                              | 144 MHz           | 76                     | 89                     | 96                      |      |

|                 |                |                                              | 120 MHz           | 67                     | 79                     | 86                      |      |

|                 |                |                                              | 90 MHz            | 53                     | 65                     | 73                      |      |

|                 |                | External clock <sup>(2)</sup> ,              | 60 MHz            | 37                     | 49                     | 56                      |      |

|                 |                | all peripherals<br>enabled <sup>(3)(4)</sup> | 30 MHz            | 20                     | 32                     | 39                      |      |

|                 |                |                                              | 25 MHz            | 16                     | 27                     | 35                      |      |

|                 |                |                                              | 16 MHz            | 11                     | 23                     | 30                      | - mA |

|                 |                |                                              | 8 MHz             | 6                      | 18                     | 25                      |      |

|                 |                |                                              | 4 MHz             | 4                      | 16                     | 23                      |      |

|                 | Supply current |                                              | 2 MHz             | 3                      | 15                     | 22                      |      |

| I <sub>DD</sub> | in Run mode    |                                              | 168 MHz           | 46                     | 61                     | 69                      |      |

|                 |                |                                              | 144 MHz           | 40                     | 52                     | 60                      |      |

|                 |                |                                              | 120 MHz           | 37                     | 48                     | 56                      |      |

|                 |                |                                              | 90 MHz            | 30                     | 42                     | 50                      |      |

|                 |                | External clock <sup>(2)</sup> ,              | 60 MHz            | 22                     | 33                     | 41                      |      |

|                 |                | all peripherals                              | 30 MHz            | 12                     | 24                     | 31                      |      |

|                 |                | disabled <sup>(3)(4)</sup>                   | 25 MHz            | 10                     | 21                     | 29                      |      |

|                 |                |                                              | 16 MHz            | 7                      | 19                     | 26                      |      |

|                 |                |                                              | 8 MHz             | 4                      | 16                     | 23                      |      |

|                 |                |                                              | 4 MHz             | 3                      | 15                     | 22                      |      |

|                 |                |                                              | 2 MHz             | 2                      | 14                     | 21                      |      |

# Table 21. Typical and maximum current consumption in Run mode, code with data processing running from Flash memory (ART accelerator disabled)

1. Guaranteed by characterization, tested in production at  $V_{\text{DD}}$  max and  $f_{\text{HCLK}}$  max with peripherals enabled.

2. External clock is 4 MHz and PLL is on when  $f_{HCLK}$  > 25 MHz.

3. When analog peripheral blocks such as (ADCs, DACs, HSE, LSE, HSI,LSI) are on, an additional power consumption should be considered.

4. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.6 mA per ADC for the analog part.

57

Figure 26. Typical current consumption versus temperature, Run mode, code with data processing running from Flash (ART accelerator OFF) or RAM, and peripherals OFF

## Figure 27. Typical current consumption versus temperature, Run mode, code with data processing running from Flash (ART accelerator OFF) or RAM, and peripherals ON

|                        |                     | I <sub>DD</sub> (1       | <sup>-</sup> yp) <sup>(1)</sup> |        |

|------------------------|---------------------|--------------------------|---------------------------------|--------|

| Perip                  | heral               | Scale1<br>(up t 168 MHz) | Scale2<br>(up to 144 MHz)       | Unit   |

|                        | SDIO                | 7.08                     | 7.92                            |        |

|                        | TIM1                | 16.79                    | 15.51                           |        |

|                        | TIM8                | 17.88                    | 16.53                           |        |

|                        | TIM9                | 7.64                     | 7.28                            |        |

|                        | TIM10               | 4.89                     | 4.82                            |        |

|                        | TIM11               | 5.19                     | 4.82                            |        |

| APB2<br>(up to 84 MHz) | ADC1 <sup>(5)</sup> | 4.67                     | 4.58                            | µA/MHz |

| (up to 04 mil2)        | ADC2 <sup>(5)</sup> | 4.67                     | 4.58                            |        |

|                        | ADC3 <sup>(5)</sup> | 4.43                     | 4.44                            |        |

|                        | SPI1                | 1.32                     | 1.39                            |        |

|                        | USART1              | 3.51                     | 3.72                            |        |

|                        | USART6              | 3.55                     | 3.75                            | ]      |

|                        | SYSCFG              | 0.74                     | 0.56                            | ]      |

Table 28. Peripheral current consumption (continued)

1. When the I/O compensation cell is ON, I<sub>DD</sub> typical value increases by 0.22 mA.

2. The BusMatrix is automatically active when at least one master is ON.

- 3. To enable an I2S peripheral, first set the I2SMOD bit and then the I2SE bit in the SPI\_I2SCFGR register.

- 4. When the DAC is ON and EN1/2 bits are set in DAC\_CR register, add an additional power consumption of 0.8 mA per DAC channel for the analog part.

- When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.6 mA per ADC for the analog part.

#### 5.3.7 Wakeup time from low-power mode

The wakeup times given in *Table 29* is measured on a wakeup phase with a 16 MHz HSI RC oscillator. The clock source used to wake up the device depends from the current operating mode:

- Stop or Standby mode: the clock source is the RC oscillator

- Sleep mode: the clock source is the clock that was set before entering Sleep mode.

All timings are derived from tests performed under ambient temperature and V<sub>DD</sub> supply voltage conditions summarized in *Table 14*.

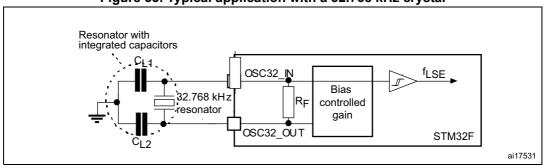

Figure 33. Typical application with a 32.768 kHz crystal

#### 5.3.9 Internal clock source characteristics

The parameters given in *Table 34* and *Table 35* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

#### High-speed internal (HSI) RC oscillator

| Symbol                              | Parameter                             | Conditions                           | Min | Тур | Max | Unit |  |  |  |  |  |

|-------------------------------------|---------------------------------------|--------------------------------------|-----|-----|-----|------|--|--|--|--|--|

| f <sub>HSI</sub>                    | Frequency                             | -                                    | -   | 16  | -   | MHz  |  |  |  |  |  |

| 100                                 | HSI user trimming step <sup>(2)</sup> | -                                    | -   | -   | 1   | %    |  |  |  |  |  |

|                                     |                                       | $T_A = -40$ to 105 °C <sup>(3)</sup> | -8  | -   | 4.5 | %    |  |  |  |  |  |

| ACC <sub>HSI</sub>                  | Accuracy of the HSI oscillator        | $T_A = -10$ to 85 °C <sup>(3)</sup>  | -4  | -   | 4   | %    |  |  |  |  |  |

|                                     |                                       | $T_A = 25 \ ^{\circ}C^{(4)}$         | -1  | -   | 1   | %    |  |  |  |  |  |

| t <sub>su(HSI)</sub> <sup>(2)</sup> | HSI oscillator startup time           | -                                    | -   | 2.2 | 4   | μs   |  |  |  |  |  |

| I <sub>DD(HSI)</sub> <sup>(2)</sup> | HSI oscillator power<br>consumption   | -                                    | -   | 60  | 80  | μA   |  |  |  |  |  |

Table 34. HSI oscillator characteristics <sup>(1)</sup>

1.  $V_{DD}$  = 3.3 V,  $T_A$  = -40 to 105 °C unless otherwise specified.

2. Guaranteed by design.

3. Guaranteed by characterization.

4. Factory calibrated, parts not soldered.

#### Low-speed internal (LSI) RC oscillator

| Table 35. LSI oscillator characteristics | (1 | ) |

|------------------------------------------|----|---|

|------------------------------------------|----|---|

| Symbol                              | Parameter                        | Min | Тур | Мах | Unit |

|-------------------------------------|----------------------------------|-----|-----|-----|------|

| f <sub>LSI</sub> <sup>(2)</sup>     | Frequency                        | 17  | 32  | 47  | kHz  |

| t <sub>su(LSI)</sub> <sup>(3)</sup> | LSI oscillator startup time      | -   | 15  | 40  | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption | -   | 0.4 | 0.6 | μA   |

1.  $V_{DD}$  = 3 V,  $T_A$  = -40 to 105 °C unless otherwise specified.

2. Guaranteed by characterization.

3. Guaranteed by design.

| Symbol                  | Parameter                  | Conditions                                  | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit |  |

|-------------------------|----------------------------|---------------------------------------------|--------------------|-----|--------------------|------|--|

|                         | Sector (128 KB) erase time | Program/erase parallelism<br>(PSIZE) = x 8  | -                  | 2   | 4                  |      |  |

| t <sub>ERASE128KB</sub> |                            | Program/erase parallelism<br>(PSIZE) = x 16 | -                  | 1.3 | 2.6                | S    |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32 | -                  | 1   | 2                  |      |  |

| t <sub>ME</sub>         | Mass erase time            | Program/erase parallelism<br>(PSIZE) = x 8  | -                  | 16  | 32                 |      |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 16 | -                  | 11  | 22                 | s    |  |

|                         |                            | Program/erase parallelism<br>(PSIZE) = x 32 | -                  | 8   | 16                 |      |  |

| V <sub>prog</sub>       | Programming voltage        | 32-bit program operation                    | 2.7                | -   | 3.6                | V    |  |

|                         |                            | 16-bit program operation                    | 2.1                | -   | 3.6                | V    |  |

|                         |                            | 8-bit program operation                     | 1.8                | -   | 3.6                | V    |  |

| Table 40. Flash memory programming | (continued) |

|------------------------------------|-------------|

|------------------------------------|-------------|

1. Guaranteed by characterization.

2. The maximum programming time is measured after 100K erase operations.

A device reset allows normal operations to be resumed.

The test results are given in *Table 43*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                              | Level/<br>Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | V <sub>DD</sub> = 3.3 V, LQFP176, T <sub>A</sub> =<br>+25 °C, f <sub>HCLK</sub> = 168 MHz, conforms<br>to IEC 61000-4-2 | 2B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | V <sub>DD</sub> = 3.3 V, LQFP176, T <sub>A</sub> =<br>+25 °C, f <sub>HCLK</sub> = 168 MHz, conforms<br>to IEC 61000-4-2 | 4A              |

#### Table 43. EMS characteristics

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

#### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

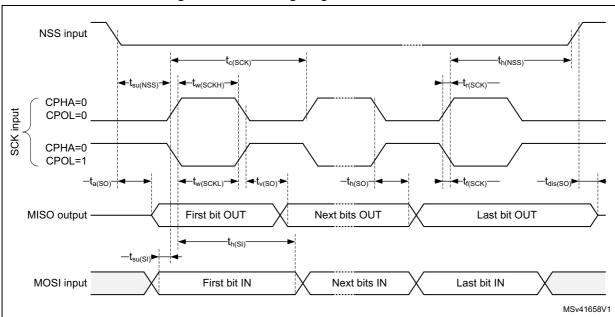

Figure 39. SPI timing diagram - slave mode and CPHA = 0

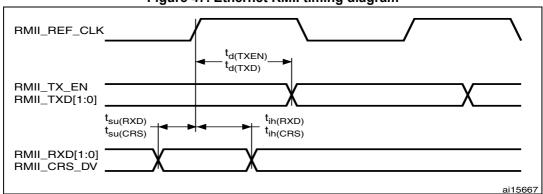

Figure 47. Ethernet RMII timing diagram

| Symbol               | Rating                           | Min | Тур | Max  | Unit |

|----------------------|----------------------------------|-----|-----|------|------|

| t <sub>su(RXD)</sub> | Receive data setup time          | 2   | -   | -    | ns   |

| t <sub>ih(RXD)</sub> | Receive data hold time           | 1   | -   | -    | ns   |

| t <sub>su(CRS)</sub> | Carrier sense set-up time        | 0.5 | -   | -    | ns   |

| t <sub>ih(CRS)</sub> | Carrier sense hold time          | 2   | -   | -    | ns   |

| t <sub>d(TXEN)</sub> | Transmit enable valid delay time | 8   | 9.5 | 11   | ns   |

| t <sub>d(TXD)</sub>  | Transmit data valid delay time   | 8.5 | 10  | 11.5 | ns   |

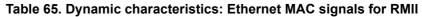

*Table 66* gives the list of Ethernet MAC signals for MII and *Figure 47* shows the corresponding timing diagram.

Figure 48. Ethernet MII timing diagram

| Symbol                      | Parameter                                      | Min                | Мах | Unit |

|-----------------------------|------------------------------------------------|--------------------|-----|------|

| t <sub>w(CLK)</sub>         | FSMC_CLK period                                | 2T <sub>HCLK</sub> | -   | ns   |

| t <sub>d(CLKL-NExL)</sub>   | FSMC_CLK low to FSMC_NEx low (x=02)            | -                  | 0   | ns   |

| t <sub>d(CLKL-NExH)</sub>   | FSMC_CLK low to FSMC_NEx high (x= 02)          | 2                  | -   | ns   |

| t <sub>d(CLKL-NADVL)</sub>  | FSMC_CLK low to FSMC_NADV low                  | -                  | 2   | ns   |

| t <sub>d(CLKL-NADVH)</sub>  | FSMC_CLK low to FSMC_NADV high                 | 2                  | -   | ns   |

| t <sub>d(CLKL-AV)</sub>     | FSMC_CLK low to FSMC_Ax valid (x=1625)         | -                  | 0   | ns   |

| t <sub>d(CLKL-AIV)</sub>    | FSMC_CLK low to FSMC_Ax invalid (x=1625)       | 0                  | -   | ns   |

| t <sub>d(CLKL-NOEL)</sub>   | FSMC_CLK low to FSMC_NOE low                   | -                  | 0   | ns   |

| t <sub>d(CLKL-NOEH)</sub>   | FSMC_CLK low to FSMC_NOE high                  | 2                  | -   | ns   |

| t <sub>d(CLKL-ADV)</sub>    | FSMC_CLK low to FSMC_AD[15:0] valid            | -                  | 4.5 | ns   |

| t <sub>d(CLKL-ADIV)</sub>   | FSMC_CLK low to FSMC_AD[15:0] invalid          | 0                  | -   | ns   |

| t <sub>su(ADV-CLKH)</sub>   | FSMC_A/D[15:0] valid data before FSMC_CLK high | 6                  | -   | ns   |

| t <sub>h(CLKH-ADV)</sub>    | FSMC_A/D[15:0] valid data after FSMC_CLK high  | 0                  | -   | ns   |

| t <sub>su(NWAIT-CLKH)</sub> | FSMC_NWAIT valid before FSMC_CLK high          | 4                  | -   | ns   |

| t <sub>h(CLKH-NWAIT)</sub>  | FSMC_NWAIT valid after FSMC_CLK high           | 0                  | -   | ns   |

Table 79. Synchronous multiplexed NOR/PSRAM read timings<sup>(1)(2)</sup>

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization.

| Symbol                      | Parameter                                    | Min                     | Max | Unit |

|-----------------------------|----------------------------------------------|-------------------------|-----|------|

| t <sub>w(CLK)</sub>         | FSMC_CLK period                              | 2T <sub>HCLK</sub> –0.5 | -   | ns   |

| t <sub>d(CLKL-NExL)</sub>   | FSMC_CLK low to FSMC_NEx low (x=02)          | -                       | 0.5 | ns   |

| t <sub>d(CLKL-NExH)</sub>   | FSMC_CLK low to FSMC_NEx high (x= 02)        | 0                       | -   | ns   |

| t <sub>d(CLKL-NADVL)</sub>  | FSMC_CLK low to FSMC_NADV low                | -                       | 2   | ns   |

| t <sub>d(CLKL-NADVH)</sub>  | FSMC_CLK low to FSMC_NADV high               | 3                       | -   | ns   |

| t <sub>d(CLKL-AV)</sub>     | FSMC_CLK low to FSMC_Ax valid (x=1625)       | -                       | 0   | ns   |

| t <sub>d(CLKL-AIV)</sub>    | FSMC_CLK low to FSMC_Ax invalid (x=1625)     | 2                       | -   | ns   |

| t <sub>d(CLKL-NOEL)</sub>   | FSMC_CLK low to FSMC_NOE low                 | -                       | 0.5 | ns   |

| t <sub>d(CLKL-NOEH)</sub>   | FSMC_CLK low to FSMC_NOE high                | 1.5                     | -   | ns   |

| t <sub>su(DV-CLKH)</sub>    | FSMC_D[15:0] valid data before FSMC_CLK high | 6                       | -   | ns   |

| t <sub>h(CLKH-DV)</sub>     | FSMC_D[15:0] valid data after FSMC_CLK high  | 3                       | -   | ns   |

| t <sub>su(NWAIT-CLKH)</sub> | FSMC_NWAIT valid before FSMC_CLK high        | 4                       | -   | ns   |

| t <sub>h(CLKH-NWAIT)</sub>  | FSMC_NWAIT valid after FSMC_CLK high         | 0                       | -   | ns   |

Table 81. Synchronous non-multiplexed NOR/PSRAM read timings<sup>(1)(2)</sup>

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization.

|                   |             | расказ | je mechanic |                       |        |        |  |

|-------------------|-------------|--------|-------------|-----------------------|--------|--------|--|

| Symbol            | millimeters |        |             | inches <sup>(1)</sup> |        |        |  |

| Symbol            | Min         | Тур    | Мах         | Min                   | Тур    | Max    |  |

| А                 | 0.540       | 0.570  | 0.600       | 0.0213                | 0.0224 | 0.0236 |  |

| A1                | -           | 0.190  | -           | -                     | 0.0075 | -      |  |

| A2                | -           | 0.380  | -           | -                     | 0.0150 | -      |  |

| A3 <sup>(2)</sup> | -           | 0.025  | -           | -                     | 0.0010 | -      |  |

| b <sup>(3)</sup>  | 0.240       | 0.270  | 0.300       | 0.0094                | 0.0106 | 0.0118 |  |

| D                 | 4.188       | 4.223  | 4.258       | 0.1649                | 0.1663 | 0.1676 |  |

| E                 | 3.934       | 3.969  | 4.004       | 0.1549                | 0.1563 | 0.1576 |  |

| е                 | -           | 0.400  | -           | -                     | 0.0157 | -      |  |

| e1                | -           | 3.600  | -           | -                     | 0.1417 | -      |  |

| e2                | -           | 3.200  | -           | -                     | 0.1260 | -      |  |

| F                 | -           | 0.3115 | -           | -                     | 0.0123 | -      |  |

| G                 | -           | 0.3845 | -           | -                     | 0.0151 | -      |  |

| aaa               | -           | 0.100  | -           | -                     | 0.0039 | -      |  |

| bbb               | -           | 0.100  | -           | -                     | 0.0039 | -      |  |

| ссс               | -           | 0.100  | -           | -                     | 0.0039 | -      |  |

| ddd               | -           | 0.050  | -           | -                     | 0.0020 | -      |  |

| eee               | -           | 0.050  | -           | -                     | 0.0020 | -      |  |

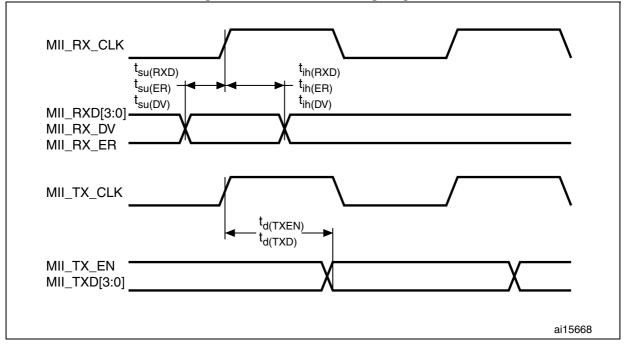

## Table 90. WLCSP90 - 4.223 x 3.969 mm, 0.400 mm pitch wafer level chip scale package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. Back side coating.

3. Dimension is measured at the maximum bump diameter parallel to primary datum Z.

## Figure 76. WLCSP90 - 4.223 x 3.969 mm, 0.400 mm pitch wafer level chip scale recommended footprint

## 7 Part numbering

| Example:                                                   | STM32 | F | 405 R | E | Т | 6 | xxx |

|------------------------------------------------------------|-------|---|-------|---|---|---|-----|

| Device family                                              |       |   |       |   |   |   |     |

| STM32 = ARM-based 32-bit microcontroller                   |       |   |       |   |   |   |     |

|                                                            |       |   |       |   |   |   |     |

| Product type                                               |       |   |       |   |   |   |     |

| F = general-purpose                                        |       |   |       |   |   |   |     |

|                                                            |       |   |       |   |   |   |     |

| Device subfamily                                           |       |   |       |   |   |   |     |

| 405 = STM32F40xxx, connectivity                            |       |   | _     |   |   |   |     |

| 407= STM32F40xxx, connectivity, camera interface, Ethernet |       |   |       |   |   |   |     |

|                                                            |       |   |       |   |   |   |     |

|                                                            |       |   |       |   |   |   |     |

| Pin count                                                  |       |   |       |   |   |   |     |

| R = 64 pins                                                |       |   |       |   |   |   |     |

| O = 90 pins                                                |       |   |       |   |   |   |     |

| V = 100 pins                                               |       |   |       |   |   |   |     |

| Z = 144 pins                                               |       |   |       |   |   |   |     |

| I = 176 pins                                               |       |   |       |   |   |   |     |

|                                                            |       |   |       |   |   |   |     |

| Flash memory size                                          |       |   |       |   |   |   |     |

| E = 512 Kbytes of Flash memory                             |       |   |       |   |   |   |     |

| G = 1024 Kbytes of Flash memory                            |       |   |       |   |   |   |     |

|                                                            |       |   |       |   |   |   |     |

| Package                                                    |       |   |       |   |   |   |     |

| T = LQFP                                                   |       |   |       |   |   |   |     |

| H = UFBGA                                                  |       |   |       |   |   |   |     |

| Y = WLCSP                                                  |       |   |       |   |   |   |     |

|                                                            |       |   |       |   |   |   |     |

| Temperature range                                          |       |   |       |   |   |   |     |

| 6 = Industrial temperature range, -40 to 85 °C.            |       |   |       |   |   |   |     |

| 7 = Industrial temperature range, –40 to 105 °C.           |       |   |       |   |   |   |     |

|                                                            |       |   |       |   |   |   |     |

| Options                                                    |       |   |       |   |   |   |     |

#### Table 99. Ordering information scheme

xxx = programmed parts

TR = tape and reel

For a list of available options (speed, package, etc.) or for further information on any aspect of this device, please contact your nearest ST sales office.

DocID022152 Rev 8