Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                    |

|----------------------------|-------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                        |

| Speed                      | 168MHz                                                                                    |

| Connectivity               | CANbus, DCMI, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                         |

| Number of I/O              | 140                                                                                       |

| Program Memory Size        | 1MB (1M x 8)                                                                              |

| Program Memory Type        | FLASH                                                                                     |

| EEPROM Size                | -                                                                                         |

| RAM Size                   | 192K x 8                                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                               |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                     |

| Oscillator Type            | Internal                                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                         |

| Mounting Type              | Surface Mount                                                                             |

| Package / Case             | 176-LQFP                                                                                  |

| Supplier Device Package    | 176-LQFP (24x24)                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f407igt6                     |

|                            |                                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2 Description

The STM32F405xx and STM32F407xx family is based on the high-performance ARM<sup>®</sup> Cortex<sup>®</sup>-M4 32-bit RISC core operating at a frequency of up to 168 MHz. The Cortex-M4 core features a Floating point unit (FPU) single precision which supports all ARM single-precision data-processing instructions and data types. It also implements a full set of DSP instructions and a memory protection unit (MPU) which enhances application security.

The STM32F405xx and STM32F407xx family incorporates high-speed embedded memories (Flash memory up to 1 Mbyte, up to 192 Kbytes of SRAM), up to 4 Kbytes of backup SRAM, and an extensive range of enhanced I/Os and peripherals connected to two APB buses, three AHB buses and a 32-bit multi-AHB bus matrix.

All devices offer three 12-bit ADCs, two DACs, a low-power RTC, twelve general-purpose 16-bit timers including two PWM timers for motor control, two general-purpose 32-bit timers. a true random number generator (RNG). They also feature standard and advanced communication interfaces.

- Up to three I<sup>2</sup>Cs

- Three SPIs, two I<sup>2</sup>Ss full duplex. To achieve audio class accuracy, the I2S peripherals can be clocked via a dedicated internal audio PLL or via an external clock to allow synchronization.

- Four USARTs plus two UARTs

- An USB OTG full-speed and a USB OTG high-speed with full-speed capability (with the ULPI),

- Two CANs

- An SDIO/MMC interface

- Ethernet and the camera interface available on STM32F407xx devices only.

New advanced peripherals include an SDIO, an enhanced flexible static memory control (FSMC) interface (for devices offered in packages of 100 pins and more), a camera interface for CMOS sensors. Refer to *Table 2: STM32F405xx and STM32F407xx: features and peripheral counts* for the list of peripherals available on each part number.

The STM32F405xx and STM32F407xx family operates in the –40 to +105 °C temperature range from a 1.8 to 3.6 V power supply. The supply voltage can drop to 1.7 V when the device operates in the 0 to 70 °C temperature range using an external power supply supervisor: refer to *Section : Internal reset OFF*. A comprehensive set of power-saving mode allows the design of low-power applications.

The STM32F405xx and STM32F407xx family offers devices in various packages ranging from 64 pins to 176 pins. The set of included peripherals changes with the device chosen.

These features make the STM32F405xx and STM32F407xx microcontroller family suitable for a wide range of applications:

- Motor drive and application control

- Medical equipment

- Industrial applications: PLC, inverters, circuit breakers

- Printers, and scanners

- Alarm systems, video intercom, and HVAC

- Home audio appliances

## 2.2.31 Universal serial bus on-the-go high-speed (OTG\_HS)

The STM32F405xx and STM32F407xx devices embed a USB OTG high-speed (up to 480 Mb/s) device/host/OTG peripheral. The USB OTG HS supports both full-speed and high-speed operations. It integrates the transceivers for full-speed operation (12 MB/s) and features a UTMI low-pin interface (ULPI) for high-speed operation (480 MB/s). When using the USB OTG HS in HS mode, an external PHY device connected to the ULPI is required.

The USB OTG HS peripheral is compliant with the USB 2.0 specification and with the OTG 1.0 specification. It has software-configurable endpoint setting and supports suspend/resume. The USB OTG full-speed controller requires a dedicated 48 MHz clock that is generated by a PLL connected to the HSE oscillator.

The major features are:

- Combined Rx and Tx FIFO size of 1 Kbit × 35 with dynamic FIFO sizing

- Supports the session request protocol (SRP) and host negotiation protocol (HNP)

- 6 bidirectional endpoints

- 12 host channels with periodic OUT support

- Internal FS OTG PHY support

- External HS or HS OTG operation supporting ULPI in SDR mode. The OTG PHY is connected to the microcontroller ULPI port through 12 signals. It can be clocked using the 60 MHz output.

- Internal USB DMA

- HNP/SNP/IP inside (no need for any external resistor)

- for OTG/Host modes, a power switch is needed in case bus-powered devices are connected

### 2.2.32 Digital camera interface (DCMI)

The camera interface is *not* available in STM32F405xx devices.

STM32F407xx products embed a camera interface that can connect with camera modules and CMOS sensors through an 8-bit to 14-bit parallel interface, to receive video data. The camera interface can sustain a data transfer rate up to 54 Mbyte/s at 54 MHz. It features:

- Programmable polarity for the input pixel clock and synchronization signals

- Parallel data communication can be 8-, 10-, 12- or 14-bit

- Supports 8-bit progressive video monochrome or raw bayer format, YCbCr 4:2:2 progressive video, RGB 565 progressive video or compressed data (like JPEG)

- Supports continuous mode or snapshot (a single frame) mode

- Capability to automatically crop the image

### 2.2.33 Random number generator (RNG)

All STM32F405xx and STM32F407xx products embed an RNG that delivers 32-bit random numbers generated by an integrated analog circuit.

### 2.2.34 General-purpose input/outputs (GPIOs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain, with or without pull-up or pull-down), as input (floating, with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog

|        | F       | Pin r   | numb    |          |         |                                                      |          |                 |       | demittions (continued)                                                                                     |                         |

|--------|---------|---------|---------|----------|---------|------------------------------------------------------|----------|-----------------|-------|------------------------------------------------------------------------------------------------------------|-------------------------|

| LQFP64 | WLCSP90 | LQFP100 | LQFP144 | UFBGA176 | LQFP176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes | Alternate functions                                                                                        | Additional<br>functions |

| 29     | H4      | 47      | 69      | R12      | 79      | PB10                                                 | I/O      | FT              | -     | SPI2_SCK / I2S2_CK /<br>I2C2_SCL/ USART3_TX /<br>OTG_HS_ULPI_D3 /<br>ETH_MII_RX_ER /<br>TIM2_CH3/ EVENTOUT | -                       |

| 30     | J4      | 48      | 70      | R13      | 80      | PB11                                                 | I/O      | FT              | -     | I2C2_SDA/USART3_RX/<br>OTG_HS_ULPI_D4 /<br>ETH_RMII_TX_EN/<br>ETH_MII_TX_EN /<br>TIM2_CH4/ EVENTOUT        | -                       |

| 31     | F4      | 49      | 71      | M10      | 81      | V <sub>CAP_1</sub>                                   | S        |                 | -     | -                                                                                                          | -                       |

| 32     | -       | 50      | 72      | N10      | 82      | V <sub>DD</sub>                                      | S        |                 | -     | -                                                                                                          | -                       |

| -      | -       | -       | -       | M11      | 83      | PH6                                                  | I/O      | FT              | -     | I2C2_SMBA / TIM12_CH1 /<br>ETH_MII_RXD2/<br>EVENTOUT                                                       | -                       |

| -      | -       | -       | -       | N12      | 84      | PH7                                                  | I/O      | FT              | -     | I2C3_SCL /<br>ETH_MII_RXD3/<br>EVENTOUT                                                                    | -                       |

| -      | -       | -       | -       | M12      | 85      | PH8                                                  | I/O      | FT              | -     | I2C3_SDA /<br>DCMI_HSYNC/<br>EVENTOUT                                                                      | -                       |

| -      | -       | -       | -       | M13      | 86      | PH9                                                  | I/O      | FT              | -     | I2C3_SMBA / TIM12_CH2/<br>DCMI_D0/ EVENTOUT                                                                | -                       |

| -      | -       | -       | -       | L13      | 87      | PH10                                                 | I/O      | FT              | -     | TIM5_CH1 / DCMI_D1/<br>EVENTOUT                                                                            | -                       |

| -      | -       | -       | -       | L12      | 88      | PH11                                                 | I/O      | FT              | -     | TIM5_CH2 / DCMI_D2/<br>EVENTOUT                                                                            | -                       |

| -      | -       | -       | -       | K12      | 89      | PH12                                                 | I/O      | FT              | -     | TIM5_CH3 / DCMI_D3/<br>EVENTOUT                                                                            | -                       |

| -      | -       | -       | I       | H12      | 90      | V <sub>SS</sub>                                      | S        | -               | -     | -                                                                                                          | -                       |

| -      | -       | -       | -       | J12      | 91      | $V_{DD}$                                             | S        | -               | -     | -                                                                                                          | -                       |

Table 7. STM32F40xxx pin and ball definitions (continued)

|        | I       | Pin r   | numb    |          |         |                                                      |          |                 |       | definitions (continued)                                                                                                         |                         |

|--------|---------|---------|---------|----------|---------|------------------------------------------------------|----------|-----------------|-------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| LQFP64 | WLCSP90 | LQFP100 | LQFP144 | UFBGA176 | LQFP176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type | I / O structure | Notes | Alternate functions                                                                                                             | Additional<br>functions |

| 55     | B6      | 89      | 133     | A10      | 161     | PB3<br>(JTDO/<br>TRACESWO)                           | I/O      | FT              | -     | JTDO/ TRACESWO/<br>SPI3_SCK / I2S3_CK /<br>TIM2_CH2 / SPI1_SCK/<br>EVENTOUT                                                     | _                       |

| 56     | A6      | 90      | 134     | A9       | 162     | PB4<br>(NJTRST)                                      | I/O      | FT              | -     | NJTRST/ SPI3_MISO /<br>TIM3_CH1 / SPI1_MISO /<br>I2S3ext_SD/ EVENTOUT                                                           | -                       |

| 57     | D7      | 91      | 135     | A6       | 163     | PB5                                                  | I/O      | FT              | -     | I2C1_SMBA/ CAN2_RX /<br>OTG_HS_ULPI_D7 /<br>ETH_PPS_OUT/TIM3_CH2<br>/ SPI1_MOSI/ SPI3_MOSI /<br>DCMI_D10 / I2S3_SD/<br>EVENTOUT | -                       |

| 58     | C7      | 92      | 136     | В6       | 164     | PB6                                                  | I/O      | FT              | -     | I2C1_SCL/ TIM4_CH1 /<br>CAN2_TX /<br>DCMI_D5/USART1_TX/<br>EVENTOUT                                                             | -                       |

| 59     | В7      | 93      | 137     | В5       | 165     | PB7                                                  | I/O      | FT              | -     | I2C1_SDA / FSMC_NL /<br>DCMI_VSYNC /<br>USART1_RX/ TIM4_CH2/<br>EVENTOUT                                                        | -                       |

| 60     | A7      | 94      | 138     | D6       | 166     | BOOT0                                                | Ι        | В               | -     | -                                                                                                                               | V <sub>PP</sub>         |

| 61     | D8      | 95      | 139     | A5       | 167     | PB8                                                  | I/O      | FT              | -     | TIM4_CH3/SDIO_D4/<br>TIM10_CH1 / DCMI_D6 /<br>ETH_MII_TXD3 /<br>I2C1_SCL/ CAN1_RX/<br>EVENTOUT                                  | -                       |

| 62     | C8      | 96      | 140     | B4       | 168     | PB9                                                  | I/O      | FT              | -     | SPI2_NSS/ I2S2_WS /<br>TIM4_CH4/ TIM11_CH1/<br>SDIO_D5 / DCMI_D7 /<br>I2C1_SDA / CAN1_TX/<br>EVENTOUT                           | -                       |

| -      | -       | 97      | 141     | A4       | 169     | PE0                                                  | I/O      | FT              | -     | TIM4_ETR / FSMC_NBL0 /<br>DCMI_D2/ EVENTOUT                                                                                     | -                       |

| -      | -       | 98      | 142     | A3       | 170     | PE1                                                  | I/O      | FT              | -     | FSMC_NBL1 / DCMI_D3/<br>EVENTOUT                                                                                                | -                       |

| 63     | -       | 99      | -       | D5       | -       | $V_{SS}$                                             | S        | -               | -     | -                                                                                                                               | -                       |

65/202

DocID022152 Rev 8

|        |      |     |        |          |                  |          |                                |                      |                        |                    | (00                       | ,                 |      |                        |          |      |          |

|--------|------|-----|--------|----------|------------------|----------|--------------------------------|----------------------|------------------------|--------------------|---------------------------|-------------------|------|------------------------|----------|------|----------|

|        |      | AF0 | AF1    | AF2      | AF3              | AF4      | AF5                            | AF6                  | AF7                    | AF8                | AF9                       | AF10              | AF11 | AF12                   | AF13     |      |          |

| Port   | ort  | SYS | TIM1/2 | TIM3/4/5 | TIM8/9/10<br>/11 | I2C1/2/3 | SPI1/SPI2/<br>I2S2/I2S2e<br>xt | SPI3/I2Sext<br>/I2S3 | USART1/2/3/<br>I2S3ext | UART4/5/<br>USART6 | CAN1/2<br>TIM12/13/<br>14 | OTG_FS/<br>OTG_HS | ЕТН  | FSMC/SDIO<br>/OTG_FS   | DCMI     | AF14 | AF15     |

|        | PD0  | -   | -      | -        | -                | -        | -                              | -                    | -                      | -                  | CAN1_RX                   | -                 | -    | FSMC_D2                | -        | -    | EVENTOUT |

|        | PD1  | -   | -      | -        | -                | -        | -                              | -                    | -                      | -                  | CAN1_TX                   | -                 | -    | FSMC_D3                | -        | -    | EVENTOUT |

|        | PD2  | -   | -      | TIM3_ETR | -                | -        | -                              | -                    | -                      | UART5_RX           | -                         | -                 | -    | SDIO_CMD               | DCMI_D11 | -    | EVENTOUT |

|        | PD3  | -   | -      | -        | -                | -        | -                              | -                    | USART2_CTS             | -                  | -                         | -                 | -    | FSMC_CLK               | -        | -    | EVENTOUT |

|        | PD4  | -   | -      | -        | -                | -        | -                              | -                    | USART2_RTS             | -                  | -                         | -                 | -    | FSMC_NOE               | -        | -    | EVENTOUT |

|        | PD5  | -   | -      | -        | -                | -        | -                              | -                    | USART2_TX              | -                  | -                         | -                 | -    | FSMC_NWE               | -        | -    | EVENTOUT |

|        | PD6  | -   | -      | -        | -                | -        | -                              | -                    | USART2_RX              | -                  | -                         | -                 | -    | FSMC_NWAIT             | -        | -    | EVENTOUT |

| Port D | PD7  | -   | -      | -        | -                | -        | -                              | -                    | USART2_CK              | -                  | -                         | -                 | -    | FSMC_NE1/<br>FSMC_NCE2 | -        | -    | EVENTOUT |

|        | PD8  | -   | -      | -        | -                | -        | -                              | -                    | USART3_TX              | -                  | -                         | -                 | -    | FSMC_D13               | -        | -    | EVENTOUT |

|        | PD9  | -   | -      | -        | -                | -        | -                              | -                    | USART3_RX              | -                  | -                         | -                 | -    | FSMC_D14               | -        | -    | EVENTOUT |

|        | PD10 | -   | -      | -        | -                | -        | -                              | -                    | USART3_CK              | -                  | -                         | -                 | -    | FSMC_D15               | -        | -    | EVENTOUT |

|        | PD11 | -   | -      | -        | -                | -        | -                              | -                    | USART3_CTS             | -                  | -                         | -                 | -    | FSMC_A16               | -        | -    | EVENTOUT |

|        | PD12 | -   | -      | TIM4_CH1 | -                | -        | -                              | -                    | USART3_RTS             | -                  | -                         | -                 | -    | FSMC_A17               | -        | -    | EVENTOUT |

|        | PD13 | -   | -      | TIM4_CH2 | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A18               | -        | -    | EVENTOUT |

|        | PD14 | -   | -      | TIM4_CH3 | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_D0                | -        | -    | EVENTOUT |

|        | PD15 | -   | -      | TIM4_CH4 | -                | -        | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_D1                | -        | -    | EVENTOUT |

#### Table 9. Alternate function mapping (continued)

577

| Bus       | Boundary address          | Peripheral                     |

|-----------|---------------------------|--------------------------------|

|           | 0xE00F FFFF - 0xFFFF FFFF | Reserved                       |

|           |                           |                                |

| Cortex-M4 | 0xE000 0000 - 0xE00F FFFF | Cortex-M4 internal peripherals |

|           | 0xA000 1000 - 0xDFFF FFFF | Reserved                       |

|           | 0xA000 0000 - 0xA000 0FFF | FSMC control register          |

| AHB3      | 0x9000 0000 - 0x9FFF FFFF | FSMC bank 4                    |

|           | 0x8000 0000 - 0x8FFF FFFF | FSMC bank 3                    |

|           | 0x7000 0000 - 0x7FFF FFFF | FSMC bank 2                    |

|           | 0x6000 0000 - 0x6FFF FFFF | FSMC bank 1                    |

|           | 0x5006 0C00- 0x5FFF FFFF  | Reserved                       |

|           | 0x5006 0800 - 0x5006 0BFF | RNG                            |

| AHB2      | 0x5005 0400 - 0x5006 07FF | Reserved                       |

|           | 0x5005 0000 - 0x5005 03FF | DCMI                           |

|           | 0x5004 0000- 0x5004 FFFF  | Reserved                       |

|           | 0x5000 0000 - 0x5003 FFFF | USB OTG FS                     |

|           | 0x4008 0000- 0x4FFF FFFF  | Reserved                       |

Table 10. register boundary addresses

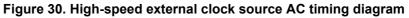

#### Low-speed external user clock generated from an external source

The characteristics given in *Table 31* result from tests performed using an low-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 14*.

| Symbol                                     | Parameter                                              | Conditions                                     | Min                | Тур    | Max                | Unit |

|--------------------------------------------|--------------------------------------------------------|------------------------------------------------|--------------------|--------|--------------------|------|

| f <sub>LSE_ext</sub>                       | User External clock source<br>frequency <sup>(1)</sup> |                                                | -                  | 32.768 | 1000               | kHz  |

| V <sub>LSEH</sub>                          | OSC32_IN input pin high level voltage                  |                                                | 0.7V <sub>DD</sub> | -      | V <sub>DD</sub>    | V    |

| V <sub>LSEL</sub>                          | OSC32_IN input pin low level voltage                   | -                                              | V <sub>SS</sub>    | -      | 0.3V <sub>DD</sub> |      |

| t <sub>w(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN high or low time <sup>(1)</sup>               |                                                | 450                | -      | -                  | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN rise or fall time <sup>(1)</sup>              |                                                | -                  | -      | 50                 | 115  |

| C <sub>in(LSE)</sub>                       | OSC32_IN input capacitance <sup>(1)</sup>              | -                                              | -                  | 5      | -                  | pF   |

| DuCy <sub>(LSE)</sub>                      | Duty cycle                                             | -                                              | 30                 | -      | 70                 | %    |

| ال                                         | OSC32_IN Input leakage current                         | $V_{SS} \!\leq\! \! V_{IN} \!\leq\! \! V_{DD}$ | -                  | -      | ±1                 | μA   |

| Table 31. Low-speed external user clock characteristics |

|---------------------------------------------------------|

|---------------------------------------------------------|

1. Guaranteed by design.

Note:

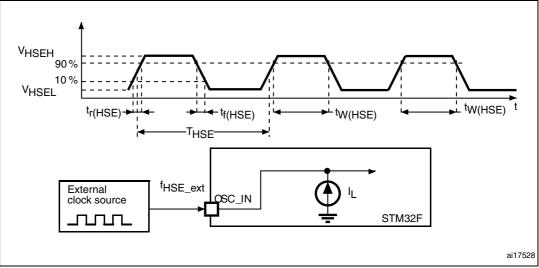

For information on electing the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <a href="https://www.st.com">www.st.com</a>.

Figure 32. Typical application with an 8 MHz crystal

1. R<sub>EXT</sub> value depends on the crystal characteristics.

#### Low-speed external clock generated from a crystal/ceramic resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 33*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter                               | Conditions                    | Min | Тур    | Мах  | Unit |

|-------------------------------------|-----------------------------------------|-------------------------------|-----|--------|------|------|

| f <sub>OSC_IN</sub>                 | Oscillator frequency                    | -                             | -   | 32.768 | -    | MHz  |

| R <sub>F</sub>                      | Feedback resistor -                     |                               | -   | 18.4   | -    | MΩ   |

| I <sub>DD</sub>                     | LSE current consumption -               |                               | -   | -      | 1    | μA   |

| G <sub>m</sub>                      | Oscillator transconductance             | Startup                       | 2.8 | -      | -    |      |

| G <sub>mcritmax</sub>               | Maximum critical crystal G <sub>m</sub> | Startup                       | -   | -      | 0.56 | μA/V |

| t <sub>SU(LSE)</sub> <sup>(2)</sup> | startup time                            | $V_{\text{DD}}$ is stabilized | -   | 2      | -    | S    |

Table 33. LSE oscillator characteristics (f<sub>LSE</sub> = 32.768 kHz) <sup>(1)</sup>

1. Guaranteed by design.

Guaranteed by characterization. t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer

*Note:* For information on electing the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

#### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application, executing EEMBC<sup>?</sup> code, is running. This emission test is compliant with SAE IEC61967-2 standard which specifies the test board and the pin loading.

| Symbol           | Parameter  | Conditions                                                                                           | Monitored<br>frequency band | Max vs.<br>[f <sub>HSE</sub> /f <sub>CPU</sub> ] | Unit |  |

|------------------|------------|------------------------------------------------------------------------------------------------------|-----------------------------|--------------------------------------------------|------|--|

|                  |            |                                                                                                      |                             | 25/168 MHz                                       |      |  |

|                  |            | V <sub>DD</sub> = 3.3 V, T <sub>A</sub> = 25 °C, LQFP176                                             | 0.1 to 30 MHz               | 32                                               |      |  |

|                  |            | package, conforming to SAE J1752/3<br>EEMBC, code running from Flash with<br>ART accelerator enabled | 30 to 130 MHz               | 25                                               | dBµV |  |

|                  |            |                                                                                                      | 130 MHz to 1GHz             | 29                                               |      |  |

| S                | Peak level |                                                                                                      | SAE EMI Level               | 4                                                | -    |  |

| S <sub>EMI</sub> |            | V <sub>DD</sub> = 3.3 V, T <sub>A</sub> = 25 °C, LQFP176                                             | 0.1 to 30 MHz               | 19                                               |      |  |

|                  |            | package, conforming to SAE J1752/3                                                                   | 30 to 130 MHz               | 16                                               | dBµV |  |

|                  |            | EEMBC, code running from Flash with ART accelerator and PLL spread                                   | 130 MHz to 1GHz             | 18                                               |      |  |

|                  |            | spectrum enabled                                                                                     | SAE EMI level               | 3.5                                              | -    |  |

| Table 44. | EMI | characteristics |

|-----------|-----|-----------------|

|-----------|-----|-----------------|

### 5.3.14 Absolute maximum ratings (electrical sensitivity)

Based on three different tests (ESD, LU) using specific measurement methods, the device is stressed in order to determine its performance in terms of electrical sensitivity.

#### Electrostatic discharge (ESD)

Electrostatic discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts  $\times$  (n+1) supply pins). This test conforms to the JESD22-A114/C101 standard.

| Symbol                | Ratings                                                  | Conditions                                                | Class | Maximum<br>value <sup>(1)</sup> | Unit |

|-----------------------|----------------------------------------------------------|-----------------------------------------------------------|-------|---------------------------------|------|

| V <sub>ESD(HBM)</sub> | Electrostatic discharge<br>voltage (human body<br>model) | $T_A = +25 \ ^{\circ}C$ conforming to JESD22-A114         | 2     | 2000 <sup>(2)</sup>             | v    |

| V <sub>ESD(CDM)</sub> | Electrostatic discharge voltage (charge device model)    | $T_A = +25 \text{ °C conforming to}$<br>ANSI/ESD STM5.3.1 | II    | 500                             | v    |

#### Table 45. ESD absolute maximum ratings

1. Guaranteed by characterization.

2. On  $V_{BAT}$  pin,  $V_{ESD(HBM)}$  is limited to 1000 V.

| Symbol                 | Parameter                                                         | Conditions                                                      | Min Max |                         | Unit                 |  |

|------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------|---------|-------------------------|----------------------|--|

| Symbol                 | Farailleter                                                       | Conditions                                                      | IVIIII  | IVIAX                   | Unit                 |  |

| t <sub>res(TIM)</sub>  | Timer resolution time                                             | AHB/APB2                                                        | 1       | -                       | t <sub>TIMxCLK</sub> |  |

|                        |                                                                   | prescaler distinct<br>from 1, f <sub>TIMxCLK</sub> =<br>168 MHz | 5.95    | -                       | ns                   |  |

|                        |                                                                   | AHB/APB2                                                        | 1       | -                       | t <sub>TIMxCLK</sub> |  |

|                        |                                                                   | prescaler = 1,<br>f <sub>TIMxCLK</sub> = 84 MHz                 | 11.9    | -                       | ns                   |  |

| _                      | Timer external clock<br>frequency on CH1 to<br>CH4                |                                                                 | 0       | f <sub>TIMxCLK</sub> /2 | MHz                  |  |

| f <sub>EXT</sub>       |                                                                   | f <sub>TIMxCLK</sub> =<br>168 MHz<br>APB2 = 84 MHz              | 0       | 84                      | MHz                  |  |

| Res <sub>TIM</sub>     | Timer resolution                                                  |                                                                 | -       | 16                      | bit                  |  |

| t <sub>COUNTER</sub>   | 16-bit counter clock<br>period when internal<br>clock is selected |                                                                 | 1       | 65536                   | t <sub>TIMxCLK</sub> |  |

| t <sub>MAX_COUNT</sub> | Maximum possible count                                            |                                                                 | -       | 32768                   | t <sub>TIMxCLK</sub> |  |

Table 53. Characteristics of TIMx connected to the APB2 domain<sup>(1)</sup>

1. TIMx is used as a general term to refer to the TIM1, TIM8, TIM9, TIM10, and TIM11 timers.

## 5.3.19 Communications interfaces

## I<sup>2</sup>C interface characteristics

The  $I^2C$  interface meets the timings requirements of the  $I^2C$ -bus specification and user manual rev. 03 for:

- Standard-mode (Sm): with a bit rate up to 100 kbit/s

- Fast-mode (Fm): with a bit rate up to 400 kbit/s.

The I<sup>2</sup>C timings requirements are guaranteed by design when the I2C peripheral is properly configured (refer to RM0090 reference manual).

The SDA and SCL I/O requirements are met with the following restrictions: the SDA and SCL I/O pins are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and  $V_{DD}$  is disabled, but is still present. Refer to Section 5.3.16: I/O port characteristics for more details on the I<sup>2</sup>C I/O characteristics.

All I<sup>2</sup>C SDA and SCL I/Os embed an analog filter. Refer to the table below for the analog filter characteristics:

| Symbol          | Parameter                                                              | Min               | Мах                | Unit |

|-----------------|------------------------------------------------------------------------|-------------------|--------------------|------|

| t <sub>AF</sub> | Maximum pulse width of spikes that are suppressed by the analog filter | 50 <sup>(2)</sup> | 260 <sup>(3)</sup> | ns   |

Table 54. I2C analog filter characteristics<sup>(1)</sup>

1. Guaranteed by design.

2. Spikes with widths below  $t_{AF(min)}$  are filtered.

3. Spikes with widths above  $t_{AF(max)}$  are not filtered

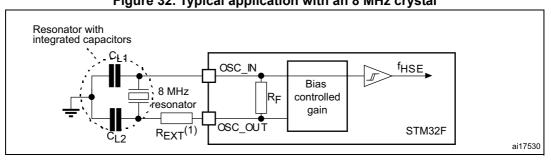

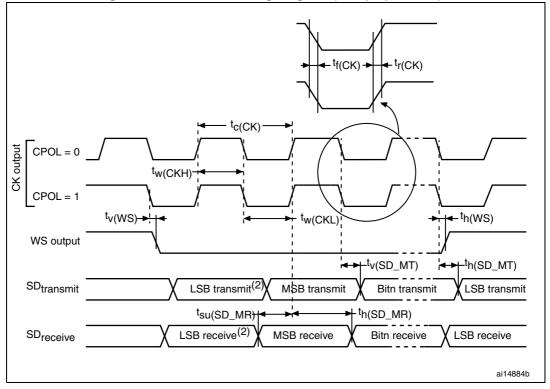

Figure 42. I<sup>2</sup>S slave timing diagram (Philips protocol)

LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

#### Figure 43. I<sup>2</sup>S master timing diagram (Philips protocol)<sup>(1)</sup>

1. Guaranteed by characterization.

2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

| Symbol                           | Parameter                                                                          | Conditions                                                                            | Min   | Тур | Max              | Unit               |

|----------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------|-----|------------------|--------------------|

| t <sub>lat</sub> <sup>(4)</sup>  | Injection trigger conversion                                                       | f <sub>ADC</sub> = 30 MHz                                                             | -     | -   | 0.100            | μs                 |

|                                  | latency                                                                            |                                                                                       | -     | -   | 3 <sup>(7)</sup> | 1/f <sub>ADC</sub> |

| t <sub>latr</sub> (4)            | Regular trigger conversion                                                         | f <sub>ADC</sub> = 30 MHz                                                             | -     | -   | 0.067            | μs                 |

| Hatr                             | latency                                                                            |                                                                                       | -     | -   | 2 <sup>(7)</sup> | 1/f <sub>ADC</sub> |

| ts <sup>(4)</sup>                | Sampling time                                                                      | f <sub>ADC</sub> = 30 MHz                                                             | 0.100 | -   | 16               | μs                 |

| C                                |                                                                                    | -                                                                                     | 3     | -   | 480              | 1/f <sub>ADC</sub> |

| t <sub>STAB</sub> <sup>(4)</sup> | Power-up time                                                                      | -                                                                                     | -     | 2   | 3                | μs                 |

| t <sub>CONV</sub> <sup>(4)</sup> |                                                                                    | f <sub>ADC</sub> = 30 MHz<br>12-bit resolution                                        | 0.50  | -   | 16.40            | μs                 |

|                                  |                                                                                    | f <sub>ADC</sub> = 30 MHz<br>10-bit resolution                                        | 0.43  | -   | 16.34            | μs                 |

|                                  | Total conversion time (including sampling time)                                    | f <sub>ADC</sub> = 30 MHz<br>8-bit resolution                                         | 0.37  | -   | 16.27            | μs                 |

|                                  |                                                                                    | f <sub>ADC</sub> = 30 MHz<br>6-bit resolution                                         | 0.30  | -   | 16.20            | μs                 |

|                                  |                                                                                    | 9 to 492 (t <sub>S</sub> for sampling +n-bit resolution for successive approximation) |       |     |                  |                    |

| f <sub>S</sub> <sup>(4)</sup> (f |                                                                                    | 12-bit resolution<br>Single ADC                                                       | -     | -   | 2                | Msps               |

|                                  | Sampling rate<br>(f <sub>ADC</sub> = 30 MHz, and<br>t <sub>S</sub> = 3 ADC cycles) | 12-bit resolution<br>Interleave Dual ADC<br>mode                                      | -     | -   | 3.75             | Msps               |

|                                  |                                                                                    | 12-bit resolution<br>Interleave Triple ADC<br>mode                                    | -     | -   | 6                | Msps               |

| I <sub>VREF+</sub> (4)           | ADC V <sub>REF</sub> DC current<br>consumption in conversion<br>mode               | -                                                                                     | -     | 300 | 500              | μA                 |

| I <sub>VDDA</sub> <sup>(4)</sup> | ADC V <sub>DDA</sub> DC current<br>consumption in conversion<br>mode               | -                                                                                     | -     | 1.6 | 1.8              | mA                 |

Table 67. ADC characteristics (continued)

1. V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V is obtained when the device operates in reduced temperature range, and with the use of an external power supply supervisor (refer to *Section : Internal reset OFF*).

2. It is recommended to maintain the voltage difference between V\_{REF+} and V\_{DDA} below 1.8 V.

3.  $V_{DDA} - V_{REF+} < 1.2 V.$

4. Guaranteed by characterization.

5.  $V_{REF+}$  is internally connected to  $V_{DDA}$  and  $V_{REF-}$  is internally connected to  $V_{SSA}$ .

6.  $R_{ADC}$  maximum value is given for V<sub>DD</sub>=1.8 V, and minimum value for V<sub>DD</sub>=3.3 V.

7. For external triggers, a delay of 1/f<sub>PCLK2</sub> must be added to the latency specified in *Table* 67.

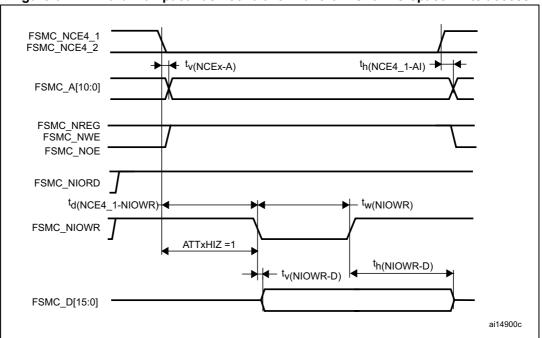

Figure 67. PC Card/CompactFlash controller waveforms for I/O space write access

Table 83. Switching characteristics for PC Card/CF read and write cycles in attribute/common space  $^{(1)(2)}$

| Symbol                    | Parameter                                    | Min                     | Мах                     | Unit |

|---------------------------|----------------------------------------------|-------------------------|-------------------------|------|

| t <sub>v(NCEx-A)</sub>    | FSMC_Ncex low to FSMC_Ay valid               | - 0                     |                         | ns   |

| t <sub>h(NCEx_AI)</sub>   | FSMC_NCEx high to FSMC_Ax invalid            | 4                       | -                       | ns   |

| t <sub>d(NREG-NCEx)</sub> | FSMC_NCEx low to FSMC_NREG valid             | -                       | 3.5                     | ns   |

| t <sub>h(NCEx-NREG)</sub> | FSMC_NCEx high to FSMC_NREG invalid          | T <sub>HCLK</sub> +4    | -                       | ns   |

| t <sub>d(NCEx-NWE)</sub>  | FSMC_NCEx low to FSMC_NWE low                | -                       | 5T <sub>HCLK</sub> +0.5 | ns   |

| t <sub>d(NCEx-NOE)</sub>  | FSMC_NCEx low to FSMC_NOE low                | -                       | 5T <sub>HCLK</sub> +0.5 | ns   |

| t <sub>w(NOE)</sub>       | FSMC_NOE low width                           | 8T <sub>HCLK</sub> –1   | 8T <sub>HCLK</sub> +1   | ns   |

| t <sub>d(NOE_NCEx)</sub>  | FSMC_NOE high to FSMC_NCEx high              | 5T <sub>HCLK</sub> +2.5 | -                       | ns   |

| t <sub>su (D-NOE)</sub>   | FSMC_D[15:0] valid data before FSMC_NOE high | 4.5                     | -                       | ns   |

| t <sub>h(N0E-D)</sub>     | FSMC_N0E high to FSMC_D[15:0] invalid        | 3                       | -                       | ns   |

| t <sub>w(NWE)</sub>       | FSMC_NWE low width                           | 8T <sub>HCLK</sub> –0.5 | 8T <sub>HCLK</sub> + 3  | ns   |

| t <sub>d(NWE_NCEx)</sub>  | FSMC_NWE high to FSMC_NCEx high              | 5T <sub>HCLK</sub> –1   | -                       | ns   |

| t <sub>d(NCEx-NWE)</sub>  | FSMC_NCEx low to FSMC_NWE low                | -                       | 5T <sub>HCLK</sub> + 1  | ns   |

| t <sub>v(NWE-D)</sub>     | FSMC_NWE low to FSMC_D[15:0] valid           | -                       | 0                       | ns   |

| t <sub>h</sub> (NWE-D)    | FSMC_NWE high to FSMC_D[15:0] invalid        | 8T <sub>HCLK</sub> –1   | -                       | ns   |

| t <sub>d</sub> (D-NWE)    | FSMC_D[15:0] valid before FSMC_NWE high      | 13T <sub>HCLK</sub> –1  | -                       | ns   |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization.

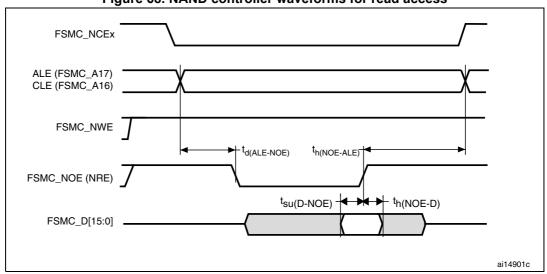

Figure 68. NAND controller waveforms for read access

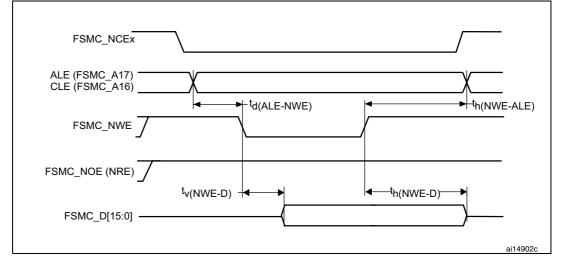

Figure 69. NAND controller waveforms for write access

|                   | package mechanical data |        |       |                       |        |        |  |

|-------------------|-------------------------|--------|-------|-----------------------|--------|--------|--|

| Symbol            | millimeters             |        |       | inches <sup>(1)</sup> |        |        |  |

| Symbol            | Min                     | Тур    | Мах   | Min                   | Тур    | Max    |  |

| А                 | 0.540                   | 0.570  | 0.600 | 0.0213                | 0.0224 | 0.0236 |  |

| A1                | -                       | 0.190  | -     | -                     | 0.0075 | -      |  |

| A2                | -                       | 0.380  | -     | -                     | 0.0150 | -      |  |

| A3 <sup>(2)</sup> | -                       | 0.025  | -     | -                     | 0.0010 | -      |  |

| b <sup>(3)</sup>  | 0.240                   | 0.270  | 0.300 | 0.0094                | 0.0106 | 0.0118 |  |

| D                 | 4.188                   | 4.223  | 4.258 | 0.1649                | 0.1663 | 0.1676 |  |

| E                 | 3.934                   | 3.969  | 4.004 | 0.1549                | 0.1563 | 0.1576 |  |

| е                 | -                       | 0.400  | -     | -                     | 0.0157 | -      |  |

| e1                | -                       | 3.600  | -     | -                     | 0.1417 | -      |  |

| e2                | -                       | 3.200  | -     | -                     | 0.1260 | -      |  |

| F                 | -                       | 0.3115 | -     | -                     | 0.0123 | -      |  |

| G                 | -                       | 0.3845 | -     | -                     | 0.0151 | -      |  |

| aaa               | -                       | 0.100  | -     | -                     | 0.0039 | -      |  |

| bbb               | -                       | 0.100  | -     | -                     | 0.0039 | -      |  |

| ссс               | -                       | 0.100  | -     | -                     | 0.0039 | -      |  |

| ddd               | -                       | 0.050  | -     | -                     | 0.0020 | -      |  |

| eee               | -                       | 0.050  | -     | -                     | 0.0020 | -      |  |

# Table 90. WLCSP90 - 4.223 x 3.969 mm, 0.400 mm pitch wafer level chip scale package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. Back side coating.

3. Dimension is measured at the maximum bump diameter parallel to primary datum Z.

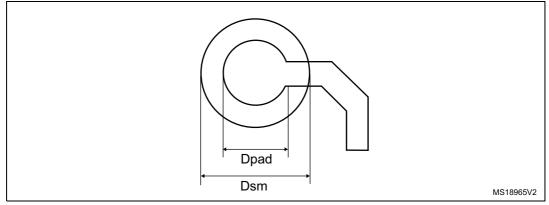

# Figure 76. WLCSP90 - 4.223 x 3.969 mm, 0.400 mm pitch wafer level chip scale recommended footprint

| Dimension      | Recommended values                            |  |  |  |

|----------------|-----------------------------------------------|--|--|--|

| Pitch          | 0.4 mm                                        |  |  |  |

| Dpad           | 260 μm max. (circular)<br>220 μm recommended  |  |  |  |

| Dsm            | 300 μm min. (for 260 μm diameter pad)         |  |  |  |

| PCB pad design | Non-solder mask defined via underbump allowed |  |  |  |

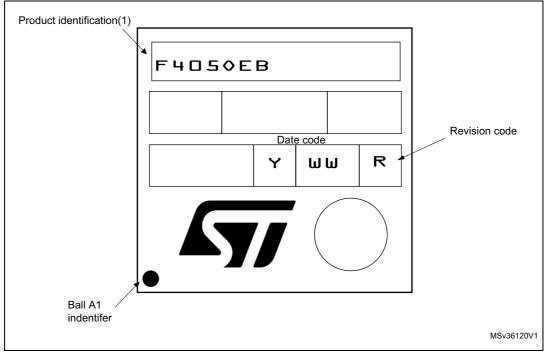

#### **Device marking for WLCSP90**

The following figure gives an example of topside marking and ball A1 position identifier location.

Other optional marking or inset/upset marks, which depend on supply chain operations, are not indicated below.

Figure 77. WLCSP90 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

1. Dimensions are in millimeters.

# Appendix A Application block diagrams

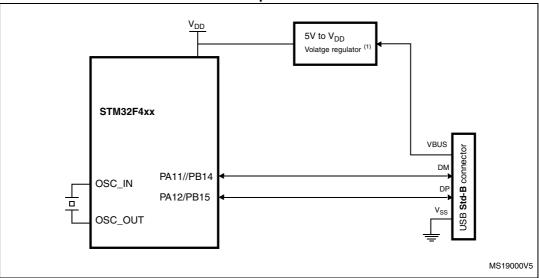

## A.1 USB OTG full speed (FS) interface solutions

Figure 93. USB controller configured as peripheral-only and used in Full speed mode

1. External voltage regulator only needed when building a  $V_{\text{BUS}}$  powered device.

2. The same application can be developed using the OTG HS in FS mode to achieve enhanced performance thanks to the large Rx/Tx FIFO and to a dedicated DMA controller.

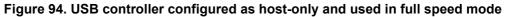

The current limiter is required only if the application has to support a V<sub>BUS</sub> powered device. A basic power switch can be used if 5 V are available on the application board.

2. The same application can be developed using the OTG HS in FS mode to achieve enhanced performance thanks to the large Rx/Tx FIFO and to a dedicated DMA controller.

Table 100. Document revision history (continued)

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

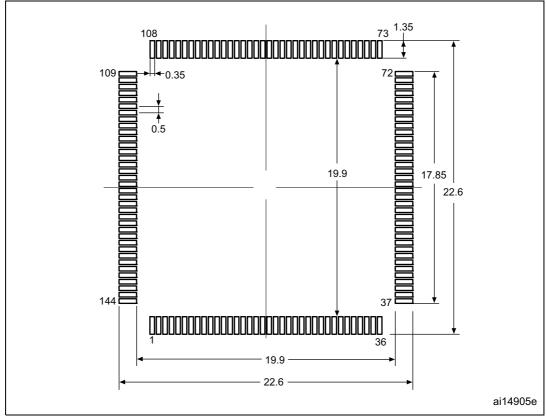

| 22-Oct-2015 | 6        | In the whole document, updated notes related to values guaranteed by design or by characterization.<br>Updated <i>Table 34: HSI oscillator characteristics</i> .<br>Changed f <sub>VCO_OUT</sub> minimum value and VCO freq to 100 MHz in<br><i>Table 36: Main PLL characteristics</i> and <i>Table 37: PLLI2S (audio PLL)</i><br><i>characteristics</i> .<br>Updated <i>Figure 39: SPI timing diagram - slave mode and CPHA = 0</i> .<br>Updated <i>Figure 53: 12-bit buffered /non-buffered DAC</i> .<br>Removed note 1 related to better performance using a restricted V <sub>DD</sub><br>range in <i>Table 68: ADC accuracy at fADC = 30 MHz</i> .<br>Upated <i>Figure 84: LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat</i><br><i>package outline</i> .<br>Updated <i>Figure 87: UFBGA176+25 ball, 10 x 10 mm, 0.65 mm pitch,</i><br><i>ultra fine pitch ball grid array package outline</i> and <i>Table 95:</i><br><i>UFBGA176+25 ball, 10 x 10 x 0.65 mm pitch, ultra thin fine pitch ball</i><br><i>grid array mechanical data</i> . |

| 16-Mar-2016 | 7        | Updated Figure 2: Compatible board design<br>STM32F10xx/STM32F2/STM32F40xxx for LQFP100 package.<br>Updated  Vssx–Vss  in Table 11: Voltage characteristics to add V <sub>REF</sub> .<br>Added V <sub>REF</sub> _in Table 67: ADC characteristics.<br>Updated Table 90: WLCSP90 - 4.223 x 3.969 mm, 0.400 mm pitch<br>wafer level chip scale package mechanical data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 09-Sep-2016 | 8        | Remove note 1 below <i>Figure 5: STM32F40xxx block diagram</i> .<br>Updated definition of stresses above maximum ratings in <i>Section 5.2:</i><br><i>Absolute maximum ratings</i> .<br>Updated $t_{h(NSS)}$ in <i>Figure 39: SPI timing diagram - slave mode and</i><br><i>CPHA = 0Figure</i> and <i>Figure 40: SPI timing diagram - slave mode and</i><br><i>CPHA = 1</i> .<br>Added note related to optional marking and inset/upset marks in all<br>package marking sections.<br>Updated <i>Figure 87: UFBGA176+25 ball, 10 x 10 mm, 0.65 mm pitch,</i><br><i>ultra fine pitch ball grid array package outline</i> and <i>Table 95:</i><br><i>UFBGA176+25 ball, 10 x 10 x 0.65 mm pitch, ultra thin fine pitch ball</i><br><i>grid array mechanical data.</i>                                                                                                                                                                                                                                                                                    |

Table 100. Document revision history (continued)