# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                    |

|----------------------------|-------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                        |

| Speed                      | 168MHz                                                                                    |

| Connectivity               | CANbus, DCMI, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                         |

| Number of I/O              | 82                                                                                        |

| Program Memory Size        | 512KB (512K x 8)                                                                          |

| Program Memory Type        | FLASH                                                                                     |

| EEPROM Size                | -                                                                                         |

| RAM Size                   | 192K x 8                                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                               |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                                     |

| Oscillator Type            | Internal                                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                         |

| Mounting Type              | Surface Mount                                                                             |

| Package / Case             | 100-LQFP                                                                                  |

| Supplier Device Package    | 100-LQFP (14x14)                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f407vet6                     |

|                            |                                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 93.  | LQPF100 – 100-pin, 14 x 14 mm low-profile quad flat package      |     |

|------------|------------------------------------------------------------------|-----|

|            | mechanical data                                                  | 170 |

| Table 94.  | LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat package      |     |

|            | mechanical data                                                  | 174 |

| Table 95.  | UFBGA176+25 ball, 10 × 10 × 0.65 mm pitch, ultra thin fine pitch |     |

|            | ball grid array mechanical data                                  | 177 |

| Table 96.  | UFBGA176+2 recommended PCB design rules (0.65 mm pitch BGA)      | 178 |

| Table 97.  | LQFP176 - 176-pin, 24 x 24 mm low profile quad flat package      |     |

|            | mechanical data                                                  | 180 |

| Table 98.  | Package thermal characteristics                                  | 184 |

| Table 99.  | Ordering information scheme                                      | 185 |

| Table 100. | Document revision history                                        | 191 |

## 2 Description

The STM32F405xx and STM32F407xx family is based on the high-performance ARM<sup>®</sup> Cortex<sup>®</sup>-M4 32-bit RISC core operating at a frequency of up to 168 MHz. The Cortex-M4 core features a Floating point unit (FPU) single precision which supports all ARM single-precision data-processing instructions and data types. It also implements a full set of DSP instructions and a memory protection unit (MPU) which enhances application security.

The STM32F405xx and STM32F407xx family incorporates high-speed embedded memories (Flash memory up to 1 Mbyte, up to 192 Kbytes of SRAM), up to 4 Kbytes of backup SRAM, and an extensive range of enhanced I/Os and peripherals connected to two APB buses, three AHB buses and a 32-bit multi-AHB bus matrix.

All devices offer three 12-bit ADCs, two DACs, a low-power RTC, twelve general-purpose 16-bit timers including two PWM timers for motor control, two general-purpose 32-bit timers. a true random number generator (RNG). They also feature standard and advanced communication interfaces.

- Up to three I<sup>2</sup>Cs

- Three SPIs, two I<sup>2</sup>Ss full duplex. To achieve audio class accuracy, the I2S peripherals can be clocked via a dedicated internal audio PLL or via an external clock to allow synchronization.

- Four USARTs plus two UARTs

- An USB OTG full-speed and a USB OTG high-speed with full-speed capability (with the ULPI),

- Two CANs

- An SDIO/MMC interface

- Ethernet and the camera interface available on STM32F407xx devices only.

New advanced peripherals include an SDIO, an enhanced flexible static memory control (FSMC) interface (for devices offered in packages of 100 pins and more), a camera interface for CMOS sensors. Refer to *Table 2: STM32F405xx and STM32F407xx: features and peripheral counts* for the list of peripherals available on each part number.

The STM32F405xx and STM32F407xx family operates in the –40 to +105 °C temperature range from a 1.8 to 3.6 V power supply. The supply voltage can drop to 1.7 V when the device operates in the 0 to 70 °C temperature range using an external power supply supervisor: refer to *Section : Internal reset OFF*. A comprehensive set of power-saving mode allows the design of low-power applications.

The STM32F405xx and STM32F407xx family offers devices in various packages ranging from 64 pins to 176 pins. The set of included peripherals changes with the device chosen.

These features make the STM32F405xx and STM32F407xx microcontroller family suitable for a wide range of applications:

- Motor drive and application control

- Medical equipment

- Industrial applications: PLC, inverters, circuit breakers

- Printers, and scanners

- Alarm systems, video intercom, and HVAC

- Home audio appliances

5

*Figure 5* shows the general block diagram of the device family.

|                           | Table 2. STM32F405xx and STM32F407xx: features and peripheral counts |             |                       |             |             |             |       |        |       |        |       |        |

|---------------------------|----------------------------------------------------------------------|-------------|-----------------------|-------------|-------------|-------------|-------|--------|-------|--------|-------|--------|

| Peripherals               |                                                                      | STM32F405RG | STM32F405OG           | STM32F405VG | STM32F405ZG | STM32F405OE | STM32 | F407Vx | STM32 | F407Zx | STM32 | F407lx |

| Flash memory in<br>Kbytes |                                                                      |             | 10                    | 24          |             | 512         | 512   | 1024   | 512   | 1024   | 512   | 1024   |

| SRAM in                   | System                                                               |             |                       |             | 192(112+    | 16+64)      |       |        |       |        |       |        |

| Kbytes                    | Backup                                                               |             |                       |             | 4           |             |       |        |       |        |       |        |

| FSMC me<br>controller     | mory                                                                 | No          | No Yes <sup>(1)</sup> |             |             |             |       |        |       |        |       |        |

| Ethernet                  |                                                                      |             | <u>.</u>              | No          |             |             |       |        | Ye    | s      |       |        |

|                           | General-<br>purpose                                                  |             |                       |             | 10          |             |       |        |       |        |       |        |

|                           | Advanced<br>-control                                                 | 2           |                       |             |             |             |       |        |       |        |       |        |

| Timers                    | Basic                                                                | 2           |                       |             |             |             |       |        |       |        |       |        |

|                           | IWDG                                                                 | Yes         |                       |             |             |             |       |        |       |        |       |        |

|                           | WWDG                                                                 | Yes         |                       |             |             |             |       |        |       |        |       |        |

|                           | RTC                                                                  | Yes         |                       |             |             |             |       |        |       |        |       |        |

| Random n<br>generator     | umber                                                                |             | Yes                   |             |             |             |       |        |       |        |       |        |

DocID022152 Rev 8

14/202

Description

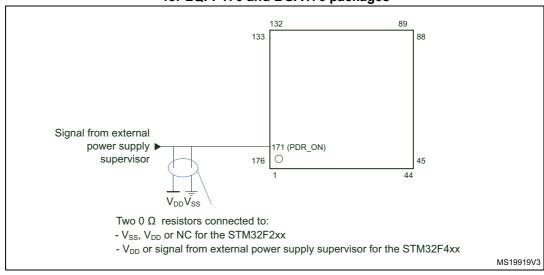

Figure 4. Compatible board design between STM32F2 and STM32F40xxx for LQFP176 and BGA176 packages

clock entry is available when necessary (for example if an indirectly used external oscillator fails).

Several prescalers allow the configuration of the three AHB buses, the high-speed APB (APB2) and the low-speed APB (APB1) domains. The maximum frequency of the three AHB buses is 168 MHz while the maximum frequency of the high-speed APB domains is 84 MHz. The maximum allowed frequency of the low-speed APB domain is 42 MHz.

The devices embed a dedicated PLL (PLLI2S) which allows to achieve audio class performance. In this case, the  $I^2S$  master clock can generate all standard sampling frequencies from 8 kHz to 192 kHz.

#### 2.2.13 Boot modes

At startup, boot pins are used to select one out of three boot options:

- Boot from user Flash

- Boot from system memory

- Boot from embedded SRAM

The boot loader is located in system memory. It is used to reprogram the Flash memory by using USART1 (PA9/PA10), USART3 (PC10/PC11 or PB10/PB11), CAN2 (PB5/PB13), USB OTG FS in Device mode (PA11/PA12) through DFU (device firmware upgrade).

#### 2.2.14 **Power supply schemes**

- V<sub>DD</sub> = 1.8 to 3.6 V: external power supply for I/Os and the internal regulator (when enabled), provided externally through V<sub>DD</sub> pins.

- V<sub>SSA</sub>, V<sub>DDA</sub> = 1.8 to 3.6 V: external analog power supplies for ADC, DAC, Reset blocks, RCs and PLL. V<sub>DDA</sub> and V<sub>SSA</sub> must be connected to V<sub>DD</sub> and V<sub>SS</sub>, respectively.

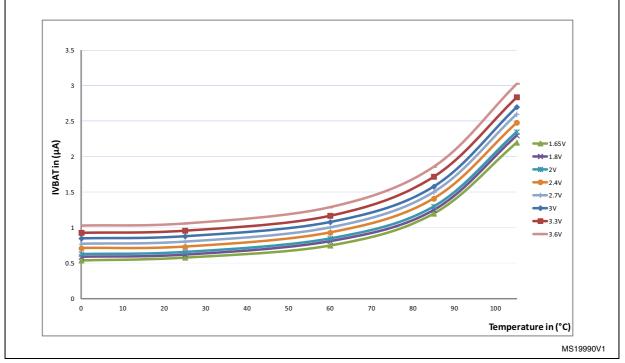

- V<sub>BAT</sub> = 1.65 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

Refer to Figure 21: Power supply scheme for more details.

Note:  $V_{DD}/V_{DDA}$  minimum value of 1.7 V is obtained when the device operates in reduced temperature range, and with the use of an external power supply supervisor (refer to Section : Internal reset OFF).

Refer to Table 2 in order to identify the packages supporting this option.

#### 2.2.15 **Power supply supervisor**

#### Internal reset ON

On packages embedding the PDR\_ON pin, the power supply supervisor is enabled by holding PDR\_ON high. On all other packages, the power supply supervisor is always enabled.

The device has an integrated power-on reset (POR) / power-down reset (PDR) circuitry coupled with a Brownout reset (BOR) circuitry. At power-on, POR/PDR is always active and ensures proper operation starting from 1.8 V. After the 1.8 V POR threshold level is reached, the option byte loading process starts, either to confirm or modify default BOR threshold levels, or to disable BOR permanently. Three BOR thresholds are available through option bytes. The device remains in reset mode when V<sub>DD</sub> is below a specified threshold, V<sub>POR/PDR</sub> or V<sub>BOR</sub>, without the need for an external reset circuit.

The device also features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

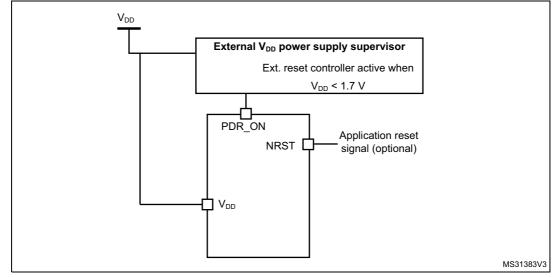

#### Internal reset OFF

This feature is available only on packages featuring the PDR\_ON pin. The internal power-on reset (POR) / power-down reset (PDR) circuitry is disabled with the PDR\_ON pin.

An external power supply supervisor should monitor  $V_{DD}$  and should maintain the device in reset mode as long as  $V_{DD}$  is below a specified threshold. PDR\_ON should be connected to this external power supply supervisor. Refer to *Figure 7: Power supply supervisor interconnection with internal reset OFF*.

Figure 7. Power supply supervisor interconnection with internal reset OFF

1. PDR = 1.7 V for reduce temperature range; PDR = 1.8 V for all temperature range.

The V<sub>DD</sub> specified threshold, below which the device must be maintained under reset, is 1.8 V (see *Figure 7*). This supply voltage can drop to 1.7 V when the device operates in the 0 to 70 °C temperature range.

A comprehensive set of power-saving mode allows to design low-power applications.

When the internal reset is OFF, the following integrated features are no more supported:

- The integrated power-on reset (POR) / power-down reset (PDR) circuitry is disabled

- The brownout reset (BOR) circuitry is disabled

- The embedded programmable voltage detector (PVD) is disabled

- V<sub>BAT</sub> functionality is no more available and V<sub>BAT</sub> pin should be connected to V<sub>DD</sub>

All packages, except for the LQFP64 and LQFP100, allow to disable the internal reset through the PDR\_ON signal.

|                     | FSMC  |                    |               |             |                        |                |  |

|---------------------|-------|--------------------|---------------|-------------|------------------------|----------------|--|

| Pins <sup>(1)</sup> | CF    | NOR/PSRAM/<br>SRAM | NOR/PSRAM Mux | NAND 16 bit | LQFP100 <sup>(2)</sup> | WLCSP90<br>(2) |  |

| PF1                 | A1    | A1                 | -             | -           | -                      | -              |  |

| PF2                 | A2    | A2                 | -             | -           | -                      | -              |  |

| PF3                 | A3    | A3                 | -             | -           | -                      | -              |  |

| PF4                 | A4    | A4                 | -             | -           | -                      | -              |  |

| PF5                 | A5    | A5                 | -             | -           | -                      | -              |  |

| PF6                 | NIORD | -                  | -             | -           | -                      | -              |  |

| PF7                 | NREG  | -                  | -             | -           | -                      | -              |  |

| PF8                 | NIOWR | -                  | -             | -           | -                      | -              |  |

| PF9                 | CD    | -                  | -             | -           | -                      | -              |  |

| PF10                | INTR  | -                  | -             | -           | -                      | -              |  |

| PF12                | A6    | A6                 | -             | -           | -                      | -              |  |

| PF13                | A7    | A7                 | -             | -           | -                      | -              |  |

| PF14                | A8    | A8                 | -             | -           | -                      | -              |  |

| PF15                | A9    | A9                 | -             | -           | -                      | -              |  |

| PG0                 | A10   | A10                | -             | -           | -                      | -              |  |

| PG1                 |       | A11                | -             | -           | -                      | -              |  |

| PE7                 | D4    | D4                 | DA4           | D4          | Yes                    | Yes            |  |

| PE8                 | D5    | D5                 | DA5           | D5          | Yes                    | Yes            |  |

| PE9                 | D6    | D6                 | DA6           | D6          | Yes                    | Yes            |  |

| PE10                | D7    | D7                 | DA7           | D7          | Yes                    | Yes            |  |

| PE11                | D8    | D8                 | DA8           | D8          | Yes                    | Yes            |  |

| PE12                | D9    | D9                 | DA9           | D9          | Yes                    | Yes            |  |

| PE13                | D10   | D10                | DA10          | D10         | Yes                    | Yes            |  |

| PE14                | D11   | D11                | DA11          | D11         | Yes                    | Yes            |  |

| PE15                | D12   | D12                | DA12          | D12         | Yes                    | Yes            |  |

| PD8                 | D13   | D13                | DA13          | D13         | Yes                    | Yes            |  |

| PD9                 | D14   | D14                | DA14          | D14         | Yes                    | Yes            |  |

| PD10                | D15   | D15                | DA15          | D15         | Yes                    | Yes            |  |

| PD11                | -     | A16                | A16           | CLE         | Yes                    | Yes            |  |

| PD12                | -     | A17                | A17           | ALE         | Yes                    | Yes            |  |

| PD13                | -     | A18                | A18           | -           | Yes                    | -              |  |

| PD14                | D0    | D0                 | DA0           | D0          | Yes                    | Yes            |  |

| PD15                | D1    | D1                 | DA1           | D1          | Yes                    | Yes            |  |

| Table 8. FSM | C pin definition | n (continued) |

|--------------|------------------|---------------|

|--------------|------------------|---------------|

| Symbol                                              |                                                  |                          |                                | Тур                                         |                                | Ма                        | x <sup>(1)</sup>           |      |

|-----------------------------------------------------|--------------------------------------------------|--------------------------|--------------------------------|---------------------------------------------|--------------------------------|---------------------------|----------------------------|------|

|                                                     | Parameter                                        | Conditions               | г                              | T <sub>A</sub> = 25 °C T <sub>A</sub><br>85 |                                | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |

|                                                     |                                                  |                          | V <sub>BAT</sub><br>=<br>1.8 V | V <sub>BAT</sub> =<br>2.4 V                 | V <sub>BAT</sub><br>=<br>3.3 V | V <sub>BAT</sub> =        |                            |      |

| I <sub>DD_VBA</sub><br>T<br>UDD_VBA<br>T<br>Current | Backup SRAM ON, low-speed oscillator and RTC ON  | 1.29                     | 1.42                           | 1.68                                        | 6                              | 11                        |                            |      |

|                                                     | Backup SRAM OFF, low-speed oscillator and RTC ON | 0.62                     | 0.73                           | 0.96                                        | 3                              | 5                         | μA                         |      |

|                                                     | current                                          | Backup SRAM ON, RTC OFF  | 0.79                           | 0.81                                        | 0.86                           | 5                         | 10                         |      |

|                                                     |                                                  | Backup SRAM OFF, RTC OFF | 0.10                           | 0.10                                        | 0.10                           | 2                         | 4                          |      |

| Table 25. Typical and maximum current consumptions in V <sub>BAT</sub> mode |

|-----------------------------------------------------------------------------|

|-----------------------------------------------------------------------------|

1. Guaranteed by characterization.

| Symbol | Parameter                | Conditions <sup>(1)</sup>                                          | l/O toggling<br>frequency (f <sub>SW</sub> ) | Тур  | Unit |

|--------|--------------------------|--------------------------------------------------------------------|----------------------------------------------|------|------|

|        |                          |                                                                    | 2 MHz                                        | 0.02 |      |

|        |                          | $V_{DD} = 3.3 V^{(2)}$                                             | 8 MHz                                        | 0.14 | -    |

|        |                          | $C = C_{INT}$                                                      | 25 MHz                                       | 0.51 |      |

|        |                          |                                                                    | 50 MHz                                       | 0.86 |      |

|        |                          |                                                                    | 60 MHz                                       | 1.30 |      |

|        |                          |                                                                    | 2 MHz                                        | 0.10 |      |

|        |                          | V <sub>DD</sub> = 3.3 V                                            | 8 MHz                                        | 0.38 |      |

|        |                          | C <sub>EXT</sub> = 0 pF                                            | 25 MHz                                       | 1.18 |      |

|        |                          | $C = C_{INT} + C_{EXT} + C_S$                                      | 50 MHz                                       | 2.47 |      |

|        |                          |                                                                    | 60 MHz                                       | 2.86 | mA   |

|        |                          | $V_{DD} = 3.3 V$ $C_{EXT} = 10 pF$ $C = C_{INT} + C_{EXT} + C_{S}$ | 2 MHz                                        | 0.17 |      |

|        | I/O switching<br>current |                                                                    | 8 MHz                                        | 0.66 |      |

| IDDIO  |                          |                                                                    | 25 MHz                                       | 1.70 |      |

|        |                          |                                                                    | 50 MHz                                       | 2.65 |      |

|        |                          |                                                                    | 60 MHz                                       | 3.48 |      |

|        |                          | V <sub>DD</sub> = 3.3 V                                            | 2 MHz                                        | 0.23 |      |

|        |                          |                                                                    | 8 MHz                                        | 0.95 |      |

|        |                          | C <sub>EXT</sub> = 22 pF                                           |                                              | 3.20 |      |

|        |                          | $C = C_{INT} + C_{EXT} + C_S$                                      | 50 MHz                                       | 4.69 | 1    |

|        |                          |                                                                    | 60 MHz                                       | 8.06 |      |

|        |                          | 2 MHz 0                                                            | 0.30                                         |      |      |

|        |                          | V <sub>DD</sub> = 3.3 V                                            | 8 MHz                                        | 1.22 |      |

|        |                          | C <sub>EXT</sub> = 33 pF                                           | 25 MHz                                       | 3.90 | -    |

|        |                          | $C = C_{INT} + C_{EXT} + C_S$                                      | 50 MHz                                       | 8.82 |      |

|        |                          |                                                                    | 60 MHz                                       | _(3) | 1    |

1.  $C_S$  is the PCB board capacitance including the pad pin.  $C_S$  = 7 pF (estimated value).

2. This test is performed by cutting the LQFP package pin (pad removal).

3. At 60 MHz, C maximum load is specified 30 pF.

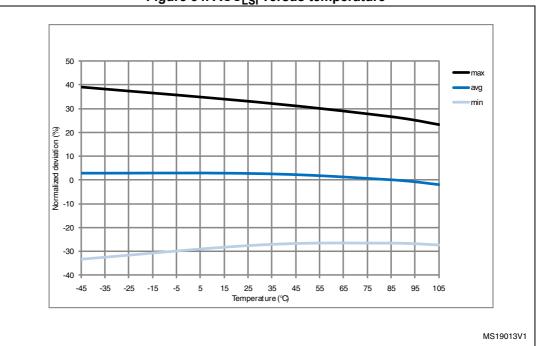

Figure 34. ACC<sub>LSI</sub> versus temperature

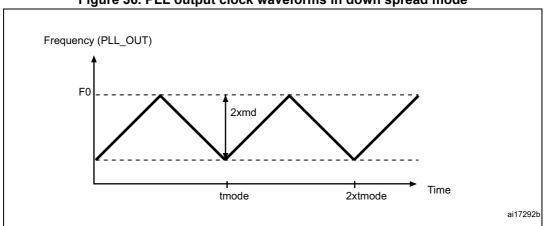

### 5.3.10 PLL characteristics

The parameters given in *Table 36* and *Table 37* are derived from tests performed under temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

| Symbol                 | Parameter                             | Conditions         | Min                 | Тур | Max  | Unit |

|------------------------|---------------------------------------|--------------------|---------------------|-----|------|------|

| f <sub>PLL_IN</sub>    | PLL input clock <sup>(1)</sup>        | -                  | 0.95 <sup>(2)</sup> | 1   | 2.10 | MHz  |

| f <sub>PLL_OUT</sub>   | PLL multiplier output clock           | -                  | 24                  | -   | 168  | MHz  |

| f <sub>PLL48_OUT</sub> | 48 MHz PLL multiplier output<br>clock | -                  | -                   | 48  | 75   | MHz  |

| f <sub>VCO_OUT</sub>   | PLL VCO output                        | -                  | 100                 | -   | 432  | MHz  |

| +                      | PLL lock time                         | VCO freq = 100 MHz | 75                  | -   | 200  |      |

| t <sub>LOCK</sub>      |                                       | VCO freq = 432 MHz | 100                 | -   | 300  | μs   |

Table 36. Main PLL characteristics

Figure 36. PLL output clock waveforms in down spread mode

#### 5.3.12 Memory characteristics

#### Flash memory

The characteristics are given at  $T_A = -40$  to 105 °C unless otherwise specified. The devices are shipped to customers with the Flash memory erased.

| Symbol          | Parameter                                  | Conditions                                  | Min | Тур | Мах | Unit |

|-----------------|--------------------------------------------|---------------------------------------------|-----|-----|-----|------|

|                 | Write / Erase 8-bit mode, $V_{DD}$ = 1.8 V | -                                           | 5   | -   |     |      |

| I <sub>DD</sub> | DD Supply current                          | Write / Erase 16-bit mode, $V_{DD}$ = 2.1 V | -   | 8   | -   | mA   |

|                 |                                            | Write / Erase 32-bit mode, $V_{DD}$ = 3.3 V | -   | 12  | -   |      |

Table 39. Flash memory characteristics

| Symbol                 | Parameter                 | Conditions                                       | Min <sup>(1)</sup> | Тур  | Max <sup>(1)</sup> | Unit |

|------------------------|---------------------------|--------------------------------------------------|--------------------|------|--------------------|------|

| t <sub>prog</sub>      | Word programming time     | Program/erase parallelism<br>(PSIZE) = x 8/16/32 | -                  | 16   | 100 <sup>(2)</sup> | μs   |

|                        |                           | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 400  | 800                |      |

| t <sub>erase16kb</sub> | Sector (16 KB) erase time | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 300  | 600                | ms   |

|                        |                           | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 250  | 500                |      |

| terase64kb             |                           | Program/erase parallelism<br>(PSIZE) = x 8       | -                  | 1200 | 2400               |      |

|                        | Sector (64 KB) erase time | Program/erase parallelism<br>(PSIZE) = x 16      | -                  | 700  | 1400               | ms   |

|                        |                           | Program/erase parallelism<br>(PSIZE) = x 32      | -                  | 550  | 1100               |      |

Table 40. Flash memory programming

| OSPEEDRy<br>[1:0] bit<br>value <sup>(1)</sup> | Symbol                                           | Parameter                                                                       | Conditions                                          | Min | Тур | Мах                | Unit |  |

|-----------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------|-----------------------------------------------------|-----|-----|--------------------|------|--|

|                                               | F <sub>max(IO)out</sub>                          | t Maximum frequency <sup>(3)</sup>                                              | C <sub>L</sub> = 30 pF, V <sub>DD &gt;</sub> 2.70 V | -   | -   | 100 <sup>(4)</sup> |      |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 30 pF, V <sub>DD &gt;</sub> 1.8 V  | -   | -   | 50 <sup>(4)</sup>  | MHz  |  |

| 44                                            |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 2.70 V | -   | -   | 180 <sup>(4)</sup> |      |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 1.8 V  | -   | -   | 100 <sup>(4)</sup> |      |  |

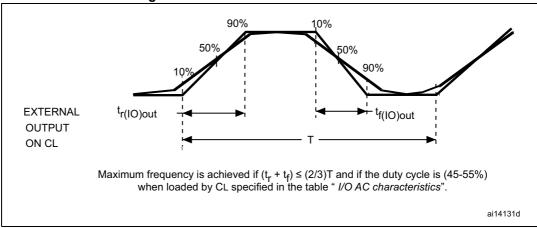

| 11                                            | t <sub>f(IO)out</sub> /<br>t <sub>r(IO)out</sub> | Output high to low level fall<br>time and output low to high<br>level rise time | C <sub>L</sub> = 30 pF, V <sub>DD &gt;</sub> 2.70 V | -   | -   | 4                  |      |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 30 pF, V <sub>DD &gt;</sub> 1.8 V  | -   | -   | 6                  | 20   |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 2.70 V | -   | -   | 2.5                | ns   |  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 1.8 V  | -   | -   | 4                  |      |  |

| -                                             | t <sub>EXTIpw</sub>                              | Pulse width of external signals detected by the EXTI controller                 |                                                     | 10  | -   | -                  | ns   |  |

Table 50. I/O AC characteristics<sup>(1)(2)</sup> (continued)

1. Guaranteed by characterization.

The I/O speed is configured using the OSPEEDRy[1:0] bits. Refer to the STM32F4xx reference manual for a description of the GPIOx\_SPEEDR GPIO port output speed register.

3. The maximum frequency is defined in *Figure* 37.

4. For maximum frequencies above 50 MHz, the compensation cell should be used.

#### Figure 37. I/O AC characteristics definition

#### 5.3.17 NRST pin characteristics

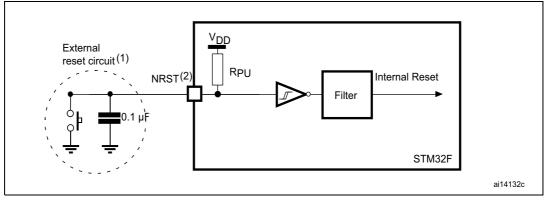

The NRST pin input driver uses CMOS technology. It is connected to a permanent pull-up resistor,  $R_{PU}$  (see *Table 48*).

Unless otherwise specified, the parameters given in *Table 51* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

| Symbol                               | Parameter                                       | Conditions                                                              | Min         | Тур | Max         | Unit |

|--------------------------------------|-------------------------------------------------|-------------------------------------------------------------------------|-------------|-----|-------------|------|

| V <sub>IL(NRST)</sub> <sup>(1)</sup> | NRST Input low level voltage                    | TTL ports                                                               | -           | -   | 0.8         |      |

| V <sub>IH(NRST)</sub> <sup>(1)</sup> | NRST Input high level voltage                   | $\begin{array}{c c} 2.7 \lor \leq V_{DD} \leq \\ 3.6 \lor \end{array} $ | -           | -   | v           |      |

| V <sub>IL(NRST)</sub> <sup>(1)</sup> | NRST Input low level voltage                    | CMOS ports                                                              | I           | -   | $0.3V_{DD}$ | v    |

| V <sub>IH(NRST)</sub> <sup>(1)</sup> | NRST Input high level voltage                   | 1.8 V ≤V <sub>DD</sub> ≤<br>3.6 V                                       | $0.7V_{DD}$ | -   | -           |      |

| V <sub>hys(NRST)</sub>               | NRST Schmitt trigger voltage<br>hysteresis      | -                                                                       | -           | 200 | -           | mV   |

| R <sub>PU</sub>                      | Weak pull-up equivalent resistor <sup>(2)</sup> | $V_{IN} = V_{SS}$                                                       | 30          | 40  | 50          | kΩ   |

| V <sub>F(NRST)</sub> <sup>(1)</sup>  | NRST Input filtered pulse                       |                                                                         | -           | -   | 100         | ns   |

| V <sub>NF(NRST)</sub> <sup>(1)</sup> | NRST Input not filtered pulse                   | V <sub>DD</sub> > 2.7 V                                                 | 300         | -   | -           | ns   |

| T <sub>NRST_OUT</sub>                | Generated reset pulse duration                  | Internal<br>Reset source                                                | 20          | -   | -           | μs   |

Table 51. NRST pin characteristics

1. Guaranteed by design.

2. The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance must be minimum (~10% order).

#### Figure 38. Recommended NRST pin protection

- 1. The reset network protects the device against parasitic resets.

- The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in Table 51. Otherwise the reset is not taken into account by the device.

#### 5.3.18 TIM timer characteristics

The parameters given in Table 52 and Table 53 are guaranteed by design.

Refer to *Section 5.3.16: I/O port characteristics* for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Symbol                 | Parameter                              | Conditions                                                     | Min    | Мах                     | Unit                 |

|------------------------|----------------------------------------|----------------------------------------------------------------|--------|-------------------------|----------------------|

| t <sub>res(TIM)</sub>  |                                        | AHB/APB1                                                       | 1      | -                       | t <sub>TIMxCLK</sub> |

|                        | Timer resolution time                  | prescaler distinct<br>from 1, f <sub>TIMxCLK</sub> =<br>84 MHz | 11.9   | -                       | ns                   |

|                        |                                        | AHB/APB1                                                       | 1      | -                       | t <sub>TIMxCLK</sub> |

|                        |                                        | prescaler = 1,<br>f <sub>TIMxCLK</sub> = 42 MHz                | 23.8   | -                       | ns                   |

| f                      | Timer external clock                   |                                                                | 0      | f <sub>TIMxCLK</sub> /2 | MHz                  |

| f <sub>EXT</sub>       | frequency on CH1 to CH4                |                                                                | 0      | 42                      | MHz                  |

| Res <sub>TIM</sub>     | Timer resolution                       |                                                                | -      | 16/32                   | bit                  |

|                        | 16-bit counter clock                   |                                                                | 1      | 65536                   | t <sub>TIMxCLK</sub> |

| t                      | period when internal clock is selected | f <sub>TIMxCLK</sub> = 84 MHz<br>APB1= 42 MHz                  | 0.0119 | 780                     | μs                   |

| <sup>t</sup> COUNTER   | 32-bit counter clock                   |                                                                | 1      | -                       | t <sub>TIMxCLK</sub> |

|                        | period when internal clock is selected |                                                                | 0.0119 | 51130563                | μs                   |

| +                      | Maximum possible count                 |                                                                | -      | 65536 × 65536           | t <sub>TIMxCLK</sub> |

| t <sub>MAX_COUNT</sub> | Maximum possible count                 |                                                                | -      | 51.1                    | S                    |

Table 52. Characteristics of TIMx connected to the APB1 domain<sup>(1)</sup>

1. TIMx is used as a general term to refer to the TIM2, TIM3, TIM4, TIM5, TIM6, TIM7, and TIM12 timers.

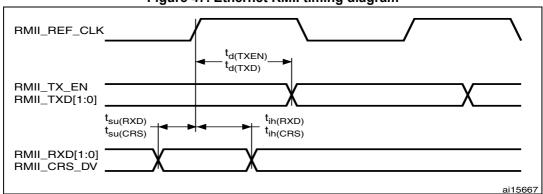

Figure 47. Ethernet RMII timing diagram

| Symbol               | Rating                                  | Min | Тур | Мах  | Unit |

|----------------------|-----------------------------------------|-----|-----|------|------|

| t <sub>su(RXD)</sub> | Receive data setup time                 | 2   | -   | -    | ns   |

| t <sub>ih(RXD)</sub> | Receive data hold time                  | 1   | -   | -    | ns   |

| t <sub>su(CRS)</sub> | Carrier sense set-up time               | 0.5 | -   | -    | ns   |

| t <sub>ih(CRS)</sub> | Carrier sense hold time                 | 2   | -   | -    | ns   |

| t <sub>d(TXEN)</sub> | (TXEN) Transmit enable valid delay time |     | 9.5 | 11   | ns   |

| t <sub>d(TXD)</sub>  | Transmit data valid delay time          | 8.5 | 10  | 11.5 | ns   |

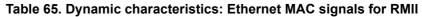

*Table 66* gives the list of Ethernet MAC signals for MII and *Figure 47* shows the corresponding timing diagram.

Figure 48. Ethernet MII timing diagram

#### **Electrical characteristics**

| Symbol                            | Parameter                                                                                                    | Min | Тур | Max                      | Unit | Comments                                                                                                                                 |  |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------|-----|-----|--------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------|--|

| R <sub>LOAD</sub> <sup>(2)</sup>  | Resistive load with buffer<br>ON                                                                             | 5   | -   | -                        | kΩ   |                                                                                                                                          |  |

| R <sub>0</sub> <sup>(2)</sup>     | Impedance output with<br>buffer OFF                                                                          | -   | -   | 15                       | kΩ   | When the buffer is OFF, the Minimum resistive load between DAC_OUT and $V_{SS}$ to have a 1% accuracy is 1.5 $M\Omega$                   |  |

| C <sub>LOAD</sub> <sup>(2)</sup>  | Capacitive load                                                                                              | -   | -   | 50                       | pF   | Maximum capacitive load at DAC_OUT pin (when the buffer is ON).                                                                          |  |

| DAC_OUT<br>min <sup>(2)</sup>     | Lower DAC_OUT voltage with buffer ON                                                                         | 0.2 | -   | -                        | V    | It gives the maximum output<br>excursion of the DAC.<br>It corresponds to 12-bit input code<br>(0x0E0) to (0xF1C) at V <sub>REF+</sub> = |  |

| DAC_OUT<br>max <sup>(2)</sup>     | Higher DAC_OUT voltage with buffer ON                                                                        | -   | -   | V <sub>DDA</sub> – 0.2   | V    | $V_{REF+} = 1.8 V$ (0x1C7) to (0xE38) at                                                                                                 |  |

| DAC_OUT<br>min <sup>(2)</sup>     | Lower DAC_OUT voltage with buffer OFF                                                                        | -   | 0.5 | -                        | mV   | It gives the maximum output                                                                                                              |  |

| DAC_OUT<br>max <sup>(2)</sup>     | Higher DAC_OUT voltage<br>with buffer OFF                                                                    | -   | -   | V <sub>REF+</sub> – 1LSB | V    | excursion of the DAC.                                                                                                                    |  |

| . (4)                             | DAC DC V <sub>REF</sub> current                                                                              | -   | 170 | 240                      |      | With no load, worst code (0x800)<br>at $V_{REF+}$ = 3.6 V in terms of DC<br>consumption on the inputs                                    |  |

| I <sub>VREF+</sub> <sup>(4)</sup> | consumption in quiescent mode (Standby mode)                                                                 | -   | 50  | 75                       | μA   | With no load, worst code (0xF1C)<br>at $V_{REF+}$ = 3.6 V in terms of DC<br>consumption on the inputs                                    |  |

|                                   | DAC DC VDDA current                                                                                          | -   | 280 | 380                      | μA   | With no load, middle code (0x800) on the inputs                                                                                          |  |

| I <sub>DDA</sub> <sup>(4)</sup>   | consumption in quiescent<br>mode <sup>(3)</sup>                                                              | -   | 475 | 625                      | μA   | With no load, worst code (0xF1C)<br>at $V_{REF+}$ = 3.6 V in terms of DC<br>consumption on the inputs                                    |  |

| DNL <sup>(4)</sup>                | Differential non linearity<br>Difference between two                                                         | -   | -   | ±0.5                     | LSB  | Given for the DAC in 10-bit configuration.                                                                                               |  |

|                                   | consecutive code-1LSB)                                                                                       | -   | -   | ±2                       | LSB  | Given for the DAC in 12-bit configuration.                                                                                               |  |

|                                   | Integral non linearity<br>(difference between                                                                | -   | -   | ±1                       | LSB  | Given for the DAC in 10-bit configuration.                                                                                               |  |

| INL <sup>(4)</sup>                | measured value at Code i<br>and the value at Code i on a<br>line drawn between Code 0<br>and last Code 1023) | -   | -   | ±4                       | LSB  | Given for the DAC in 12-bit configuration.                                                                                               |  |

Table 74. DAC characteristics (continued)

| раскаде теспалісаї дата |       |             |       |                       |        |        |  |

|-------------------------|-------|-------------|-------|-----------------------|--------|--------|--|

| Symbol                  |       | millimeters |       | inches <sup>(1)</sup> |        |        |  |

| Symbol                  | Min   | Тур         | Мах   | Min                   | Тур    | Max    |  |

| А                       | 0.540 | 0.570       | 0.600 | 0.0213                | 0.0224 | 0.0236 |  |

| A1                      | -     | 0.190       | -     | -                     | 0.0075 | -      |  |

| A2                      | -     | 0.380       | -     | -                     | 0.0150 | -      |  |

| A3 <sup>(2)</sup>       | -     | 0.025       | -     | -                     | 0.0010 | -      |  |

| b <sup>(3)</sup>        | 0.240 | 0.270       | 0.300 | 0.0094                | 0.0106 | 0.0118 |  |

| D                       | 4.188 | 4.223       | 4.258 | 0.1649                | 0.1663 | 0.1676 |  |

| E                       | 3.934 | 3.969       | 4.004 | 0.1549                | 0.1563 | 0.1576 |  |

| е                       | -     | 0.400       | -     | -                     | 0.0157 | -      |  |

| e1                      | -     | 3.600       | -     | -                     | 0.1417 | -      |  |

| e2                      | -     | 3.200       | -     | -                     | 0.1260 | -      |  |

| F                       | -     | 0.3115      | -     | -                     | 0.0123 | -      |  |

| G                       | -     | 0.3845      | -     | -                     | 0.0151 | -      |  |

| aaa                     | -     | 0.100       | -     | -                     | 0.0039 | -      |  |

| bbb                     | -     | 0.100       | -     | -                     | 0.0039 | -      |  |

| ссс                     | -     | 0.100       | -     | -                     | 0.0039 | -      |  |

| ddd                     | -     | 0.050       | -     | -                     | 0.0020 | -      |  |

| eee                     | -     | 0.050       | -     | -                     | 0.0020 | -      |  |

## Table 90. WLCSP90 - 4.223 x 3.969 mm, 0.400 mm pitch wafer level chip scale package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. Back side coating.

3. Dimension is measured at the maximum bump diameter parallel to primary datum Z.

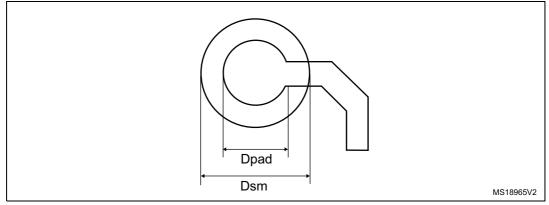

## Figure 76. WLCSP90 - 4.223 x 3.969 mm, 0.400 mm pitch wafer level chip scale recommended footprint

## 6.2 LQFP64 package information

Figure 78. LQFP64 – 64-pin, 10 x 10 mm low-profile quad flat package outline SEATING PLANE С <[₽] 0.25 mm GAUGE PLANE Ŧ Ł ¥ D k D1 L1 D3 48 33 32 49 b ШШ **1**7 64 ₿₿₿₿ ▋▋₿ Ht 8888 16 PIN 1 IDENTIFICATION 1 5W\_ME\_V3

1. Drawing is not to scale.

| Table 92. LQFP64 – 64-pin 10 x 10 mm low-profile quad flat package |

|--------------------------------------------------------------------|

| mechanical data                                                    |

| Symbol |       | millimeters |       | inches <sup>(1)</sup> |        |        |  |

|--------|-------|-------------|-------|-----------------------|--------|--------|--|

|        | Min   | Тур         | Мах   | Min                   | Тур    | Max    |  |

| А      | -     | -           | 1.600 | -                     | -      | 0.0630 |  |

| A1     | 0.050 | -           | 0.150 | 0.0020                | -      | 0.0059 |  |

| A2     | 1.350 | 1.400       | 1.450 | 0.0531                | 0.0551 | 0.0571 |  |

| b      | 0.170 | 0.220       | 0.270 | 0.0067                | 0.0087 | 0.0106 |  |

| с      | 0.090 | -           | 0.200 | 0.0035                | -      | 0.0079 |  |

| D      | -     | 12.000      | -     | -                     | 0.4724 | -      |  |

| D1     | -     | 10.000      | -     | -                     | 0.3937 | -      |  |

| D3     | -     | 7.500       | -     | -                     | 0.2953 | -      |  |

| E      | -     | 12.000      | -     | -                     | 0.4724 | -      |  |

| E1     | -     | 10.000      | -     | -                     | 0.3937 | -      |  |

## Appendix A Application block diagrams

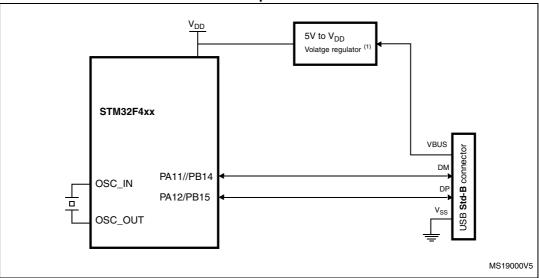

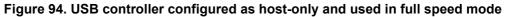

### A.1 USB OTG full speed (FS) interface solutions

Figure 93. USB controller configured as peripheral-only and used in Full speed mode

1. External voltage regulator only needed when building a  $V_{\text{BUS}}$  powered device.

2. The same application can be developed using the OTG HS in FS mode to achieve enhanced performance thanks to the large Rx/Tx FIFO and to a dedicated DMA controller.

The current limiter is required only if the application has to support a V<sub>BUS</sub> powered device. A basic power switch can be used if 5 V are available on the application board.

2. The same application can be developed using the OTG HS in FS mode to achieve enhanced performance thanks to the large Rx/Tx FIFO and to a dedicated DMA controller.

Table 100. Document revision history (continued)