#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                    |

|----------------------------|-------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                        |

| Speed                      | 168MHz                                                                                    |

| Connectivity               | CANbus, DCMI, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                         |

| Number of I/O              | 82                                                                                        |

| Program Memory Size        | 1MB (1M x 8)                                                                              |

| Program Memory Type        | FLASH                                                                                     |

| EEPROM Size                |                                                                                           |

| RAM Size                   | 192K × 8                                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                               |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                                     |

| Oscillator Type            | Internal                                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                         |

| Mounting Type              | Surface Mount                                                                             |

| Package / Case             | 100-LQFP                                                                                  |

| Supplier Device Package    | 100-LQFP (14x14)                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f407vgt6                     |

|                            |                                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| recommended footprint                                                        | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| UFBGA176+25 ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ball grid array package outline                                              | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| UFBGA176+25 - 201-ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ball grid array recommended footprint                                        | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| UFBGA176+25 marking example (package top view)1                              | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

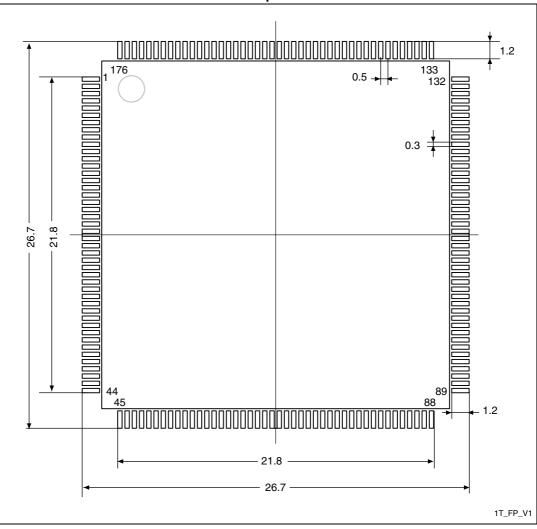

| LQFP176 - 176-pin, 24 x 24 mm low profile quad flat package outline          | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| LQFP176 - 176-pin, 24 x 24 mm low profile quad flat recommended footprint 18 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| LQFP176 marking example (package top view)18                                 | 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| USB controller configured as peripheral-only and used                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| in Full speed mode                                                           | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

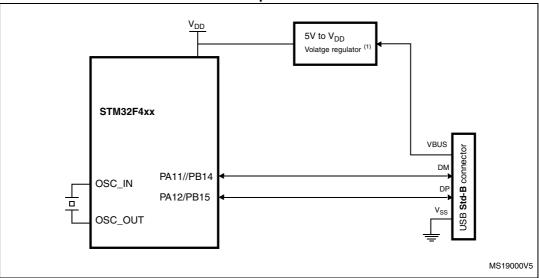

| USB controller configured as host-only and used in full speed mode           | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| USB controller configured in dual mode and used in full speed mode           | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| USB controller configured as peripheral, host, or dual-mode                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| and used in high speed mode                                                  | 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

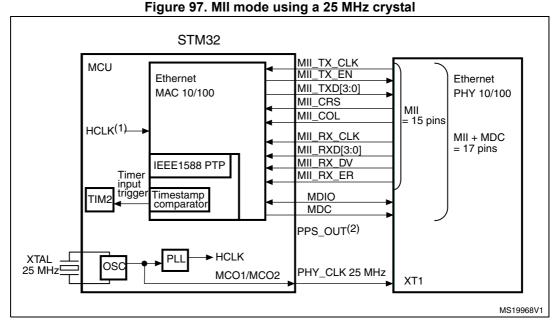

| MII mode using a 25 MHz crystal                                              | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

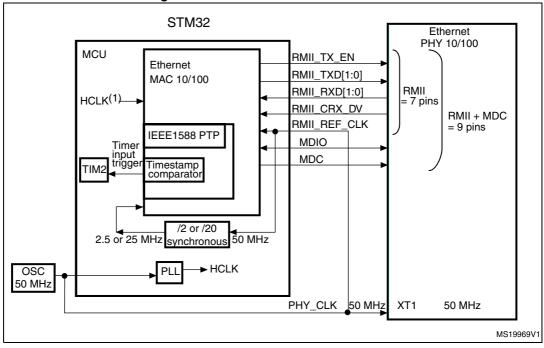

| RMII with a 50 MHz oscillator                                                | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RMII with a 25 MHz crystal and PHY with PLL19                                | 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                              | ball grid array package outline11UFBGA176+25 - 201-ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch11ball grid array recommended footprint11UFBGA176+25 marking example (package top view)11LQFP176 - 176-pin, 24 x 24 mm low profile quad flat package outline14LQFP176 - 176-pin, 24 x 24 mm low profile quad flat recommended footprint.16LQFP176 marking example (package top view)16USB controller configured as peripheral-only and used16in Full speed mode16USB controller configured as host-only and used in full speed mode16USB controller configured as peripheral, host, or dual-mode16and used in high speed mode16MII mode using a 25 MHz crystal16RMII with a 50 MHz oscillator16 |

Standby mode, the SRAM and register contents are lost except for registers in the backup domain and the backup SRAM when selected.

The device exits the Standby mode when an external reset (NRST pin), an IWDG reset, a rising edge on the WKUP pin, or an RTC alarm / wakeup / tamper /time stamp event occurs.

The standby mode is not supported when the embedded voltage regulator is bypassed and the  $V_{12}$  domain is controlled by an external power.

## 2.2.20 V<sub>BAT</sub> operation

The  $V_{BAT}$  pin allows to power the device  $V_{BAT}$  domain from an external battery, an external supercapacitor, or from  $V_{DD}$  when no external battery and an external supercapacitor are present.

$V_{BAT}$  operation is activated when  $V_{DD}$  is not present.

The V<sub>BAT</sub> pin supplies the RTC, the backup registers and the backup SRAM.

Note: When the microcontroller is supplied from  $V_{BAT}$ , external interrupts and RTC alarm/events do not exit it from  $V_{BAT}$  operation.

When PDR\_ON pin is not connected to  $V_{DD}$  (internal reset OFF), the  $V_{BAT}$  functionality is no more available and  $V_{BAT}$  pin should be connected to  $V_{DD}$ .

## 2.2.21 Timers and watchdogs

The STM32F405xx and STM32F407xx devices include two advanced-control timers, eight general-purpose timers, two basic timers and two watchdog timers.

All timer counters can be frozen in debug mode.

*Table 4* compares the features of the advanced-control, general-purpose and basic timers.

| Timer<br>type        | Timer         | Counter<br>resolution | Counter<br>type         | Prescaler<br>factor                   | DMA<br>request<br>generation | Capture/<br>compare<br>channels | Complemen-<br>tary output | Max<br>interface<br>clock<br>(MHz) | Max<br>timer<br>clock<br>(MHz) |

|----------------------|---------------|-----------------------|-------------------------|---------------------------------------|------------------------------|---------------------------------|---------------------------|------------------------------------|--------------------------------|

| Advanceo<br>-control | TIM1,<br>TIM8 | 16-bit                | Up,<br>Down,<br>Up/down | Any integer<br>between 1<br>and 65536 | Yes                          | 4                               | Yes                       | 84                                 | 168                            |

Table 4. Timer feature comparison

## 2.2.31 Universal serial bus on-the-go high-speed (OTG\_HS)

The STM32F405xx and STM32F407xx devices embed a USB OTG high-speed (up to 480 Mb/s) device/host/OTG peripheral. The USB OTG HS supports both full-speed and high-speed operations. It integrates the transceivers for full-speed operation (12 MB/s) and features a UTMI low-pin interface (ULPI) for high-speed operation (480 MB/s). When using the USB OTG HS in HS mode, an external PHY device connected to the ULPI is required.

The USB OTG HS peripheral is compliant with the USB 2.0 specification and with the OTG 1.0 specification. It has software-configurable endpoint setting and supports suspend/resume. The USB OTG full-speed controller requires a dedicated 48 MHz clock that is generated by a PLL connected to the HSE oscillator.

The major features are:

- Combined Rx and Tx FIFO size of 1 Kbit × 35 with dynamic FIFO sizing

- Supports the session request protocol (SRP) and host negotiation protocol (HNP)

- 6 bidirectional endpoints

- 12 host channels with periodic OUT support

- Internal FS OTG PHY support

- External HS or HS OTG operation supporting ULPI in SDR mode. The OTG PHY is connected to the microcontroller ULPI port through 12 signals. It can be clocked using the 60 MHz output.

- Internal USB DMA

- HNP/SNP/IP inside (no need for any external resistor)

- for OTG/Host modes, a power switch is needed in case bus-powered devices are connected

## 2.2.32 Digital camera interface (DCMI)

The camera interface is *not* available in STM32F405xx devices.

STM32F407xx products embed a camera interface that can connect with camera modules and CMOS sensors through an 8-bit to 14-bit parallel interface, to receive video data. The camera interface can sustain a data transfer rate up to 54 Mbyte/s at 54 MHz. It features:

- Programmable polarity for the input pixel clock and synchronization signals

- Parallel data communication can be 8-, 10-, 12- or 14-bit

- Supports 8-bit progressive video monochrome or raw bayer format, YCbCr 4:2:2 progressive video, RGB 565 progressive video or compressed data (like JPEG)

- Supports continuous mode or snapshot (a single frame) mode

- Capability to automatically crop the image

## 2.2.33 Random number generator (RNG)

All STM32F405xx and STM32F407xx products embed an RNG that delivers 32-bit random numbers generated by an integrated analog circuit.

## 2.2.34 General-purpose input/outputs (GPIOs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain, with or without pull-up or pull-down), as input (floating, with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog

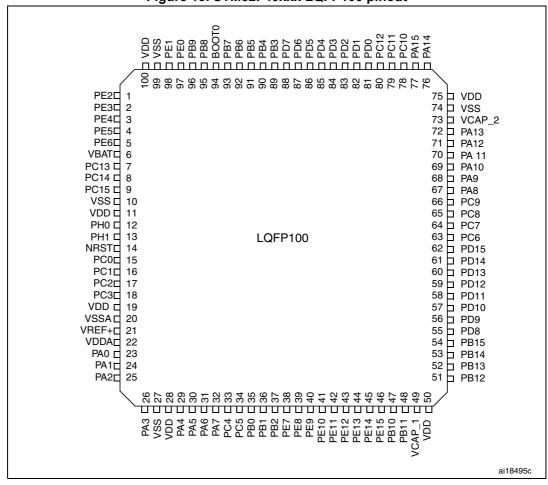

Figure 13. STM32F40xxx LQFP100 pinout

1. The above figure shows the package top view.

63/202

DocID022152 Rev 8

|        | Table 9. Alternate function mapping (continued) |                       |           |          |                  |               |                                |                      |                        |                    |                           |                    |                                      |                      |                |      |          |

|--------|-------------------------------------------------|-----------------------|-----------|----------|------------------|---------------|--------------------------------|----------------------|------------------------|--------------------|---------------------------|--------------------|--------------------------------------|----------------------|----------------|------|----------|

|        |                                                 | AF0                   | AF1       | AF2      | AF3              | AF4           | AF5                            | AF6                  | AF7                    | AF8                | AF9                       | AF10               | AF11                                 | AF12                 | AF13           |      |          |

| Po     | ort                                             | SYS                   | TIM1/2    | TIM3/4/5 | TIM8/9/10<br>/11 | I2C1/2/3      | SPI1/SPI2/<br>I2S2/I2S2e<br>xt | SPI3/I2Sext<br>/I2S3 | USART1/2/3/<br>I2S3ext | UART4/5/<br>USART6 | CAN1/2<br>TIM12/13/<br>14 | OTG_FS/<br>OTG_HS  | ETH                                  | FSMC/SDIO<br>/OTG_FS | DCMI           | AF14 | AF15     |

|        | PB0                                             | -                     | TIM1_CH2N | TIM3_CH3 | TIM8_CH2N        | -             | -                              | -                    | -                      | -                  | -                         | OTG_HS_ULPI_<br>D1 | ETH _MII_RXD2                        | -                    | -              | -    | EVENTOUT |

|        | PB1                                             | -                     | TIM1_CH3N | TIM3_CH4 | TIM8_CH3N        |               | -                              | -                    | -                      | -                  | -                         | OTG_HS_ULPI_<br>D2 | ETH _MII_RXD3                        | -                    | -              | -    | EVENTOUT |

|        | PB2                                             | -                     | -         | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                  | -                                    | -                    | -              | -    | EVENTOUT |

|        | PB3                                             | JTDO/<br>TRACES<br>WO | TIM2_CH2  | -        | -                | -             | SPI1_SCK                       | SPI3_SCK<br>I2S3_CK  | -                      | -                  | -                         | -                  | -                                    | -                    | -              | -    | EVENTOUT |

|        | PB4                                             | NJTRST                | -         | TIM3_CH1 |                  | -             | SPI1_MISO                      | SPI3_MISO            | I2S3ext_SD             | -                  | -                         | -                  | -                                    | -                    | -              | -    | EVENTOUT |

|        | PB5                                             | -                     | -         | TIM3_CH2 |                  | I2C1_SMB<br>A | SPI1_MOSI                      | SPI3_MOSI<br>I2S3_SD |                        | -                  | CAN2_RX                   | OTG_HS_ULPI_<br>D7 | ETH_PPS_OUT                          | -                    | DCMI_D10       | -    | EVENTOUT |

|        | PB6                                             | -                     | -         | TIM4_CH1 |                  | I2C1_SCL      | -                              | -                    | USART1_TX              | -                  | CAN2_TX                   | -                  | -                                    | -                    | DCMI_D5        | -    | EVENTOUT |

|        | PB7                                             | -                     | -         | TIM4_CH2 |                  | I2C1_SDA      | -                              | -                    | USART1_RX              | -                  | -                         | -                  | -                                    | FSMC_NL              | DCMI_VSYN<br>C | -    | EVENTOUT |

| Port B | PB8                                             | -                     | -         | TIM4_CH3 | TIM10_CH1        | I2C1_SCL      | -                              | -                    | -                      | -                  | CAN1_RX                   | -                  | ETH _MII_TXD3                        | SDIO_D4              | DCMI_D6        | -    | EVENTOUT |

|        | PB9                                             | -                     | -         | TIM4_CH4 | TIM11_CH1        | I2C1_SDA      | SPI2_NSS<br>I2S2_WS            | -                    | -                      | -                  | CAN1_TX                   | -                  | -                                    | SDIO_D5              | DCMI_D7        | -    | EVENTOUT |

|        | PB10                                            | -                     | TIM2_CH3  | -        | -                | I2C2_SCL      | SPI2_SCK<br>I2S2_CK            | -                    | USART3_TX              | -                  | -                         | OTG_HS_ULPI_<br>D3 | ETH_MII_RX_ER                        | -                    | -              | -    | EVENTOUT |

|        | PB11                                            | -                     | TIM2_CH4  | -        | -                | I2C2_SDA      | -                              | -                    | USART3_RX              | -                  | -                         | OTG_HS_ULPI_<br>D4 | ETH _MII_TX_EN<br>ETH<br>_RMII_TX_EN | -                    | -              | -    | EVENTOUT |

|        | PB12                                            | -                     | TIM1_BKIN | -        | -                | I2C2_<br>SMBA | SPI2_NSS<br>I2S2_WS            | -                    | USART3_CK              | -                  | CAN2_RX                   | OTG_HS_ULPI_<br>D5 | ETH _MII_TXD0<br>ETH _RMII_TXD0      | OTG_HS_ID            | -              | -    | EVENTOUT |

|        | PB13                                            | -                     | TIM1_CH1N | -        | -                | -             | SPI2_SCK<br>I2S2_CK            | -                    | USART3_CTS             | -                  | CAN2_TX                   | OTG_HS_ULPI_<br>D6 | ETH _MII_TXD1<br>ETH _RMII_TXD1      | -                    | -              | -    | EVENTOUT |

|        | PB14                                            | -                     | TIM1_CH2N | -        | TIM8_CH2N        | -             | SPI2_MISO                      | I2S2ext_SD           | USART3_RTS             | -                  | TIM12_CH1                 | -                  | -                                    | OTG_HS_DM            | -              | -    | EVENTOUT |

|        | PB15                                            | RTC_<br>REFIN         | TIM1_CH3N | -        | TIM8_CH3N        | -             | SPI2_MOSI<br>I2S2_SD           | -                    | -                      | -                  | TIM12_CH2                 | -                  | -                                    | OTG_HS_DP            | -              | -    | EVENTOUT |

Pinouts and pin description

577

69/202

DocID022152 Rev 8

|        |      | 1   | r      | 1        | 1                |               |                                |                      |                        |                    | ``                        | ,                   |              | 1                    | 1              | r    | ,        |

|--------|------|-----|--------|----------|------------------|---------------|--------------------------------|----------------------|------------------------|--------------------|---------------------------|---------------------|--------------|----------------------|----------------|------|----------|

|        |      | AF0 | AF1    | AF2      | AF3              | AF4           | AF5                            | AF6                  | AF7                    | AF8                | AF9                       | AF10                | AF11         | AF12                 | AF13           |      |          |

| Po     | ort  | SYS | TIM1/2 | TIM3/4/5 | TIM8/9/10<br>/11 | I2C1/2/3      | SPI1/SPI2/<br>I2S2/I2S2e<br>xt | SPI3/I2Sext<br>/I2S3 | USART1/2/3/<br>I2S3ext | UART4/5/<br>USART6 | CAN1/2<br>TIM12/13/<br>14 | OTG_FS/<br>OTG_HS   | ЕТН          | FSMC/SDIO<br>/OTG_FS | DCMI           | AF14 | AF15     |

|        | PH0  | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                   | -            | -                    | -              | -    | EVENTOUT |

|        | PH1  | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                   | -            | -                    | -              | -    | EVENTOUT |

|        | PH2  | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                   | ETH _MII_CRS | -                    | -              | -    | EVENTOUT |

|        | PH3  | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                   | ETH _MII_COL | -                    | -              | -    | EVENTOUT |

|        | PH4  | -   | -      | -        | -                | I2C2_SCL      | -                              | -                    | -                      | -                  | -                         | OTG_HS_ULPI_<br>NXT | -            | -                    | -              | -    | EVENTOUT |

|        | PH5  | -   | -      | -        | -                | I2C2_SDA      | -                              | -                    | -                      | -                  | -                         | -                   | -            | -                    | -              | -    | EVENTOUT |

|        | PH6  | -   | -      | -        | -                | I2C2_<br>SMBA | -                              | -                    | -                      | -                  | TIM12_CH1                 | -                   | ETH_MII_RXD2 | -                    | -              | -    | EVENTOUT |

| DestU  | PH7  | -   | -      | -        | -                | I2C3_SCL      | -                              | -                    | -                      | -                  | -                         | -                   | ETH_MII_RXD3 | -                    | -              | -    | EVENTOUT |

| Port H | PH8  | -   | -      | -        | -                | I2C3_SDA      | -                              | -                    | -                      | -                  | -                         | -                   | -            | -                    | DCMI_<br>HSYNC | -    | EVENTOUT |

|        | PH9  | -   | -      | -        | -                | I2C3_<br>SMBA | -                              | -                    | -                      | -                  | TIM12_CH2                 | -                   | -            | -                    | DCMI_D0        | -    | EVENTOUT |

|        | PH10 | -   | -      | TIM5_CH1 | -                | -             | -                              | -                    | -                      | -                  | -                         | -                   | -            | -                    | DCMI_D1        | -    | EVENTOUT |

|        | PH11 | -   | -      | TIM5_CH2 | -                | -             | -                              | -                    | -                      | -                  | -                         | -                   | -            | -                    | DCMI_D2        | -    | EVENTOUT |

|        | PH12 | -   | -      | TIM5_CH3 | -                | -             | -                              | -                    | -                      | -                  | -                         | -                   | -            | -                    | DCMI_D3        | -    | EVENTOUT |

|        | PH13 | -   | -      | -        | TIM8_CH1N        | -             | -                              | -                    | -                      | -                  | CAN1_TX                   | -                   | -            | -                    | -              | -    | EVENTOUT |

|        | PH14 | -   | -      | -        | TIM8_CH2N        | -             | -                              | -                    | -                      | -                  | -                         | -                   | =            | -                    | DCMI_D4        | -    | EVENTOUT |

|        | PH15 | -   | -      | -        | TIM8_CH3N        | -             | -                              | -                    | -                      | -                  | -                         | -                   | -            | -                    | DCMI_D11       | -    | EVENTOUT |

Table 9. Alternate function mapping (continued)

577

| Bus       | Boundary address          | Peripheral                     |

|-----------|---------------------------|--------------------------------|

|           | 0xE00F FFFF - 0xFFFF FFFF | Reserved                       |

|           |                           |                                |

| Cortex-M4 | 0xE000 0000 - 0xE00F FFFF | Cortex-M4 internal peripherals |

|           | 0xA000 1000 - 0xDFFF FFFF | Reserved                       |

|           | 0xA000 0000 - 0xA000 0FFF | FSMC control register          |

|           | 0x9000 0000 - 0x9FFF FFFF | FSMC bank 4                    |

| AHB3      | 0x8000 0000 - 0x8FFF FFFF | FSMC bank 3                    |

|           | 0x7000 0000 - 0x7FFF FFFF | FSMC bank 2                    |

|           | 0x6000 0000 - 0x6FFF FFFF | FSMC bank 1                    |

|           | 0x5006 0C00- 0x5FFF FFFF  | Reserved                       |

|           | 0x5006 0800 - 0x5006 0BFF | RNG                            |

| AHB2      | 0x5005 0400 - 0x5006 07FF | Reserved                       |

|           | 0x5005 0000 - 0x5005 03FF | DCMI                           |

|           | 0x5004 0000- 0x5004 FFFF  | Reserved                       |

|           | 0x5000 0000 - 0x5003 FFFF | USB OTG FS                     |

|           | 0x4008 0000- 0x4FFF FFFF  | Reserved                       |

Table 10. register boundary addresses

|                 |                               |                                                                              |                       | Тур                       | Ма                        | x <sup>(2)</sup>           |      |

|-----------------|-------------------------------|------------------------------------------------------------------------------|-----------------------|---------------------------|---------------------------|----------------------------|------|

| Symbol          | Parameter                     | Conditions                                                                   | fhclk                 | T <sub>A</sub> =<br>25 °C | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |

|                 |                               |                                                                              | 168 MHz               | 87                        | 102                       | 109                        |      |

|                 |                               |                                                                              | 144 MHz               | 67                        | 80                        | 86                         |      |

|                 |                               |                                                                              | 120 MHz               | 56                        | 69                        | 75                         |      |

|                 |                               | External clock <sup>(3)</sup> , all<br>peripherals enabled <sup>(4)(5)</sup> | 90 MHz                | 44                        | 56                        | 62                         |      |

|                 |                               |                                                                              | 60 MHz                | 30                        | 42                        | 49                         |      |

|                 |                               |                                                                              | 30 MHz                | 16                        | 28                        | 35                         |      |

|                 |                               |                                                                              | 25 MHz                | 12                        | 24                        | 31                         |      |

|                 |                               |                                                                              | 16 MHz <sup>(6)</sup> | 9                         | 20                        | 28                         |      |

| 1               |                               |                                                                              | 8 MHz                 | 5                         | 17                        | 24                         |      |

|                 |                               |                                                                              | 4 MHz                 | 3                         | 15                        | 22                         | - mA |

|                 | Supply current in<br>Run mode |                                                                              | 2 MHz                 | 2                         | 14                        | 21                         |      |

| I <sub>DD</sub> |                               |                                                                              | 168 MHz               | 40                        | 54                        | 61                         |      |

|                 |                               |                                                                              | 144 MHz               | 31                        | 43                        | 50                         |      |

|                 |                               |                                                                              | 120 MHz               | 26                        | 38                        | 45                         |      |

|                 |                               |                                                                              | 90 MHz                | 20                        | 32                        | 39                         |      |

|                 |                               | - (2)                                                                        | 60 MHz                | 14                        | 26                        | 33                         |      |

|                 |                               | External clock <sup>(3)</sup> , all peripherals disabled <sup>(4)(5)</sup>   | 30 MHz                | 8                         | 20                        | 27                         |      |

|                 |                               |                                                                              | 25 MHz                | 6                         | 18                        | 25                         |      |

|                 |                               |                                                                              | 16 MHz <sup>(6)</sup> | 5                         | 16                        | 24                         |      |

|                 |                               |                                                                              | 8 MHz                 | 3                         | 15                        | 22                         |      |

|                 |                               |                                                                              | 4 MHz                 | 2                         | 14                        | 21                         |      |

|                 |                               |                                                                              | 2 MHz                 | 2                         | 14                        | 21                         |      |

# Table 20. Typical and maximum current consumption in Run mode, code with data processing running from Flash memory (ART accelerator enabled) or RAM <sup>(1)</sup>

1. Code and data processing running from SRAM1 using boot pins.

2. Guaranteed by characterization, tested in production at V<sub>DD</sub> max and f<sub>HCLK</sub> max with peripherals enabled.

3. External clock is 4 MHz and PLL is on when  $f_{HCLK}$  > 25 MHz.

4. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.6 mA per ADC for the analog part.

5. When analog peripheral blocks such as ADCs, DACs, HSE, LSE, HSI, or LSI are ON, an additional power consumption should be considered.

6. In this case HCLK = system clock/2.

57

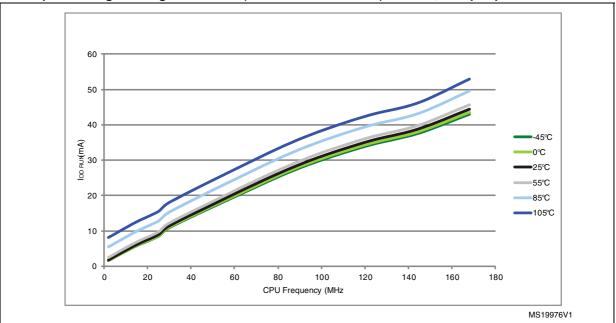

Figure 26. Typical current consumption versus temperature, Run mode, code with data processing running from Flash (ART accelerator OFF) or RAM, and peripherals OFF

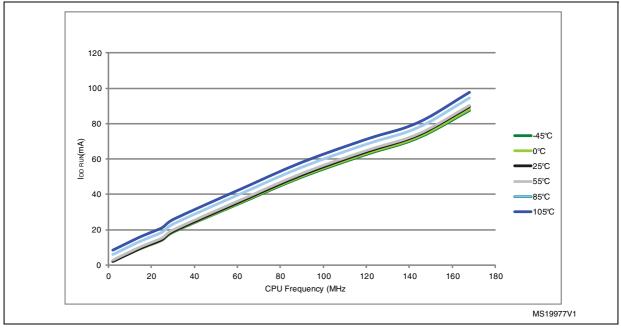

# Figure 27. Typical current consumption versus temperature, Run mode, code with data processing running from Flash (ART accelerator OFF) or RAM, and peripherals ON

## Low-speed external user clock generated from an external source

The characteristics given in *Table 31* result from tests performed using an low-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 14*.

| Symbol                                     | Parameter                                              | Conditions                                     | Min                | Тур    | Max                | Unit |

|--------------------------------------------|--------------------------------------------------------|------------------------------------------------|--------------------|--------|--------------------|------|

| f <sub>LSE_ext</sub>                       | User External clock source<br>frequency <sup>(1)</sup> |                                                | -                  | 32.768 | 1000               | kHz  |

| V <sub>LSEH</sub>                          | OSC32_IN input pin high level voltage                  |                                                | 0.7V <sub>DD</sub> | -      | V <sub>DD</sub>    | V    |

| V <sub>LSEL</sub>                          | OSC32_IN input pin low level voltage                   | -                                              | V <sub>SS</sub>    | -      | 0.3V <sub>DD</sub> |      |

| t <sub>w(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN high or low time <sup>(1)</sup>               |                                                | 450                | -      | -                  | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN rise or fall time <sup>(1)</sup>              |                                                | -                  | -      | 50                 | 115  |

| C <sub>in(LSE)</sub>                       | OSC32_IN input capacitance <sup>(1)</sup>              | -                                              | -                  | 5      | -                  | pF   |

| DuCy <sub>(LSE)</sub>                      | Duty cycle                                             | -                                              | 30                 | -      | 70                 | %    |

| ال                                         | OSC32_IN Input leakage current                         | $V_{SS} \!\leq\! \! V_{IN} \!\leq\! \! V_{DD}$ | -                  | -      | ±1                 | μA   |

| Table 31. Low-speed external user clock characteristics |

|---------------------------------------------------------|

|---------------------------------------------------------|

1. Guaranteed by design.

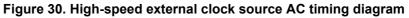

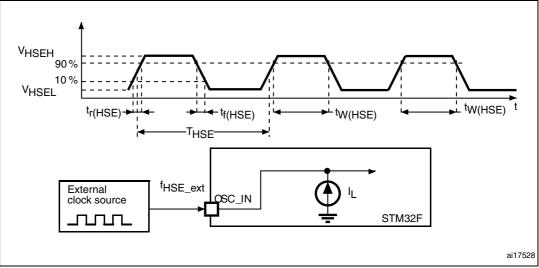

Figure 34. ACC<sub>LSI</sub> versus temperature

## 5.3.10 PLL characteristics

The parameters given in *Table 36* and *Table 37* are derived from tests performed under temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

| Symbol                 | Parameter                             | Conditions         | Min                 | Тур | Max  | Unit |  |

|------------------------|---------------------------------------|--------------------|---------------------|-----|------|------|--|

| f <sub>PLL_IN</sub>    | PLL input clock <sup>(1)</sup>        | -                  | 0.95 <sup>(2)</sup> | 1   | 2.10 | MHz  |  |

| f <sub>PLL_OUT</sub>   | PLL multiplier output clock           | -                  | 24                  | -   | 168  | MHz  |  |

| f <sub>PLL48_OUT</sub> | 48 MHz PLL multiplier output<br>clock | -                  | -                   | 48  | 75   | MHz  |  |

| f <sub>VCO_OUT</sub>   | PLL VCO output                        | -                  | 100                 | -   | 432  | MHz  |  |

| t                      | PLL lock time                         | VCO freq = 100 MHz | 75                  | -   | 200  | μs   |  |

| t <sub>LOCK</sub>      |                                       | VCO freq = 432 MHz | 100                 | -   | 300  | μο   |  |

Table 36. Main PLL characteristics

| Symbol                          | Parameter                                        | Conditions                   | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit |

|---------------------------------|--------------------------------------------------|------------------------------|--------------------|-----|--------------------|------|

| t <sub>prog</sub>               | Double word programming                          |                              | -                  | 16  | 100 <sup>(2)</sup> | μs   |

| t <sub>ERASE16KB</sub>          | Sector (16 KB) erase time                        | T <sub>A</sub> = 0 to +40 °C | -                  | 230 | -                  |      |

| t <sub>ERASE64KB</sub>          | Sector (64 KB) erase time                        | V <sub>DD</sub> = 3.3 V      | -                  | 490 | -                  | ms   |

| t <sub>ERASE128KB</sub>         | Sector (128 KB) erase time                       | V <sub>PP</sub> = 8.5 V      | -                  | 875 | -                  |      |

| t <sub>ME</sub>                 | Mass erase time                                  |                              | -                  | 6.9 | -                  | S    |

| V <sub>prog</sub>               | Programming voltage                              | -                            | 2.7                | -   | 3.6                | V    |

| V <sub>PP</sub>                 | V <sub>PP</sub> voltage range                    | -                            | 7                  | -   | 9                  | V    |

| I <sub>PP</sub>                 | Minimum current sunk on the $V_{\rm PP}$ pin     | -                            | 10                 | -   | -                  | mA   |

| t <sub>VPP</sub> <sup>(3)</sup> | Cumulative time during which $V_{PP}$ is applied | -                            | -                  | -   | 1                  | hour |

| Table 41. Flash memor | y programming with V <sub>PP</sub> |

|-----------------------|------------------------------------|

|-----------------------|------------------------------------|

1. Guaranteed by design.

2. The maximum programming time is measured after 100K erase operations.

3.  $V_{PP}$  should only be connected during programming/erasing.

| Symbol           | Parameter      | Conditions                                                                              | Value<br>Min <sup>(1)</sup> | Unit    |

|------------------|----------------|-----------------------------------------------------------------------------------------|-----------------------------|---------|

| N <sub>END</sub> | Endurance      | $T_A = -40$ to +85 °C (6 suffix versions)<br>$T_A = -40$ to +105 °C (7 suffix versions) | 10                          | kcycles |

| t <sub>RET</sub> | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C                                       | 30                          |         |

|                  |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C                                      | 10                          | Years   |

|                  |                | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 55 °C                                     | 20                          |         |

#### Table 42. Flash memory endurance and data retention

1. Guaranteed by characterization.

2. Cycling performed over the whole temperature range.

## 5.3.13 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

## Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

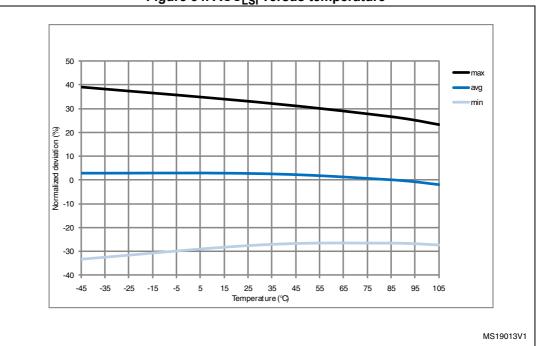

Figure 54. Asynchronous non-multiplexed SRAM/PSRAM/NOR read waveforms

1. Mode 2/B, C and D only. In Mode 1, FSMC\_NADV is not used.

#### Table 75. Asynchronous non-multiplexed SRAM/PSRAM/NOR read timings<sup>(1)(2)</sup>

| Symbol                    | Parameter                                    | Min                     | Max                    | Unit |

|---------------------------|----------------------------------------------|-------------------------|------------------------|------|

| t <sub>w(NE)</sub>        | FSMC_NE low time                             | 2T <sub>HCLK</sub> -0.5 | 2 T <sub>HCLK</sub> +1 | ns   |

| t <sub>v(NOE_NE)</sub>    | FSMC_NEx low to FSMC_NOE low                 | 0.5                     | 3                      | ns   |

| t <sub>w(NOE)</sub>       | FSMC_NOE low time                            | 2T <sub>HCLK</sub> –2   | 2T <sub>HCLK</sub> + 2 | ns   |

| t <sub>h(NE_NOE)</sub>    | FSMC_NOE high to FSMC_NE high hold time      | 0                       | -                      | ns   |

| t <sub>v(A_NE)</sub>      | FSMC_NEx low to FSMC_A valid                 | -                       | 4.5                    | ns   |

| t <sub>h(A_NOE)</sub>     | Address hold time after FSMC_NOE high        | 4                       | -                      | ns   |

| t <sub>v(BL_NE)</sub>     | FSMC_NEx low to FSMC_BL valid                | -                       | 1.5                    | ns   |

| t <sub>h(BL_NOE)</sub>    | FSMC_BL hold time after FSMC_NOE high        | 0                       | -                      | ns   |

| t <sub>su(Data_NE)</sub>  | Data to FSMC_NEx high setup time             | T <sub>HCLK</sub> +4    | -                      | ns   |

| t <sub>su(Data_NOE)</sub> | Data to FSMC_NOEx high setup time            | T <sub>HCLK</sub> +4    | -                      | ns   |

| t <sub>h(Data_NOE)</sub>  | Data hold time after FSMC_NOE high           | 0                       | -                      | ns   |

| t <sub>h(Data_NE)</sub>   | (Data_NE) Data hold time after FSMC_NEx high |                         | -                      | ns   |

| t <sub>v(NADV_NE)</sub>   | FSMC_NEx low to FSMC_NADV low                | -                       | 2                      | ns   |

| t <sub>w(NADV)</sub>      | FSMC_NADV low time                           | -                       | T <sub>HCLK</sub>      | ns   |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization.

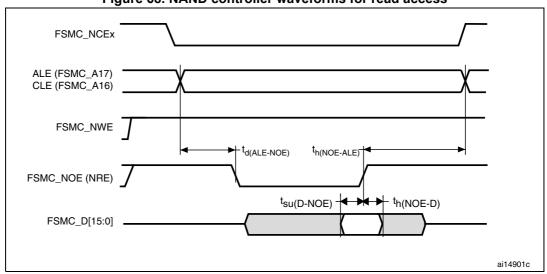

Figure 68. NAND controller waveforms for read access

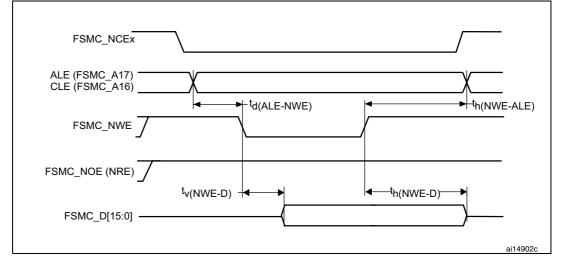

Figure 69. NAND controller waveforms for write access

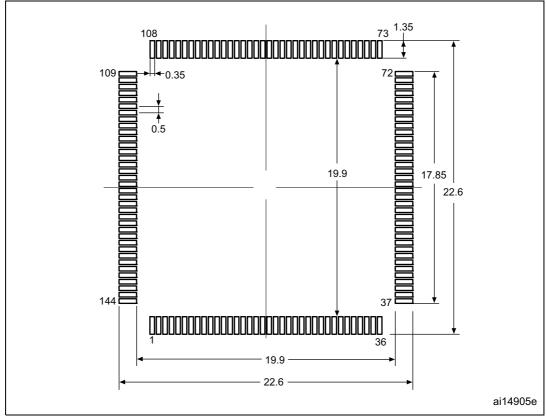

1. Dimensions are in millimeters.

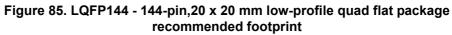

Figure 91. LQFP176 - 176-pin, 24 x 24 mm low profile quad flat recommended footprint

1. Dimensions are expressed in millimeters.

## Appendix A Application block diagrams

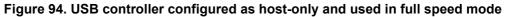

## A.1 USB OTG full speed (FS) interface solutions

Figure 93. USB controller configured as peripheral-only and used in Full speed mode

1. External voltage regulator only needed when building a  $V_{\text{BUS}}$  powered device.

2. The same application can be developed using the OTG HS in FS mode to achieve enhanced performance thanks to the large Rx/Tx FIFO and to a dedicated DMA controller.

The current limiter is required only if the application has to support a V<sub>BUS</sub> powered device. A basic power switch can be used if 5 V are available on the application board.

2. The same application can be developed using the OTG HS in FS mode to achieve enhanced performance thanks to the large Rx/Tx FIFO and to a dedicated DMA controller.

## A.3 Ethernet interface solutions

1.  $f_{HCLK}$  must be greater than 25 MHz.

2. Pulse per second when using IEEE1588 PTP optional signal.

#### Figure 98. RMII with a 50 MHz oscillator

1. f<sub>HCLK</sub> must be greater than 25 MHz.

## 8 Revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-Sep-2011 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 24-Jan-2012 | 2        | Added WLCSP90 package on cover page.<br>Renamed USART4 and USART5 into UART4 and UART5,<br>respectively.<br>Updated number of USB OTG HS and FS in <i>Table 2: STM32F405xx</i><br>and <i>STM32F407xx: features and peripheral counts.</i><br>Updated <i>Figure 3: Compatible board design between</i><br><i>STM32F10xx/STM32F2/STM32F40xxx for LQFP144 package</i> and<br><i>Figure 4: Compatible board design between STM32F2 and</i><br><i>STM32F40xxx for LQFP176 and BGA176 packages,</i> and removed<br>note 1 and 2.<br>Updated <i>Section 2.2.9: Flexible static memory controller (FSMC).</i><br>Modified I/Os used to reprogram the Flash memory for CAN2 and<br>USB OTG FS in <i>Section 2.2.13: Boot modes.</i><br>Updated note in <i>Section 2.2.14: Power supply schemes.</i><br>PDR_ON no more available on LQFP100 package. Updated<br><i>Section 2.2.16: Voltage regulator.</i> Updated condition to obtain a<br>minimum supply voltage of 1.7 V in the whole document.<br>Renamed USART4/5 to UART4/5 and added LIN and IrDA feature for<br>UART4 and UART5 in <i>Table 5: USART feature comparison.</i><br>Removed support of I2C for OTG PHY in <i>Section 2.2.30: Universal</i><br><i>serial bus on-the-go full-speed (OTG_FS).</i><br>Added <i>Table 6: Legend/abbreviations used in the pinout table.</i><br><i>Table 7: STM32F40xxx pin and ball definitions:</i> replaced V <sub>SS_3</sub> ,<br>V <sub>SS_4</sub> , and V <sub>SS_8</sub> by V <sub>SS</sub> : reformatted <i>Table 7: STM32F40xxx pin and</i><br><i>ball definitions</i> to better highlight I/O structure, and alternate functions<br>versus additional functions; signal corresponding to LQFP100 pin 99<br>changed from PDR_ON to V <sub>SS</sub> : EVENTOUT added in the list of<br>alternate functions for all I/OS; ADC3_IN8 added as alternate function<br>for PD11 and PD12, respectively; PH10 alternate function<br><i>TIM15_CH1_ETR</i> renamed TIM5_CH1; updated PA4 and PA5 I/O<br>structure to TTa.<br>Removed OTG_HS_SCL, OTG_HS_SDA, OTG_FS_INTN in <i>Table 7:</i><br><i>STM32F40xxx pin and ball definitions</i> and <i>Table 9: Alternate function</i><br><i>mapping.</i><br>Changed TCM data RAM to CCM data RAM in <i>Figure 18:</i><br><i>STM32F40xxx pin and ball definitions</i> and <i>Table 9: Alternate function</i><br><i>mapping.</i><br>Changed TCM data RAM to CCM data |

### Table 100. Document revision history

| Date                | Revision                     | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|---------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Date<br>24-Jan-2012 | Revision<br>2<br>(continued) | Changes         Added V <sub>12</sub> in Table 19: Embedded reset and power control block characteristics.         Updated Table 21: Typical and maximum current consumption in Run mode, code with data processing running from Flash memory (ART accelerator disabled) and Table 20: Typical and maximum current consumption in Run mode, code with data processing running from Flash memory (ART accelerator enabled) or RAM. Added Figure , Figure 25, Figure 26, and Figure 27.         Updated Table 22: Typical and maximum current consumption in Sleep mode and removed Note 1.         Updated Table 23: Typical and maximum current consumptions in Stop mode and Table 24: Typical and maximum current consumptions in Stop mode and Table 25: Typical and maximum current consumptions in Standby mode, Table 25: Typical and maximum current consumptions in Standby mode, Table 25: Typical and maximum current consumptions in Standby mode, and Table 27: Switching output I/O current consumption.         Section : On-chip peripheral current consumption: modified conditions, and updated Table 28: Peripheral current consumption and Note 2.         Changed f <sub>HSE_ext</sub> to 50 MHz and t <sub>r(HSE)</sub> /t <sub>f(HSE)</sub> maximum value in Table 30: High-speed external user clock characteristics.         Added C <sub>in(LSE)</sub> in Table 31: Low-speed external user clock characteristics.         Updated maximum PLL input clock frequency, removed related note, and deleted jitter for MCO for RMII Ethernet typical value in Table 36: Main PLL characteristics. Updated maximum PLLI2S input clock frequency and removed related note in Table 37: PLLI2S (audio PLL) characteristics.         Updated Section : Flash memory to specify that the devices are shipped to customers with the Flash memory erased. Updated Table 39: Fl |  |

Table 100. Document revision history (continued)