# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                    |

|----------------------------|-------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                           |

| Core Size                  | 32-Bit Single-Core                                                                        |

| Speed                      | 168MHz                                                                                    |

| Connectivity               | CANbus, DCMI, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                         |

| Number of I/O              | 82                                                                                        |

| Program Memory Size        | 1MB (1M x 8)                                                                              |

| Program Memory Type        | FLASH                                                                                     |

| EEPROM Size                | -                                                                                         |

| RAM Size                   | 192K × 8                                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                               |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                                     |

| Oscillator Type            | Internal                                                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                        |

| Mounting Type              | Surface Mount                                                                             |

| Package / Case             | 100-LQFP                                                                                  |

| Supplier Device Package    | 100-LQFP (14x14)                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f407vgt7                     |

|                            |                                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2 Description

The STM32F405xx and STM32F407xx family is based on the high-performance ARM<sup>®</sup> Cortex<sup>®</sup>-M4 32-bit RISC core operating at a frequency of up to 168 MHz. The Cortex-M4 core features a Floating point unit (FPU) single precision which supports all ARM single-precision data-processing instructions and data types. It also implements a full set of DSP instructions and a memory protection unit (MPU) which enhances application security.

The STM32F405xx and STM32F407xx family incorporates high-speed embedded memories (Flash memory up to 1 Mbyte, up to 192 Kbytes of SRAM), up to 4 Kbytes of backup SRAM, and an extensive range of enhanced I/Os and peripherals connected to two APB buses, three AHB buses and a 32-bit multi-AHB bus matrix.

All devices offer three 12-bit ADCs, two DACs, a low-power RTC, twelve general-purpose 16-bit timers including two PWM timers for motor control, two general-purpose 32-bit timers. a true random number generator (RNG). They also feature standard and advanced communication interfaces.

- Up to three I<sup>2</sup>Cs

- Three SPIs, two I<sup>2</sup>Ss full duplex. To achieve audio class accuracy, the I2S peripherals can be clocked via a dedicated internal audio PLL or via an external clock to allow synchronization.

- Four USARTs plus two UARTs

- An USB OTG full-speed and a USB OTG high-speed with full-speed capability (with the ULPI),

- Two CANs

- An SDIO/MMC interface

- Ethernet and the camera interface available on STM32F407xx devices only.

New advanced peripherals include an SDIO, an enhanced flexible static memory control (FSMC) interface (for devices offered in packages of 100 pins and more), a camera interface for CMOS sensors. Refer to *Table 2: STM32F405xx and STM32F407xx: features and peripheral counts* for the list of peripherals available on each part number.

The STM32F405xx and STM32F407xx family operates in the –40 to +105 °C temperature range from a 1.8 to 3.6 V power supply. The supply voltage can drop to 1.7 V when the device operates in the 0 to 70 °C temperature range using an external power supply supervisor: refer to *Section : Internal reset OFF*. A comprehensive set of power-saving mode allows the design of low-power applications.

The STM32F405xx and STM32F407xx family offers devices in various packages ranging from 64 pins to 176 pins. The set of included peripherals changes with the device chosen.

These features make the STM32F405xx and STM32F407xx microcontroller family suitable for a wide range of applications:

- Motor drive and application control

- Medical equipment

- Industrial applications: PLC, inverters, circuit breakers

- Printers, and scanners

- Alarm systems, video intercom, and HVAC

- Home audio appliances

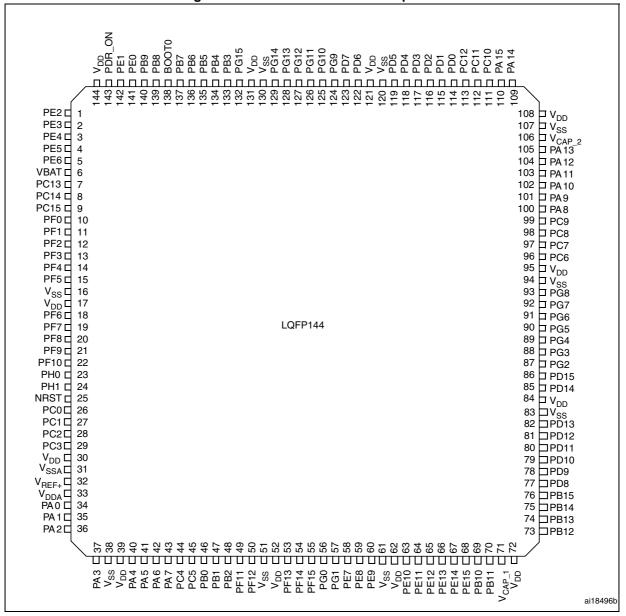

Figure 14. STM32F40xxx LQFP144 pinout

1. The above figure shows the package top view.

|   | 1     | 2    | 3    | 4              | 5   | 6      | 7    | 8    | 9    | 10     | 11   | 12   | 13     | 14   | 15       |

|---|-------|------|------|----------------|-----|--------|------|------|------|--------|------|------|--------|------|----------|

| А | PE3   | PE2  | PE1  | PE0            | PB8 | PB5    | PG14 | PG13 | PB4  | PB3    | PD7  | PC12 | PA15   | PA14 | PA13     |

| В | PE4   | PE5  | PE6  | PB9            | PB7 | PB6    | PG15 | PG12 | PG11 | PG10   | PD6  | PD0  | PC11   | PC10 | PA12     |

| с | VBAT  | PI7  | PI6  | PI5            | VDD | PDR_ON | VDD  | VDD  | VDD  | PG9    | PD5  | PD1  | PI3    | Pl2  | PA11     |

| D | PC13  | PI8  | PI9  | Pl4            | VSS | BOOT0  | VSS  | VSS  | VSS  | PD4    | PD3  | PD2  | PH15   | PI1  | PA10     |

| E | PC14  | PF0  | PI10 | PI11           |     |        |      |      |      |        |      | PH13 | PH14   | P10  | PA 9     |

| F | PC15  | VSS  | VDD  | PH2            |     | VSS    | VSS  | VSS  | VSS  | VSS    |      | VSS  | VCAP_2 | PC9  | PA 8     |

| G | PH0   | VSS  | VDD  | PH3            |     | VSS    | VSS  | VSS  | VSS  | VSS    |      | VSS  | VDD    | PC8  | PC7      |

| н | PH1   | PF2  | PF1  | PH4            |     | VSS    | VSS  | VSS  | VSS  | VSS    |      | VSS  | VDD    | PG8  | PC6      |

| J | NRST  | PF3  | PF4  | PH5            |     | VSS    | VSS  | VSS  | VSS  | VSS    |      | VDD  | VDD    | PG7  | PG6      |

| к | PF7   | PF6  | PF5  | VDD            |     | VSS    | VSS  | VSS  | VSS  | VSS    |      | PH12 | PG5    | PG4  | PG3      |

| L | PF10  | PF9  | PF8  | BYPASS_<br>REG |     |        |      |      |      |        |      | PH11 | PH10   | PD15 | PG2      |

| М | VSSA  | PC0  | PC1  | PC2            | PC3 | PB2    | PG1  | VSS  | VSS  | VCAP_1 | PH6  | PH8  | PH9    | PD14 | PD13     |

| Ν | VREF- | PA 1 | PA0  | PA4            | PC4 | PF13   | PG0  | VDD  | VDD  | VDD    | PE13 | PH7  | PD12   | PD11 | PD10     |

| Ρ | VREF+ | PA2  | PA6  | PA5            | PC5 | PF12   | PF15 | PE8  | PE9  | PE11   | PE14 | PB12 | PB13   | PD9  | PD8      |

| R | VDDA  | PA3  | PA7  | PB1            | PB0 | PF11   | PF14 | PE7  | PE10 | PE12   | PE15 | PB10 | PB11   | PB14 | PB15     |

|   |       |      |      |                |     |        |      |      |      |        |      |      |        |      | ai18497b |

Figure 16. STM32F40xxx UFBGA176 ballout

1. This figure shows the package top view.

|   |      | •              |        |       |      |      |        |      |      |        |

|---|------|----------------|--------|-------|------|------|--------|------|------|--------|

|   | 10   | 9              | 8      | 7     | 6    | 5    | 4      | 3    | 2    | 1      |

| A | VBAT | PC13           | PDR_ON | BOOT0 | PB4  | PD7  | PD4    | PC12 | PA14 | VDD    |

| В | PC14 | PC15           | VDD    | PB7   | PB3  | PD6  | PD2    | PA15 | PI1  | VCAP_2 |

| С | PA0  | vss            | PB9    | PB6   | PD5  | PD1  | PC11   | PI0  | PA12 | PA11   |

| D | PC2  | BYPASS_<br>REG | PB8    | PB5   | PD0  | PC10 | PA13   | PA10 | PA9  | PA8    |

| E | PC0  | PC3            | vss    | VSS   | VDD  | VSS  | VDD    | PC9  | PC8  | PC7    |

| F | PH0  | PH1            | PA1    | VDD   | PE10 | PE14 | VCAP_1 | PC6  | PD14 | PD15   |

| G | NRST | VDDA           | PA5    | PB0   | PE7  | PE13 | PE15   | PD10 | PD12 | PD11   |

| н | VSSA | PA3            | PA6    | PB1   | PE8  | PE12 | PB10   | PD9  | PD8  | PB15   |

| J | PA2  | PA4            | PA7    | PB2   | PE9  | PE11 | PB11   | PB12 | PB14 | PB13   |

|   | •    | :              | •      |       |      | 1    | 1      |      | :    |        |

Figure 17. STM32F40xxx WLCSP90 ballout

1. This figure shows the package bump view.

| Table 6. Legend/abbreviations used in the | pinout table |

|-------------------------------------------|--------------|

|-------------------------------------------|--------------|

| Name                   | Abbreviation          | Definition                                                                                         |  |  |  |  |  |

|------------------------|-----------------------|----------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Pin name               |                       | specified in brackets below the pin name, the pin function during and after as the actual pin name |  |  |  |  |  |

|                        | S                     | Supply pin                                                                                         |  |  |  |  |  |

| Pin type               | I Input only pin      |                                                                                                    |  |  |  |  |  |

|                        | I/O                   | Input / output pin                                                                                 |  |  |  |  |  |

|                        | FT                    | 5 V tolerant I/O                                                                                   |  |  |  |  |  |

|                        | ТТа                   | 3.3 V tolerant I/O directly connected to ADC                                                       |  |  |  |  |  |

| I/O structure          | B Dedicated BOOT0 pin |                                                                                                    |  |  |  |  |  |

|                        | RST                   | Bidirectional reset pin with embedded weak pull-up resistor                                        |  |  |  |  |  |

| Notes                  | Unless otherwise      | specified by a note, all I/Os are set as floating inputs during and after reset                    |  |  |  |  |  |

| Alternate<br>functions | Functions selected    | d through GPIOx_AFR registers                                                                      |  |  |  |  |  |

| Additional functions   | Functions directly    | selected/enabled through peripheral registers                                                      |  |  |  |  |  |

|        | F       | Pin r   | numb    |          |         |                                                      |            |                 |                                                            | definitions (continued)                                                           |                         |

|--------|---------|---------|---------|----------|---------|------------------------------------------------------|------------|-----------------|------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------|

| LQFP64 | WLCSP90 | LQFP100 | LQFP144 | UFBGA176 | LQFP176 | Pin name<br>(function after<br>reset) <sup>(1)</sup> | Pin type   | I / O structure | Notes                                                      | Alternate functions                                                               | Additional<br>functions |

| -      | -       | -       | -       | C14      | 133     | PI2                                                  |            |                 | TIM8_CH4 /SPI2_MISO /<br>DCMI_D9 / I2S2ext_SD/<br>EVENTOUT | -                                                                                 |                         |

| -      | _       | -       | I       | C13      | 134     | PI3                                                  | I/O        | FT              |                                                            | TIM8_ETR / SPI2_MOSI /<br>I2S2_SD / DCMI_D10/<br>EVENTOUT                         | -                       |

| -      | -       | -       | -       | D9       | 135     | V <sub>SS</sub>                                      | S          | -               | -                                                          | -                                                                                 | _                       |

| -      | -       | -       | -       | C9       | 136     | V <sub>DD</sub>                                      | S          | -               | -                                                          | -                                                                                 | -                       |

| 49     | A2      | 76      | 109     | A14      | 137     | PA14<br>(JTCK/SWCLK)                                 | I/O        | FT              | -                                                          | JTCK-SWCLK/ EVENTOUT                                                              | -                       |

| 50     | В3      | 77      | 110     | A13      | 138     | PA15<br>(JTDI)                                       | I/O        | FT              | -                                                          | JTDI/ SPI3_NSS/<br>I2S3_WS/TIM2_CH1_ETR<br>/ SPI1_NSS / EVENTOUT                  | _                       |

| 51     | D5      | 78      | 111     | B14      | 139     | PC10                                                 | I/O        | FT              | -                                                          | SPI3_SCK / I2S3_CK/<br>UART4_TX/SDIO_D2 /<br>DCMI_D8 / USART3_TX/<br>EVENTOUT     | -                       |

| 52     | C4      | 79      | 112     | B13      | 140     | PC11                                                 | I/O        | FT              | -                                                          | UART4_RX/ SPI3_MISO /<br>SDIO_D3 /<br>DCMI_D4/USART3_RX /<br>I2S3ext_SD/ EVENTOUT | -                       |

| 53     | A3      | 80      | 113     | A12      | 141     | PC12                                                 | I/O        | FT              | -                                                          | UART5_TX/SDIO_CK /<br>DCMI_D9 / SPI3_MOSI<br>/I2S3_SD / USART3_CK/<br>EVENTOUT    | -                       |

| -      | D6      | 81      | 114     | B12      | 142     | PD0                                                  | I/O        | FT              | -                                                          | FSMC_D2/CAN1_RX/<br>EVENTOUT                                                      | -                       |

| -      | C5      | 82      | 115     | C12      | 143     | PD1                                                  | I/O        | FT              | -                                                          | FSMC_D3 / CAN1_TX/<br>EVENTOUT                                                    | -                       |

| 54     | B4      | 83      | 116     | D12      | 144     | PD2                                                  | . I/O FT - |                 | -                                                          | TIM3_ETR/UART5_RX/<br>SDIO_CMD / DCMI_D11/<br>EVENTOUT                            | -                       |

| -      | -       | 84      | 117     | D11      | 145     | PD3                                                  | FSMC_CLK/  |                 | USART2_CTS/                                                | -                                                                                 |                         |

|        |      |                |                        |           |                  |               | Table                          | 9. Alterr            | nate funct             | ion ma             | pping                     |                    |                                           |                      |                |      |          |

|--------|------|----------------|------------------------|-----------|------------------|---------------|--------------------------------|----------------------|------------------------|--------------------|---------------------------|--------------------|-------------------------------------------|----------------------|----------------|------|----------|

|        |      | AF0            | AF1                    | AF2       | AF3              | AF4           | AF5                            | AF6                  | AF7                    | AF8                | AF9                       | AF10               | AF11                                      | AF12                 | AF13           |      |          |

| Po     | ort  | SYS            | TIM1/2                 | TIM3/4/5  | TIM8/9/10<br>/11 | I2C1/2/3      | SPI1/SPI2/<br>I2S2/I2S2e<br>xt | SPI3/I2Sext<br>/I2S3 | USART1/2/3/<br>I2S3ext | UART4/5/<br>USART6 | CAN1/2<br>TIM12/13/<br>14 | OTG_FS/<br>OTG_HS  | ETH                                       | FSMC/SDIO<br>/OTG_FS | DCMI           | AF14 | AF15     |

|        | PA0  | -              | TIM2_CH1_<br>ETR       | TIM 5_CH1 | TIM8_ETR         | -             | -                              | -                    | USART2_CTS             | UART4_TX           | -                         | -                  | ETH_MII_CRS                               | -                    | -              | -    | EVENTOUT |

|        | PA1  | -              | TIM2_CH2               | TIM5_CH2  | -                | -             | -                              | -                    | USART2_RTS             | UART4_RX           | -                         | -                  | ETH_MII<br>_RX_CLK<br>ETH_RMIIREF<br>_CLK | -                    | -              | -    | EVENTOUT |

|        | PA2  | -              | TIM2_CH3               | TIM5_CH3  | TIM9_CH1         | -             | -                              | -                    | USART2_TX              | -                  | -                         | -                  | ETH_MDIO                                  | -                    | -              | -    | EVENTOUT |

|        | PA3  | -              | TIM2_CH4               | TIM5_CH4  | TIM9_CH2         | -             | -                              | -                    | USART2_RX              | -                  | -                         | OTG_HS_ULPI_<br>D0 | ETH _MII_COL                              | -                    | -              | -    | EVENTOUT |

|        | PA4  | -              | -                      | -         | -                | -             | SPI1_NSS                       | SPI3_NSS<br>I2S3_WS  | USART2_CK              | -                  | -                         | -                  | -                                         | OTG_HS_SOF           | DCMI_<br>HSYNC | -    | EVENTOUT |

|        | PA5  | -              | TIM2_CH1_<br>ETR       | -         | TIM8_CH1N        | -             | SPI1_SCK                       | -                    | -                      | -                  | -                         | OTG_HS_ULPI_<br>CK | -                                         | -                    | -              | -    | EVENTOUT |

|        | PA6  | -              | TIM1_BKIN              | TIM3_CH1  | TIM8_BKIN        | -             | SPI1_MISO                      | -                    | -                      | -                  | TIM13_CH1                 | -                  | -                                         | -                    | DCMI_PIXCK     | -    | EVENTOUT |

| Port A | PA7  | -              | TIM1_CH1N              | TIM3_CH2  | TIM8_CH1N        | -             | SPI1_MOSI                      | -                    | -                      | -                  | TIM14_CH1                 | -                  | ETH_MII_RX_DV<br>ETH_RMII<br>_CRS_DV      | -                    | -              | -    | EVENTOUT |

|        | PA8  | MCO1           | TIM1_CH1               | -         | -                | I2C3_SCL      | -                              | -                    | USART1_CK              | -                  | -                         | OTG_FS_SOF         | -                                         | -                    | -              | -    | EVENTOUT |

|        | PA9  | -              | TIM1_CH2               | -         | -                | I2C3_<br>SMBA | -                              | -                    | USART1_TX              | -                  | -                         | -                  | -                                         | -                    | DCMI_D0        | -    | EVENTOUT |

|        | PA10 | -              | TIM1_CH3               | -         | -                | -             | -                              | -                    | USART1_RX              | -                  | -                         | OTG_FS_ID          | -                                         | -                    | DCMI_D1        | -    | EVENTOUT |

|        | PA11 | -              | TIM1_CH4               | -         | -                | -             | -                              | -                    | USART1_CTS             | -                  | CAN1_RX                   | OTG_FS_DM          | -                                         | -                    | -              | -    | EVENTOUT |

|        | PA12 | -              | TIM1_ETR               | -         | -                | -             | -                              | -                    | USART1_RTS             | -                  | CAN1_TX                   | OTG_FS_DP          | -                                         | -                    | -              | -    | EVENTOUT |

|        | PA13 | JTMS-<br>SWDIO | -                      | -         | -                | -             | -                              | -                    | -                      | -                  | -                         | -                  | -                                         | -                    | -              | -    | EVENTOUT |

|        | PA14 | JTCK-<br>SWCLK | -                      | -         | -                | -             | -                              | -                    | -                      | -                  | -                         | -                  | -                                         | -                    | -              | -    | EVENTOUT |

|        | PA15 | JTDI           | TIM 2_CH1<br>TIM 2_ETR | -         | -                | -             | SPI1_NSS                       | SPI3_NSS/<br>I2S3_WS | -                      | -                  | -                         | -                  | -                                         | -                    | -              | -    | EVENTOUT |

DocID022152 Rev 8

5

62/202

STM32F405xx, STM32F407xx

Pinouts and pin description

67/202

DocID022152 Rev 8

|         |      |     |        |          |                  | Tab           | ole 9. Alt                     | ernate fi            | unction m              | apping             | (contin                   | ued)              |      |                      |          |      |          |

|---------|------|-----|--------|----------|------------------|---------------|--------------------------------|----------------------|------------------------|--------------------|---------------------------|-------------------|------|----------------------|----------|------|----------|

|         |      | AF0 | AF1    | AF2      | AF3              | AF4           | AF5                            | AF6                  | AF7                    | AF8                | AF9                       | AF10              | AF11 | AF12                 | AF13     |      |          |

| P       | ort  | SYS | TIM1/2 | TIM3/4/5 | TIM8/9/10<br>/11 | I2C1/2/3      | SPI1/SPI2/<br>I2S2/I2S2e<br>xt | SPI3/I2Sext<br>/I2S3 | USART1/2/3/<br>I2S3ext | UART4/5/<br>USART6 | CAN1/2<br>TIM12/13/<br>14 | OTG_FS/<br>OTG_HS | ETH  | FSMC/SDIO<br>/OTG_FS | DCMI     | AF14 | AF15     |

|         | PF0  | -   | -      | -        | -                | I2C2_SDA      | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A0              | -        | -    | EVENTOUT |

|         | PF1  | -   | -      | -        | -                | I2C2_SCL      | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A1              | -        | -    | EVENTOUT |

|         | PF2  | -   | -      | -        | -                | I2C2_<br>SMBA | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A2              | -        | -    | EVENTOUT |

|         | PF3  | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A3              | -        | -    | EVENTOUT |

|         | PF4  | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A4              | -        | -    | EVENTOUT |

|         | PF5  | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A5              | -        | -    | EVENTOUT |

|         | PF6  | -   | -      | -        | TIM10_CH1        | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_NIORD           | -        | -    | EVENTOUT |

| Port F  | PF7  | -   | -      | -        | TIM11_CH1        | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_NREG            | -        | -    | EVENTOUT |

| T OIL I | PF8  | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | TIM13_CH1                 | -                 | -    | FSMC_<br>NIOWR       | -        | -    | EVENTOUT |

|         | PF9  | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | TIM14_CH1                 | -                 | -    | FSMC_CD              | -        | -    | EVENTOUT |

|         | PF10 | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_INTR            | -        | -    | EVENTOUT |

|         | PF11 | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    |                      | DCMI_D12 | -    | EVENTOUT |

|         | PF12 | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A6              | -        | -    | EVENTOUT |

|         | PF13 | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A7              | -        | -    | EVENTOUT |

|         | PF14 | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A8              | -        | -    | EVENTOUT |

|         | PF15 | -   | -      | -        | -                | -             | -                              | -                    | -                      | -                  | -                         | -                 | -    | FSMC_A9              | -        | -    | EVENTOUT |

Pinouts and pin description

5

| Symbol                               | Ratings                                                                 | Max.  | Unit |

|--------------------------------------|-------------------------------------------------------------------------|-------|------|

| I <sub>VDD</sub>                     | Total current into V <sub>DD</sub> power lines (source) <sup>(1)</sup>  | 240   |      |

| I <sub>VSS</sub>                     | Total current out of $V_{SS}$ ground lines (sink) <sup>(1)</sup>        | 240   |      |

| I                                    | Output current sunk by any I/O and control pin                          | 25    |      |

| I <sub>IO</sub>                      | Output current source by any I/Os and control pin                       | 25    | mA   |

| ı (2)                                | Injected current on five-volt tolerant I/O <sup>(3)</sup>               | -5/+0 |      |

| I <sub>INJ(PIN)</sub> <sup>(2)</sup> | Injected current on any other pin <sup>(4)</sup>                        | ±5    |      |

| $\Sigma I_{\rm INJ(PIN)}^{(4)}$      | Total injected current (sum of all I/O and control pins) <sup>(5)</sup> | ±25   |      |

#### Table 12. Current characteristics

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

2. Negative injection disturbs the analog performance of the device. See note in Section 5.3.21: 12-bit ADC characteristics.

3. Positive injection is not possible on these I/Os. A negative injection is induced by  $V_{IN} < V_{SS}$ .  $I_{INJ(PIN)}$  must never be exceeded. Refer to *Table 11* for the values of the maximum allowed input voltage.

4. A positive injection is induced by  $V_{IN}$  >  $V_{DD}$  while a negative injection is induced by  $V_{IN}$  <  $V_{SS}$ .  $I_{INJ(PIN)}$  must never be exceeded. Refer to *Table 11* for the values of the maximum allowed input voltage.

5. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values).

#### Table 13. Thermal characteristics

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | –65 to +150 | °C   |

| TJ               | Maximum junction temperature | 125         | °C   |

### 5.3 Operating conditions

### 5.3.1 General operating conditions

#### Table 14. General operating conditions

| Symbol                             | Parameter                                                  | Conditions                             | Min                | Тур | Max | Unit |

|------------------------------------|------------------------------------------------------------|----------------------------------------|--------------------|-----|-----|------|

| f                                  | Internal AHB clock frequency                               | VOS bit in PWR_CR register = $0^{(1)}$ | 0                  | -   | 144 |      |

| f <sub>HCLK</sub>                  | Internal AITE Clock frequency                              | VOS bit in PWR_CR register= 1          | 0                  | -   | 168 | MHz  |

| f <sub>PCLK1</sub>                 | Internal APB1 clock frequency                              | -                                      | 0                  | -   | 42  |      |

| f <sub>PCLK2</sub>                 | Internal APB2 clock frequency                              | -                                      | 0                  | -   | 84  |      |

| V <sub>DD</sub>                    | Standard operating voltage                                 | -                                      | 1.8 <sup>(2)</sup> | -   | 3.6 | V    |

| V <sub>DDA</sub> <sup>(3)(4)</sup> | Analog operating voltage<br>(ADC limited to 1.2 M samples) | Must be the same potential as          | 1.8 <sup>(2)</sup> | -   | 2.4 | V    |

| *DDA````                           | Analog operating voltage<br>(ADC limited to 1.4 M samples) | V <sub>DD</sub> <sup>(5)</sup>         | 2.4                | -   | 3.6 | v    |

| V <sub>BAT</sub>                   | Backup operating voltage                                   | -                                      | 1.65               | -   | 3.6 | V    |

|                         |                      | I <sub>DD</sub> (1       | Гур) <sup>(1)</sup>       |        |

|-------------------------|----------------------|--------------------------|---------------------------|--------|

| Perip                   | bheral               | Scale1<br>(up t 168 MHz) | Scale2<br>(up to 144 MHz) | Unit   |

|                         | OTG_FS               | 26.45                    | 26.67                     |        |

| AHB2<br>(up to 168 MHz) | DCMI                 | 5.87                     | 5.35                      | μA/MHz |

| (up to 168 MHz)         | RNG                  | 1.50                     | 1.67                      |        |

| AHB3<br>(up to 168 MHz) | FSMC                 | 12.46                    | 11.31                     | µA/MHz |

| Bus m                   | atrix <sup>(2)</sup> | 13.10                    | 11.81                     | µA/MHz |

|                         | TIM2                 | 16.71                    | 16.50                     |        |

|                         | TIM3                 | 12.33                    | 11.94                     |        |

|                         | TIM4                 | 13.45                    | 12.92                     |        |

|                         | TIM5                 | 17.14                    | 16.58                     |        |

|                         | TIM6                 | 2.43                     | 3.06                      |        |

|                         | TIM7                 | 2.43                     | 2.22                      |        |

|                         | TIM12                | 6.62                     | 6.83                      |        |

|                         | TIM13                | 5.05                     | 5.47                      |        |

|                         | TIM14                | 5.26                     | 5.61                      |        |

|                         | PWR                  | 1.00                     | 0.56                      |        |

|                         | USART2               | 2.69                     | 2.78                      |        |

|                         | USART3               | 2.74                     | 2.78                      |        |

| APB1<br>(up to 42 MHz)  | UART4                | 3.24                     | 3.33                      | µA/MH: |

|                         | UART5                | 2.69                     | 2.78                      |        |

|                         | I2C1                 | 2.67                     | 2.50                      |        |

|                         | I2C2                 | 2.83                     | 2.78                      |        |

|                         | I2C3                 | 2.81                     | 2.78                      |        |

|                         | SPI2                 | 2.43                     | 2.22                      |        |

|                         | SPI3                 | 2.43                     | 2.22                      |        |

|                         | I2S2 <sup>(3)</sup>  | 2.43                     | 2.22                      |        |

|                         | I2S3 <sup>(3)</sup>  | 2.26                     | 2.22                      |        |

|                         | CAN1                 | 5.12                     | 5.56                      |        |

|                         | CAN2                 | 4.81                     | 5.28                      |        |

|                         | DAC <sup>(4)</sup>   | 1.67                     | 1.67                      |        |

|                         | WWDG                 | 1.00                     | 0.83                      | 1      |

Table 28. Peripheral current consumption (continued)

A device reset allows normal operations to be resumed.

The test results are given in *Table 43*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                              | Level/<br>Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | V <sub>DD</sub> = 3.3 V, LQFP176, T <sub>A</sub> =<br>+25 °C, f <sub>HCLK</sub> = 168 MHz, conforms<br>to IEC 61000-4-2 | 2B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | V <sub>DD</sub> = 3.3 V, LQFP176, T <sub>A</sub> =<br>+25 °C, f <sub>HCLK</sub> = 168 MHz, conforms<br>to IEC 61000-4-2 | 4A              |

#### Table 43. EMS characteristics

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

#### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

#### Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 37* and *Table 50*, respectively.

Unless otherwise specified, the parameters given in *Table 50* are derived from tests performed under the ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

| OSPEEDRy<br>[1:0] bit<br>value <sup>(1)</sup> | Symbol                                           | Parameter                                                                       | Conditions                                                  | Min | Тур | Мах                | Unit |

|-----------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------|-----|-----|--------------------|------|

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD &gt;</sub> 2.70 V         | -   | -   | 4                  |      |

|                                               | f                                                | Maximum frequency <sup>(3)</sup>                                                | C <sub>L</sub> = 50 pF, V <sub>DD &gt;</sub> 1.8 V          | -   | -   | 2                  | MHz  |

|                                               | 'max(IO)out                                      |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 2.70 V         | -   | -   | 8                  |      |

| 00                                            |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 1.8 V          | -   | -   | 4                  |      |

|                                               | t <sub>f(IO)out</sub> /<br>t <sub>r(IO)out</sub> | Output high to low level fall<br>time and output low to high<br>level rise time | C <sub>L</sub> = 50 pF, V <sub>DD</sub> = 1.8 V to<br>3.6 V | -   | -   | 100                | ns   |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD &gt;</sub> 2.70 V         | -   | -   | 25                 |      |

|                                               | f <sub>max(IO)out</sub>                          | <sub>ux(IO)out</sub> Maximum frequency <sup>(3)</sup>                           | C <sub>L</sub> = 50 pF, V <sub>DD &gt;</sub> 1.8 V          | -   | -   | 12.5               | MHz  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 2.70 V         | -   | -   | 50 <sup>(4)</sup>  |      |

| 01                                            |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 1.8 V          | -   | -   | 20                 |      |

| 01                                            |                                                  |                                                                                 | C <sub>L</sub> = 50 pF, V <sub>DD</sub> >2.7 V              | -   | -   | 10                 |      |

|                                               | t <sub>f(IO)out</sub> /                          | Output high to low level fall time and output low to high                       | C <sub>L</sub> = 50 pF, V <sub>DD</sub> > 1.8 V             | -   | -   | 20                 | ns   |

|                                               | t <sub>r(IO)out</sub>                            |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 2.70 V         | -   | -   | 6                  | 115  |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 1.8 V          | -   | -   | 10                 |      |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 40 pF, V <sub>DD &gt;</sub> 2.70 V         | -   | -   | 50 <sup>(4)</sup>  |      |

|                                               | f                                                | Maximum fraguana $u^{(3)}$                                                      | C <sub>L</sub> = 40 pF, V <sub>DD &gt;</sub> 1.8 V          | -   | -   | 25                 | MHz  |

|                                               | Imax(IO)out                                      | Maximum frequency <sup>(3)</sup>                                                | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 2.70 V         | -   | -   | 100 <sup>(4)</sup> |      |

| 10                                            |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 1.8 V          | -   | -   | 50 <sup>(4)</sup>  |      |

| 10                                            |                                                  |                                                                                 | C <sub>L</sub> = 40 pF, V <sub>DD &gt;</sub> 2.70 V         | -   | -   | 6                  |      |

|                                               | t <sub>f(IO)out</sub> /                          | Output high to low level fall time and output low to high                       | C <sub>L</sub> = 40 pF, V <sub>DD &gt;</sub> 1.8 V          | -   | -   | 10                 |      |

|                                               | t <sub>r(IO)out</sub>                            | level rise time                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 2.70 V         | -   | -   | 4                  | ns   |

|                                               |                                                  |                                                                                 | C <sub>L</sub> = 10 pF, V <sub>DD &gt;</sub> 1.8 V          | -   | -   | 6                  |      |

Table 50. I/O AC characteristics<sup>(1)(2)</sup>

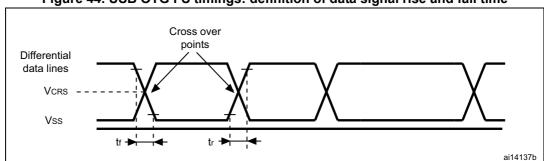

#### Figure 44. USB OTG FS timings: definition of data signal rise and fall time

#### Table 59. USB OTG FS electrical characteristics<sup>(1)</sup>

|                  | Driver o                        | haracteristics                 |     |     |      |

|------------------|---------------------------------|--------------------------------|-----|-----|------|

| Symbol           | Parameter                       | Conditions                     | Min | Max | Unit |

| t <sub>r</sub>   | Rise time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |

| t <sub>f</sub>   | Fall time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF         | 4   | 20  | ns   |

| t <sub>rfm</sub> | Rise/ fall time matching        | t <sub>r</sub> /t <sub>f</sub> | 90  | 110 | %    |

| V <sub>CRS</sub> | Output signal crossover voltage | -                              | 1.3 | 2.0 | V    |

1. Guaranteed by design.

2. Measured from 10% to 90% of the data signal. For more detailed informations, please refer to USB Specification - Chapter 7 (version 2.0).

#### **USB HS characteristics**

Unless otherwise specified, the parameters given in *Table 62* for ULPI are derived from tests performed under the ambient temperature,  $f_{HCLK}$  frequency summarized in *Table 61* and  $V_{DD}$  supply voltage conditions summarized in *Table 60*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>.

Refer to Section Section 5.3.16: I/O port characteristics for more details on the input/output characteristics.

|             | Iu              |                              | chistics            |                     |      |

|-------------|-----------------|------------------------------|---------------------|---------------------|------|

| Symbol      |                 | Parameter                    | Min. <sup>(1)</sup> | Max. <sup>(1)</sup> | Unit |

| Input level | V <sub>DD</sub> | USB OTG HS operating voltage | 2.7                 | 3.6                 | V    |

#### Table 60. USB HS DC electrical characteristics

1. All the voltages are measured from the local ground potential.

| Table 61. USB HS clock timing parameters <sup>(1</sup> |

|--------------------------------------------------------|

|--------------------------------------------------------|

| Parameter                                                      | Symbol          | Min                     | Nominal | Мах | Unit |     |

|----------------------------------------------------------------|-----------------|-------------------------|---------|-----|------|-----|

| f <sub>HCLK</sub> value to guarantee prope<br>USB HS interface | er operation of | -                       | 30      | -   | -    | MHz |

| Frequency (first transition)                                   | 8-bit ±10%      | F <sub>START_8BIT</sub> | 54      | 60  | 66   | MHz |

#### Equation 1: R<sub>AIN</sub> max formula

$$R_{AIN} = \frac{(k - 0.5)}{f_{ADC} \times C_{ADC} \times \ln(2^{N+2})} - R_{ADC}$$

The formula above (*Equation 1*) is used to determine the maximum external impedance allowed for an error below 1/4 of LSB. N = 12 (from 12-bit resolution) and k is the number of sampling periods defined in the ADC\_SMPR1 register.

| Symbol | Parameter                    | Test conditions                                                                                         | Тур  | Max <sup>(1)</sup> | Unit |

|--------|------------------------------|---------------------------------------------------------------------------------------------------------|------|--------------------|------|

| ET     | Total unadjusted error       |                                                                                                         | ±2   | ±5                 |      |

| EO     | Offset error                 | f <sub>PCLK2</sub> = 60 MHz,                                                                            | ±1.5 | ±2.5               |      |

| EG     | Gain error                   | $f_{ADC} = 30 \text{ MHz}, R_{AIN} < 10 \text{ k}\Omega, V_{DDA} = 1.8^{(2)} \text{ to } 3.6 \text{ V}$ | ±1.5 | ±3                 | LSB  |

| ED     | Differential linearity error | $V_{DDA} = 1.8^{(2)}$ to 3.6 V                                                                          | ±1   | ±2                 |      |

| EL     | Integral linearity error     |                                                                                                         | ±1.5 | ±3                 |      |

1. Guaranteed by characterization.

V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V is obtained when the device operates in reduced temperature range, and with the use of an external power supply supervisor (refer to Section : Internal reset OFF).

Note:

te: ADC accuracy vs. negative injection current: injecting a negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents. Any positive injection current within the limits specified for I<sub>INJ(PIN)</sub> and SI<sub>INJ(PIN)</sub> in Section 5.3.16 does not affect the ADC accuracy.

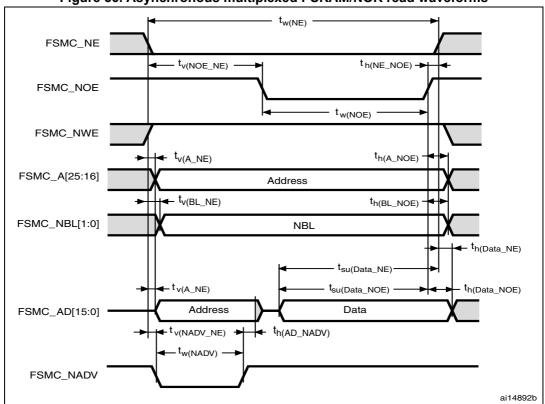

Figure 56. Asynchronous multiplexed PSRAM/NOR read waveforms

### Table 77. Asynchronous multiplexed PSRAM/NOR read timings<sup>(1)(2)</sup>

| Symbol                    | Parameter                                             | Min                     | Мах                     | Unit |

|---------------------------|-------------------------------------------------------|-------------------------|-------------------------|------|

| t <sub>w(NE)</sub>        | FSMC_NE low time                                      | 3T <sub>HCLK</sub> –1   | 3T <sub>HCLK</sub> +1   | ns   |

| t <sub>v(NOE_NE)</sub>    | FSMC_NEx low to FSMC_NOE low                          | 2T <sub>HCLK</sub> -0.5 | 2T <sub>HCLK</sub> +0.5 | ns   |

| t <sub>w(NOE)</sub>       | FSMC_NOE low time                                     | T <sub>HCLK</sub> –1    | T <sub>HCLK</sub> +1    | ns   |

| t <sub>h(NE_NOE)</sub>    | FSMC_NOE high to FSMC_NE high hold time               | 0                       | -                       | ns   |

| t <sub>v(A_NE)</sub>      | FSMC_NEx low to FSMC_A valid                          | -                       | 3                       | ns   |

| t <sub>v(NADV_NE)</sub>   | FSMC_NEx low to FSMC_NADV low                         | 1                       | 2                       | ns   |

| t <sub>w(NADV)</sub>      | FSMC_NADV low time                                    | T <sub>HCLK</sub> – 2   | T <sub>HCLK</sub> +1    | ns   |

| t <sub>h(AD_NADV)</sub>   | FSMC_AD(adress) valid hold time after FSMC_NADV high) | T <sub>HCLK</sub>       | -                       | ns   |

| t <sub>h(A_NOE)</sub>     | Address hold time after FSMC_NOE high                 | T <sub>HCLK</sub> –1    | -                       | ns   |

| t <sub>h(BL_NOE)</sub>    | FSMC_BL time after FSMC_NOE high                      | 0                       | -                       | ns   |

| t <sub>v(BL_NE)</sub>     | FSMC_NEx low to FSMC_BL valid                         | -                       | 2                       | ns   |

| t <sub>su(Data_NE)</sub>  | Data to FSMC_NEx high setup time                      | T <sub>HCLK</sub> +4    | -                       | ns   |

| t <sub>su(Data_NOE)</sub> | Data to FSMC_NOE high setup time                      | T <sub>HCLK</sub> +4    | -                       | ns   |

| t <sub>h(Data_NE)</sub>   | Data hold time after FSMC_NEx high                    | 0                       | -                       | ns   |

| t <sub>h(Data_NOE)</sub>  | Data hold time after FSMC_NOE high                    | 0                       | -                       | ns   |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization.

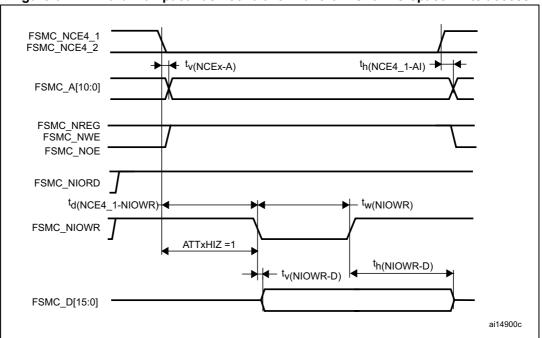

Figure 67. PC Card/CompactFlash controller waveforms for I/O space write access

Table 83. Switching characteristics for PC Card/CF read and write cycles in attribute/common space  $^{(1)(2)}$

| Symbol                    | Parameter                                    | Min                     | Мах                     | Unit |

|---------------------------|----------------------------------------------|-------------------------|-------------------------|------|

| t <sub>v(NCEx-A)</sub>    | FSMC_Ncex low to FSMC_Ay valid               | -                       | 0                       | ns   |

| t <sub>h(NCEx_AI)</sub>   | FSMC_NCEx high to FSMC_Ax invalid            | 4                       | -                       | ns   |

| t <sub>d(NREG-NCEx)</sub> | FSMC_NCEx low to FSMC_NREG valid             | -                       | 3.5                     | ns   |

| t <sub>h(NCEx-NREG)</sub> | FSMC_NCEx high to FSMC_NREG invalid          | T <sub>HCLK</sub> +4    | -                       | ns   |

| t <sub>d(NCEx-NWE)</sub>  | FSMC_NCEx low to FSMC_NWE low                | -                       | 5T <sub>HCLK</sub> +0.5 | ns   |

| t <sub>d(NCEx-NOE)</sub>  | FSMC_NCEx low to FSMC_NOE low                | -                       | 5T <sub>HCLK</sub> +0.5 | ns   |

| t <sub>w(NOE)</sub>       | FSMC_NOE low width                           | 8T <sub>HCLK</sub> –1   | 8T <sub>HCLK</sub> +1   | ns   |

| t <sub>d(NOE_NCEx)</sub>  | FSMC_NOE high to FSMC_NCEx high              | 5T <sub>HCLK</sub> +2.5 | -                       | ns   |

| t <sub>su (D-NOE)</sub>   | FSMC_D[15:0] valid data before FSMC_NOE high | 4.5                     | -                       | ns   |

| t <sub>h(N0E-D)</sub>     | FSMC_N0E high to FSMC_D[15:0] invalid        | 3                       | -                       | ns   |

| t <sub>w(NWE)</sub>       | FSMC_NWE low width                           | 8T <sub>HCLK</sub> –0.5 | 8T <sub>HCLK</sub> + 3  | ns   |

| t <sub>d(NWE_NCEx)</sub>  | FSMC_NWE high to FSMC_NCEx high              | 5T <sub>HCLK</sub> –1   | -                       | ns   |

| t <sub>d(NCEx-NWE)</sub>  | FSMC_NCEx low to FSMC_NWE low                | -                       | 5T <sub>HCLK</sub> + 1  | ns   |

| t <sub>v(NWE-D)</sub>     | FSMC_NWE low to FSMC_D[15:0] valid           | -                       | 0                       | ns   |

| t <sub>h</sub> (NWE-D)    | FSMC_NWE high to FSMC_D[15:0] invalid        | 8T <sub>HCLK</sub> –1   | -                       | ns   |

| t <sub>d</sub> (D-NWE)    | FSMC_D[15:0] valid before FSMC_NWE high      | 13T <sub>HCLK</sub> –1  | -                       | ns   |

1. C<sub>L</sub> = 30 pF.

2. Guaranteed by characterization.

### 6.2 LQFP64 package information

Figure 78. LQFP64 – 64-pin, 10 x 10 mm low-profile quad flat package outline SEATING PLANE С <[₽] 0.25 mm GAUGE PLANE ¥ Ł ¥ D k D1 L1 D3 48 33 32 49 b Ш Ш Ш **1**7 64 ₿₿₿₿ ▋▋₿ Ht 8888 16 PIN 1 IDENTIFICATION 1 5W\_ME\_V3

1. Drawing is not to scale.

| Table 92. LQFP64 – 64-pin 10 x 10 mm low-profile quad flat package |

|--------------------------------------------------------------------|

| mechanical data                                                    |

| Symbol | millimeters |        |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|--------|-------|-----------------------|--------|--------|

|        | Min         | Тур    | Мах   | Min                   | Тур    | Max    |

| А      | -           | -      | 1.600 | -                     | -      | 0.0630 |

| A1     | 0.050       | -      | 0.150 | 0.0020                | -      | 0.0059 |

| A2     | 1.350       | 1.400  | 1.450 | 0.0531                | 0.0551 | 0.0571 |

| b      | 0.170       | 0.220  | 0.270 | 0.0067                | 0.0087 | 0.0106 |

| с      | 0.090       | -      | 0.200 | 0.0035                | -      | 0.0079 |

| D      | -           | 12.000 | -     | -                     | 0.4724 | -      |

| D1     | -           | 10.000 | -     | -                     | 0.3937 | -      |

| D3     | -           | 7.500  | -     | -                     | 0.2953 | -      |

| E      | -           | 12.000 | -     | -                     | 0.4724 | -      |

| E1     | -           | 10.000 | -     | -                     | 0.3937 | -      |

| Table 95. UFBGA176+25 ball, 10 × 10 × 0.65 mm pitch, ultra thin fine pitch |  |

|----------------------------------------------------------------------------|--|

| ball grid array mechanical data (continued)                                |  |

| Symbol | millimeters |     |       | inches <sup>(1)</sup> |     |        |

|--------|-------------|-----|-------|-----------------------|-----|--------|

| Symbol | Min         | Тур | Max   | Min                   | Тур | Max    |

| eee    | -           | -   | 0.150 | -                     | -   | 0.0059 |

| fff    | -           | -   | 0.050 | -                     | -   | 0.0020 |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

## Figure 88. UFBGA176+25 - 201-ball, 10 x 10 mm, 0.65 mm pitch, ultra fine pitch ball grid array recommended footprint

| 00000000000000000000000000000000000000  |           |

|-----------------------------------------|-----------|

|                                         |           |

|                                         |           |

| 0000 00000 0000                         |           |

| 0000 00000 0000                         |           |

| 0000 00000 0000                         |           |

| 0000 00000 0000                         |           |

| 0000 0000                               |           |

| 000000000000000000000000000000000000000 |           |

| 000000000000000000000000000000000000000 |           |

| 000000000000000000000000000000000000000 |           |

| 000000000000000                         | 0E7_FP_V1 |

|                                         |           |

#### Table 96. UFBGA176+2 recommended PCB design rules (0.65 mm pitch BGA)

| Dimension | Recommended values                                               |

|-----------|------------------------------------------------------------------|

| Pitch     | 0.65                                                             |

| Dpad      | 0.300 mm                                                         |

| Dsm       | 0.400 mm typ. (depends on the soldermask registration tolerance) |

Note:

Non solder mask defined (NSMD) pads are recommended.

4 to 6 mils solder paste screen printing process.

Stencil opening is 0.300 mm.

Stencil thickness is between 0.100 mm and 0.125 mm.

Pad trace width is 0.100 mm.

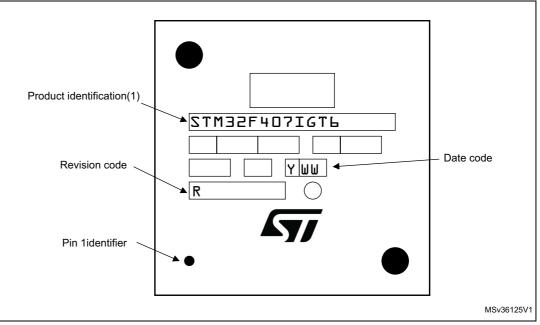

#### **Device marking for LQFP176**

The following figure gives an example of topside marking and pin 1 position identifier location.

Other optional marking or inset/upset marks, which depend on supply chain operations, are not indicated below.

Figure 92. LQFP176 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

| Date                | Revision                     | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|---------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Date<br>04-Jun-2013 | Revision<br>4<br>(continued) | Changes<br>Updated Table 64: Dynamic characteristics: Eternity MAC signals for<br>SMI.<br>Updated Table 66: Dynamic characteristics: Ethernet MAC signals for<br>MII.<br>Updated Table 79: Synchronous multiplexed NOR/PSRAM read<br>timings.<br>Updated Table 80: Synchronous multiplexed PSRAM write timings.<br>Updated Table 81: Synchronous non-multiplexed NOR/PSRAM read<br>timings.<br>Updated Table 82: Synchronous non-multiplexed PSRAM write<br>timings.<br>Updated Section 5.3.27: Camera interface (DCMI) timing specifications<br>including Table 87: DCMI characteristics and addition of Figure 72:<br>DCMI timing diagram.<br>Updated Section 5.3.28: SD/SDIO MMC card host interface (SDIO) |  |  |

|                     |                              | <i>characteristics</i> including <i>Table 88</i> .<br>Updated <i>Chapter Figure 9</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

Table 100. Document revision history (continued)

| Date        | Revision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 22-Oct-2015 | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | In the whole document, updated notes related to values guaranteed by design or by characterization.<br>Updated <i>Table 34: HSI oscillator characteristics</i> .<br>Changed f <sub>VCO_OUT</sub> minimum value and VCO freq to 100 MHz in<br><i>Table 36: Main PLL characteristics</i> and <i>Table 37: PLLI2S (audio PLL)</i><br><i>characteristics</i> .<br>Updated <i>Figure 39: SPI timing diagram - slave mode and CPHA = 0</i> .<br>Updated <i>Figure 53: 12-bit buffered /non-buffered DAC</i> .<br>Removed note 1 related to better performance using a restricted V <sub>DD</sub><br>range in <i>Table 68: ADC accuracy at fADC = 30 MHz</i> .<br>Upated <i>Figure 84: LQFP144 - 144-pin, 20 x 20 mm low-profile quad flat</i><br><i>package outline</i> .<br>Updated <i>Figure 87: UFBGA176+25 ball, 10 x 10 mm, 0.65 mm pitch,</i><br><i>ultra fine pitch ball grid array package outline</i> and <i>Table 95:</i><br><i>UFBGA176+25 ball, 10 x 10 x 0.65 mm pitch, ultra thin fine pitch ball</i><br><i>grid array mechanical data</i> . |  |  |

| 16-Mar-2016 | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Updated Figure 2: Compatible board design<br>STM32F10xx/STM32F2/STM32F40xxx for LQFP100 package.<br>Updated  Vssx–Vss  in Table 11: Voltage characteristics to add V <sub>REF</sub> .<br>Added V <sub>REF</sub> _in Table 67: ADC characteristics.<br>Updated Table 90: WLCSP90 - 4.223 x 3.969 mm, 0.400 mm pitch<br>wafer level chip scale package mechanical data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| 09-Sep-2016 | <ul> <li>Remove note 1 below <i>Figure 5: STM32F40xxx block diagram</i>.<br/>Updated definition of stresses above maximum ratings in <i>Section Absolute maximum ratings</i>.<br/>Updated t<sub>h(NSS</sub>) in <i>Figure 39: SPI timing diagram - slave mode ar CPHA = 0Figure</i> and <i>Figure 40: SPI timing diagram - slave mode ar CPHA = 1</i>.<br/>Added note related to optional marking and inset/upset marks in a package marking sections.<br/>Updated <i>Figure 87: UFBGA176+25 ball, 10 x 10 mm, 0.65 mm pi ultra fine pitch ball grid array package outline</i> and <i>Table 95: UFBGA176+25 ball, 10 × 10 × 0.65 mm pitch, ultra thin fine pitch grid array mechanical data</i>.</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

Table 100. Document revision history (continued)